# A One-Transistor-Synapse Strategy for Electrically-Programmable Massively-Parallel Analog Array Processors

R. Domínguez-Castro, S. Espejo, A. Rodríguez-Vázquez, R. Carmona

Instituto de Microelectrónica de Sevilla-Universidad de Sevilla, Edificio CICA, C/Tarfia s/n, 41012-Sevilla, SPAIN, Phone: +34 5 4239923; FAX: +34 5 4231832; email: espejo@cnm.us.es

ABSTRACT: This paper presents a linear, four-quadrants, electrically-programmable, one-transistor synapse strategy applicable to the implementation of general massively-parallel analog processors in CMOS technology. It is specially suited for translationally-invariant processing arrays with local connectivity, and results in a significant reduction in area occupation and power dissipation of the basic processing units. This allows higher integration densities and therefore, permits the integration of larger arrays on a single chip.

#### 1. Introduction

The electronic implementation of artificial neural systems is one of the few fields in which analog VLSI has resisted the continuous expansion of digital processing techniques, and is expected to remain doing so in the future [1]. Massively-parallel analog array processors can be considered as a subset of artificial neural systems, their specific characteristics being a regular spatial distributions of the elementary processing units (or cells), and a connectivity limited to nearby cells in the array. Cellular neural networks [2] are a typical example of this class of systems.

The local connectivity and regularity, as well as the generally simple processing function performed by the cells, facilitates their compact and efficient monolithic implementation. This, together with the high computation capability derived from their highly-parallel architecture forecasts a wide range of potential applications.

One of the most promising application fields is the preprocessing front-end of real-time perception systems, for instance artificial vision [3], [4], [5]. Their role is usually to extract a reduced set of key characteristics from the large set of input data, and to transmit them to higher level processors in the perception/decision chain which would be unable to manage the raw input data in real time.

Most spatio-temporal linear or nonlinear functions with moderate accuracy requirements can generally be realized by these electronic systems, including motion detection and estimation [6], "center of gravity" calculation, segmentation, etc. [7]. Furthermore, the high processing speed resulting from parallelism permits the use of moderate or even large sequential processing applications combining different spatio-temporal filters, if the electronic implementations are programmable [8]. This opens a huge range of more

complex applications, some examples of which are object classifications according to size, orientation, or texture, object-counting, and character recognition [7].

The most important trend in the electronic implementation of these class of systems is the maximization of the number of elementary processing units that can be placed in a single chip. This must be combined with the achievement of an acceptable accuracy for the system parameters. The first trend imposes strong commitment in the design of the cell circuitry: areaefficiency. A second but also important objective is power-economy. Unfortunately, in analog processing circuits, area and power consumption of individual devices are directly related to accuracy [9]. Therefore, the selection of a circuit strategy as simple as possible for the prescribed processing function is crucial.

This paper proposes a one-transistor, four-quadrants, electrically-programmable, linear synapse for the implementation of massively-parallel analogarray processors in CMOS technologies. The proposal is easily extensible to general artificial neural networks.

# 2. Analog-Array-Processors Elementary Units

Each processing unit (or *cell*) in a massively-parallel analog-array processor can be characterized by an interconnection pattern and by an specific processing function. These characteristics are often considered invariant from cell to cell, resulting in an additional simplification of the electronic implementation. This property, commonly referred to as spatial invariance or uniformity, will be assumed without loss of generality.

A common characteristic of massively-parallel analog processing algorithms is the *local* computation (within each cell c) of a weighted aggregation of contributions from the cells in its neighborhood,

$$y_c = \sum_{i=1}^{N} A_i x_i \tag{1}$$

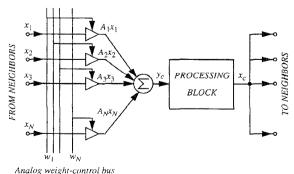

The aggregated signal  $y_c$  is then used as input to a processing-block which realizes some specific function, and generates an output  $x_c$  representative of the cell state. In turn, this output constitutes the (unscaled) contribution of the cell to its neighbors. This general cell architecture is illustrated in Fig. 1. The output  $x_i$  of each neighbor is weighted by a coef-

ficient  $A_i$ , which is independent of the particular receptor cell c under the assumed spatial uniformity. Except for specific purpose systems it is generally required that the scaling coefficients (or weights)  $A_i$  be electrically programmable, for versatility reasons.

At a system level, the required number of signal-scaling circuit-blocks (or *synapses*) can be computed as *N* times the number of cells. The associated area and power consumption, as well as the obvious effects of the synapse accuracy on the overall performance of the system, renders the selection of the synapse circuitry a crucial issue in the design of integrated analog array processors.

### 3. Electrically-Programmable Synapses

Electrically programmable synapses must be driven by the input signal  $x_i$ , and by a weight signal  $w_i$  used to program the scaling coefficient  $A_i$ . Under the assumed spatial uniformity, only N different weight values will coexist throughout the array. Therefore, a reduced number (N) of global nodes (common to all cells in the network) satisfy the programming-related routing requirements of the array, if the programming signals  $w_i$  are codified as voltages. Since every cell output  $x_c$  is transmitted to N synapses located within its N neighboring cells, it is also appropriate that synapse input signals  $x_i$  be codified as voltages. Finally, because scaled signals must be added at the input of each cell's processing block, it is convenient that synapse output signals  $A_i x_i$  be given in current form, eliminating the need of a dedicated summing circuit.

Although the required functionality of a programmable analog synapse may suggest the use of linear analog multipliers, there are some specific circumstances common to almost every analog-array processing algorithm which expand the set of selectable circuit blocks.

First note that while the synapses output current is expected to be linear with the input signal  $x_i$ , it is not required to be linear with the weight signal  $w_i$ , whose function is simply to allow weight variations in some prescribed range. Therefore, function  $A_i(w_i)$  may be nonlinear in general.

Second, in almost every analog-array processing algorithm, the weight values are invariant during processing. Therefore, the dynamic response with

Fig. 1: General architecture of an analog-processing-array elementary processing unit (cell).

respect to the weight signal is of little concern and, more important, after setting the weight values, any error or deviation from the ideal behavior independent of the input signal  $x_i$  (but in general dependent on  $w_i$ ) may be cancelled using autozeroing, before performing the processing function.

This is a good practice in general because the offset of the aggregated signal is given by the addition of the output-current offset of the N synapses driving each cell. Indeed, this is often the dominant error source of this class of systems.

In the last years, synapse circuits based on MOS transistors operating in their ohmic region have been employed by several authors [10], [11]. The choice is based on a combined estimation of several performance figures (including area occupation, accuracy, linearity, programming weight range, signal-range, and power efficiency) which predicts important advantages as compared to other classes of synapse circuits based on the quadratic law of MOS transistors in saturation, or the exponential law of bipolar transistors and MOS transistors in weak inversion.

Regardless the family, practically all synapse circuits employ differential or fully differential architectures to achieve four-quadrants behavior and also for linearity reasons. Typical examples include those synapses based on differential pairs, like the Gilbert multiplier [12], and also the synapses employed in [10] and [11]. In addition to the larger complexity of the synapse, this usually forces the use of differential or fully differential architectures in the processing block as well, thus resulting in a substantial increase in area occupation.

In the following section we propose a one-transistor, four-quadrants, electrically-programmable synapse circuit with single-ended architecture.

#### 4. A One-Transistor Synapse Circuit

The DC current of an MOS transistor operating in its strong-inversion ohmic region can be described by the following well-known first-order approximation

$$I_{DS} = \beta \left( V_{GS} - V_T (V_{SB}) - \frac{V_{DS}}{2} \right) V_{DS}$$

(2)

where

$$\beta = \mu C \frac{W}{ox L} \tag{3}$$

$$V_T(V_{SB}) = V_{T0} + \gamma \left( \sqrt{V_{SB} - \phi_B} - \sqrt{\phi_B} \right)$$

(4)

and every symbols has its well established meaning in MOS literature.

Eq. (2) predicts an *incrementally* linear relation between  $I_{DS}$  and  $V_{GS}$ , and an *approximately* linear dependence with  $V_{DS}$  for  $V_{DS} \ll 2 \left[ V_{GS} - V_T (V_{SB}) \right]$ . These considerations have been widely exploited for many applications, including MOS implementations of active RC filters [13], analog multipliers for RF communication circuits [14] and also synapse circuits for massively-parallel analog processing systems

[10], [11] using differential architectures.

The use of a single transistor to implement an electrically programmable synapse with signals represented by single-ended voltages requires that one of the diffusion terminals be set to a fixed voltage level. The gate and the other diffusion terminals can then be employed as input points, while the output is obtained from the current flowing out of the fixed-voltage diffusion terminal. This is conceptually illustrated in Fig. 2 in which a nullator and a DC voltage source represent the ideally null-impedance input terminal of the processing block in Fig. 1. Such a virtual-reference level is required because the output impedance of the synapse is low due to its operation in the ohmic region. The input impedance at the diffusion input is also low, while that at the gate input is high. Two alternatives can then be considered: using the gate terminal for  $x_i$  and the diffusion terminal for  $w_i$ , or the other way around. This has implications on the output-impedance requirements for either the cell processing-block or the voltage sources driving the analog-weight control bus, but the major decision factor is related to linearity.

Equation (2) is valid only for  $V_{DS} \ge 0$  and therefore, the use of the notation introduced in Fig. 2 requires an independent consideration of the two possible cases  $V_A \ge V_L$  and  $V_A \le V_L$ . Still, simple analysis results in the following combined expression for  $I_n$ , valid in either of the two cases,

$$I_N = \beta (V_A - V_L) V_G - \beta \left( \hat{V}_T + \frac{V_A + V_L}{2} \right) (V_A - V_L)$$

(5)

with

$$\hat{V_T} = \begin{cases} V_{T0} + \gamma \left( \sqrt{V_L - \phi_B} - \sqrt{\phi_B} \right) ; V_A \ge V_L \\ V_{T0} + \gamma \left( \sqrt{V_A - \phi_B} - \sqrt{\phi_B} \right) ; V_A \le V_L \end{cases}$$

$$(6)$$

Note that the second summand in (5) is independent of  $V_G$  and that the first summand is linear with  $V_G$ . Since we need a linear behavior with respect to one of the inputs  $(x_i)$  and we can eliminate any systematic offset in a previous step, it seems straight forward that we can chose  $x_i \equiv V_G$  and  $w_i \equiv V_A$ , as shown in Fig. 2.

There is still another issue related to the obtention of a four-quadrants behavior. While the two possibilities  $V_A \ge V_L$  and  $V_A \le V_L$  provide double sign capability for the weight,  $V_G$  must always be positive. Therefore we must select a sufficiently high reference level on the gate voltage to act as the zero level for  $x_i$ . Let us define:

$$V_{X} = V_{x} + V_{x0} \Rightarrow V_{x} = V_{X} - V_{x0} \equiv x_{n}$$

$$V_{G} \Rightarrow V_{X} \qquad I_{N}$$

$$V_{A} \rightarrow V_{W} \qquad I_{N}$$

$$V_{L}$$

$$V_{L}$$

$$V_{L}$$

$$V_{R} \Rightarrow V_{L}$$

$$V_{L}$$

$$V_{R} \Rightarrow V_{L}$$

$$V_{R} \Rightarrow V_{L}$$

$$V_{R} \Rightarrow V_{L}$$

Fig. 2: One transistor synapse concept.

and in the same manner, referring the weight voltage to  $V_L$ , this is, selecting  $V_{w0} = V_L$ , we have

$$V_W = V_w + V_L \Rightarrow V_w = V_W - V_L \equiv w_n \tag{8}$$

Using this new notation, equations (5) and (6) can be rewritten respectively as:

$$I_{N} = \beta V_{w} V_{x} + \beta V_{w} \left( V_{x0} - \hat{V}_{T} - V_{L} - \frac{V_{w}}{2} \right)$$

(9)

$$\hat{V_T} = \begin{cases} V_{T0} + \gamma \left( \sqrt{V_L - \phi_B} - \sqrt{\phi_B} \right) & ; V_w \ge 0 \\ V_{T0} + \gamma \left( \sqrt{V_w + V_L - \phi_B} - \sqrt{\phi_B} \right) & ; V_w \le 0 \end{cases}$$

(10)

where both  $V_x$  and  $V_w$  can be either positive or negative and still, the first summand in (9) is linear with  $V_x$  and the second one is independent of  $V_x$ . We define the weight and the output offset of the synapse, respectively, as

$$G(V_w) = \beta V_w \tag{11}$$

$$I_0(V_w) = G(V_w) \left( V_{x0} - \hat{V}_T - V_L - \frac{V_w}{2} \right)$$

(12)

This allows (9) to be written in the following form

$$I_N(V_w, V_x) = G(V_w)V_x + I_0(V_w)$$

(13)

Let us now assume that we can eliminate the term  $I_0(V_w)$ , Then, we can define

$$I_N = I_n + I_0 \Rightarrow I_n = I_N - I_0 \equiv A_i x_i \tag{14}$$

and rewrite (13) as

$$I_n(V_w, V_r) = G(V_w)V_r$$

(15)

which is the equation of four-quadrants, electrically-programmable, linear analog synapse. This relies only on the *separated* dependencies shown in (13), and not on the specific forms of  $G(V_w)$  and  $I_0(V_w)$ , a fact that will become relevant for the consideration of second order effects in a latter section

### 5. Cell and Control Circuitry

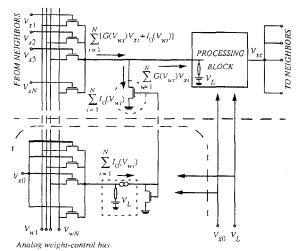

In order to preserve the high area efficiency provided by the one-transistor synapses, the circuitry employed within each cell for the elimination of the N second summands (one per synapse) should be as simple as possible.

Under the assumed spatial invariance of the weight signals, common to most analog-array processing systems, the *sum* of the *N* summands to be eliminated in each cell is also spatially invariant. Therefore, we can reproduce its value in a small circuitry, shared by all the cells in the network and placed at the periphery of the cell array, and substract it at the input nodes of each cell processing block, by means of simple current mirrors. Only the output branch of the current mirror must be located within the cell, the input branch being shared also by all the cells in the network with the help of one single global node: the gate voltage of the multi-output current mirror.

Fig. 3 illustrates the required circuitry. The top part of the figures describes de cell circuitry, identical to

Fig. 1 using one-transistor synapses, and only one additional transistor (circled) for the substraction of the N second summands in (13). The lower part of the figure describes the circuitry required at the periphery of the cell array and shared by the whole network.

This circuitry relies on the use of matched current-conveyors [12] at the peripheral circuitry and at the input node of the cells processing-block. Their electronic implementation can be shown to be highly efficient in terms of area and power consumption [11].

It might be argued that large-distance mismatch effects could result in cancellation errors of the independent terms. However, as mentioned earlier, it is generally convenient to employ autozeroing techniques. Such autozeroing, which can be easily implemented with area-efficient current memories [15] in the cases considered (current-output synapses), would eliminate the cancellation error as well. Indeed, the use of autozeroing may render unnecessary the proposed substraction circuitry, since it could be used to eliminate the complete sum of independent terms rather than their remaining error. Although combining high-signal-ranges and high-absoluteaccuracy is often difficult, the recently proposed class of S<sup>2</sup>I current memories [16] may provide a good solution.

## 6. Operation Limits and Second Order Effects

One fundamental limitation to the operation range of the proposed synapse is imposed by the ohmic region limits of the MOS transistor, which can be approximated by

$$V_{GS} \ge V_{DS} + V_T(V_{SB}) \tag{16}$$

Substitution of the previously employed notation in this equation yields the following lower limit for the gate voltage

$$V_X \ge \begin{cases} V_L + V_T(V_W) & : V_W \le V_L \\ V_W + V_T(V_L) & : V_W \ge V_L \end{cases} \tag{17}$$

Except for this limit, no other restrictions exist on

Fig. 3: Cell (top) and peripheral (bottom) circuitry employed for independent-terms substraction.

the proposed synapse, on the basis of the first order model considered. It can be shown that there is only one second order effect, *mobility degradation*, which represents a relevant deviation from the functional dependence expressed in (13). Other second order effects affect only to the precise form of  $G(V_w)$  and  $I_0(V_w)$  which is irrelevant for our discussion.

Mobility degradation models predict a reduction in the effective carriers mobility ( $\mu$  in equation (3)) with transversal (normal to channel surface) electric field, something that affects our present discussion because the transversal electric field depends on the gate voltage and thus, the first summand will not be linear with  $V_x$ . Although the widely accepted *simple* model for mobility degradation [17].

$$\mu = \frac{\mu_0}{1 + \theta \left( V_{GS} - V_T (V_{SB}) \right)} \tag{18}$$

predicts a continuous reduction of the effective mobility starting just above  $V_{GS} = V_T(V_{SB})$ , the fact is that in most technologies, there is an appreciable (~2.0v)  $V_{GS}$  range above  $V_T(V_{SB})$  within which mobility reduction is negligible. Furthermore, some higher level models accounting for mobility degradation employ a specific parameter to define a field threshold below which no mobility degradation occurs (UCRIT in SPICE level 2 [18]). Regardless the continuous or thresholded modeling of mobility degradation, we can always define a maximum effective gate voltage

$$V_{GE_{\text{MAX}}} = [V_{GS} - V_{T}(V_{SB})]_{\text{MAX}}$$

(19)

below which any reasonable linearity requirements are satisfied. The operation of the synapse must be restricted to this range.

Performing the appropriate substitutions in (19) yields the following upper limit for the gate voltage,

$$V_X \leq \left\{ \begin{array}{l} V_W + V_T(V_W) + V_{GE_{\mbox{\scriptsize MAX}}} \; ; V_W \leq V_L \\ V_L + V_T(V_L) + V_{GE_{\mbox{\scriptsize MAX}}} \; ; V_W \geq V_L \end{array} \right. \tag{20}$$

The selection of  $V_L$  and  $V_{x0}$  must be made based on the limits imposed by (17) and (20). In turn, this will result in an upper limit for the allowed signal ranges of  $V_w$  and  $V_x$ . Equation (17) can be rewritten as,

$$\begin{split} &V_x+V_{x0} \geq V_w+V_L+V_T(V_L) & ; V_w \geq 0 \\ &V_x+V_{x0} \geq V_L+V_T(V_w+V_L) & ; V_w \leq 0 \end{split} \tag{21}$$

Let us denote the signal ranges of  $V_w$  and  $V_x$  by  $|V_w| \le V_{w\max}$  and  $|V_x| \le V_{x\max}$ , respectively. In the above equation, the worst-case limit for  $V_{x0}$  is given by the first inequality when  $V_w = V_{w\max}$  and  $V_x = -V_{x\max}$ , which yields,

$$V_{x0} \ge V_L + V_T(V_L) + V_{wmax} + V_{xmax}$$

(22)

Regarding  $V_L$ , its value must be sufficiently high to provide room for the minimum  $V_{w}$  value and also for some possible loss of voltage range due to the limited

output swing of the circuits generating the analog weight control signals, which we denote as  $V_{W \min}$ . This is,

$$V_L \ge V_{w \max} + V_{w \min} \tag{23}$$

Because an upper limit for the voltage ranges exist due to mobility degradation, and also because we are interested in maximizing the signal ranges and/or allowing a reduced power supply operation, we will select the minimum allowed value for  $V_L$ . Substituting  $V_L = V_{w \max} + V_{w \min}$  in (22) results in a minimum value for  $V_{x0}$ ,

$$V_{x(1)} \ge V_{w\min} + V_T (V_{w\max} + V_{w\min}) + 2V_{w\max} + V_{x\max}$$

(24)

Again, we select  $V_{x0}$  as its minimum allowed value. The resulting maximum value for  $V_X$  is then given by  $V_{X \text{max}} = V_{x0} + V_{x \text{max}}$ , this is,

$$V_{X_{\text{max}}} = V_{W_{\text{min}}} + V_T (V_{W_{\text{max}}} + V_{W_{\text{min}}}) + 2V_{W_{\text{max}}} + 2V_{X_{\text{max}}}$$

(25)

and the worst case mobility degradation limit will be imposed by the first inequality in (20), when  $V_W$  is minimum, this is,  $V_W = V_L - V_{wmax} = V_{Wmin}$ , which yields,

$$V_{X\max} \le V_{W\min} + V_{T}(V_{W\min}) + V_{GE_{\max}}$$

(26)

Using (25) into (26), yields,

$$V_{w\max} + V_{x\max} \le \frac{1}{2} V_{GEMAX} - \frac{1}{2} \left[ V_{T} (V_{w\max} + V_{W\min}) - V_{T} (V_{W\min}) \right]$$

(27)

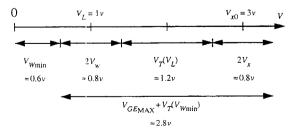

For moderate linearity requirements, the right hand side of the above equation takes values in the range of one volt for typical CMOS technologies, which for  $V_{w\max} = V_{x\max}$  provides a peak-to-peak signal range of about one volt for both  $V_x$  and  $V_w$ .

Fig. 4 illustrates the above discussion and shows the voltage distribution selected for a particular technology: a standard n-well,  $0.8\mu m$  CMOS process available through EUROPRACTICE. With small changes, these values should be valid for most typical CMOS technologies. Note that the minimum power supply level should be at least slightly above  $V_{X_{max}} = 3.4\nu$  to prevent the possible loss of voltage range due to the limited output swing of the processing block. Still, an optimization of the output swing of both the analog weight control drivers and the output stage of the processing block should allow the operation of the proposed synapse with power supply levels in the range of  $3.3\nu$ , with similar signal swings for  $V_x$  and  $V_{yy}$ .

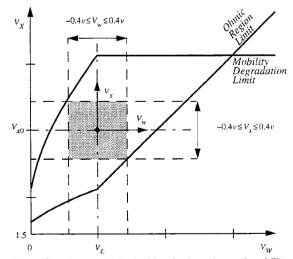

Fig. 5 provides an additional insight into the selection of  $V_L$  and  $V_{x0}$  values and the associated signal ranges. It shows the allowed operation region, delim-

Fig. 4: Voltage range distribution for synapse operation.

ited by (17) and (20) in the  $V_X \cdot V_W$  plane, within which a squared range (under the assumption  $V_{wmax} = V_{xmax}$ ) for signals  $V_x$  and  $V_w$ , centered around ( $V_L$ ,  $V_{x0}$ ), must be defined. The graphs correspond to  $V_L = 1v$  and the specific parameters of the technology being employed. Note that although apparently, an appreciable increase in signal ranges could be obtained by increasing the values of  $V_L$  and  $V_{x0}$ , this is not true in general because the limits imposed by (17) and (20) will also shift with  $V_L$ . In view of (27), the increase would be small. On the other hand, it would require a larger power supply.

#### 7. Results

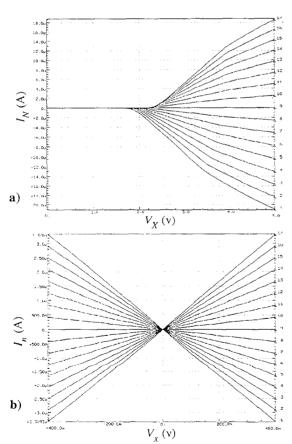

In this section we will illustrate the behavior of the proposed synapse in a specific n-well, 0.8µm CMOS technology available through EUROPRACTICE. Fig. 6 contains HSPICE level 2 simulated transfer characteristics of the proposed synapse. Transistors sizes are  $W = 6\mu m$  and  $L = 24\mu m$ . These geometries correspond to reasonable sizes in a practical application, in which a low aspect ratio serves to the purposes of having reasonable current levels through the analog weight-control lines, as well as moderate power dissipation in the chip. Large channel areas (relative to technology resolution) are required for matching considerations [9]. Still, low resolution technologies are highly convenient for matching considerations and also because most of the cell area is usually dedicated to contacts, routing, and active region separations.

Fig. 6a reflects the total transistor current  $I_N$  versus the total gate voltage  $V_X$ , for different values of the weight signal voltage  $V_w$ . The value of  $V_L$  is 1.0v. Values of  $V_w$ , relative to  $V_L$ , range from - 0.4v (lower trace) to + 0.4v (upper trace) in 50mv increments. The mobility degradation effects are clearly visible at the right side, while those related to the pinch-off region can be observed at left side, specially for positive values of  $V_w$ . The region around  $V_{x0} = 3.0v$  reflects the behavior predicted by (13). Fig. 6b shows the result

Fig. 5: Signal ranges delimited by ohmic region and mobility degradation limits.

obtained after substracting the independent term  $I_0(V_w)$ , by means of the circuitry described in Fig. 3. Wort-case  $(V_w = 0.4\nu)$  total harmonic distortion (THD) is below 0.05% at 1Hz and 0.7% at 1MHz. Similar results are obtained from the p-channel version of the circuitry.

#### 8. Conclusions

This paper has proposed and discussed an electrically programmable, one-transistor, four-quadrants linear synapse strategy for massively-parallel analog array processing systems, based on MOS operation in the triode region. Signal ranges for both the input and the weight signal are in the range of 1vpp, and total harmonic distortion is below 0.7% at 1MHz. Operation from reduced power supplies of about 3.3v seems feasible. The proposed synapse circuit results in a substantial reduction in area and power consumption of the basic cell, as compared to traditionally employed synapses based on differential or fully-differential architectures. This allows the realization of array processors with a larger number of units in the same chip.

Acknowledgment: This work has been funded by spanish CICYT under contract TIC96-1392-C02-02 (SIVA: Active Vision Integrated System).

Fig. 6: HSPICE level-2 simulations of the proposed synapse: a) Current  $I_N$  in Fig. 2 versus gate voltage  $V_X$  for different values of  $V_{w^*}$  b) Current  $I_n = I_N - I_0$  obtained using the circuitry described in Fig. 3.

#### 9. References

- [1] E. Vittoz, "Analog VLSI Signal Processing: Why, Where and How?". Analog Integrated Circuits and Signal Processing, Vol.6, pp. 27-44, (July) 1994.

- [2] L.O. Chua and T. Roska, "The CNN Paradigm", IEEE Trans. Circuits and Systems-I, Vol. CAS-40, pp 147-156, March 1993.

- [3] C.Koch and H.Li (editors): Vision Chips: Implementing Vision Algorithms using Analog VLSI Circuits. New York, IEEE Press 1994.

- [4] K. Kyuma, E. Lange, J. Ohta, A. Hermanns, B. Banish and M. Oita, "Artificial Retinas - Fast, Versatile Image Processors", *Nature*, Vol. 372, pp. 197-198, November 1994.

- [5] F. Werblin, A. Jacobs and J. Teeters, "The Computational Eye", *IEEE Spectrum*, pp. 30-37, May 1996.

- [6] W. Bair, C. Koch, A. Moore, T. Horiuchi, B. Bishofberger and J, Lazzaro: "Computing Motion Using Analog VLSI Vision Chips: An Experimental Comparison Among Four Approaches". Proc. Second Int. Conf. on Microelectronics for Neural Networks. pp 291,309, Munich, October 1991.

- [7] T. Roska and L. Kék, Analogic CNN Program Library, Analogical and Neural Computing Laboratory Memo. DNS-5-1994, Budapest, 1994.

- [8] T. Roska and L.O. Chua, "The CNN Universal Machine: An Analogic Array Computer", *IEEE Transactions on Circuits and Systems-II*, Vol., 40, No.-3, March 1993.

- [9] M.J.M Pelgrom, A.C.J. Duinmaijer and A.P.G. Welbers: "Matching Properties of MOS Transistors". IEEE J. Solid-State Circuits, Vol. 24, pp 1433-1440, October 1989.

- [10] P. Kinget and M. Steyaert, "An Analog Parallel Array Processor for Real-Time Sensor Signal Processing", 1996 Int. Solid State Circuits Conference, paper 6.1, 1996.

- [11] S. Espejo, A. Rodríguez-Vázquez, R. Carmona and R. Domínguez-Castro: "A 0.8µm CMOS Programmable Analog-Array-Processing Vision-Chip with Local Logic and Image-Memory". 1996 European Solid State Circuits Conference, pp. 276-279. Neuchâtel, September 1996.

- [12] C. Toumazou, F.J. Lidgey, D.G. Haigh (Eds.): "Analog IC Design: the Current-Mode Approach", Peter Peregrinus, 1990.

- [13] Y.P. Tsividis: "Integrated Continuous-Time Filter-Design -- An Overview". *IEEE J. Solid-State Cir*cuits, Vol. 29, pp 166-176, march 1994.

- [14] B. Song: "CMOS RF Circuits for Data Communication Applications", *IEEE J. Solid-State Circuits*, Vol.21, pp 310-317, April 1986.

- [15] C. Toumazou, J.B. Hughes, N.C. Battersby (Eds.): "Switched-Currents an Analog Technique for Digital Technology", Peter Peregrinus, 1993.

- [16] J.B. Hughes and K.W. Moulding: "S<sup>2</sup>I: A Switched-Current Technique for High Performance". Electronic Letters. Vol.29, No. 16, pp. 1400-1401, August 1993.

- [17] Y.P. Tsividis, "Operation and Modeling of the MOS Transistors". New York; McGraw-Hill, 1987.

- [18] P Antognetti, G. Massobrio (Eds.): "Semiconductor Device Modeling with SPICE", McGraw-Hill, 1988.