# Tunable Low Noise Amplifier Implementation With Low Distortion Pseudo-Resistance for *in Vivo* Brain Activity Measurement

Zoltán Kárász, Student Member, IEEE, Richárd Fiáth, Student Member, IEEE, Péter Földesy, Member, IEEE, and Ángel Rodríguez Vázquez, Fellow, IEEE

*Abstract*—This paper presents a low power neural signal amplifier with tunable cut-off frequencies. The presented compact amplifier, which is used for sensing various types of neural signals, reduces the size and the power consumption of the whole circuit. The distinguishing features of this solution are the large time constant, linearity, and small achievable area, which are realized with a configurable series of pseudo resistances. The proof of concept has been manufactured on TSMC 90 nm technology.

*Index Terms*—Brain-computer interface, large time constant, neuro-amplifier, pseudo-resistor, LFP, fully differential OTA, common-mode feedback.

### I. INTRODUCTION

THE BIOMEDICAL field is one of the most dynamically developing research area in the analog IC design, specially the low-power implementations for implantable neural interfaces. Some of the examination procedure needs a longerterm recording as it is available with fMRI and better spatial resolution than using EEG technique [1], [2]. Even though in our experiment the portability of the measuring instrument is not an important issue, in principle, it is a relevant question to ensure the freedom of movement of the test subject.

Our interest concerns mostly the implantable cortical micro sensor arrays, which causes minimal structural damages in the analyzed region. From the engineer's aspect, measuring the

Manuscript received September 30, 2013; revised November 8, 2013 and December 4, 2013; accepted December 4, 2013. Date of publication December 12, 2013; date of current version March 11, 2014. This work was supported by the Hungarian National Development Agency under Grants TÁMOP-4.2.1.B-11/2/KMR-2011-0002 and TÁMOP-4.2.2/B-10/1- 2010-0014. The associate editor coordinating the review of this paper and approving it for publication was Prof. Aime Lay-Ekuakille.

Z. Kárász and P. Földesy were with the Institute of Computer Science and Control, Hungarian Academy of Sciences, Budapest 1111, Hungary. They are now with Péter Pázmány University, Faculty of Information Technology, Budapest 1088, Hungary (e-mail: karasz@sztaki.mta.hu; foldesy@ sztaki.mta.hu).

R. Fiáth was with the Research Centre for Natural Sciences, Hungarian Academy of Sciences, Budapest 1111, Hungary. He is now with the School of Ph.D. Studies, Semmelweis University, Budapest 1085, Hungary (e-mail: fiath.richard@ttk.mta.hu).

Á. R. Vázquez was with the Instituto de Microelectrónica de Sevilla, Sevilla 41092, Spain. He is now with the University of Seville, Seville 41092, Spain (e-mail: angel@imse-cnm.csic.es).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSEN.2013.2294971

brain activity could be simplified to an electrical connection between the brain tissue and the electrode. The implantable neural recording devices have to achieve strict specifications, including the power consumption, noise and distortion requirements, defined maximal thermal dissipation and specified input frequency range. The presented architecture is an Operational Trans-conductance Amplifier (OTA) based capacitive feedback single input differential output amplifier including pseudoresistors chains to achieve programmable large time constant and significantly reduced distortion.

## II. BACKGROUND OF NEURAL RECORDING

#### A. Neural Signal

A neuron can produce 100 mV internal voltage changes relative to the extracellular fluid. This voltage can be recorded directly with patch-clamp electrodes, but the in vivo chronic recordings using multi-electrode arrays are able to utilize the smaller extracellular potentials from several micrometers from the cell [3]. The amplitude of the signal is on the order of 100  $\mu$ V [4]. The neural action potentials are called "spikes". Neurons rarely fire more rapidly than 100 spikes per second, although rapid bursts of several spikes are possible. Neurons produce spikes of nearly identical amplitude near to the soma, but the measured signal depend on the position of the electrode relative to the cell. Two main classification methods are prevalent for the high frequency cell activity recording, the multi-unit activity (MUA) and the single-unit activity (SUA). The lower frequency (under 500 Hz) oscillations are known as the local field potentials (LFPs). They arise from the synchronous synaptic and trans-membrane activity of many neurons in one region of the brain. The recorded LFP signals are already filtered, because the extracellular space acts as a low pass filter. The high frequencies such as that produced by action potentials are attenuate more with distance. In the most experiments the electrode arrays scarred the tissue around microelectrode tips. This scar tissue tends to attenuate spike signals from nearby neurons, but LFP signals are less affected. In many applications, it is desirable to separate LFP from spike signals so they may be analyzed separately. This is easily accomplished by linear filtering since LFPs occupy frequencies from approximately 0.1 - 500 Hz, while the

Fig. 1. Transistor model.

energy of the spikes are concentrated in the 500 Hz-7 kHz range.

#### **B.** Amplifier Requirements

The realization of large time constants is fundamental for filters especially in implantable biomedical sensors. The filters are also required to be tunable. In addition, realizations with low power dissipation and small size are also critical. Several approaches with very large time constants have been reported [5]–[7]. The trivial solution is to employ fixed on-chip physical resistor and capacitor, which requires large chip area. The possible alternatives can be categorized into pseudo-resistor implementations [3], [6], [10], [11], switched-capacitor (SC) methods [14]-[16] and operational trans-conductance amplifier capacitor (OTA-C) techniques with very small transconductance's [14]–[16] to allow the on-chip capacitance to be kept manageably low. The current cancellation and division generate a continuous current consumption [8]. The switchedcapacitor provides a method for tuning the transfer-function, but generates large distortion [14].

## C. MOS Pseudo-Resistor

This work is based on pseudo-resistors, as they outperform other solutions in terms of power and area efficiency to reach large time constant [3]. The pseudo-resistance has small size and low parasitic capacitance values (in the range of aF), but it also has some serious non-ideal behavior, which means large distortion in the LFP range. Due to the small transistor size the deviation of the resistance will be grater after the fabrication.

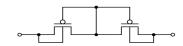

To be able to handle the pseudo element it is necessary to model the resistance of the MOS transistor (Fig. 1).

A descriptive linear model is based on the source diffusion, the channel resistance, the accumulation resistance, the component resistance, the drift region resistance and the substrate resistance [6]. For more appropriate result it needs a nonlinear approximation.

$$\frac{1}{R}\Big|_{V_{\rm DS}=0} = \frac{dI_D}{dU_D}\Big|_{V_{\rm DS}=0} = \frac{dI_D}{dU_S}\Big|_{V_{\rm DS}=0}$$

$$= g_m = \frac{2I_S}{\phi_t} \left(\sqrt{1+i_f-1}\right) \tag{1}$$

Fig. 2. Schematic of the pseudo-resistor element.

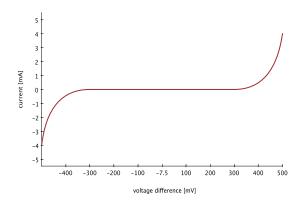

Fig. 3. Current voltage relation on a pseudo transistor.

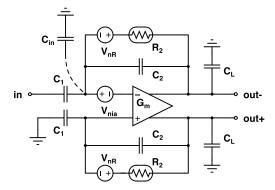

Fig. 4. Schematic of the capacitive feedback amplifier.

In the strong inversion (2) and weak inversion (3) region it is possible to explain the resistance as follows:

$$\frac{1}{R}\Big|_{V_{\text{DS}}=0} = g_m = \mu C'_{\text{ox}} \frac{W}{L} \Big( V_G - V_{T_0} - nV_Q \Big)$$

(2)

$$g_m = \frac{2I_S}{\phi_t} \Big(\frac{1}{2}i_f\Big) = \frac{2I_S}{\phi_t} \exp\left(\frac{V_G - V_{T_0} - nV_Q n\phi_t}{n\phi_t}\right)$$

(3)

where n is the slope parameter.

The most prevalent utilization of the MOS transistor as a resistor is the pseudo-resistor. Its advantages are the minimal size, the simplicity and the large effective resistance [9].

The basic symmetric element contains two transistors that are connected as a MOS diode and a parasitic source-bulk diode connected in anti-parallel (Fig. 2). If the voltage across the device is small enough, then neither diode will conduct strongly, and the effective resistance becomes very large (> 10 G $\Omega$ ).

The current-voltage relationship (Fig. 3) [6], [11] of the expansive element indicates that the effective resistance of the element is large for small signals and small for large signals. Therefore the adaptation is slow for small signals and fast for large signals.

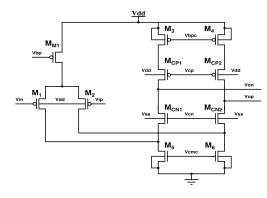

Fig. 5. Differential input cascoded OTA.

The nonlinear variation of the resistance in the feedback loop means the frequency response would not be permanent during the operation. If the cutoff frequency is altered that significantly impairs the distortion in the lower frequency range (under 100 Hz).

Another relevant problem to address with this solution is the large impact of the technological parameters and the operational conditions. The biomedical applications have strict operating requirements in the 30–44 °C temperature range, which actually reduce the variation, but still leave large manufacturing uncertainty (which depends on technology used).

## **III. BASIC NEURO-AMPLIFIER TOPOLOGY**

The amplifier is based on an operational transconductance amplifier (OTA) topology (Fig. 5) [5], [6], [11]–[13]. A capacitive feedback network consisting of  $C_1$  and  $C_2$  capacitors sets the mid-band gain of the amplifier. The input is capacitively coupled through  $C_1$ , so any dc offset from the electrode-tissue interface is removed (Fig. 4).  $C_1$  should be made much smaller than the capacitive part of the electrode impedance to minimize signal attenuation. The  $R_2$  elements shown in the feedback loop set the low-frequency cut-off.

The approximate transfer function is given by

$$\frac{v_{out+} - v_{out-}}{v_{in}} = \frac{C_1}{C_2} \frac{1 - sC_2/G_m}{\left(\frac{1}{sR_2C_2 + 1}\right) \left(s\frac{C_LC_1}{G_mC_2} + 1\right)}$$

(4)

The midband gain  $A_M$  is set by the capacitance ratio  $C_1/C_2$ , and the gain is flat between the lower and upper cutoff frequencies  $f_L$  and  $f_H$ . The product of  $R_2$  and  $C_2$  determines the lower cutoff frequency, while the upper cutoff is determined by the load capacitance  $C_L$ , the OTA trans-conductance  $G_m$ , and the mid-band gain. Capacitive feed introduces a right-halfplane zero at  $f_z$ , but this zero can be very at high frequency by setting

$$C_2 \ll \sqrt{C_1 C_L} \tag{5}$$

so that it has little practical effect on the amplifier's operation. Below a particular frequency called  $f_{corner}$ , the noise contribution from  $v_{nR}$  will dominate. If  $R_2$  is implemented as a real resistor so that its noise spectral density is

$$v_{nR}^2(f) = 4kTR_2 \tag{6}$$

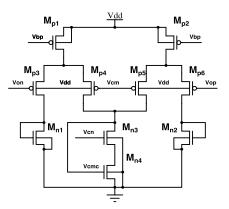

Fig. 6. Common mode feedback for the amplifier.

and  $C_1 \gg C_2$ ,  $C_{in}$ , then  $f_{corner}$  is approximately

$$f_{corner} \approx \sqrt{\frac{3C_L}{2C_1}} f_L f_H \tag{7}$$

A similar result is obtained for pseudo resistor element used as  $R_2$ . To minimize the noise contribution from the  $R_2$  elements, we should ensure that  $f_{corner} \ll f_L$ .

If the noise contribution from  $R_2$  is negligible and  $C_1 \gg C_2$ ,  $C_{in}$ , then the output *rms* noise voltage of the neural amplifier is dominated by the thermal noise from the OTA.

$$v_{nia}^2 = \frac{16kT}{3g_{m1}} \left( 1 + 2\frac{g_{m3}}{g_{m1}} + \frac{g_{m7}}{g_{m1}} \right)$$

(8)

where  $g_{m1}$  is the trans-conductance of the input devices  $M_1$  and  $M_2$ . The noise of the cascode transistors is negligible.

In that case the load capacitance is determined by

$$C_L = \frac{4k\Gamma}{V_{ni}^2 3A_M} \tag{9}$$

In practical implantable multi electrode systems, the size of the capacitances is limited. On the one hand it is due to the minimal size of the  $C_2$  with tolerable fabrication variance. On the other hand the available space set the maximum for the  $C_1$ . The ratio between the capacitances defines the amplification magnitude.

In order to cancel the common-mode current component in the differential output it is necessary to use a feed back circuit, which compares the common mode voltage with a reference and correct the common-mode level. The implementation of this circuit can be seen on Fig. 6, where  $V_{on}$  and  $V_{op}$  are the outputs of the OTA. The  $V_{bp}$  and  $V_{cn}$  are biasing the circuit and the  $V_{cm}$  is the desired common-mode level. The  $V_{cmc}$  is the feedback signal for the amplifier. In Table I and II the used transistor dimensions can be seen respectively for the OTA and the common mode feedback (CMFB) circuit.

# IV. PROPOSED SERIALLY-CONNECTED DIGITALLY CONTROLLABLE PSEUDO-RESISTOR

There is a possible tradeoff between the noise and distortion. Based on our simulation and measurement using more pseudo resistor element in series helps decreasing the nonlinearity

TABLE I TRANSISTOR SIZE CHART FOR THE CMFB

| Element                          | W/L size [µm] |

|----------------------------------|---------------|

| M <sub>p1</sub> /M <sub>p2</sub> | 1/5           |

| $M_{p3}/M_{p4}/M_{p5}/M_{p6}$    | 5/1           |

| $M_{n1}/M_{n2}$                  | 0.5/4         |

| M <sub>n3</sub>                  | 2/1           |

| M <sub>n4</sub>                  | 1/9           |

TABLE II TRANSISTOR SIZE CHART FOR THE OTA

Fig. 7. Resistance variation at different number pseudo-resistor in series (curves  $PS_2$ ,  $PS_8$ ,  $PS_{16}$ ,  $PS_{32}$  respectively) [G $\Omega$ /V].

effect at the price of increasing noise figure. In this section this tradeoff is analyzed on resistor-chains, which contain different number of pseudo resistor elements.

Serializing pseudo-resistors results in decreasing distortion approximately linearly with the number of elements, due to the voltage different would be smaller between the two sides of each element (Fig. 7). Comparing the PS<sub>2</sub> to PS<sub>64</sub> the  $\Delta V$  over one pseudo-resistor (Fig. 2) proportionally 32 times smaller.

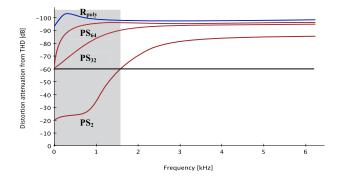

In order to fulfill the accuracy requirements for the system, we need to satisfy the total harmonic distortion (THD) criteria at the whole frequency range. For a typical 8-bit accuracy case, it is necessary to keep at least the -60 dB level (Fig. 8).

# A. Gated Pseudo-Resistance

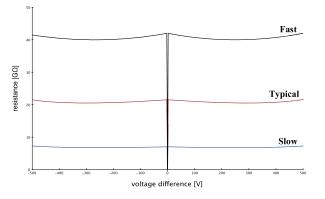

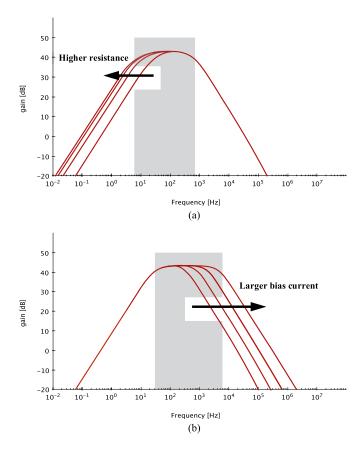

The resistance control is another important aspect in the design, because of the high parameter variation in a corner situation (Fig. 9) and the ability to tune the band pass

Fig. 8. THD of the capacitive feedback amplifier with different resistor implementation showing the constraint for a typical -60 dB system.

Fig. 9.  $PS_{32}$  Resistance variation in different corners, caused by the temperature and supply voltage variation.

Fig. 10. Gated pseudo-resistance schematic.

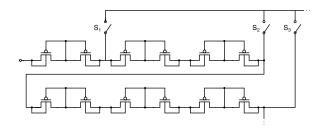

frequencies. It is possible to give controllability to the resistance if we use switches to shortcut the remaining part of the chain (Fig. 10). The overall resistance of this gated structure needs to be designed at least with the required maximal resistance plus the slow corner deviation. The large number of the series connected pseudo resistor does not have large area overhead neither the additional parasitic capacitances.

The switch implementation needs careful design as well. Large open state impedance is required so that they could be commensurable to the pseudo-resistances, otherwise the leakage will reduce the overall resistance; hence they must be optimized to the OFF resistance oppositely the general usage.

Another issue is how to scale the different segments in the resistor chain. It is not effective to use identical number of resistors in each segment if we want to tune and compensate with the same chain (Fig. 11), because the tuning and the compensation need different size of variation. The exact

Fig. 11. (a) Transfer function at different  $f_L$ . (b) Transfer function at different  $f_H$ .

choice of distribution (linear, exponential, or binary weighted) depends on the required cut-off frequencies and the degree of the corner deviations.

Finally, we achieved a programmable solution that helps us to increase the robustness against the technology parameter variation, to reduce the distortion and gives us the possibility to set the cut-off frequency.

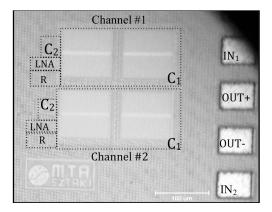

#### V. MEASUREMENTS

In order to prove the theory and verify simulations we designed the architecture with 32 pseudo-resistors chain and a low power LNA. The targeted technology was the TSMC 90 nm LP-RF [29]. A micro-photo can be seen of the two amplifiers in Fig. 13.

The in vivo experiments were approved by the Animal Care Committee of the Institute of Cognitive Neuroscience and Psychology, Research Centre for Natural Sciences, Hungarian Academy of Sciences, Budapest, Hungary. For the in vivo experiments we used Wistar rats (weight of 250-350 g, n = 3). Initial anesthesia was achieved by intramuscular injection of a mixture of 37.5 mg/ml ketamine and 5 mg/ml xylazine at 0.2 ml/100 g body weight. The temperature was maintained at 37 °C throughout the recording sessions. The anesthesia was maintained with several updates of the same drug at 0.2 ml/hour. Craniotomy was performed over the trunk region of the primary somatosensory cortex in a stereotaxic frame (David Kopf Instruments, Tujunga, CA). The target site was

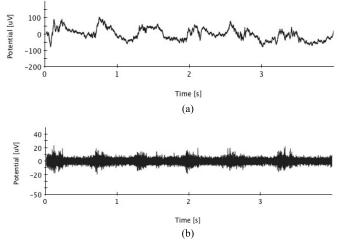

Fig. 12. (a) Recorded LFP signal (2.8 - 500 Hz band-pass). (b) Recorded MUA (500 Hz - 5 kHz band-pass).

Fig. 13. Micro-photo of two-channel amplifier.

anterior-posterior -2.7 mm and medial-lateral 2.8 mm with respect to the bregma [17]. A silicon probe [18] was attached to a manual microdrive (David Kopf Instruments, Tujunga, CA) and it was slowly (0.1 mm/sec) inserted in the trunk region. The amplifier was attached to the output leads of the silicon probe.

The outputs of the amplifier were fed into a high input impedance AD converter and digitized at 20 kHz/channel sampling rate, with 16-bit precision (PCI-6259, National Instruments, Austin, TX). The data was processed using NeuroScan Edit 4.3 software (Compumedics, El Paso, TX).

The first test was performed to deal with electrical parameters, than we made the experiment with the multi-probe electrode [18] on rodents (Fig. 12). The measured parameters are shown in Table III and IV. The different bias current implies different noise and power consumption.

As illustrated in Fig. 12, it was possible to record LFPs and MUA in the rat cortex. While the LFP is the summed synaptic activity of many neurons, the MUA shows the action potential firing of the cells close to the electrode contacts. Both signal types can be obtained from the raw data by filtering in the appropriate frequency range. Our results prove that the amplifier is functional in vivo.

TABLE III Amplifier Performance Comparison Based on the Electrical Measurements. The Simulation Results Can be Found in Parenthesis

| Parameter                                 | [5]                    | [21]     | [22]       | [27]   | [28]                 | This work               |

|-------------------------------------------|------------------------|----------|------------|--------|----------------------|-------------------------|

| Supply Voltage [V]                        | 2.5                    | 3        | 3          | 1.2    | 0.5                  | 1.2                     |

| Process Technology                        | 0.5 µm                 | 350nm    | 350nm      | 130nm  | 65nm                 | 90 nm                   |

| Midband Gain [dB]                         | 39.5                   | 37.5     | 6-47       | 40     | 40-56                | 44.1 (44)               |

| -3 dB Bandwidth                           | 7.2 kHz                | 1~10 kHz | 0.1-12 kHz | 10 kHz | 0.3~10 kHz           | 2.8 Hz~8.1(10) kHz      |

| Input Referred Noise [µV <sub>RMS</sub> ] | 2.2                    | 10.6     | 2.95       | 2.2    | 4.9                  | 5.9 (6.2)               |

| Noise Efficiency Factor                   | 4                      | 5.78     | 3.1        | 6.25   | 5.99                 | 4.9                     |

| THD [%]                                   | $1@16 \text{ mV}_{pp}$ | -        | -          | -      | $2@200 \ \mu V_{pp}$ | 0.1@10 mV <sub>pp</sub> |

| CMRR [dB]                                 | 83                     | 74       | 99         | -      | 75                   | 73 (78)                 |

| PSRR [dB]                                 | 85                     | 55       | 85         | -      | 64                   | 81 (90)                 |

| Tunable cut-off frequency                 | -                      | -        | +          | +      | +                    | +                       |

| Variable gain                             | -                      | -        | +          | -      | +/-                  | -                       |

| Power [µW]/ch.                            | 16                     | 6        | 27         | 68     | 15                   | 0.7 - 4.6               |

| Area $[mm^2]/ch$ .                        | 0.16                   | 0.058    | 0.08       | 0.013  | 0.25                 | 0.025                   |

TABLE IV DIFFERENT BIAS CURRENT INFLUENCE ON NOISE

| Current                    | Noise                                     |

|----------------------------|-------------------------------------------|

| [A]                        | [µ v <sub>RMS</sub> ]                     |

| 50n                        | 4,8                                       |

| 100n                       | 4,6                                       |

| 500n                       | 4,1                                       |

| 1 <i>u</i>                 | 3,9                                       |

| [A]<br>50n<br>100n<br>500n | [μV <sub>RMS</sub> ]<br>4,8<br>4,6<br>4,1 |

# VI. CONCLUSION

In this paper we presented a tunable low noise amplifier circuit with a low distortion pseudo-resistance chain for the battery less implantable neural recording. The basic MOS pseudo-resistance is not able to the handle the low frequency input, because the high distortion and the sensitivity for the corner situation [19]–[22], [25]–[28]. The gated chain could be an optimal solution. It gives the tuning range to decrease the corner effect and set the high-pass cutoff frequency. In summary the presented for implantable neural recording outperform the existing solutions in terms of area and linearity (Table III).

## REFERENCES

- S. Chen, B. Mulgrew, and P. M. Grant, "A clustering technique for digital communications channel equalization using radial basis function networks," *IEEE Trans. Neural Netw.*, vol. 4, no. 4, pp. 570–578, Jul. 1993.

- [2] A.-T. Avestruz, W. Santa, D. Carlson, R. Jensen, S. Stanslaski, A. Helfenstine, *et al.*, "A 5 μW/channel spectral analysis IC for chronic bidirectional brain–machine interfaces," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 3006–3024, Dec. 2008.

- [3] R. Rieger, A. Demosthenous, and J. Taylor, "A 230-nW 10-s time constant CMOS integrator for an adaptive nerve signal amplifier," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1968–1975, Nov. 2004.

- [4] K. Seidl, T. Torfs, P. A. De Mazière, G. Van Dijck, R. Csercsa, B. Dombovari, *et al.*, "Control and data acquisition software for highdensity CMOS-based microprobe arrays implementing electronic depth control," *Biomed. Tech.*, vol. 55, no. 3, pp. 183–191, 2010.

- [5] R. R. Harrison and C. Charles, "A low-power low-noise CMOS amplifier for neural recording applications," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 958–965, Jun. 2003.

- [6] F. Gozzini, G. Ferrari, and M. Sampietro, "Linear transconductor with rail-to-rail input swing for very large time constant applications," *Electron. Lett.*, vol. 42, no. 19, pp. 1069–1070, 2006.

- [7] W. Wattanapanitch, M. Fee, and R. Sarpeshkar, "An energy-efficient micropower neural recording amplifier," *IEEE Trans. Biomed. Circuits Syst.*, vol. 1, no. 2, pp. 136–147, Jun. 2007.

- [8] R. Rieger, J. Taylor, A. Demosthenous, N. Donaldson, and P. J. Langlois, "Design of a low-noise preamplifier for nerve cuff electrode recording," *IEEE J. Solid-State Circuits*, vol. 38, no. 8, pp. 1373–1379, Aug. 2003.

- [9] I. F. Triantis and A. Demosthenous, "An improved, very long timeconstant CMOS integrator for use in implantable neuroprosthetic devices," in *Proc. Eur. Conf. Circuit Theory Des.*, vol. 3. Aug./Sep. 2005, pp. III/15–III/18.

- [10] X. Zou, X. Xu, J. Tan, L. Yao, and Y. Lian, "A 1-V 1.1-μW sensor interface IC for wearable biomedical devices," in *Proc. IEEE ISCAS*, May 2008, pp. 2725–2728.

- [11] M. Yin and M. Ghovanloo, "A low-noise preamplifier with adjustable gain and bandwidth for biopotential recording applications," in *Proc. IEEE ISCAS*, May 2007, pp. 321–324.

- [12] E. Yoon and S.-I. Chang, "Low-power area-efficient analog front-end for neural interfaces," in *Proc. IEEE Circuits Syst. Med. Environ. Appl. Workshop*, Merida, Mexico, Dec. 2009, pp. 1–4.

- [13] B. Gosselin, M. Sawan, and C. A. Chapman, "A low-power integrated bioamplifier with active low-frequency suppression," *IEEE Trans. Biomed. Circuits Syst.*, vol. 1, no. 3, pp. 184–192, Sep. 2007.

- [14] M. Steyaert, P. Kinget, and W. Sansen, "Full integration of extremely large time constants in CMOS," *Electron. Lett.*, vol. 27, no. 10, pp. 790–791, May 1991.

- [15] I. F. Triantis and A. Demosthenous, "A BiCMOS ENG amplifier with high SIR output," in *Proc. IEEE ISCAS*, vol. 1. May 2005, pp. 744–747.

- [16] I. F. Triantis and A. Demosthenous, "An improved, very long timeconstant CMOS integrator for use in implantable neuroprosthetic devices," in *Proc. Eur. Conf. Circuit Theory Des.*, vol. 3. 2005, pp. III/15–III/18.

- [17] G. Paxinos and C. H. Watson, *The Rat Brain in Stereotaxic Coordinates*. San Diego, CA, USA: Academic, 1998.

- [18] L. Grand, A. Pongrácz, E. Vázsonyi, G. Márton, D. Gubán, R. Fiáth, et al., "A novel multisite silicon probe for high quality laminar neural recordings," Sens. Actuators A, Phys., vol. 166, no. 1, pp. 14–21, 2011.

- [19] J. Silva-Martinez and J. Salcedo-Suner, "IC voltage to current transducers with very small transconductance," *Analog Integr. Circuits Signal Process.*, vol. 13, no. 3, pp. 285–293, 1997.

- [20] M. Yin and M. Ghovanloo, "A low-noise preamplifier with adjustable gain and bandwidth for biopotential recording applications," in *Proc. IEEE ISCAS*, May 2007, pp. 321–324.

- [21] K. A. Ng and Y. P. Xu, "A compact, low input capacitance neural recording amplifier," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, no. 5, pp. 610–620, Oct. 2013.

- [22] A. Demosthenous, I. Pachnis, D. Jiang, and N. Donaldson, "An integrated amplifier with passive neutralization of myoelectric interference from neural recording tripoles," *IEEE Sensors J.*, vol. 13, no. 9, pp. 3236–3248, Sep. 2013.

- [23] S. Yuan, L. G. Johnson, C. C. Liu, C. Hutchens, and R. L. Rennaker, "Current biased pseudo-resistor for implantable neural signal recording applications," in *Proc. 51st MWSCAS*, Aug. 2008, pp. 658–661.

- [24] C.-H. Chan, J. Wills, J. LaCoss, J. J. Granacki, and J. Choma, "A novel variable-gain micro-power band-pass auto-zeroing CMOS amplifier," in *Proc. IEEE ISCAS*, May 2007, pp. 337–340.

- [25] B. K. Thurgood, D. J. Warren, N. M. Ledbetter, G. A. Clark, and R. R. Harrison, "A wireless integrated circuit for 100-channel chargebalanced neural stimulation," *IEEE Trans. Biomed. Circuits Syst.*, vol. 3, no. 6, pp. 405–414, Dec. 2009.

- [26] X. Zou, X. Xu, L. Yao, and Y. Lian, "A 1-V 450-nW fully integrated programmable biomedical sensor interface chip," *IEEE J. Solid-State Circuits*, vol. 44, no. 4, pp. 1067–1077, Apr. 2009.

- [27] R. M. Walker, H. Gao, P. Nuyujukian, K. Makinwa, K. V. Shenoy, T. Meng, *et al.*, "A 96-chanell full data rate direct neural interface in 0.13 μm CMOS," in *Proc. IEEE Symp VLSI Circuits*, Jun. 2011, pp. 144–145.

- [28] R. Muller, S. Gambini, and J. Rabay, "A 0.013 mm<sup>2</sup> 5 μW DC-coupled neural signal acquisition IC with 0.5 V supply," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2011, pp. 302–304.

- [29] (2011). Low-Power RF Process [Online]. Available: http://www. tsmc.com/english/dedicatedFoundry/technology/90nm.htm

physiology of sleep.

**Péter Földesy** received the M.S. and Ph.D. degrees (Hons.) from the Budapest University of Technology and Economics, Budapest, Hungary, in 1995 and 2002, respectively, all in electrical engineering. Since 2007, he has been with Pazmany Peter Catholic University, Faculty of Information Technology, Budapest, where he is currently an Assistant Professor. He has held research positions at the Institute for Computer Science and Control, Hungarian Academy of Sciences from 1996 to 2013 and the Research Centre for Natural Sciences, Institute for

Richárd Fiáth received the M.S. degree in computer

engineering from Pazmany Peter Catholic Univer-

sity, Faculty of Information Technology, Budapest, Hungary, in 2009. Since 2009, he has been pursuing

the Ph.D. degree at the Szentagothai Janos Doctoral School of Neurosciences, Semmelweis University,

Budapest, and performs research at the Institute of Cognitive Neuroscience and Psychology, Research

Centre for Natural Sciences, Hungarian Academy

of Sciences, Budapest. His main interests are the

investigation of thalamocortical oscillations and the

Technical Physics and Materials Science, Budapest, in 2013, as a Senior Research Fellow. His research interests include integrated vision sensors, THz imaging and technology, and smart sensor design.

**Zoltán Kárász** was born in Budapest, Hungary, on January 20, 1984. He received the Engineer's degree in information technology engineering from Pazmany Peter Catholic University, Budapest, in 2008. He is currently pursuing the Doctoral degree. He is a Young Researcher with the Institute for Computer Science and Control, Hungarian Academy of Sciences, in 2008. His main research interest is in the design of integrated low-noise amplifiers for biomedical research.

Ángel Rodríguez Vázquez is currently a Full Professor of electronics with the University of Seville, Seville, Spain, and is appointed for research at the Institute of Microelectronics of Seville, Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Cientficas-University of Seville. He has authored eight books; over 50 chapters in edited books, including original tutorials on chaotic integrated circuits, design of data converters, and design of chips for vision; and some 500 articles in peerreviewed specialized publications. His research work

is widely quoted, and he has an h-index of 35. His current research interests are in the areas of imagers and vision systems using 3-D integration technologies and of ultra-low-power medical electronic devices.