# NON-IDEAL QUANTIZATION NOISE SHAPING IN SWITCHED-CURRENT BANDPASS $\Sigma\Delta$ MODULATORS

J.M. de la Rosa, B. Pérez-Verdú, F. Medeiro, R. del Río and A. Rodríguez-Vázquez (IEEE Fellow)

Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC) Edificio CICA-CNM, C/Tarfia s/n, 41012-Sevilla, SPAIN Phone: +34 95 4239923; FAX: +34 95 4231832 E-mail: jrosa@imse.cnm.es

### **ABSTRACT**

This paper presents a systematic analysis of the major switched-current (SI) errors and their influence on the quantization noise shaping of SI BandPass  $\Sigma\Delta$  Modulators (BP $\Sigma\Delta$ Ms). Closed form equations are provided for the degradation of the signal-to-noise ratio and for the change of the *notch* frequency position in order to facilitate the design of this class of modulators. All these results have been validated by non-ideal time-domain behavioral simulations. (\*)

#### 1. INTRODUCTION

A wide variety of CMOS analog sampled-data  $\Sigma\Delta$ -modulators ( $\Sigma\Delta$ Ms) have been reported in literature for applications ranging from instrumentation to telecom [1]. Most of them use switched-capacitor (SC) circuits. However, the trend towards the combination of analog and digital circuitry in mixed-signal chips with low production cost has motivated exploring design techniques such as switched-current (SI), which can be manufactured in standard VLSI single-poly technologies with no extra processing steps required [2]. Several SI lowpass  $\Sigma\Delta$ M ICs for different applications have already been reported [3][4]. Recently, we have also reported a SI BP $\Sigma\Delta$ M realized in a single-poly 0.8  $\mu$ m CMOS technology [5].

Unlike SC  $\Sigma\Delta Ms$ , whose non-idealities have been described and modeled [1], thus allowing generation of systematic top-down design methodologies [6][7], until now there is not such equivalent study for SI  $\Sigma\Delta Ms$ . This paper presents a systematic analysis of the major SI error mechanisms which degrade the quantization noise shaping of 4th-order BP $\Sigma\Delta Ms$ . The aim of this study is to identify the influence of each error and to provide equations which facilitate the design of this class of modulators.

## 2. QUANTIZATION NOISE SHAPING IN BANDPASS $\Sigma\Delta$ MODULATORS

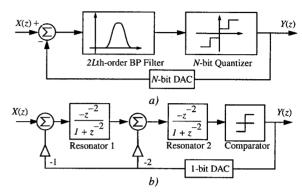

Fig.1(a) shows the block diagram of a single-loop BP $\Sigma\Delta M$ . Assuming that the quantizer can be modeled as an additive, white noise source, the z-transform of the modulator output can be expressed as follows:

$$Y(z) = S_{TF}(z)X(z) + N_{TF}(z)E(z)$$

(1)

where X(z) is the input signal and E(z) represents the quantization error. Typically, BP $\Sigma\Delta M$  architectures are obtained from the corresponding lowpass prototypes by applying a  $z^{-1} \rightarrow -z^{-2}$  transformation; this keeps the stability properties of the original architecture and allows us to take advantage of the available knowledge on the properties of lowpass modulators [1]. Thus, the ideal quantization Noise Transfer Function ( $N_{TF}$ ) is of the bandstop

(\*)This work has been supported by the Spanish CICYT Project TIC 97-0580

**Figure 1.** Conceptual Block Diagram of a BandPass  $\Sigma\Delta$  Modulator, a) *N*-bit 2*L*th-Order. b) 1-bit 4th-Order.

type,

$$N_{TF}(z) = (1 + z^{-2})^{L} (2)$$

where 2L is the loop order. This latter function has L transmission zeroes at  $f_s/4$ , where  $f_s$  stands for the sampling frequency.

Assuming that the *N*-bit quantizer in Fig.1(a) has a quantization step equal to q, its quantization noise power spectral density is  $N_Q = q^2/(12f_s)$ . As a consequence of the noise shaping, the in-band quantization noise power results in

$$P_{Q} = \int_{f_{s}/4 - B_{W}/2}^{f_{s}/4 + B_{W}/2} 2N_{Q} |N_{TF}(f)|^{2} df \approx \frac{\left[\Delta/(2^{N} - 1)\right]^{2} \pi^{2L}}{12(2L + 1)M^{2L + 1}}$$

(3)

where  $\Delta$  represents full-scale range of the quantizer; i.e.  $\Delta = q(2^N - 1)$ ,  $B_W$  is the signal bandwidth and  $M \equiv f_s/(2B_W)$  is the oversampling ratio.

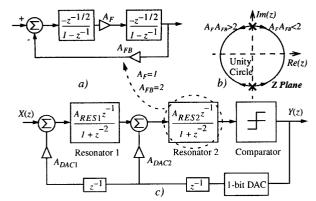

This paper focuses on 1-bit (N=1) modulators with L=2. These modulators are easy to understand and relatively simple to design. They are capable to provide high resolution together with large tolerance to imperfections and robust, stable operation. Thus, we will start from a 2nd-order lowpass modulator, which after the  $z^{-1} \rightarrow -z^{-2}$  transformation, results in the associated bandpass architecture shown in Fig.1(b). The *resonator* in Fig.1(b) can be realized using different alternatives [8]. Fig.2(a) shows one based on two LDI integrators in a feedback loop. This implementation is adopted because it remains stable under changes of the feedback coefficient due to circuit parasitics. Fig.2(b) illustrates this by plotting the movement of the resonator poles due to changes of the scaling coefficient  $A_F A_{FB}$  around its nominal value of 2. It can be seen that they remain at the unity circle.

Fig.2(c) shows the architecture of a 4th-order bandpass  $\Sigma\Delta$

Figure 2. a) LDI Loop Resonator. b) Movement of Poles Around the Unity Circle Due to Changes in the Feedback Gain. c) Block Diagram of a BPΣΔM Based on the Resonator of Fig.2(a).

modulator based on the resonator of Fig.2(a). The scaling factors have been optimized to obtain similar dynamic range for both resonators [5], giving  $A_{RES2} = A_{DAC2} = -A_{DAC1} = 1$  and  $A_{RES1} = 1/2$ .

By making N=1 and L=2 in (3), we obtain the quantization noise power  $P_Q$  for this modulator. On the other hand, assuming that the input signal of the modulator is a sinewave of amplitude  $A \le \Delta/2$ , we obtain the following expressions for the Signal-to-Noise Ratio (SNR) and the Dynamic Range (DR) [1]

$$SNR = \frac{A^2}{2P_O} = \frac{15M^5}{2\pi^4} \left(\frac{2A}{\Delta}\right)^2 \qquad DR = \frac{(\Delta/2)^2}{2P_O} = \frac{15M^5}{2\pi^4}$$

(4)

as it can be derived from (4), the resolution of this modulator increases with M at a rate of about 2.5 bits per octave. However, as we will see in the following section, error sources in practical SI circuits cause the quantization noise to increase in the signal band, thus lowering the reached resolution.

## 3. SI BUILDING BLOCKS AND ASOCIATED ERRORS

As shown in [2], the major error sources of the memory cell are: finite drain conductance, incomplete settling, and switch charge injection. Their isolated influence on the memory cell and on the integrator transfer function were analysed in [2]. However, for our study we are interested on their cumulative influence on the degradation of the quantization noise shaping in BP $\Sigma\Delta$ Ms.

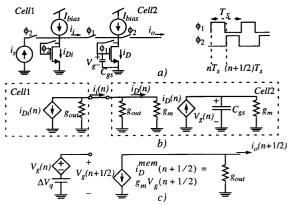

Consider the cascaded memory cells shown in Fig.3(a). During clock phase  $\phi_1$ , *Cell*1 is in hold mode while *Cell*2 is in sampling mode. The small-signal equivalent circuit for such a configuration is shown in Fig.3 (b). The stationary current of the memory transistor in *Cell*2,  $i_D(n)$ , is given by

$$i_D(n) = -(1 - \varepsilon_g)i_{Di}(n) \tag{5}$$

where  $\varepsilon_g=2g_{out}/g_m$ , with  $g_m$  and  $g_{out}$  being the small-signal input and output conductance of *Cell2*, respectively. Expression (5) is also valid for other memory cells by substituting  $g_m$  by the corresponding input transconductance. However, it applies only if the memory cell reaches the steady state before the end of the sampling phase. Otherwise, an additional error is generated as a consequence of the incomplete settling of the voltage at the gate of the memory

**Figure 3.** a) Cascaded Memory Cells and Clock Phases. b) Equivalent Circuit During Phase  $\phi_1$  and c) During Phase  $\phi_2$ .

transistor. Solving the equivalent circuit of Fig.3(b) for  $V_g$  with  $V_g(n-1)=i_D^{mem}(n-1)/g_m$  as the initial condition of the gate-source capacitor  $C_{gg}$  yields

$$V_{g}(n) = [(1 - \varepsilon_{s})i_{D}(n) + \varepsilon_{s}i_{D}^{mem}(n-1)]/g_{m}$$

(6)

where  $\varepsilon_s = \exp[-T_s g_m/(2C_{gs})]$  stands for the incomplete settling error and  $i_D^{mem}(\dot{n}-1)$  represents the memorized drain current in the previous sampling phase. When the memory switch opens, in the beginning of phase  $\phi_2$ , the charge injected by the switch transistor in  $C_{gs}$  introduces an additional error term  $(\Delta V_q)[2]$ , so that

$$V_g(n+1/2) = V_g(n) + \Delta V_q = (1 - \varepsilon_q)V_g(n)$$

(7)

Fig.3(c) shows the equivalent circuit for the *Cell*2 in the hold mode. Considering all errors above, the z-transform of  $i_D^{mem}$  is

$$i_{D}^{mem}(z) = \frac{-(1 - \epsilon_g)(1 - \epsilon_q)(1 - \epsilon_s)z^{-1/2}i_{Di}(z)}{1 - \epsilon_s(1 - \epsilon_q)z^{-1}} \tag{8}$$

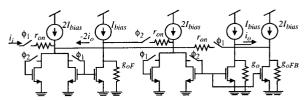

Let consider now the conceptual SI realization of the *resonator* block of Fig.2(a) shown in Fig.4. In addition to the memory cell errors ( $\varepsilon_g$ ,  $\varepsilon_q$  and  $\varepsilon_s$ ), there are some errors due to non-idealities in the connection of the integrators. We define these errors as follows:

$$\varepsilon_{F,FB} = r_{on}g_{oF,FB}; \varepsilon_{g_{F,FB}} = (g_{oF,FB}/g_m)(1 - \varepsilon_{F,FB}) \quad (9)$$

where  $r_{on}$  is the steering switch on-resistance and  $g_{oF}$ ,  $g_{oFB}$  are the output conductances of the current mirrors, as stated in Fig.4. Using the equivalent circuit shown in Fig.3 for the memory cells which form the integrators, the following transfer function is obtained for the non-ideal resonator:

Figure 4. Schematic of the Resonator Including SI Errors.

$$H_{res}^{err}(z) \cong \frac{(1-\mu_1)z^{-1} + \mu_2 z^{-2}}{1+\xi_1 z^{-1} + (1-\xi_2)z^{-2}}$$

(10)

where

$$\mu_{1} = 2\varepsilon_{F} + 2\varepsilon_{s} + 2\varepsilon_{g} + 2\varepsilon_{q} + \varepsilon_{g_{F}}; \mu_{2} = -2\varepsilon_{s}$$

$$\xi_{1} = -(2\varepsilon_{F} + 2\varepsilon_{FB} + 4\varepsilon_{s} + \varepsilon_{g_{F}} + \varepsilon_{g_{FB}})$$

$$\xi_{2} = 4\varepsilon_{s} + 4\varepsilon_{g} + 4\varepsilon_{q} + \varepsilon_{g_{F}} + \varepsilon_{g_{FB}}$$

(11)

### 4. NON-IDEAL QUANTIZATION NOISE SHAPING

Substituting (10) in the transfer function of the resonator in Fig.2(c), the erroneous quantization noise transfer function  $N_{TF}^{err}$  is approximately given by

$$N_{TF}^{err}(z) \cong \frac{\left[1 + \xi_1 z^{-1} + (1 - \xi_2) z^{-2}\right]^2}{1 + 2\xi_1 z^{-1} + \left[\xi_1^2 - 2(\xi_2 - \mu_1)\right] z^{-2}}$$

(12)

As (12) shows, the zeroes of  $N_{TF}^{err}$  are shifted from their nominal positions at  $f_s/4$ , thus degrading the filtering performed by the resonators and making the quantization noise floor to increase in the signal band, and correspondingly, the *SNR* to decrease.

We can group the mentioned errors in three different families attending to the way they degrade the zeroes of  $N_{TF}^{err}(z)$ , which map into different increases of the quantization noise power  $P_Q$ . Table I shows the non-ideal quantization noise power for each family of errors. This table provides insight on the influence of each error source. Assuming typical variations of the error parameters between 0.1% and 1%, several conclusions are drawn from (12) and Table I:

- •The only effect of errors  $\varepsilon_g$  and  $\varepsilon_q$ , denoted by parameter  $\varepsilon_\alpha$  in Table I, consists in reducing the Q-factor of the resonator transfer function, thus lowering the bandstop attenuation of the modulator bandpass filtering. For these errors, the deviation in the quantization noise power is dominated by the term  $(\varepsilon_\alpha M)^2$  up to  $\varepsilon_\alpha M \approx 0.6$ ; beyond this limit the term  $(\varepsilon_\alpha M)^4$  dominates, thus practically destroying all the benefits of the oversampling.

- •The errors  $\epsilon_F$  and  $\epsilon_{FB}$ , represented by parameter  $\epsilon_{\beta}$  in Table I, just change the position of signal band center frequency, often called *notch* frequency. However, the quantization noise power does not significantly increase. For this family of errors, the term  $(\epsilon_{\beta} M)^2$  dominates up to  $\epsilon_{\beta} M \approx 2.2$ .

- •The errors  $\varepsilon_s$  and  $\varepsilon_{gF}$ ,  $\varepsilon_{gFB}$ , represented through parameters  $\varepsilon_{\gamma 1}$  and  $\varepsilon_{\gamma 2}$ , respectively in Table I, degrade the position of the

Table I: Non-Ideal Quantization Noise Power

| Error                                               | Quantization Noise Power, $P_Q$                                                                                                                                                                                     |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\varepsilon_{\alpha} = \varepsilon_{g, q}$         | $P_Q^{\alpha} = \frac{\pi^4 \Delta^2}{60M^5} \left[ 1 + \frac{160}{3} \left( \frac{\varepsilon_{\alpha} M}{\pi} \right)^2 + 1280 \left( \frac{\varepsilon_{\alpha} M}{\pi} \right)^4 \right]$                       |

| $\varepsilon_{\beta} = \varepsilon_{F, FB}$         | $P_Q^{\beta} = \frac{\pi^4 \Delta^2}{60M^5} \left[ 1 + 40 \left( \frac{\varepsilon_{\beta} M}{\pi} \right)^2 + 80 \left( \frac{\varepsilon_{\beta} M}{\pi} \right)^4 \right]$                                       |

| $ \varepsilon_{\gamma_1} = \varepsilon_s $          | $P_Q^{\gamma_1} = \frac{\pi^4 \Delta^2}{60M^5} \left[ 1 + \frac{640}{3} \left( \frac{\varepsilon_{\gamma_1} M}{\pi} \right)^2 + 5120 \left( \frac{\varepsilon_{\gamma_1} M}{\pi} \right)^4 \right]$                 |

| $ \varepsilon_{\gamma_2} = \varepsilon_{g_{F,FB}} $ | $P_{Q}^{\gamma_{2}} = \frac{\pi^{4} \Delta^{2}}{60 M^{5}} \left[ 1 + \frac{40}{3} \left( \frac{\varepsilon_{\gamma_{2}} M}{\pi} \right)^{2} + 20 \left( \frac{\varepsilon_{\gamma_{2}} M}{\pi} \right)^{4} \right]$ |

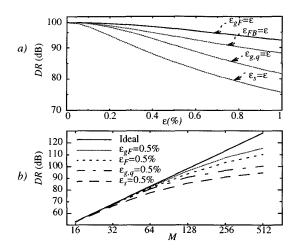

**Figure 5.** DR Degradation with Errors. a) DR vs. Error for M = 128. b) DR vs. M for Error Equal to 0.5%.

notch frequency and increase the quantization noise power in the signal band. For  $\varepsilon_s$ , the term  $(\varepsilon_{\gamma_1} M)^2$  dominates up to  $\varepsilon_{\gamma_1} M \approx 0.6$ , while for  $\varepsilon_{gF}$ ,  $(\varepsilon_{\gamma_2} M)^2$  dominates up to  $\varepsilon_{\gamma_2} M \approx 2.6$ .

•For similar values of parameters  $\varepsilon_{\alpha}$ ,  $\varepsilon_{\beta}$ ,  $\varepsilon_{\gamma 1}$  and  $\varepsilon_{\gamma 2}$ , the settling error produces larger deviations in the noise transfer function than the rest of errors - illustrated in Fig.5(a). This forces using larger oversampling ratios to achieve the ideal *SNR* level as is shown in Fig.5(b) by plotting *DR* degraded by the different errors as a function of *M*.

Other scaling errors are found at the modulator level. However, they do not influence the resonator transfer function but the resonator and DAC gains. For typical values of these errors (1%), the increase in the quantization noise power is negligible.

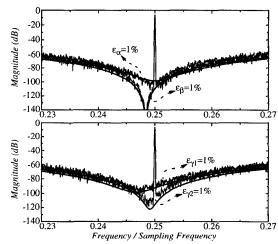

All these results have been validated by simulation using a time-domain SI behavioral simulator [9]. As an illustration, Fig.6 shows several simulated modulator output spectra obtained for a sinusoidal input signal of amplitude  $A = \Delta/4$  and centered at

Figure 6. Influence of Different SI Errors on  $N_{TF}$

$f_s/4$ . This figure compares the degradation of  $N_{TF}$  in the presence of  $\varepsilon_{g,q}$ ,  $\varepsilon_{FB}$ ,  $\varepsilon_s$ , and  $\varepsilon_{gF}$ , obtained with the theoretical model (solid line) with that obtained through simulation. A good agreement can be observed between both approaches.

# 5. GUIDELINES FOR THE DESIGN OF SI 4th-ORDER BANDPASS $\Sigma\Delta$ MODULATORS

In practical applications, the designer should consider the cumulative influence of errors on the modulator performance. From (3) and (12), the quantization noise power degraded by all errors can be derived as follows

$$P_Q^{err} = \frac{\pi^4 \Delta^2}{60 M^5} \left[ 1 + \frac{10}{3} (3\xi_1^2 + \xi_2^2) \left( \frac{M}{\pi} \right)^2 + 5(\xi_1^2 + \xi_2^2)^2 \left( \frac{M}{\pi} \right)^4 \right]$$

(13)

Making all errors equal to an error bound named  $\varepsilon$  the following quantization noise power is obtained

$$P_Q^{err} = \frac{\pi^4 \Delta^2}{60M^5} \left[ 1 + k_1 \varepsilon^2 \left( \frac{M}{\pi} \right)^2 + k_2 \varepsilon^4 \left( \frac{M}{\pi} \right)^4 \right]$$

(14)

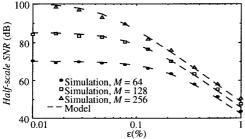

where  $k_1=4960/3$  and  $k_2=438080$ . This equation allows us to express the quantization noise power degradation in terms of  $\varepsilon$ . Thus, forcing all SI errors in the modulator to be smaller than  $\varepsilon$  bounds the quantization noise power with (14). Fig.7 plots the half-scale SNR (obtained for a sinusoidal input signal of amplitude  $A=\Delta/4$ ) as a function of  $\varepsilon$ , for M=64, M=128 and M=256. Simulation results match very well with the data calculated from (14).

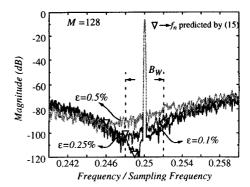

In BP $\Sigma\Delta$ Ms, the control of the *notch* frequency ( $f_n$ ) position is also critical. In practice, this frequency is fixed by the system requirements, so that its position should not be significantly shifted from  $f_s/4$ . We can derive  $f_n$  by solving (12) for the frequency of the zeroes. Assuming that  $\xi_1, \xi_2 \ll 1$  the error in  $f_n$ , denoted as  $\delta f_n$ , is given by

$$\delta f_n = f_n - \frac{f_s}{4} \cong \xi_1 \frac{M}{\pi} \left( \frac{B_W}{2} \right) \tag{15}$$

From (11) it is seen that  $\xi_1 \leq 0$  and therefore  $f_n \leq f_s/4$  for all SI BP $\Sigma\Delta Ms$ . On the other hand, considering that the quantization noise power is minimum at  $f_n$ , we can define a maximum error  $\left|\delta f_{n_{max}}\right| \leq B_W/2$ . From (15) and assuming all SI errors to be equal to  $\varepsilon$ , this condition is satisfied if  $\varepsilon \leq \pi/(10M)$ . For instance, if M=128, it obtains  $\varepsilon \leq 0.25$ %. Fig.8 illustrates this by plotting three output spectra corresponding to different values of  $\varepsilon$ . It is seen that the predictions of (15) agrees with simulation data.

Figure 7. SNR Degradation vs.  $\varepsilon$  for an Input Signal of  $\Delta/4$  Amplitude. M = 64, M = 128, M = 256.

Figure 8. Notch Frequency Degradation with SI Errors.

#### 6. CONCLUSIONS

The study presented in this paper classifies the SI non-idealities attending to the way they degrade the quantization noise shaping in bandpass  $\Sigma\Delta$  modulators. Closed-form equations have been derived for the influence of SI errors on the modulator performance. As a result of such an analysis, some practical guidelines for the design of BP $\Sigma\Delta$ Ms using SI circuits are given. This approach has been validated by detailed time domain behavioral simulation.

#### REFERENCES

- [1] S.R. Norsworthy, R. Schreier, G.C. Temes (editors), Delta-Sigma Converters. Theory, Design and Simulation. New York, IEEE Press, 1997.

- [2] C.Toumazou, J.B.Hughes, and N.C. Battersby (editors), Switched-Currents: An Analogue Technique for digital technology, London, Peter Peregrinus Ltd.,1993.

- [3] N. Tan and S. Eriksson, "A Low-Voltage Switched- Current Delta-Sigma Modulator", *IEEE Journal of Solid-State Circuits*, pp. 599-603, May 1995.

- [4] N. Moeneclaey and A. Kaiser, "Design Techniques for High-Resolution Current-Mode Sigma-Delta Modulators", IEEE Journal of Solid-State Circuits, pp. 953-958, July 1997.

- [5] J.M. de la Rosa, B. Pérez-Verdú, F. Medeiro and A. Rodríguez-Vázquez, "A 2.5MHz 55dB Switched- Current BandPass ΣΔ Modulator for AM Signal Conversion", Proc. of the 1997 European Solid-State Circuits Conference, pp. 156-159, 1997.

- [6] B. Boser and B.A. Wooley, "The Design of Sigma-Delta Modulation Analog-to-Digital Converters", *IEEE Journal of Solid-State Circuits*, pp.1298-1308, December 1988.

- [7] F. Medeiro, B. Pérez-Verdú and A. Rodríguez-Vázquez, Top-down Design of High-Performance Sigma-Delta Modulators, Kluwer Academic Publishers, 1998.

- [8] F.W. Singor and W. M. Snelgrove, "Switched-Capacitor Bandpass Delta-Sigma A/D Modulation at 10.7 MHz", *IEEE Journal of Solid-State Circuits*, pp. 184-192, March 1995.

- [9] J.M. de la Rosa, A. Kaiser and B. Pérez-Verdú, "Interactive Verification of Switched-Current Sigma- Delta Modulators", Proc. of 1998 IEEE International Conference on Electronics, Circuits and Systems, pp. 2.157-2.160, 1998.