Hindawi Publishing Corporation Active and Passive Electronic Components Volume 2016, Article ID 8351406, 10 pages http://dx.doi.org/10.1155/2016/8351406

# Research Article

# **Energy-Aware Low-Power CMOS LNA with Process-Variations Management**

# Jorge Luis González, 1 Robson Luiz Moreno, 2 Juan Carlos Cruz, 1 and Diego Vázquez 3

<sup>1</sup>Centro de Investigaciones en Microelectrónica (CIME-CUJAE), Antigua Carretera de Vento, km 8, Capdevila, Boyeros, 10800 Havana, Cuba

<sup>2</sup>Universidade Federal de Itajubá (UNIFEI), Avenida BPS 1303, Bairro Pinheirinho, Caixa Postal 50, 37500 903 Itajubá, MG, Brazil

<sup>3</sup>Instituto de Microelectrónica de Sevilla (IMSE-CNM-CSIC), Parque Científico y Tecnológico Cartuja,

Calle Américo Vespucio s/n, 41092 Sevilla, Spain

Correspondence should be addressed to Jorge Luis González; jorgeluis.gr@electrica.cujae.edu.cu

Received 22 November 2015; Revised 18 January 2016; Accepted 20 January 2016

Academic Editor: Ching Liang Dai

Copyright © 2016 Jorge Luis González et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

A reconfigurable low-noise amplifier (LNA) with digitally controllable gain and power consumption is presented. This architecture allows increasing power consumption only when required, that is, to improve LNA's radiofrequency performance at extreme communication-channel conditions and/or to counteract the effect of process, voltage, and temperature variations. The proposed design leads to significant power saving when a relaxed operation is acceptable. The LNA is implemented in a 130 nm 1.2 V CMOS technology for a 2.4 GHz IEEE-802.15.4 application. Simulated LNA performance (taking into account the worst cases under process variations) is comparable to recently published works.

#### 1. Introduction

A system with multiple operation modes, able to adapt its performance dynamically depending on working conditions, can be implemented using reconfigurable circuits. Modes with relaxed requirements can be designed to operate at lower biasing current and/or voltage, leading to an overall decrease in power consumption compared to conventional fixed circuits. This power-saving approach has been applied in the following two scenarios: (1) to mitigate the effects of process variations (improving yield and reliability) [1-3] and (2) to implement wireless-receiver blocks which adjust their power consumption depending on communication-channel conditions (energy-aware receivers) [4-7]. Combining both features in an integrated receiver circuit shows up as a very attractive design goal, due to the growing demand and mass production of low-power wireless devices. However, such a solution has not been already reported.

In the receiver context, especially in fully integrated implementation scenarios, the low-noise amplifier (LNA) is

a key block that determines the overall system performance [8]. It has to offer, simultaneously, good input matching, low-noise contribution, high linearity, and high reverse isolation, constrained by power consumption. In addition, its gain is crucial and represents a trade-off between receiver's noise and linearity performances [8, 9]. In this sense, adjusting RF parameters of the LNA, especially gain, by controlling the biasing of amplifying-stage transistors, has been used to allow power-consumption saving under relaxed communication-channel conditions [6, 7, 10].

On the other hand, adaptability has been also used to mitigate the effects of process variations on CMOS-LNAs [3, 11–15]. The proposal presented by González et al. [3] shows the potentials of an adaptable LNA to save power when its behavior under process variations remains close to the typical-case performance. However, the reported solutions focus on calibrating fixed-gain LNAs; thus, they do not exploit the advantages of variable-gain schemes.

This work presents a reconfigurable LNA capable of adjusting its power consumption taking into account

communication-channel conditions and the effects of process, supply-voltage, and temperature variations. This energy-aware LNA uses architecture with digitally controllable gain and power consumption. The proposed power-saving strategy is corroborated by implementing a 130 nm 1.2 V CMOS LNA for a 2.4 GHz IEEE-802.15.4 application. LNA behavior under process variations is analyzed via Monte Carlo simulations, the results of which are used to evaluate the corresponding receiver performance.

This paper is organized as follows. Section 2 summarizes the main equations that support the ideas followed in this work, from a system-level point of view. Section 3 describes the reconfigurable architecture and the proposed powersaving strategy as a function of communication-channel conditions and the effects of process variations. Section 4 presents the main implementation details and discusses simulation results, including the comparison with other LNAs for IEEE-802.15.4 receivers. Finally, conclusions are given in Section 5.

## 2. A System-Level Overview

The working principle of an energy-aware receiver relies on the fact that noise figure (NF) and linearity requirements depend on the received input-signal level. This can be understood by examining the following expressions [16]:

$$NF \le P - 10\log(kTB) - SNR_{\min},\tag{1}$$

$$IIP_3 \ge \frac{3P_{interf} - P + SNR_{min}}{2},\tag{2}$$

$$IIP_3 \ge P + 10 \, dB. \tag{3}$$

In the above equations, NF is the noise figure, P is the inputsignal power, k is the Boltzmann constant, T is the absolute temperature, B is the channel bandwidth, SNR<sub>min</sub> is the minimum signal-to-noise ratio required by the application (including some design margin which accounts for losses that are not certainly determined at system-level design time), IIP<sub>3</sub> is the input-referred third-order intermodulation intercept point, and  $P_{\text{interf}}$  is the power of interferer signals. All the magnitude values are expressed in logarithmic units (dB or dBm), with the exception of kTB product. Equation (3) derives from the general assumption that considers the 1 dB compression point (CP<sub>1dB</sub>) as the upper limit of input power [17] and from the approximate relationship CP<sub>1dB</sub> = IIP<sub>3</sub> – 10 dB [8], in order to use IIP<sub>3</sub> as the only linearity measurement.

It can be seen from (1) that NF can be relaxed as inputsignal power increases. On the other hand, IIP<sub>3</sub> has two critical values: one required to detect a weak desired signal in the presence of interferers (see (2)) and the other required to drive the maximum signal level (see (3)). However, linearity requirement of the receiver can be lessened at intermediate signal levels. This can be exploited for saving energy by implementing a reconfigurable circuit with multiple operation modes (i.e., with different values of NF and IIP<sub>3</sub>), taking into account the fact that more relaxed NF and IIP<sub>3</sub> can be achieved with lower power consumption [19]. The aforementioned approach contrasts with the use of traditional circuits, which must be designed to work at worst-case conditions, thus requiring higher and fixed power consumption.

2.1. LNA in the Receiver Context. Receiver parameters ( $F_{\rm Rx}$ , IIP $_{\rm 3Rx}$ ) can be related to those of the LNA ( $G_{\rm LNA}$ ,  $F_{\rm LNA}$ , and IIP $_{\rm 3LNA}$ ) and the other building blocks ( $F_{\rm fs}$ , IIP $_{\rm 3fs}$ , where subscript "fs" stands for "following stages," i.e., from mixer input to A/D output) using cascaded-stages equations (4) [8]. Hence,

$$F_{\rm Rx} = F_{\rm LNA} + \frac{F_{\rm fs} - 1}{G_{\rm LNA}},$$

$$\frac{1}{\rm IIP_{\rm 3Rx}} = \frac{1}{\rm IIP_{\rm 3LNA}} + \frac{G_{\rm LNA}}{\rm IIP_{\rm 3fs}}.$$

(4)

In the above equations, F is the noise factor, such as NF =  $10 \log F$ , while gain and IIP<sub>3</sub> are expressed in "times" (W/W) and W (or mW), respectively.

Controlling LNA parameters, particularly gain, allows adjusting the noise figure and linearity of the receiver. The LNA should provide high gain and low-noise figure to guarantee the required noise figure of the receiver for detecting the minimum input-signal level. However, LNA gain can be reduced as the NF of the receiver can be relaxed, when receiving higher input-signal levels. LNA gain reduction also allows lowering the linearity of the LNA and the subsequent stages, without affecting the receiver linearity required to drive large input-signal power. Therefore, it is convenient to design adaptable LNAs, with the capability of switching between high and low gain modes [20, 21].

When needed, gain can be lowered by reducing the transconductance of amplifying-stage transistors, which in fact allows for power-consumption saving [6, 7, 10]. However, changing the DC operation point affects other RF parameters, thus limiting the gain variation rate. Therefore, the inclusion of extra DC-invariant gain-controlling methods could be useful, for example, to compensate for linearity degradation, as it is shown here.

#### 3. The Proposed Energy-Aware LNA

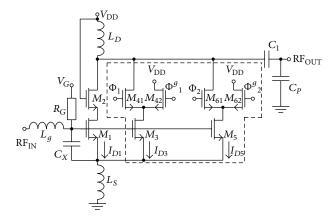

Based on the widely used inductively degenerated commonsource topology, Figure 1 shows the proposed reconfigurable LNA implementing the above ideas. This is an improved proposal with respect to that presented at [3], where only worst-case process variations were dealt with.

Gain and power consumption are digitally controlled through inputs  $\Phi_{1,2}$  and  $\Phi_{1,2}^g$ . Controllability is introduced by connecting two extra branches in parallel with the traditional cascode configuration ( $M_1$  and  $M_2$ ). Each branch comprises a transconductance stage ( $M_3$  and  $M_5$ ) and a cascode pair acting as a current switch ( $M_{41}/M_{61}$ , connected to signal output, and  $M_{42}/M_{62}$ , connected to  $V_{\rm DD}$  as a signal-dumping path). Identical branches are considered for simplicity. This circuit combines two different control techniques: (1) gain and power control through transistor width scalability [7] and (2) current-splitting gain-control technique [22, 23].

| $\overline{\Phi_1\Phi_2/\Phi_1^{\mathcal{G}}\Phi_2^{\mathcal{G}}}$ | 11/00   | 10/00<br>01/00 | 00/00                  | 00/01<br>00/10                   | 00/11   |

|--------------------------------------------------------------------|---------|----------------|------------------------|----------------------------------|---------|

| Mode                                                               | HG-FP   | MG-MP          | LG-LP                  | LG-MP                            | LG-FP   |

| Gain                                                               | Highest | $\downarrow$   | $\downarrow\downarrow$ | $\downarrow\downarrow\downarrow$ | Lowest  |

| Power consumption                                                  | Highest | Medium         | Lowest                 | Medium                           | Highest |

| Input resistance                                                   | Highest | Medium         | Lowest                 | Medium                           | Highest |

TABLE 1: Summary of operation modes features.

FIGURE 1: Reconfigurable LNA.

Other characteristics associated with the base topology can be summarized as follows. Degeneration inductance  $(L_s)$  provides the real part of input impedance without adding an extra noise source [24]. Gate-source connected capacitor  $(C_X)$  allows reducing noise figure without increasing power consumption in gain constrained applications [25, 26]. Gate inductor  $(L_g)$  tunes the necessary input impedance and drain inductor  $(L_D)$  provides parallel resonance with the total capacitance at output. Capacitive divider  $(C_1, C_P)$  is used to match output impedance with 50  $\Omega$  termination for standalone prototype testing.

3.1. Operation Modes Description. The operation modes that arise from the scheme of Figure 1 can be described as follows.

The highest gain of the LNA is set by connecting both switchable branches to the output network ( $\Phi_1\Phi_2=11/\Phi_1^g\Phi_2^g=00$ ). However, this HG-FP (standing for "high gain, full power") mode also presents the highest power consumption. If one of the extra branches is turned off (setting  $\Phi_1\Phi_2$  to 10 or 01, with  $\Phi_1^g\Phi_2^g=00$ ), a midgain and midpower mode (MG-MP) is obtained, while turning off both switchable branches ( $\Phi_1\Phi_2=00/\Phi_1^g\Phi_2^g=00$ ) leads to a low gain mode with the lowest power consumption (LG-LP mode).

The drawback of the above-described operation (width scalability) is that it affects the input-impedance matching. The reason is that the input resistance is lower as less current flows through the degeneration inductor (as switchable branches are disconnected). Thus, the allowable impedance matching degradation limits the total gain variation and power-saving ratio.

When needed, modes with lower gain can be achieved, but at the expense of consuming the middle or the highest power values. Low gain/midpower (LG-MP) and low gain/full power (LG-FP) modes are set by turning on one or both switchable branches via the dumping cascode transistors ( $\Phi_1\Phi_2=00$  with  $\Phi_1^g\Phi_2^g=10$  or 01, for LG-MP mode, and  $\Phi_1\Phi_2=00/\Phi_1^g\Phi_2^g=11$ , for LG-FP mode). Although in the three low gain modes (LG-LP, LG-MP, and LG-FP) only the fixed branch ( $M_1$  and  $M_2$ ) is connected to the output, different gain values are obtained because of the variations of the input-stage operation point. When a switchable branch is turned on but the signal flowing through it is dumped to ground (via  $V_{\rm DD}$  path), it does not contribute to the output signal; however, it does increase the input resistance, causing a reduction of the amplifier transconductance.

In summary, Table 1 shows the controlling codes and the expected performance of the different operations modes.

3.2. Adjusting Strategy. Next, the proposed usage of the different operation modes, or adjusting strategy, is presented.

HG-FP mode should provide gain over a certain value,  $G_{\min}$ , in the worst case due to process variations, with  $G_{\min}$  being the minimum gain value needed to achieve the required sensitivity (i.e., NF<sub>Rxmax</sub>). On the other hand, the midgain typical value can be set slightly over  $G_{\min}$  by properly sizing  $M_1$ ,  $M_3$ , and  $M_5$ . This way, those receivers less affected by process variations can use MG-MP mode instead of HG-FP mode to receive minimum input-signal level, thus saving power consumption in such cases without degrading production yield.

LG-LP mode can be used for saving power when inputsignal level allows relaxing receiver NF. Depending on the linearity of both, the LNA and the subsequent stages, this low gain mode could also satisfy the system requirement for the maximum input-signal level. However, lower gain modes (LG-MP or LG-FP) could be useful to compensate possible linearity degradation in the LNA due to process variations, increasing power consumption but only when being required.

# 4. Implementation and Results

In order to corroborate the proposed ideas, a LNA was designed and simulated using a 130 nm CMOS technology for a 2.4 GHz IEEE-802.15.4 application. Channel length was set to the minimum value (120 nm) for each transistor. Cascode-transistor width was set to half of the corresponding transconductance-stage transistor. Taking a value of 10 dB for  $G_{\min}$  [27], gain of 12 dB is required for the HG-FP mode

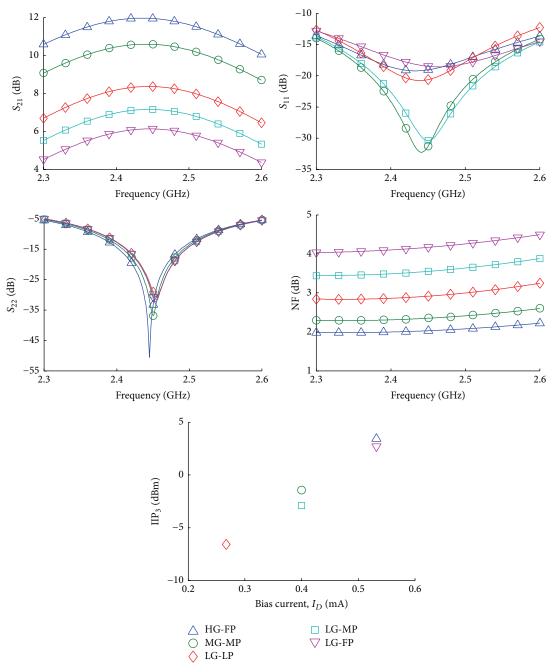

FIGURE 2: Typical-case simulation results.

in the typical case (obtained by corner simulations). MG-MP gain was set close to 10.5 dB. Transistor widths ratio  $W_1:W_3:W_5=2:1:1$  was found to offer a suitable gain variation having proper input-impedance matching in every mode ( $S_{11}<-10$  dB). Transistor widths and current values were chosen from the results of simulation-based design space exploration carried out with the conventional topology (i.e., without switchable branches), minimizing power consumption while trading off LNA's NF and IIP<sub>3</sub>. Passive components were determined to match impedance values at MG-MP mode, in order to tolerate both the increase and the

decrease of input resistance when switching among modes with different biasing currents. Table 2 shows the selected components sizes and biasing. The full power consumption (all branches turned on) is 0.64 mW from a 1.2 V supply, with 25% and 50% power saving when using mid- and lowest power modes, respectively. A current mirror was included to provide gate-biasing voltage,  $V_G$ .

Figure 2 shows typical-case simulation results at  $27^{\circ}$ C. Pairs of modes with the same power consumption (HG-FP/LG-FP and MG-MP/LG-MP) show similar input matching ( $S_{11}$ ) and IIP<sub>3</sub>, as expected taking into account the fact

TABLE 2: LNA component values.

| $I_{D1}/W_1$ ( $\mu$ A/ $\mu$ m) | $I_{D3,5}/W_{3,5} \ (\mu { m A}/\mu { m m})$ | <i>L</i> <sub>S</sub> (nH) | $L_{g}$ (nH) | $C_X$ (fF) | C <sub>1</sub> (fF) | $C_P$ (pF) | $L_D$ (nH) |

|----------------------------------|----------------------------------------------|----------------------------|--------------|------------|---------------------|------------|------------|

| 267/28                           | 133/14                                       | 2.4                        | 11.2         | 246        | 426                 | 1.59       | 10.5       |

that corresponding DC operating points remain fixed. On the other hand, output matching  $(S_{22})$  is not practically affected when switching between modes. The higher the biasing current, the higher the IIP $_3$  and the larger the gain variation obtained by current splitting. This higher-IIP $_3$ /lower gain combination reinforces using LG-MP or LG-FP if the receiver requires better linearity.

4.1. LNA under Process Variations. LNA behavior under process variations was analyzed via 1000-run Monte Carlo simulations, using the statistical distribution provided by the foundry. Receiver performance was evaluated analytically, using LNA simulation results and (4). The overall NF and IIP<sub>3</sub> specifications of the stages following the LNA (NF<sub>fs</sub>, IIP<sub>3fs</sub>) were set to meet receiver requirements, at every Monte Carlo run, with at least one high gain/low gain modes combination. Receiver specifications were taken to comply with IEEE-802.15.4 standard [28], using the requirements at extreme communication-channel conditions proposed by [29]:  $\{NF = 15.5 \, dB; \, IIP_3 = -32 \, dBm\}$ , for detecting minimum input-signal level (-85 dBm, although, for IIP<sub>3</sub> calculation, minimum input-signal power is taken as 3 dB over receiver's sensitivity [28], i.e., -82 dBm [16]) with maximum interference (–52 dBm) and  $SNR_{min} = 10.5 \ dB$  (derived from the values given by [29]); and  $IIP_3 = -10 \text{ dBm}$ , for receiving the maximum input power (-20 dBm). The most relaxed NF<sub>fs</sub> and IIP  $_{\rm 3fs}$  were selected (25.3 dB and 4.2 dBm, resp.), achieved when using the HG-FP/LG-FP modes combination.

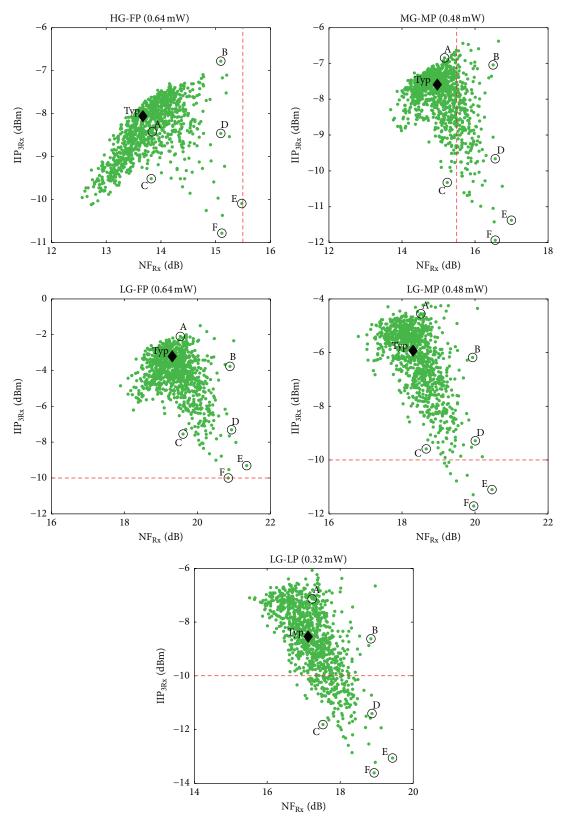

Figure 3 shows the values of NF and IIP<sub>3</sub> of the receiver, corresponding to every run of Monte Carlo simulations (dots) and to the typical case (color-filled diamond). Dashed lines mark out receiver specifications according to the function of each operation mode (NF specification for high gain and midgain modes, IIP<sub>3</sub> specification for low gain modes).

IIP<sub>3</sub> is always higher than the minimum value required for receiving weak signals in the presence of interferers (–32 dBm); thus, noise figure determines receiver sensitivity in all cases. In addition, in each case, the maximum inputsignal power that can be handled by the high gain and midgain modes is always higher than the sensitivity of the low gain modes. This guarantees that any input-signal level is covered by at least one operation mode.

According to the minimum power consumption that needs to be used to meet receiver requirements at extreme communication-channel conditions, five possible scenarios were obtained. For each scenario, the behavior of a specific run has been highlighted in Figure 3. Circuits with lower or no degradation in their RF performance (e.g., run A), with respect to the typical case, can use the lowest power-consumption combination (MG-MP/LG-LP, consuming 0.48 and 0.32 mW, resp.) for receiving the minimum

and maximum input-signal levels required by the standard (NF $_{RxMG-MP}$  < 15.5 dB and IIP $_{3RxLG-LP}$  > -10 dBm).

When the noise figure of the receiver using MG-MP mode does not ensure the receiver sensitivity (NF<sub>RxMG-MP</sub> > 15.5 dB), thus HG-FP mode (increasing power consumption to 0.64 mW) has to be used instead (e.g., runs B, D, E, and F). In such cases, HG-FP mode should be combined with one of the low gain modes depending on linearity performance: having acceptable linearity (IIP $_{3RxLG-LP}$  > -10 dBm) allows using LG-LP mode (e.g., run B); midlevel linearity degradation (IIP $_{3RxLG-LP}$  < -10 dBm but IIP $_{3RxLG-MP}$  > -10 dBm) requires using LG-MP mode (consuming 0.48 mW, e.g., run D), while runs with more degraded linearity (IIP $_{3RxLG-MP}$  < -10 dBm) demand the mode with the lowest gain and highest IIP $_3$ , LG-FP mode (0.64 mW, e.g., runs E and F). Particularly, runs E and F correspond with the worst cases of receiver's noise figure and linearity, respectively.

On the other hand, if receiver noise figure is acceptable but linearity degrades, MG-MP/LG-MP combination is used (e.g., run C). The last possible scenario, cases with an acceptable receiver NF and highly degraded IIP<sub>3</sub>, does not present any occurrence; thus, MG-MP/LG-FP combination is not required.

Table 3 summarizes the above information, including the occurrence probability of each scenario. In most of the runs, the lowest power-consumption combination (MG-MP/LG-LP) can be used, while the most power-consuming combination (HG-FP/LG-FP) is required only in 1% of the cases.

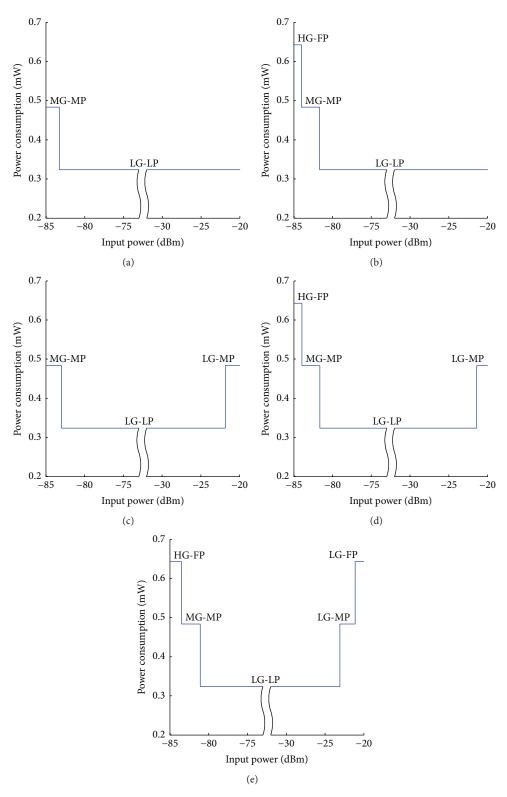

Additionally, with independence of operation modes required to handle extreme communication-channel conditions, the lowest DC power can be consumed (i.e., using the LG-LP mode) during circuit operation as input-signal level moves away from its minimum and maximum values and more relaxed behavior of receiver's noise and linearity can be tolerated (according to (1)–(3)). This can be observed in Figure 4, where the minimum required power consumption of the LNA has been plotted as a function of input-signal level. Five different plots have been included, corresponding to each process-variations scenario. It is noticeable that the LG-LP mode can handle most of the input-signal power range. This should increase the probabilities of saving energy at operation time.

4.2. Supply and Temperature Variations. The capabilities of the proposed circuit to counteract the effects of supply-voltage and temperature variations, as other important causes of performance degradation in microelectronics circuits, were also analyzed. Simulations sweeping  $V_{\rm DD}$  value, at 27°C, and temperature, with  $V_{\rm DD}=1.2$  V, were carried out using the typical-case circuit with respect to process variations.

$\label{eq:figure 3: NF and IIP_3 of the receiver calculated from Monte Carlo simulation results of the designed LNA.$

FIGURE 4: LNA power-consumption profile as a function of input-signal power, for different process-variations scenarios.

| LNA performance                 | Receiver performance          | Minimum input-power reception | Maximum input-power reception | Number of cases | Sample in<br>Figure 3 |

|---------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------|-----------------------|

| Gain ok and IIP <sub>3</sub> ok | NF ok and IIP <sub>3</sub> ok | MG-MP (-25% <sup>†</sup> )    | LG-LP (-50% <sup>†</sup> )    | 74%             | A                     |

| Gain↓ and IIP₃ ok               | NF↑ and IIP <sub>3</sub> ok   | HG-FP (100% <sup>†</sup> )    | LG-LP (-50% <sup>†</sup> )    | 11%             | В                     |

| Gain ok and $IIP_3 \downarrow$  | NF ok and $IIP_3 \downarrow$  | MG-MP $(-25\%^{\dagger})$     | $LG-MP(-25\%^{\dagger})$      | 6%              | С                     |

| Gain↓ and $IIP_3$ ↓↓            | NF↑ and $IIP_3$ ↓             | HG-FP (100% <sup>†</sup> )    | LG-MP $(-25\%^{\dagger})$     | 8%              | D                     |

| Gain   and IIP2                 | NF↑ and IIP₂                  | HG-FP (100% <sup>†</sup> )    | LG-FP (100% <sup>†</sup> )    | 1%              | E and F               |

Table 3: Modes utilization at extreme communication-channel conditions, depending on the effects of process variations.

Table 4: Performance comparison of LNAs for IEEE-802.15.4 receivers.

| Reference            | Tech.<br>(nm) | f <sub>o</sub><br>(GHz) | $V_{ m DD} \  m (V)$ | P <sub>DC</sub> (mW) | Gain<br>(dB) | NF<br>(dB) | IIP <sub>3</sub> (dBm) | NF <sub>fs</sub> (dB) | IIP <sub>3fs</sub> (dBm) |

|----------------------|---------------|-------------------------|----------------------|----------------------|--------------|------------|------------------------|-----------------------|--------------------------|

|                      |               |                         |                      | 0.64                 | 10.1         | 2.5        | -8.1                   |                       |                          |

| This work 130        | 130           | 2.45                    | 1.2                  | 0.32                 | 6.5          | 3.4        | -13.3                  | 25.3                  | 4.2                      |

|                      |               |                         |                      | 0.64                 | 4.6          | 4.5        | -9.5                   |                       |                          |

| [6] <sup>†</sup> 180 |               |                         |                      | 4.3                  | 27           | 7          | -11.5                  |                       |                          |

|                      | 2.25 1.8      | 2.5                     | 26                   | 8                    | -9.5         | 41.9       | 25.3                   |                       |                          |

|                      |               |                         |                      | 1.1                  | 19           | 9          | -10.5                  |                       |                          |

| [18]                 | 90            | 2.45                    | 1.2                  | 0.68                 | 9.7          | 4.36       | -4                     | 24.9                  | 1.0                      |

<sup>&</sup>lt;sup>†</sup>Half the power from differential structure considered, in order to normalize comparison.

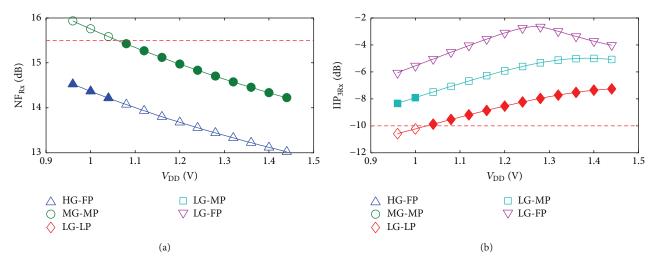

Receiver performance was evaluated using the values of  $NF_{fs}$  and  $IIP_{3fs}$  calculated to cover the worst cases of process variations (25.3 dB and 4.2 dBm, resp.).

Figure 5 shows the performance of NF and IIP3 in the receiver under LNA supply variations, up to ±20% with respect to its nominal value (i.e., from 0.96 V to 1.44 V). Dashed lines indicate receiver requirements (NF<sub>Rx</sub> < 15.5 dB;  $IIP_{3Rx} > -10 \, dBm$ ), while color-filled markers denote the operation mode meeting each specification with the lowest power consumption. Receiver's NF rises as  $V_{\rm DD}$  decreases, mainly because LNA gain drops due to a decrease of  $M_1$ 's transconductance. On the other hand, despite the LNA gain reduction, receiver's IIP<sub>3</sub> also degrades for  $V_{\rm DD}$  decreasing below 1.2 V, caused by degradation of LNA linearity. However, the proposed LNA shows up to be capable of counteracting these effects. When using MG-MP mode does not meet receiver's sensitivity (NF $_{RxMG-MP}$  > 15.5 dB for  $V_{DD}$  < 1.06 V), switching to HG-FP mode allows fulfilling this requirement at the expense of increasing power consumption. Similarly, LG-LP mode cannot be used to receive the maximum input-signal level (IIP $_{3RxLG-LP}$  <  $-10 \, dBm$ ) for  $V_{\rm DD}$  < 1.03 V, but lower gain modes maintain the required receiver's linearity (e.g., LG-MP in the analyzed range).

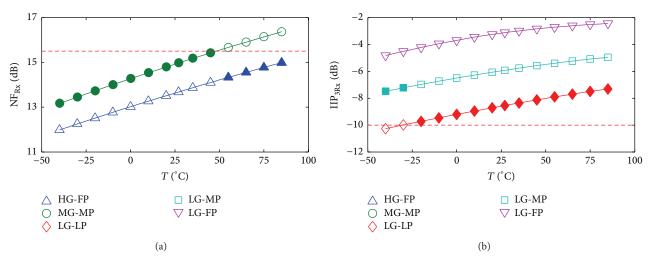

Regarding temperature variations, Figure 6 shows receiver's NF and IIP $_3$  behavior calculated using simulation results of the LNA, sweeping this parameter from  $-40^{\circ}$ C to 85°C. When temperature increases, it causes the degradation of noise figure, while if it decreases then IIP $_3$  drops. Again, switching to higher power-consumption operation modes allows meeting the required sensitivity or linearity when needed (NF $_{\rm RxMG-MP}$  > 15.5 dB for T > 49°C; IIP $_{\rm 3RxLG-LP}$  < -10 dBm for T <  $-30^{\circ}$ C).

4.3. Comparison to Other Works. Table 4 compares the performance of the proposed LNA with previously published IEEE-802.15.4 LNAs (energy-aware [6] and conventional [18] designs). From our work, the following modes and cases from process-variation analysis are presented: the lowest gain (highest NF) case of HG-FP mode and the lowest IIP $_3$  case of LG-LP and LG-FP modes. In order to evaluate and compare the performance of each LNA in the receiver context, required NF and IIP $_3$  of the following stages were calculated and presented.

The power-saving ratio  $[(P_{DCmax} - P_{DCmin})/P_{DCmax}]$  in [6] is better than ours (74% versus 50%), but our design presents significantly lower power consumption. The higher gain in [6] relaxes NF in the subsequent stages but demands better linearity in a similar degree. On the other hand, RF performance and full power consumption of the proposed LNA are comparable to those presented at [18], but ours can save up to 50% of power under relaxed working conditions.

#### 5. Conclusions

A reconfigurable LNA with digitally controllable gain and power consumption is presented as an energy-aware solution. Novel design guidelines are given to minimize power consumption as a function of both communication-channel conditions and the effects of process variations. A 130 nm 1.2 V CMOS LNA following the presented proposal was designed for a 2.4 GHz IEEE-802.15.4 application, corroborating the effectiveness of the power-saving strategy. The designed LNA shows up to be capable of counteracting the effect of supply-voltage and temperature variations as well. Simulation results, taking into account worst cases under process variations,

<sup>&</sup>lt;sup>†</sup>Power consumption with respect to the full power modes.

FIGURE 5: Receiver's NF (a) and IIP<sub>3</sub> (b) under LNA supply variations.

FIGURE 6: Receiver's NF (a) and IIP<sub>3</sub> (b) under LNA temperature variations.

are comparable to recently published works, having the advantage that significant power saving can be achieved with our proposal under relaxed working conditions.

#### **Conflict of Interests**

The authors declare that there is no conflict of interests regarding the publication of this paper.

# Acknowledgments

This work has been supported by CAPES-Brazil through Project 176/12, CNPq (Brazil), MAEC-AECID (Spain) through FORTIN project (Ref. D/024124/09), FEDER program through the Junta de Andalucía Project P09-TIC-5386, and Ministerio de Economía y Competitividad (Spain) through Project TEC2011-28302.

## References

- [1] G. Gielen, P. De Wit, E. Maricau et al., "Emerging yield and reliability challenges in nanometer CMOS technologies," in *Proceedings of the Design, Automation and Test in Europe (DATE '08)*, pp. 1322–1327, Munich, Germany, March 2008.

- [2] A. Papanikolaou, F. Lobmaier, H. Wang, M. Miranda, and F. Catthoor, "A system-level methodology for fully compensating process variability impact of memory organizations in periodic applications," in *Proceedings of the 3rd IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and Systems Synthesis (CODES+ISSS '05)*, pp. 117–122, September 2005.

- [3] J. L. González, J. C. Cruz, D. Vázquez, and A. Rueda, "Analysis of process variations' impact on a 2.4 GHz 90 nm CMOS LNA," in *Proceedings of the 4th IEEE Latin American Symposium on Circuits and Systems (LASCAS '13)*, pp. 1–4, IEEE, Cusco, Peru, February-March 2013.

- [4] A. Tasić, S.-T. Lim, W. A. Serdijn, and J. R. Long, "Design of adaptive multimode RF front-end circuits," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 2, pp. 313–322, 2007.

- [5] R. Senguttuvan, S. Sen, and A. Chatterjee, "Multidimensional adaptive power management for low-power operation of wireless devices," *IEEE Transactions on Circuits and Systems II:* Express Briefs, vol. 55, no. 9, pp. 867–871, 2008.

- [6] A. V. Do, C. C. Boon, M. A. Do, K. S. Yeo, and A. Cabuk, "An energy-aware CMOS receiver front end for low-power 2.4-GHz applications," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 10, pp. 2675–2684, 2010.

- [7] K. Ghosal, T. Anand, V. Chaturvedi, and B. Amrutur, "A power-scalable RF CMOS receiver for 2.4 GHz Wireless Sensor Network applications," in *Proceedings of the 19th IEEE International Conference on Electronics, Circuits, and Systems (ICECS '12)*, pp. 161–164, Seville, Spain, December 2012.

- [8] B. Razavi, RF Microelectronics, Prentice-Hall, Upper Saddle River, NJ, USA, 1998.

- [9] T. H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Cambridge University Press, Cambridge, UK, 2nd edition, 2004.

- [10] M. Aya, T. Thierry, D. Yann, and B. Jean-Baptiste, "A variable gain 2.4-GHz CMOS low noise amplifier employing body biasing," in *Proceedings of the Research in Microelectronics and Electronics. Ph.D. (PRIME '09)*, pp. 168–171, IEEE, Cork, Ireland, July 2009.

- [11] T. Das, A. Gopalan, C. Washburn, and P. R. Mukund, "Self-calibration of input-match in RF front-end circuitry," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 52, no. 12, pp. 821–825, 2005.

- [12] K. Jayaraman, Q. Khan, B. Chi, W. Beattie, Z. Wang, and P. Chiang, "A self-healing 2.4GHz LNA with on-chip S11/S21 measurement/calibration for in-situ PVT compensation," in Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC '10), pp. 311–314, IEEE, Anaheim, Calif, USA, May 2010.

- [13] Y. Liu and J.-S. Yuan, "CMOS RF low-noise amplifier design for variability and reliability," *IEEE Transactions on Device and Materials Reliability*, vol. 11, no. 3, pp. 450–457, 2011.

- [14] A. Goyal, M. Swaminathan, A. Chatterjee, D. C. Howard, and J. D. Cressler, "A new self-healing methodology for RF amplifier circuits based on oscillation principles," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 20, no. 10, pp. 1835–1848, 2012.

- [15] Y.-R. Wu, Y.-K. Hsieh, P.-C. Ku, and L.-H. Lu, "A built-in gain calibration technique for RF low-noise amplifiers," in *Proceedings of the IEEE 32nd VLSI Test Symposium (VTS '14)*, pp. 1–6, Napa, Calif, USA, April 2014.

- [16] N.-J. Oh and S.-G. Lee, "Building a 2.4-GHz radio transceiver using IEEE 802.15.4," *IEEE Circuits and Devices Magazine*, vol. 21, no. 6, pp. 43–51, 2005.

- [17] J. Rogers and C. Plett, *Radio Frequency Integrated Circuit Design*, Artech House, Boston, Mass, USA, 2nd edition, 2010.

- [18] R. Fiorelli, F. Silveira, and E. Peralias, "MOST moderate-weak-inversion region as the optimum design zone for CMOS 2.4-GHz CS-LNAs," *IEEE Transactions on Microwave Theory and Techniques*, vol. 62, no. 3, pp. 556–566, 2014.

- [19] W. Sheng, A. Emira, and E. Sánchez-Sinencio, "CMOS RF receiver system design: a systematic approach," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 53, no. 5, pp. 1023–1034, 2006.

- [20] F. Ellinger, U. Lott, and W. Bachtold, "A 5.2 GHz variable gain LNA MMIC for adaptive antenna combining," in *Proceedings* of the IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, pp. 197–200, Anaheim, Calif, USA, June 1999.

- [21] F. Keng Leong, "Dual-band high-linearity variable-gain lownoise amplifiers for wireless applications," in *Proceedings of* the IEEE International Solid-State Circuits Conference. Digest of Technical Papers (ISSCC '99), pp. 224–225, IEEE, San Francisco, Calif, USA, February 1999.

- [22] W. R. Davis and J. E. Solomon, "A high-performance monolithic IF amplifier incorporating electronic gain control," *IEEE Journal of Solid-State Circuits*, vol. 3, no. 4, pp. 408–416, 1968.

- [23] M. Koutani, H. Kawamura, S. Toyoyama, and K. Iizuka, "A digitally controlled variable-gain low-noise amplifier with strong immunity to interferers," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 11, pp. 2395–2403, 2007.

- [24] A. N. Karanicolas, "A 2.7-V 900-MHz CMOS LNA and mixer," IEEE Journal of Solid-State Circuits, vol. 31, no. 12, pp. 1939–1944, 1996.

- [25] P. Andreani and H. Sjöland, "Noise optimization of an inductively degenerated CMOS low noise amplifier," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 48, no. 9, pp. 835–841, 2001.

- [26] L. Belostotski and J. W. Haslett, "Noise figure optimization of inductively degenerated CMOS LNAs with integrated gate inductors," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 53, no. 7, pp. 1409–1422, 2006.

- [27] R. Fiorelli, A. Villegas, E. Peralías, D. Vázquez, and A. Rueda, "2.4-GHz single-ended input low-power low-voltage active front-end for ZigBee applications in 90 nm CMOS," in Proceedings of the 20th European Conference on Circuit Theory and Design (ECCTD '11), pp. 829–832, IEEE, Linkoping, Sweden, August 2011.

- [28] IEEE, "IEEE Standard for local and metropolitan area networks—part 15.4: low-rate wireless personal area networks," IEEE Std 802.15.4e-2012, IEEE, 2011.

- [29] N. Trung-Kien, V. Krizhanovskii, L. Jeongseon et al., "A low-power RF direct-conversion receiver/transmitter for 2.4-GHz-band IEEE 802.15.4 standard in 0.18-\(\mu\)m CMOS technology," *IEEE Transactions on Microwave Theory and Techniques*, vol. 54, no. 12, pp. 4062–4071, 2006.

Submit your manuscripts at http://www.hindawi.com

International Journal of Antennas and

Propagation