# ESCUELA SUPERIOR DE INGENIEROS DEPARTAMENTO DE INGENIERÍA ELECTRÓNICA UNIVERSIDAD DE SEVILLA

## TESIS DOCTORAL

# Contributions to the Detection and Diagnosis of Soft Errors In Radiation Environments

Autor: Juan Manuel Mogollón García Director: Miguel Ángel Aguirre Echánove

# ESCUELA SUPERIOR DE INGENIEROS DEPARTAMENTO DE INGENIERÍA ELECTRÓNICA UNIVERSIDAD DE SEVILLA

### **DOCTORAL THESIS**

Submitted to the

University of Seville

for the degree of

Doctor on Electronics Engineering

Contributions to the Detection and Diagnosis of Soft Errors in Radiation Environments

**Author:** Director:

Juan Manuel Mogollón García Miguel Ángel Aguirre Echánove

Sevilla, 15 de Agosto de 2012

# Acknowledgements

"Knowledge is in the end based on acknowledgement."

- Ludwig Wittgenstein

Esta tesis es el fruto de una larga y apasionante odisea profesional, pero también personal. Me gustaría mostrar mi agradecimiento a todos aquellos que hicieron posible que este barco llegara a buen puerto:

A mi director, Miguel Ángel Aguirre, por su entrega y dedicación, por concebir el germen de esta tesis y, sobre todo, por demostrar una confianza férrea en mi trabajo.

A mis compañeros de trabajo Hipólito Guzmán y Javier Nápoles, a Poli en particular por donarme la plantilla LATEX de su tesis y a los dos por insuflarme ánimos en los momentos de flaqueza. Ha sido un placer enorme formar parte de este equipo, y espero que nuestro futuro profesional continúe mucho tiempo de la mano.

A Rogelio, que me otorgó la oportunidad de dedicarme a la investigación y me pertrechó para ello. También a Alfredo, por enseñarme valiosísimos rudimentos de la ingeniería electrónica en mis primeros proyectos industriales.

A todos mis compañeros del departamento, que me han enseñado de forma ostensiva lo que es trabajar en equipo: Migue, Clara, Enrique, Perdi, Nando, Jose Ramón, Trini, Carmen, Antonio...

A David Merodio, Boris Glass, Jelle Poupaert y Roland Weigand, de la Sección de Microelectrónica de ESTEC (ESA), por hacer que mi estancia allí fuera deliciosa, y por contribuir con sus comentarios a mejorar este trabajo.

A mi familia, por su apoyo incondicional y paciencia ilimitada.

Y por supuesto al Maestro, cada día con él fue un repertorio de *lessons learned* para la vida, thank you Jon.

| Acknowledgements |  |  |

|------------------|--|--|

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

|                  |  |  |

## **Abstract**

The effects of ionizing radiation on semiconductors are under study since the invention of the bipolar transistor back in 1947. Outer space is a harsh radiation environment as showed by the first orbiting artificial satellites. It was during the space race in the 50's, when the study of induced errors in critical electronic components underwent an important impulse. The need for robust electronics against radiation has been always present in the aerospace sector. Nowadays, the trend in industry towards scale down semiconductor technologies is bringing these concerns down to the electronic equipments operating at sea level. Modern nanoscale technologies are challenging designers to develop new and more efficient hardening techniques to guarantee reliability in electronic components for critical systems in civil aviation, automotive or nuclear energy industries, for example.

• Research activities within the group the author belongs in the field of Single Event Effects (SEE) on electronic devices, unveiled the necessity to establish a methodology to diagnose errors observed on electronic components when put under ionizing radiation. Generally, it becomes very difficult to correlate with certainty the observed errors to the internal faults. Furthermore, complexity inherent to the instrumentation in a particle accelerator radiation test, added to the own design complexity of the device under test (DUT), require some kind of criterion for the validation of observed errors that can be of diverse nature (dose damage, physical damage or even signal integrity issues). Obtaining cross section curves for SEE (Single Event Effects) is the common way to represent experimental results from radiation tests. This curves represent a collection of experimental data that have to be previously carefully classified. The same is valid in tests addressed to evaluate Real Time Soft Error Rates (RTSER). Regarding error classification, the standard JEDEC JESD89-1A recommends to follow a "failure criteria" for proper identification of detected errors at the outputs of a circuit in radiation tests. A validation method is required. This thesis introduces a methodology which contributes to the identification of observed errors for proper validation of the experimental results.

- The radiation effects research group based at the Department of Electronics Engineering of the University of Seville have a contrasted experience in the use of hardware emulators for early evaluation of robustness against soft errors in digital designs. Hardware emulation platforms are used to inject faults in the netlist of a digital design in order to study the evolution of the logic state of the circuit under operation. The main advantage in comparison to simulation techniques is in hardware acceleration, allowing fast execution of massive fault injection campaigns. Massive or systematic fault injection campaigns allow to check exhaustively the response of a digital circuit in a harsh radiation environment. These campaigns produce a lot of information on the vulnerabilities of the design. This data must be processed statistically. The availability to correlate the clock cycle for fault injection and the corresponding target register with the associated response would be very valuable to establish the cause of observed errors during a beam test, where only outputs are monitored. The main contribution of this thesis is in the detection and diagnosis of soft errors appearing in radiation experiments.

- Results from an injection campaign depend on the DUT, but also on the set of applied stimuli or *workload*. The results from a massive injection campaign can be used to perform a statistical analysis about the *quality* of the test vectors for diagnosis. It is expected that different faults share the same failure pattern (signature) at the outputs so it'd become impossible to determine the cause of the observed error in a radiation experiment. In the setup of a radiation experiment it is recommendable to consider a set of test vectors that minimize the aliasing in diagnosis. The methodology developed in this thesis definitely contributes to this point, introducing a *figure of merit* for the quality of the set of test vectors.

The work described in this thesis is aimed at establishing a methodology to obtain a *dictionary of faults* where a connection exists between a well known internal fault and the circuit's response coded in a signature of few bytes. In a radiation test, these signatures can be recorded in real time to identify the origin of the damage by means of the fault dictionary, generated by exhaustive fault injection in a hardware emulator. In case the signature is not present in the fault dictionary, it can be stated that the observed error was not generated by a fault like the modeled for the dictionary generation. The origin of the error can be a different type of SEE or an error of different nature, for example physical damage.

The thesis culminates with a radiation test in a particle accelerator. The University of Seville hosts the facilities of the National Accelerators Center, in particular the Tandem Van der Graaf Linear accelerator, which has proven to be an excelent testbench for the validation of the error detection and diagnosis methodology proposed in this thesis.

# **Table of Contents**

| Ac | knov  | ledgements                                      | ix |

|----|-------|-------------------------------------------------|----|

| Al | strac | t                                               | хi |

| 1  | Intr  | oduction                                        | 23 |

|    | 1.1   | Electronics and Ionizing Radiation              | 23 |

|    | 1.2   | Radiation Effects on Semiconductors             | 26 |

|    |       | 1.2.1 Activation by Nuclear Reactions           | 28 |

|    |       | 1.2.2 Displacement Damage Effects               | 30 |

|    |       | 1.2.3 Total Ionizing Dose                       | 30 |

|    |       | 1.2.4 Single-Event Effects                      | 31 |

|    | 1.3   | Hardness Assurance Against Radiation            | 35 |

|    | 1.4   | Fault Injection Techniques for Digital Circuits | 36 |

|    |       | 1.4.1 Hardware-Based Fault Injection: HWFI      | 37 |

|    |       | 1.4.2 Software-Based Fault Injection: SWFI      | 38 |

|    |       | 1.4.3 Simulation-Based Fault Injection: SBFI    | 38 |

|    |       | 1.4.4 Hybrid Techniques: Hardware Emulation     | 39 |

|    | 1.5   | Hardware Emulators for Fault Injection          | 39 |

|    |       | 1.5.1 Instrumented Fault Injection              | 41 |

|    |       | 1.5.1.1 Emulation Systems Depending on a Host   | 41 |

|    |       | 1.5.1.2 Autonomous Emulation System             | 43 |

|    |       | 1.5.2 Fault Injection by Reconfiguration        | 44 |

|    | 1.6   | Revision of FT-UNSHADES                         | 46 |

|    |       | 1.6.1 Basic Operation                           | 47 |

|    |       | 1.6.2 Injection Run                             | 48 |

|    | 1.7   | Scope of the Thesis                             | 49 |

| 2  | Soft  | Error Testing                                   | 53 |

|    | 2.1   | Introduction                                    | 53 |

|    | 2.2   | SEE Computer Simulation                         | 54 |

|    |       | 2.2.1 SPICE                                     | 55 |

|   |      | 2.2.2 SRIM                                        |

|---|------|---------------------------------------------------|

|   |      | 2.2.3 TCAD                                        |

|   | 2.3  | Radiation Testing                                 |

|   |      | 2.3.1 Cross-Sections                              |

|   |      | 2.3.2 Proton Beams 61                             |

|   |      | 2.3.3 Neutron Tests                               |

|   |      | 2.3.4 Pulsed Laser Method                         |

|   |      | 2.3.5 Ion Beams                                   |

|   |      | 2.3.5.1 Broad Beam                                |

|   |      | 2.3.5.2 Microprobe                                |

|   | 2.4  | Proposed Methodology for Soft Error Testing       |

|   | 2.5  | Remarks on This Chapter                           |

| 3 | Sign | ature Analysis 69                                 |

|   | 3.1  | Introduction                                      |

|   | 3.2  | Use of Signature Analysis for Soft Error Testing  |

|   | 3.3  | Signature Module                                  |

|   | 3.4  | Hash Functions                                    |

|   | 3.5  | Fowler-Noll-Vo Versus RIPEMD160 Hash Functions 76 |

|   |      | 3.5.1 Implementation on an FPGA Device            |

|   |      | 3.5.2 Pros and Cons                               |

|   | 3.6  | Remarks on This Chapter                           |

| 4 | Faul | t Injection Campaigns 83                          |

|   | 4.1  | Introduction                                      |

|   | 4.2  | Beam Test Mode of Operation                       |

|   | 4.3  | Fault Dictionary Generation                       |

|   |      | 4.3.1 SEU Dictionaries                            |

|   |      | 4.3.2 SET Dictionaries                            |

|   |      | 4.3.3 MBU Dictionaries                            |

|   | 4.4  | Workload Suitability for Fault Diagnosis          |

|   | 4.5  | Remarks on This Chapter                           |

| 5 | Exp  | eriment at the Particle Accelerator 97            |

|   | 5.1  | Introduction                                      |

|   | 5.2  | Automatic Test Equipment                          |

|   | 5.3  | Microbeam Chamber                                 |

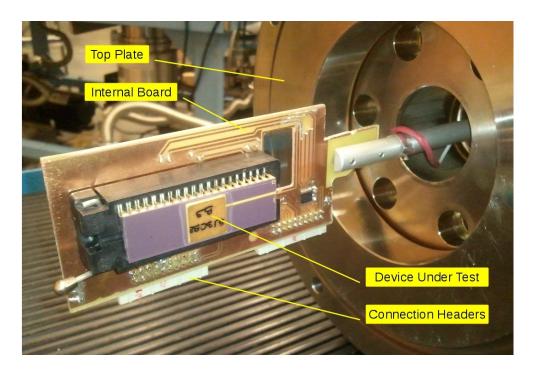

|   | 5.4  | Vehicle Under Test                                |

|   | 5.5  | Signal Integrity Issues                           |

|   | 2.3  | 5.5.1 Emulator-Side Voltage Translation           |

|   |      | 5.5.2 DUT-Side Voltage Translation                |

|   |      |                                                   |

|    | 5.6    | Projectile Selection                                  | 109 |

|----|--------|-------------------------------------------------------|-----|

|    | 5.7    | Final Test Considerations                             | 111 |

|    |        | 5.7.1 Multi-Bit Upset                                 | 111 |

|    |        | 5.7.2 SET Errors                                      | 112 |

|    |        | 5.7.3 Timing                                          | 112 |

|    | 5.8    | Remarks on This Chapter                               |     |

| 6  | Disc   | ussion of the Results                                 | 115 |

| U  | 6.1    | Introduction                                          |     |

|    | 6.2    | Experimental Results                                  |     |

|    | 6.3    | Side Effects                                          |     |

|    | 0.5    | Side Effects                                          | 110 |

| 7  | Cone   | clusions and Future Work                              | 121 |

|    | 7.1    | Conclusions of the Present Work                       | 121 |

|    | 7.2    | Future Work                                           | 122 |

| Ap | pend   | ices                                                  | 125 |

| A  | VHI    | OL Considerations for Turning FT-UNSHADES into an ATE | 127 |

| R  | DCR    | Designs for the Microprobe End-Line                   | 129 |

| D  | ГСБ    | Designs for the Wicroprobe End-Line                   | 149 |

| C  | Log    | Files from Radiation Experiments                      | 133 |

| D  | VHI    | OL Entity for FNV                                     | 135 |

| E  | VHI    | OL Package for RIPEMD-160                             | 137 |

|    |        |                                                       |     |

| Bi | bliogr | aphy                                                  | 143 |

| Gl | ossar  | v                                                     | 160 |

# **List of Figures**

| 1.1  | Explorer I technical details. Source: U.S. Army SMDC                    | 24  |

|------|-------------------------------------------------------------------------|-----|

| 1.2  | Twins RBSP satellites and Van Allen belts. Image courtesy of            |     |

|      | NASA/Johns Hopkins University Applied Physics Laboratory                | 25  |

| 1.3  | Activation by capture of slow neutron                                   | 29  |

| 1.4  | Technology Computer Aided Design (TCAD) simulation of ion-              |     |

|      | ization track in a MOS transistor after ion strike at normal inci-      |     |

|      | dence [33]                                                              | 32  |

| 1.5  | Parasitic resistors and transistors in CMOS structure giving place      |     |

|      | to unwanted thyristor eventually triggered by ion strike                | 33  |

| 1.6  | Propagation Induced Pulse Broadening effect after a transient volt-     |     |

|      | age excursion in a node of a chain of inverters. Schematic for          |     |

|      | mixed-mode simulation [68]                                              | 34  |

| 1.7  | Schematic of a 6-transistor SRAM cell                                   | 34  |

| 1.8  | 3D model of a 6-transistor SRAM cell for TCAD simulation [33] .         | 35  |

| 1.9  | Schema with main blocks in an emulator system managed by a              |     |

|      | host computer. Source: [21]                                             | 41  |

| 1.10 | Fault Injector architecture for each FF in the design. Source: [22] .   | 42  |

| 1.11 | Fault Injector architecture $DFF_{inj}$ for every FF to be injected.    |     |

|      | Source: [109]                                                           | 43  |

| 1.12 | Big picture of an autonomous hardware emulator. Source: [56]            | 43  |

| 1.13 | Autonomous hardware emulator block diagram. Source: [56]                | 44  |

| 1.14 | FT-UNSHADES board                                                       | 46  |

| 1.15 | FT-UNSHADES block diagram                                               | 47  |

|      |                                                                         |     |

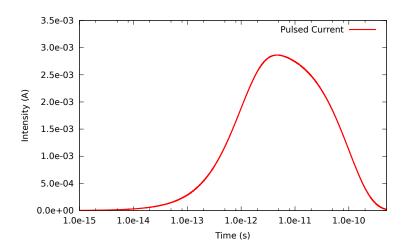

| 2.1  | Pulsed current shaping to simulate the currents appearing after ion     |     |

|      | or laser irradiation close to the nodes of a MOS transistor. *Note:     |     |

|      | Time is in logarithmic scale, so rise time is orders of magnitude       | ~ ~ |

| 2.2  | shorter than fall time                                                  | 56  |

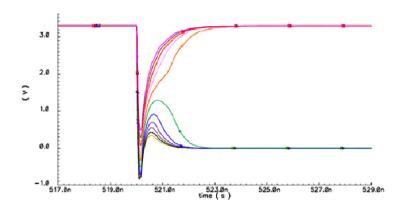

| 2.2  | SPICE parametric simulation to find the threshold value of $Q_{tot}$ in |     |

|      | equation 2.1 giving place to bit-flip                                   | 57  |

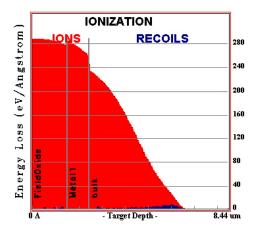

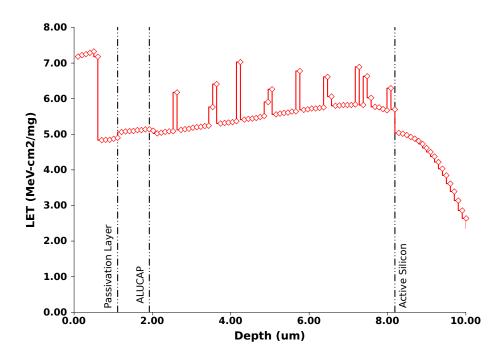

| 2.3 | Linear Energy Transfer profile for a 12 MeV Mg ion passing through a simplified layer model of the AMIS C5 technology                                                                                                                                                                                                                                        | 58 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.4 | SRAM cell for mixed simulation Spice-TCAD to estimate the LET threshold for bit-flip                                                                                                                                                                                                                                                                         | 60 |

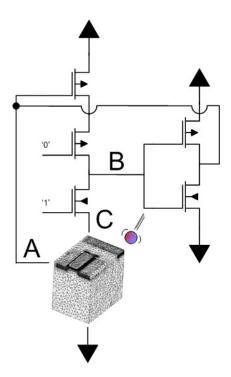

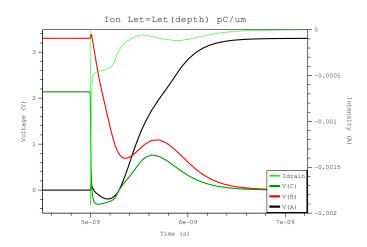

| 2.5 | Mixed-mode transient simulation for the strike of 12 MeV Mg ion on the cell of Figure 2.4                                                                                                                                                                                                                                                                    | 61 |

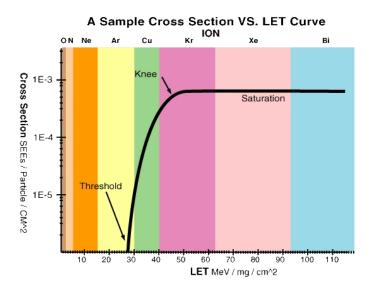

| 2.6 | Cross section vs. LET curve. Y-axis represents the probability of having SEE per unit area and incident ion. The X-axis is the ion LET. Source: The Aerospace Corporation                                                                                                                                                                                    | 62 |

| 2.7 | Cyclotron at the CNA. Protons were accelerated to 18 MeV for a first dynamic radiation experiment on a Xilinx CPLD [107]                                                                                                                                                                                                                                     | 63 |

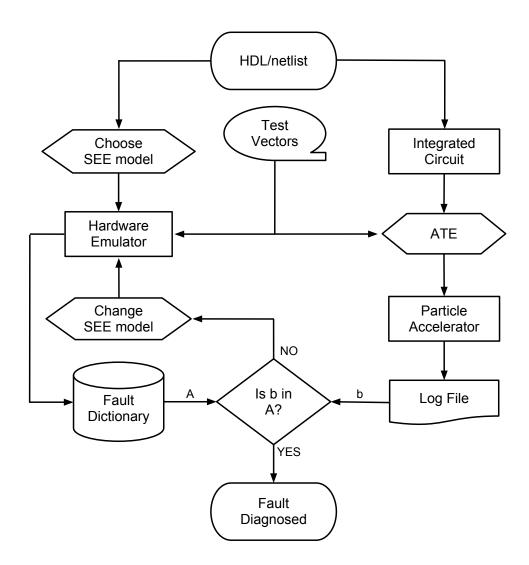

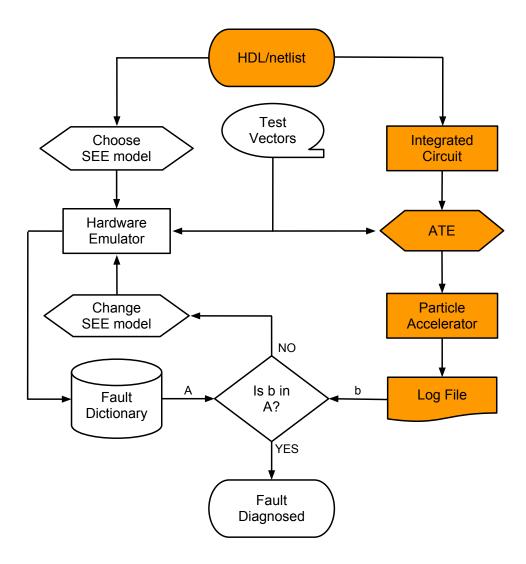

| 2.8 | Flow chart of the proposed approach                                                                                                                                                                                                                                                                                                                          | 67 |

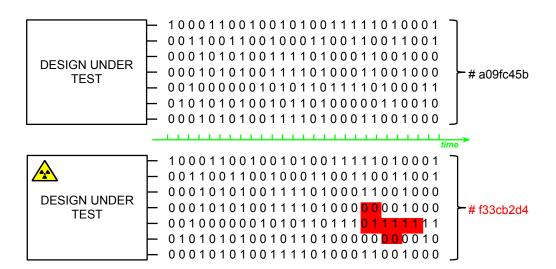

| 3.1 | Figure on the top represents the normal data flow from the DUT output port and the associated hexadecimal signature or <i>golden</i> signature. Figure on the bottom represents the circuit operating under radiation, an erroneous data flow (the error pattern is shadowed) and the associated <i>anomalous</i> signature                                  | 72 |

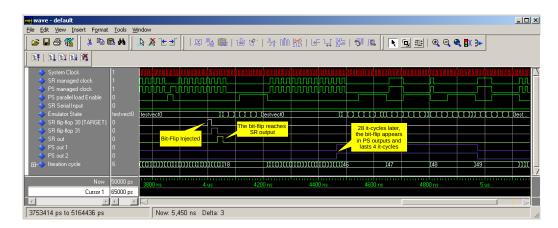

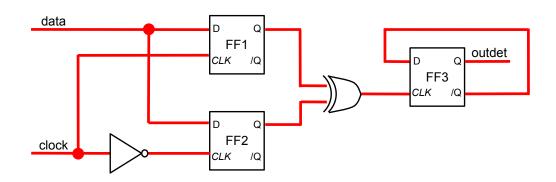

| 3.2 | Modelsim simulation of a bit-flip induced by pulsed laser irradiation of a digital circuit [85]. The method for error detection in this case was a coincidence detector designed to be a reduced version of FT-UNSHADES [3] for radiation experiments                                                                                                        | 73 |

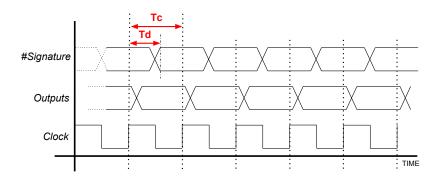

| 3.3 | Signature time delay Td compared to the system clock period Tc                                                                                                                                                                                                                                                                                               | 74 |

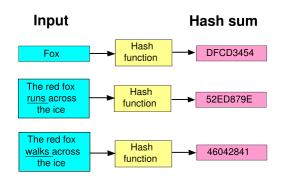

| 3.4 | Graph illustrating some features of hash functions                                                                                                                                                                                                                                                                                                           | 75 |

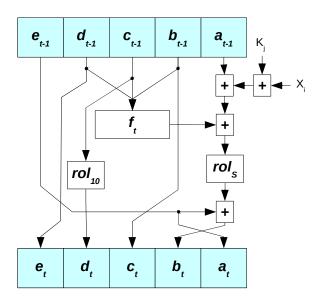

| 3.5 | A stage of the cryptographic hash function RIPEMD160                                                                                                                                                                                                                                                                                                         | 77 |

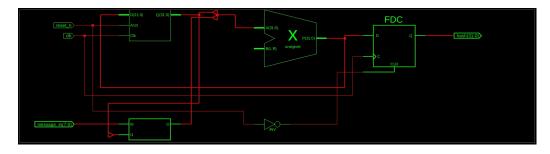

| 3.6 | Schematic view of the FNV module by the Xilinx Synthesis Tool.                                                                                                                                                                                                                                                                                               | 79 |

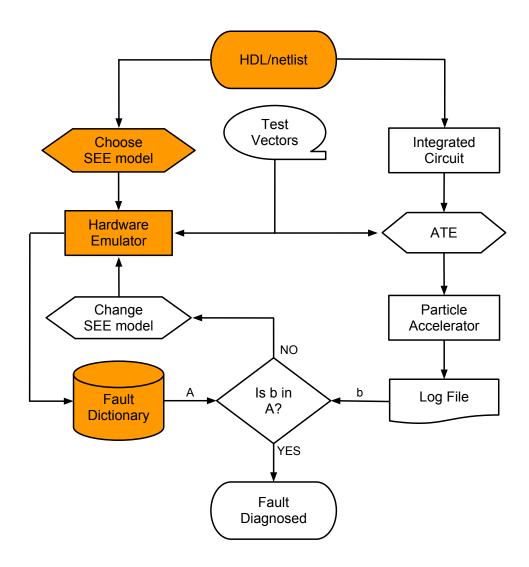

| 4.1 | Flow chart of the proposed approach. The left branch corresponds to the fault dictionary generation                                                                                                                                                                                                                                                          | 85 |

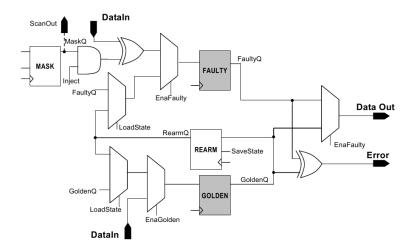

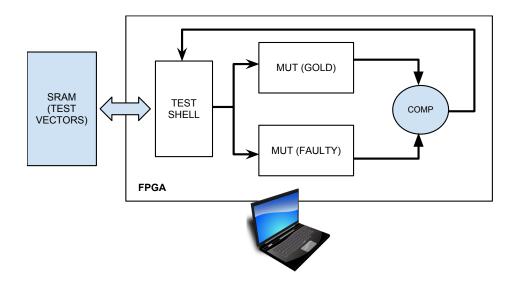

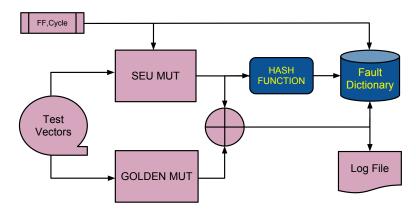

| 4.2 | Block Diagram showing integration of the Hash Function in the classic architecture of FTUNSHADES                                                                                                                                                                                                                                                             | 86 |

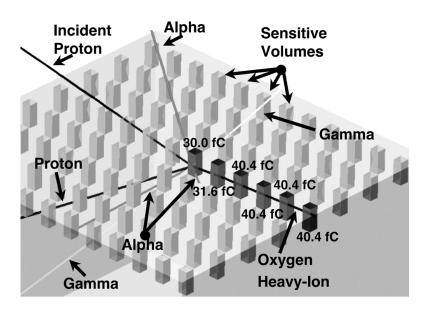

| 4.3 | Multi Bit Upset simulation by proton irradiation, triggering a nuclear reaction resulting in direct ionization of several sensitive volumes by an oxygen ion [106]                                                                                                                                                                                           | 90 |

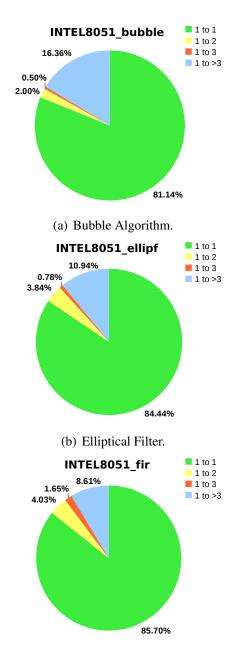

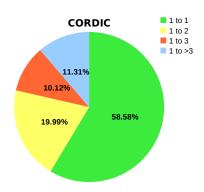

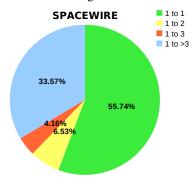

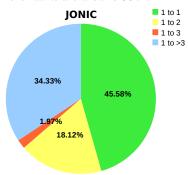

| 4.4 | (1/2) Failure percentage distribution attending to the number of possible faults involved for different programs running on the Intel 8051 processor. First sector to the right corresponds to failures diagnosed without uncertainty (1 to 1). The number of possible faults involved for a given failure is represented increasing clockwise up to 1 to >3 | 93 |

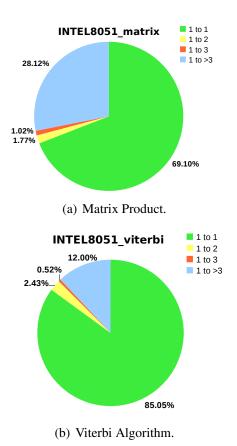

| 4.5  | (2/2) Failure percentage distribution attending to the number of possible faults involved for different programs running on the Intel 8051 processor. First sector to the right corresponds to failures diagnosed without uncertainty (1 to 1). The number of possible faults involved for a given failure is represented increasing clockwise up to 1 to >3 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.6  | Failure percentage distribution for different designs attending to the number of possible faults involved. First sector to the right corresponds to failures diagnosed without uncertainty (1 to 1). The number of possible faults involved for a given failure is represented increasing clockwise up to 1 to >3                                            |

| 5.1  | Flow chart of the proposed approach. The right branch corresponds to the radiation experiment                                                                                                                                                                                                                                                                |

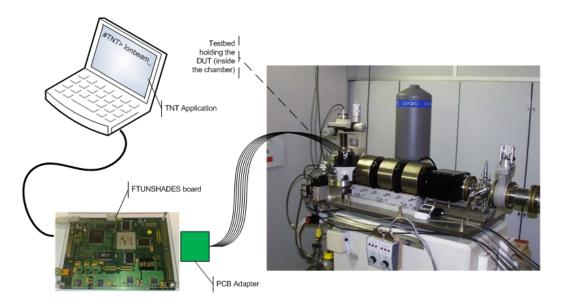

| 5.2  | Automated Test Equipment (ATE) / Test Fixture 100                                                                                                                                                                                                                                                                                                            |

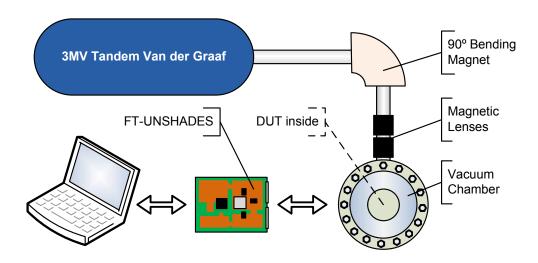

| 5.3  | Floor plan of the experimental setup at the CNA facilities 101                                                                                                                                                                                                                                                                                               |

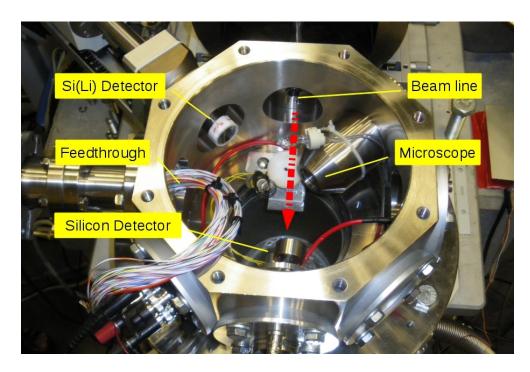

| 5.4  | Vacuum chamber at the nuclear microprobe line of the 3MV Tandem Van der Graaf Accelerator                                                                                                                                                                                                                                                                    |

| 5.5  | Top plate of the vacuum chamber at the nuclear microprobe line and target integrated circuit. The golden lid covering the silicon die is removed before irradiation                                                                                                                                                                                          |

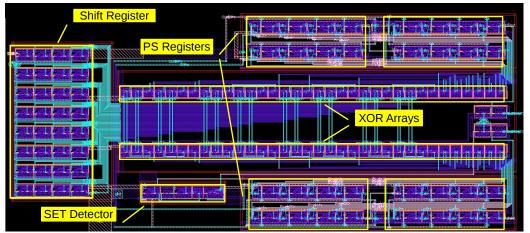

| 5.6  | Layout of one of the six replicas of the circuit under test 103                                                                                                                                                                                                                                                                                              |

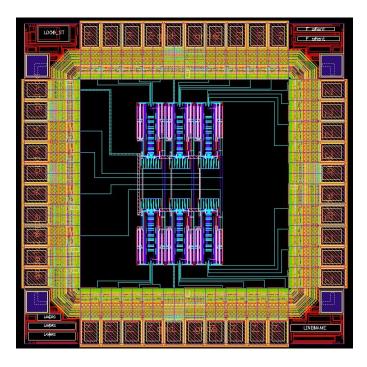

| 5.7  | JONIC. View of the target die featuring six replicas of the circuit showed in Figure 5.6                                                                                                                                                                                                                                                                     |

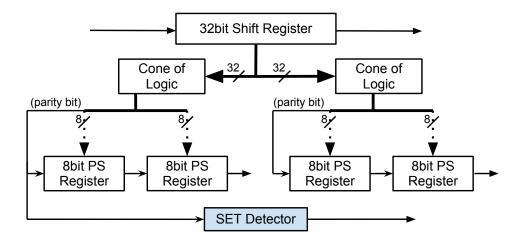

| 5.8  | Block diagram of the design under test. See text for a detailed description                                                                                                                                                                                                                                                                                  |

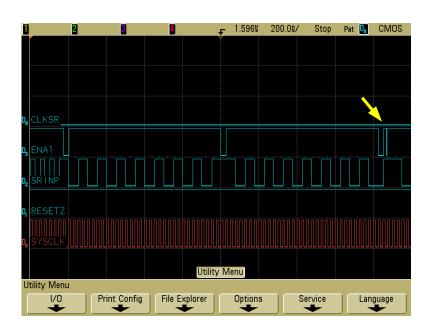

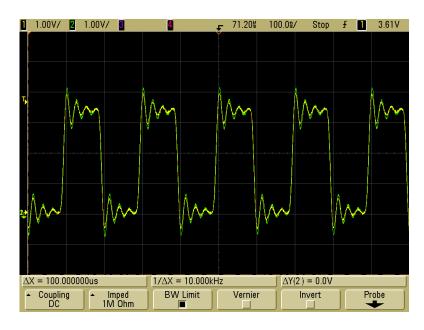

| 5.9  | Waveforms of input stimuli. A glitch is showed in the input data of the SR                                                                                                                                                                                                                                                                                   |

| 5.10 | Waveforms of input stimuli. A glitch appears in the signal "ENA"                                                                                                                                                                                                                                                                                             |

| 0.10 | that controls the parallel load of the PS registers 107                                                                                                                                                                                                                                                                                                      |

| 5.11 | Ringing in the clock signal in the DUT side                                                                                                                                                                                                                                                                                                                  |

|      | Simulated ionizing LET profile for 13 MeV Carbon ions striking a layered model of JONIC device                                                                                                                                                                                                                                                               |

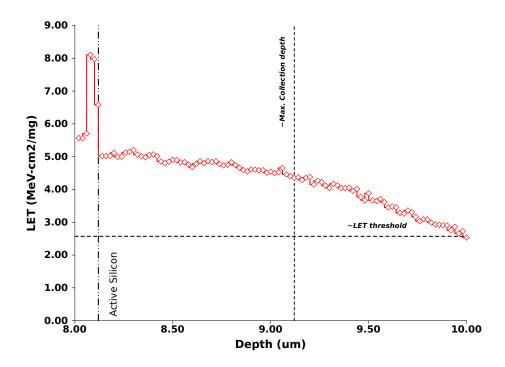

| 5.13 | Detail of the ionizing LET profile in Fig. 5.12 to show direct ionization in the active region of the silicon device                                                                                                                                                                                                                                         |

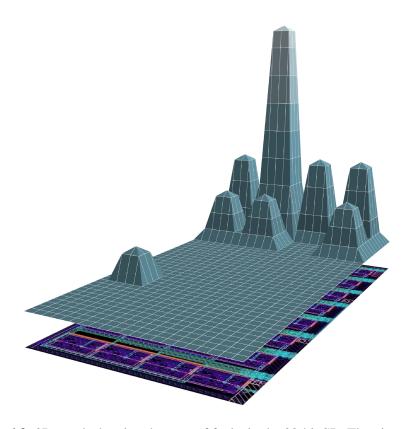

| 5.14 | Floor plan of the 32-bit Shift Register under radiation. Colored tiles represent possible patterns for MBU fault injection in order to get MBU fault dictionaries                                                                                                                                                                                            |

| 6.1  | Chart representing the FFs affected during irradiation of the 32b Shift Register                                                                                                                                                                                                                                                                             |

|      | Simi register                                                                                                                                                                                                                                                                                                                                                |

| 6.2 | Chart representing the interval of clock cycles in the workload        |

|-----|------------------------------------------------------------------------|

|     | affected during irradiation of the 32-bit Shift Register               |

| 6.3 | 3D graph showing the map of faults in the 32-bit SR. The picture       |

|     | in the base plane is the actual layout of the shift register 119       |

| 6.4 | Block diagram of the SET detector in JONIC                             |

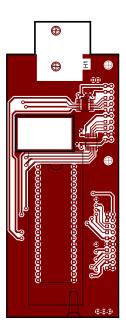

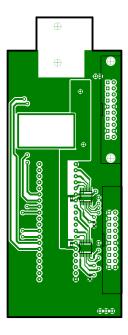

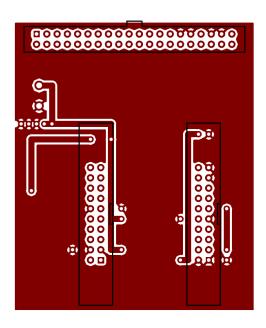

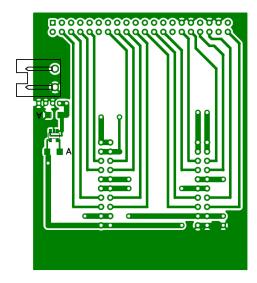

| B.1 | Top layer of the testbed holding the DUT inside the microprobe's       |

|     | vacuum chamber. Not to scale                                           |

| B.2 | Bottom layer of the testbed holding the DUT inside the micro-          |

|     | probe's vacuum chamber. Not to scale                                   |

| B.3 | Top layer of the pcb adapter for FT-UNSHADES connection to             |

|     | the microprobe's hermetically-sealed feedthrough. Not to scale 131     |

| B.4 | Bottom layer of the pcb adapter for FT-UNSHADES connection             |

|     | to the microprobe's hermetically-sealed feedthrough. Not to scale. 131 |

# **List of Tables**

| 1.1 | Total Ionizing Dose effects. Relevant primary and secondary radiations in different mission scenarios. Source: Handbook of Mitigation techniques against Radiation Effects for ASICs and FPGAs |   |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

|     | [32]                                                                                                                                                                                           |   | 27 |

| 1.2 | Displacement Effects. Relevant primary and secondary radiations in different mission scenarios. Source: Handbook of Mitigation                                                                 |   |    |

| 1.3 | techniques against Radiation Effects for ASICs and FPGAs [32] . Single Event Effects. Relevant primary and secondary radiations                                                                | • | 28 |

| 1.3 | in different mission scenarios. Source: Handbook of Mitigation                                                                                                                                 |   | 20 |

|     | techniques against Radiation Effects for ASICs and FPGAs [32]                                                                                                                                  | • | 29 |

| 2.1 | Layer model of an AMIS C5 device                                                                                                                                                               |   |    |

| 2.2 | Charge deposition in the layer model of an AMIS C5 device                                                                                                                                      | • | 59 |

| 3.1 | Implementation comparison of two different hash algorithms using Xilinx tools and FPGAs                                                                                                        |   | 80 |

| 4.1 | HDL Synthesis summary for the digital designs used for fault dictionary generation                                                                                                             |   | 91 |

# CHAPTER 1

## Introduction

"I think there's a little bit of sizzling here. Honestly, I can feel it.

The ions are flying back and forth."

— Regis Philbin

"Don't fear failure. Not failure, but low aim, is the crime. In great attempts it is glorious even to fail" — Bruce Lee

#### **Contents**

| 1.1 | Electronics and Ionizing Radiation              | 23 |

|-----|-------------------------------------------------|----|

| 1.2 | Radiation Effects on Semiconductors             | 26 |

| 1.3 | Hardness Assurance Against Radiation            | 35 |

| 1.4 | Fault Injection Techniques for Digital Circuits | 36 |

| 1.5 | Hardware Emulators for Fault Injection          | 39 |

| 1.6 | Revision of FT-UNSHADES                         | 46 |

| 1.7 | Scope of the Thesis                             | 49 |

## 1.1 Electronics and Ionizing Radiation

Ionizing radiation effects on semiconductors showed up for the first time on several in-flight anomalies detected in some missions of the early space race. These anomalies have been reported since the very beginning of the space era [110].

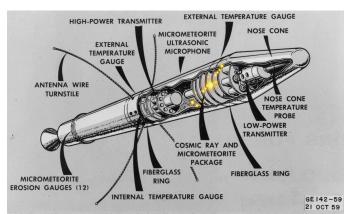

Figure 1.1: Explorer I technical details. Source: U.S. Army SMDC

In 1953, only six years after the invention of the bipolar transistor, Walter Kohn (awarded with the Nobel Prize on Chemistry in 1998) started researching the effects of energetic electrons on semiconductors at Bell Laboratories, under the supervision of William Bradford Shockley [37]. The aforementioned W. Kohn wrote: "My project was radiation damage of Si and Ge by energetic electrons, critical for the use of the recently developed semiconductor devices for applications in outer space". It is noticeable that the effects of radiation on semiconductor devices were a field of study three years before Bardeen, Brattain and Shockley were awarded with the Nobel Prize on Physics for the invention of the bipolar transistor. This anecdote is an example on how the race for the leadership on Space technologies boosted the research of radiation effects on semiconductors.

USA's first artificial satellite Explorer-I (see Figure 1.1) was launched on January 31, 1958. It carried aboard several Geiger detectors as part of an experiment proposed by J.A. Van Allen to measure cosmic rays in orbit. When the satellite reached an altitude of 900 km approximately, detectors mysteriously stopped counting particles. It was found out that Geiger counters had run into saturation detecting much higher flux of particles than expected in the outer space, so Van Allen thought it suggested regions of dense radiation surrounding the Earth. That day were discovered what we know today as Van Allen Belts.

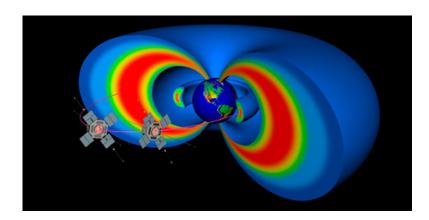

Almost two months later, in March 26, satellite Explorer-III was put into a very eccentric orbit to measure particle flux densities at a wide range of altitudes confirming the existence of the Van Allen Belts. Figure 1.2 represents the electromagnetic confinement of charged particles in the Earth's magnetic field which gives place to the so called Van Allen Belts. The picture is an artistic representation of the twins satellites of the Radiation Belt Storm Probes mission to be launched no earlier than Aug 23, 2012. There exist two belts consisting mainly of high energetic electrons (outer belt, 13000-60000 km) and a combination of protons and electrons (inner belt, 100-10000 km). There are other species of light

**Figure 1.2:** Twins RBSP satellites and Van Allen belts. Image courtesy of NASA/Johns Hopkins University Applied Physics Laboratory

ions like alpha particles but in a minor proportion. Earth's magnetic field confines charged particles from the outer space preventing them from reaching Earth's surface and acting as a shield against solar wind and cosmic rays. Recently it has been discovered [1] a belt of anti-protons generated by nuclear reactions of galactic cosmic rays interacting with atmosphere. At typical altitudes of civil aviation and below, the main radiation background consist of neutrons produced in nuclear reactions after cosmic rays or high energy protons penetrate the atmosphere and collide with molecules in it.

Few years after launching the Explorer-I, on July 10, 1962, NASA launched the AT&T's telecommunication satellite Telstar-1, designed and constructed at Bell Labs. Telstar-1 started the era of the telecommunications via satellite. A day before the launching of Telstar-1, on July 9, 1962, the U.S. government carried out a nuclear experiment in high altitude named Starfish Prime. The experiment consisted on the detonation of a thermonuclear bomb equivalent to 1.4 megatons of TNT at 400 km of altitude above the Pacific Ocean. Among other consequences, the detonation injected a big amount of electrons in the magnetic shield of the Earth, increasing considerably the effects of the Van Allen belts on the electronic devices aboard Telstar-1. After several failures during almost one year of operation, the satellite finally lost communications and go out of control on February 21, 1962. It was the first satellite to get lost due to the effects of ionizing radiation on the electronics aboard. Even though problems on Telstar-1 electronics were indirectly provoked by the action of humans, other anomalies on electronics caused by natural space radiation coming from solar wind, cosmic rays and Van Allen belts appeared since the beginning of space exploration. A data base of satellite failures on flight can be found on the web [97].

Density of particles is higher at the poles of the terrestrial magnetic axis, which

is 11° apart from the rotation axis of the Earth. Furthermore, both axes intersect near 500 km above the center of the Earth. This tilt and translation make the south pole of the inner belt closer to the Earth than the north pole originating a region known as the South Atlantic Anomaly (SAA) centered close to the coast of Brazil. The SAA is the area where the trapped particles are closest to Earth's surface, affecting considerably satellites operating at Low Earth Orbit (LEO) which usually switch off their electronics devices when passing through it.

But the problem of radiation on electronics is also present at sea level. First failures reported occurred in 1978 when Intel engineers detected several errors in the stored data of Dynamic Random Access Memory (DRAM) modules. Those effects were named *soft fails*. The origin of the radiation in this case were traces of radioactive elements in the chip encapsulation producing a yield of high energetic alpha particles.

Traditionally the major concerns on the effects of radiation on components and systems were for the space agencies, aerospace industries and for military industry involved in aerospace technologies. However, the increasing scale of integration of new technology nodes is bringing all the issues of radiation closer to other electronic industries like computer makers and automotive industry mainly, among others.

#### 1.2 Radiation Effects on Semiconductors

As far as this thesis is not directly related to the physics of semiconductors, the present chapter is intended to provide a brief introduction to different effects observed in semiconductor devices when irradiated with high energetic particles or photons, without setting out the solid state physics and equations behind them. Interaction of radiation with semiconductors can be classified in three main types attending to the physical effect involved. These types are:

- Activation by Nuclear Reactions

- Displacement Damage Effects

- Ionizing Effects

All these effects must be taken into consideration when designing for reliability in harsh radiation environments and it is not trivial to test hardening against one of this physical effects without being affected by another. For instance, experiments with protons to test soft error rates in a bank of memories must control carefully the fluence of the irradiation session, to prevent dose effects from appearing [78]. It is of great importance to know about side effects during radiation experiments

| Mission        | Important primary             | Important secondary        |

|----------------|-------------------------------|----------------------------|

| type           | radiations                    | radiation                  |

| LEO            | ·Trapped p and e <sup>-</sup> | X-rays from e <sup>-</sup> |

| LEO            | ·Solar p                      | A-lays Holli e             |

| High MEO       | ·Trapped e <sup>-</sup>       | X-rays from e <sup>-</sup> |

| Tilgii WiLO    | ·Solar protons                |                            |

| Low MEO        | ·Trapped e <sup>-</sup>       | V maria from a-            |

| LOW MILO       | ·Solar p                      | X-rays from e <sup>-</sup> |

|                | ·Low Energy trapped p         | X-rays from e <sup>-</sup> |

| GEO            | ·Trapped e <sup>-</sup>       |                            |

|                | ·Solar p                      |                            |

|                | ·Cosmic rays                  |                            |

| Interplanetary | ·Solar energetic              |                            |

| '              | particles                     | X-rays from e              |

| space          | ·Other planetary              |                            |

|                | trapped-belts                 |                            |

| Planetary      | ·Solar energetic              | Secondary p&n              |

| lander         | particles                     |                            |

**Table 1.1:** Total Ionizing Dose effects. Relevant primary and secondary radiations in different mission scenarios. Source: Handbook of Mitigation techniques against Radiation Effects for ASICs and FPGAs [32]

to account for unwanted phenomena like degradation in the performance of the device or errors coming from causes other than the targeted in the experiment. Discrimination of the errors observed at the outputs of irradiated circuits is a major issue and is one of the motivations of this thesis, as discussed in section 1.7.

The consequences of radiation on devices depend on several factors, as the absorbed dose or the energy of the incoming radiation. High radiation doses can lead to the complete destruction of the device or a permanent failure state only recoverable through annealing or hard resetting. Destructive or physical damage is out of the scope of this thesis and neither non-destructive effects like aging nor performance degradation due to total ionizing dose are considered after this preliminary chapter. Only Soft Errors due to single events will be considered and are suitable for the test technique developed in this thesis. The main radiation effects threatening the reliability of electronics during space missions are showed in Tables 1.1, 1.2 y 1.3.

Among ionizing effects, it is necessary to differentiate between accumulated dose effects and single-event effects in semiconductor technologies. Each type of them will be described separately later in this section.

Single-event Effects on Metal-Oxide-Semiconductor devices are of special interest and typical errors affecting Complementary-MOS transistors will be discussed in more detail due to the presence of this technology in today electronics.

| Mission        | Important primary       | Important secondary |

|----------------|-------------------------|---------------------|

| type           | radiations              | radiation           |

|                | ·Trapped p              |                     |

| LEO            | ·Trapped e <sup>-</sup> | Secondary n         |

|                | ·Solar protons          |                     |

|                | ·Trapped p (low MEO)    |                     |

| MEO            | ·Trapped e <sup>-</sup> | Secondary n         |

|                | ·Solar p                |                     |

|                | ·Low Energy trapped p   |                     |

| GEO            | ·Trapped e <sup>-</sup> | Secondary n         |

|                | ·Solar p                |                     |

|                | ·Cosmic rays            |                     |

| Internlenatory | ·Solar energetic        |                     |

| Interplanetary | particles               | Secondary n         |

| space          | ·Other planetary        |                     |

|                | trapped-belts           |                     |

| Planetary      | ·Cosmic rays            |                     |

| lander         | ·Solar energetic        | Secondary p&n       |

| Tanuci         | particles               |                     |

**Table 1.2:** Displacement Effects. Relevant primary and secondary radiations in different mission scenarios. Source: Handbook of Mitigation techniques against Radiation Effects for ASICs and FPGAs [32]

### 1.2.1 Activation by Nuclear Reactions

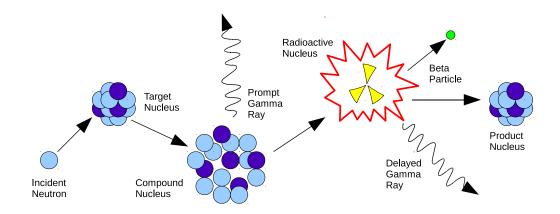

Stable nuclei exposed to a flux of energetic particles are candidate to go unstable and radioactive due to nuclear reactions. Particle like protons, neutrons or ions can strike a stable nucleus and remove some nucleons by inelastic scattering. Also low energy neutrons can be captured by a nucleus making it unstable. These nuclei decay by emission of radiation usually in the form of positrons, that can ionize the surroundings in what is a sort of indirect ionization (see Figure 1.3).

There are a variety of possible nuclear reactions with a corresponding cross section<sup>1</sup> depending on the incident particle and the targeted nucleus but the most common in space environments are those produced by high energy protons. Ionization from secondary particles like neutrons are specially important in thick materials.

The most important source of activation is an intensive proton flux located at altitudes of inner Van Allen Belt's equator, with energies ranging from 30 to 400 MeV. For other altitudes, cosmic rays are the leading source of activation and for interplanetary distances solar protons dominate [44]. Except for the case of

$<sup>^{1}</sup>$ The concept of cross section is widely used in nuclear physics to measure the probability of a given nuclear interaction and is measured in barns ( $10^{-28}m^{2}$ ). The cross section is the equivalent area of the whole target nucleus area producing a given reaction.

| Mission<br>type      | Important primary radiations                                           | Important secondary radiation     |

|----------------------|------------------------------------------------------------------------|-----------------------------------|

| LEO                  | ·Trapped p ·Solar energetic particles ·Cosmic rays                     | Secondary n                       |

| MEO                  | ·Trapped p ·Solar energetic particles ·Cosmic rays                     | Secondary n                       |

| GEO                  | ·Solar energetic particles ·Cosmic rays                                | Secondary n                       |

| Interplanetary space | ·Cosmic rays ·Solar energetic particles ·Other planetary trapped-belts | Secondary n                       |

| Planetary<br>lander  | ·Cosmic rays<br>·Solar energetic<br>particles                          | Secondary n,p<br>and heavier ions |

**Table 1.3:** Single Event Effects. Relevant primary and secondary radiations in different mission scenarios. Source: Handbook of Mitigation techniques against Radiation Effects for ASICs and FPGAs [32]

Figure 1.3: Activation by capture of slow neutron

neutrons with no direct ionization, dose due to activation by nuclear reaction is smaller than dose due to primary particle ionization.

#### 1.2.2 Displacement Damage Effects

When particles pass through semiconductors, elastic collisions with atoms in the crystal lattice can result in displacement effects. Eventually the hit of an ion results in the displacement of one lattice atom leaving a vacancy. These defects in the crystal lattice affect the periodicity of the crystal structure, allowing new energy states or energy traps in the band gap for the electrons in the semiconductor, affecting charge carriers mobility. This kind of structural damage is quantified by the Non-Ionizing Energy Loss (NIEL) related to the material for a given incident ion. Macroscopically, the effect associated to displacement damage is a degradation in the electrical response of the device like increase in leakage currents or gain deterioration in bipolar devices. A complete survey on displacement damage effects on silicon can be found in [102].

#### **1.2.3** Total Ionizing Dose

When ionizing radiation pass through the bulk of a semiconductor device, a number of electron-hole pairs are created. The so generated charged particles quickly recombine as they move away by drift-diffusion mechanisms. Charge built up in dielectric layers and interfaces however is not removed easily, mainly the positive charge that remain trapped for long time. Long term exposition to radiation led to the well-known ionizing dose effects. In CMOS devices, charge generated by ionizing radiation in the gate oxide is the responsible for aging or degradation of the electrical characteristics of the device. A common effect in CMOS transistors is a progressive shift in the threshold voltage that increase with dose and directly impact noise margins in digital circuits.

It is important to note that from 130 nm CMOS processes and on, the gate oxide is thin enough to prevent trapped charge from appearing due to quantum tunnel effect. Hence, total dose in modern devices is not so critical and fluence must not be a serious problem in Single Event Effect (SEE) radiation experiments [10].

There are other effects related to rapid increase in the **dose rate** resulting in the injection of big amounts of electron-hole pairs in the semiconductor. The subsequent effects are mainly transient excursion in voltage signals.

#### 1.2.4 Single-Event Effects

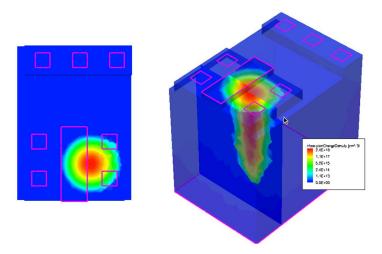

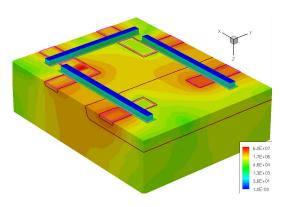

These effects are particular cases of ionization where the strike of a single ion or neutron on the active areas of a semiconductor can lead to what is also known as Single-event phenomena (SEP). Depending on the sensitivity of the device, the resulting effect can destruct it or corrupt in some sense its functionality. Figure 1.4 illustrates the ionization track along the first microns of the bulk region in a MOS transistor.

The charge deposition by an ionizing particle passing through a MOS device provokes fast current fluxes in neighbor contact nodes, which lead to transient voltages in capacitive loads. The current pulse is usually modeled like a double exponential with parameters obtained heuristically from experiments, as seen later in this chapter.

The integration of this current pulse is the charge collected and is directly related to the charge deposited by the incident particle. The amount of charge collected is the key parameter determining the behavior of the circuit, but also the shape of this current is influencing as can be read in [41]. When considering Single Event Upsets (SEU) in SRAM cells, there is a threshold value for the minimum charge deposited by the ionizing particle giving place to the flip of the stored bit, this values is known as **critical charge** ( $Q_{crit}$ ) [28]. High-scaled technologies feature low critical charge, this way lowering more and more the ion linear energy transfer (LET) threshold required to achieve a bit-flip. On the other side, the sensitive volume is also lower in modern technologies balancing the effect of decreased ( $Q_{crit}$ ) and giving place to a repertory of single event effects [12].

The Dictionary of Terms for Solid State Technology [48] includes the following definitions adopted in this thesis and introduced here for the sake of language accuracy in the rest of the document:

- SEB Single-event Burnout. An event in which a single energetic-particle strike induces a localized high-current state in a device that results in catastrophic failure. This effect is associated normally to power MOSFET devices.

- SEFI Single-event Functional Interruption. A soft error that causes the component to reset, lock-up, or otherwise malfunction in a detectable way, but does not require power cycling of the device (off and back on) to restore operability, unlike single-event latch-up (SEL), or result in permanent damage as in single event burnout (SEB).

- SEGR Single-event Gate Rupture. An event in which a single energetic-particle strike results in a breakdown and subsequent conducting path through the gate oxide of a MOSFET.

**Figure 1.4:** Technology Computer Aided Design (TCAD) simulation of ionization track in a MOS transistor after ion strike at normal incidence [33].

- SEH:SHE Single-event Hard Error. An irreversible change in operation resulting from a single radiation event and typically associated with permanent damage to one or more elements of a device (e.g., gate oxide rupture).

- SEL Single-event Latch-up. An abnormal high-current state in a device caused by the passage of a single energetic particle through sensitive regions of the device structure and resulting in the loss of device functionality.

- SET Single-event transient. A momentary voltage excursion (voltage spike) at a node in an integrated circuit caused by a single energetic-particle strike.

- SEU Single-event upset. A soft error caused by the signal induced by a single energetic-particle strike.<sup>2</sup>

- MCU Multiple-cell upset. A single event that induces several bits in an IC to fail at the same time.

- MBU Multiple-bit Upset. A multiple-cell upset (MCU) in which two or more error bits occur in the same word.

In the context of this thesis, the only events of concern are those provoking soft errors or non-destructive effects.

<sup>&</sup>lt;sup>2</sup>In some publications the term SEU also covers latch-up events

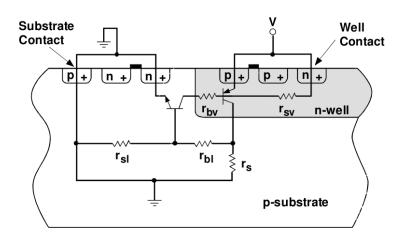

**Figure 1.5:** Parasitic resistors and transistors in CMOS structure giving place to unwanted thyristor eventually triggered by ion strike.

#### • Single-event Latch-up.

Single-event latch-up usually leads to destruction of the affected device if it is not unbiased immediately by an anti-latch-up circuit or similar. In CMOS technology, the charge generated along the ion track can trigger a parasitic thyristor between the power rails (see Figure 1.5) that only can be switched off by opening the supply current path. In some circumstances, it is possible that, due to serial resistance from other parts of the circuit, the consumption is limited and the device is not burned out. These cases are commonly detected as stuck-at bits tied to a fixed voltage.

It is worth noting that single-event latch-up can't show "latchup windows" [49] as in the case of dose rate irradiation [9] from gamma ray for example.

#### • Single-event Transient.

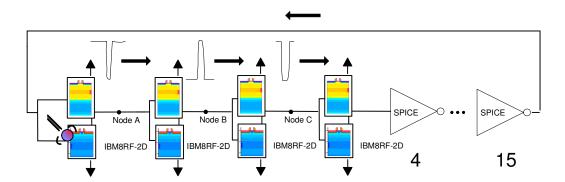

The immediate effect after an ion strikes a semiconductor device is a fast current appearing in the affected node. In CMOS devices this current either charges or discharges the capacity associated with the node giving place to a rapid momentary change in the voltage [24]. These voltage glitches behave as pulses propagating through combinational logic to reach sequential elements like flip-flops. Along the path, these pulses eventually get broader by a phenomenon known as Propagation Induced Pulse Broadening or PIPB Effect [68]. This effect makes transient pulses more likely to be captured by a clock edge when reaching flip-flops, corrupting one or more elements. Figure 1.6 represent the simulated effect in a chain of inverters.

**Figure 1.6:** Propagation Induced Pulse Broadening effect after a transient voltage excursion in a node of a chain of inverters. Schematic for mixed-mode simulation [68].

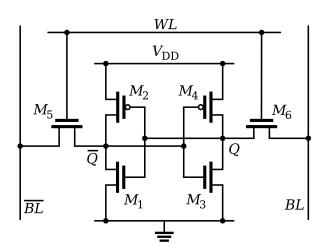

Figure 1.7: Schematic of a 6-transistor SRAM cell.

#### • Single-event Upset

The existence of SEU errors was discovered in 1975 [16] although were predicted back in 1969 [112]. The most well known device upset is probably the event of a ion striking a SRAM cell. The upset consists of flipping the logical state stored in the cell. The flipping of a bit is not necessarily an error, since the Flip-Flop (FF) can be rewritten before the corrupt data propagates to other parts of the circuits. Figure 1.7 is the schematic of a typical SRAM cell with two inverters connected back-to-back in a metastable configuration. The transient charge unbalance created by an ion strike can change the state of Q. A Technology Computer Aided Design (TCAD) 3D model of the SRAM cell is showed in Figure 1.8

**Figure 1.8:** 3D model of a 6-transistor SRAM cell for TCAD simulation [33]

As discussed later in Section 1.7, the present thesis focuses on test methods for soft errors. Hence for the rest of the document all the references to errors, test methods, techniques or whatever other topics, must be understood regarding soft errors in semiconductor devices. Dose effects on semiconductors are out of the scope of this Thesis.

### 1.3 Hardness Assurance Against Radiation

Hardness assurance of electronic parts is a major issue in aerospace industry where semiconductor devices are supposed to be exposed to harsh radiation environments. The Space Product Assurance standard ECSS-Q-ST-60-02C for ASIC and FPGA development establishes a comprehensive set of guidelines for designers including requirements for hardness assurance against radiation. Also the ESA Handbook on Space engineering product assurance entitled: "Techniques for Radiation Effects Mitigation in ASICs and FPGAs" deal with validation methods for the mitigation of radiation effects. Nowadays in space missions, radiation engineers have to get involved from the early stages of the project. As CMOS technology nodes go deeper and deeper into the nanometer scale, other industries with high reliability constraints at ground level are also concerned about environment radiation and usually maintain task forces in the field of radiation hardness validation. The techniques and procedures developed in this thesis are intended to be a contribution in this field.

In computer industry for example, equipments deploying big amount of memory banks such as racks of servers are statistically more vulnerable and traditionally implemented mitigation techniques against radiation. The higher and higher integration and density of memory cells make these devices the most vulnerable, and the most significant contribution to the Soft Error Rate (SER) in System on

Chip (SoC) devices. This point explains why memories have been the "laboratory rats" for researchers, with tons of papers on TCAD and Spice simulations, radiation tests for different species of ions and neutrons, design best practices, etc. Serve as an example the widely tested 6-transistor SRAM (Static Random Access Memory) cells.

As mentioned in Section 1.1, soft errors in commercial electronic devices were reported more than 30 years ago, however the history of standards for commercial semiconductor industry is much more recent. JEDEC standard JESD89A "Measurement and Reporting of Alpha Particle and Terrestrial Cosmic Ray-Induced Soft Errors in Semiconductor Devices" is the main document regarding testing of Soft Error Rates of integrated circuits and reporting of results. The Automotive Electronics Council (AEC) published requirements for common electrical component qualification. Document AEC-Q100-Rev-G "Failure Mechanism Based Stress Test Qualification for Integrated Circuits" specifies the cases when integrated circuits require SER testing and refers to the JESD89 standard for the test method. Also DO-254 and IEC/TS 62396 are examples for standards of the avionic industry considering radiation effects issues.

Space and military agencies started standardization and certification procedures for electronic parts hardness assurance establishing the guidelines for radiation testing as in the ESA/SCC Basic Specification No.25100 from the European Space Agency (ESA) or the MIL-STD-750 from the Department of Defense of the United States of America.

There are several papers on design for soft error mitigation, for example [79], with several approaches to enhance robustness against soft error due to radiation.

Testing integrated circuits against environmental radiation is an issue of concern in modern electronic technologies and researchers all over the world are more and more interested in. As long as new hardness strategies and procedures develop, big effort need to be made on the methods to test these advances

### 1.4 Fault Injection Techniques for Digital Circuits

Fault injection plays a key role in this thesis as introduced in section 1.3. In the SER test methodology presented in this thesis, a preliminary massive fault injection campaign is required to generate a full-coverage fault dictionary for the Circuit Under Test (CUT). The more complete the fault dictionary, the more likely to diagnose faults in the radiation experiment. Of course, covering the whole available cause of errors in a medium-size digital circuit can be a very time consuming task, in much cases unaffordable. Hence, the fault injection platform must be chosen to optimize the generation of the fault dictionary.

There is a wide spectrum of techniques aimed to inject faults in digital circuits

and of course there is no universal platform suitable for all purposes, generally different needs require different fault injection platforms. The main use of these platforms is in validating mitigation techniques at the design stage as in [53]. A well-established classification from text [13] for fault injection techniques is adopted in this document to introduce the state of the art in this field.

Fault injection (FI) platforms must optimize preferably *Controllability*, *Observability*, *Intrusiveness*, *Velocity* and *Cost*. Controllability in this context is the ability to induce faults in all the elements in the target susceptible to fail. Observability is the capacity to observe in time and space the internal and external state of the target. Intrusiveness is the degree of target instrumentation by the injector, it is desirable to have as less intrusiveness as possible. Velocity and Cost must be also taken into consideration. Most of FI techniques are in a tradeoff between these properties and have a limited field of application. The use of these tools is traditionally in the design stages of integrated circuits and in tests of reliability or fault tolerance to faults induced by radiation.

Induced faults in fault injectors are models of the physical fault suitable for a determined level of abstraction, except in the case of ion beam induced faults. In the Register Transfer Level (RTL), the "bit-flip" model of error is of great interest when dealing with soft errors in digital circuits. Except by SET in analog circuits, all soft-SEE can be modeled using the bit-flip model. So this is an atomistic building block to model more complex effects like MCU or MBU.

The bit-flip model is essential in the development of this thesis and is the model adopted for most of fault injectors used to model soft errors. The concept is quite simple and consist of flipping the logic state of a single bit in a given clock cycle. Other models are the stuck-at fault and the bridging. Stuck-at model consists of forcing either logic high or low value in a given port, bit or flip-flop in the Device Under Test (DUT). Bridging is induced by forcing a single port, bit or flip-flop to the logical value of an adjacent port, bit or flip-flop.

#### 1.4.1 Hardware-Based Fault Injection: HWFI

Hardware Fault Injection requires a hardware architecture (in most cases ad-hoc hardware) suitable for fault injection and storage of the resulting effects. For these techniques a working prototype of the DUT must be available, so that these techniques are not to be used in the early stages of the design. There are several platforms for fault injection based on the stuck-at or bridging fault models. The usual way to inject these faults is by sticking or bridging some pins in the prototype, so that these methods are referred to as "pin-level" fault injection. Examples of this approach are MESSALINE [8] developed by the LAAS Research Center at Toulouse (France) and RIFLE [58] developed by the University of Coimbra (Portugal).

Another approach is to inject faults by mean of ion beams generated in a particle accelerator (low controlability) which is in fact the most appropriate test to reproduce the operating conditions in a harsh radiation environments (except by in-flight radiation experiments, of course). For these purposes, the TIMA Laboratory developed THESIC [111] and THESIC+ [34] for radiation testing of Integrated Circuits. To some extent, all radiation test facilities offer a basic testbed for the user to setup an experiment. Intense pulsed laser is a widely used alternative to particle accelerators to inject faults in integrated circuits using backside irradiation with good results [62].

The main advantage of HWFI techniques is in the execution time of injection campaigns (not so the setup time) since the DUT is clocked at hardware speed. There is also the possibility of inducing faults in some blocks that are not accessible by other methods. Some withdraws are usually rigidity, limited observability and poor controlability.

#### 1.4.2 Software-Based Fault Injection: SWFI

These techniques don't need a final prototype of the DUT and are mainly aimed to test complex systems like microprocessors or microcontrollers. The observability and controllability is normally limited to user or context registers and the targets in this case are code blocks, subroutines or applications running in a given microprocessor of interest. The code under execution is modified to change the normal operation of the system in the same way that it would happen when affected by radiation. It is possible in some cases to inject faults in several levels of abstraction, from RTL or failures at the memory elements, to errors in applications like packet duplication in communication networks. A common approach [51] is to include a Code Emulated Upset (CEU) that deliberately corrupts data in a given memory address and is triggered by an interruption request. One of the disadvantages of these techniques are a speed penalty due software execution. There are several mature platforms available like FERRARI [52] or XCEPTION [59].

## 1.4.3 Simulation-Based Fault Injection: SBFI

A model of the Device Under Test is simulated in a computer and faults are injected by changing logic levels in the model during simulation. These techniques allow for fault tolerance studies in the design stage of the DUT, when still no prototypes are available. Of course, an HDL model of the DUT must be available, which is not always possible. The main advantage is a great observability and controllability, and the major drawback is the penalty in velocity due to all the system is software-based. These approaches provide high observability and controllability.

The most commonly used technique consists of simulating HDL models of the DUT. Among the SBFI platforms we can mention MEFISTO [17], AMATISTA [35] or the "SEU Simulation Tool" [36] developed by the European Space Agency (ESA) and nowadays exploited by the Antonio de Nebrija University for fault tolerance analysis [94].

#### 1.4.4 Hybrid Techniques: Hardware Emulation

Hardware emulation is a type of hybrid technique combining the advantages of SBFI and HWFI techniques. The properties of FPGA devices make them very attractive to be used for hardware emulation. The use of FPGAs allows to synthesize an (VHDL) model of the DUT to test it at hardware speeds, moreover fault injection can be performed via reconfiguration or instrumentation of the DUT (as usually in HWFI techniques). FPGA-based tools are versatile and fault injection campaigns can be highly controllable with full access to all the registers in the design. Cost is not an issue due to constant decrease of prices and enhancement of FPGA technologies. Execution times are improved several order of magnitude in comparison to SWFI techniques. Observability is usually a tradeoff to time, but if time is not a major constraint, full observability is usually achieved. Primary classification in hardware emulation techniques is based on the injection mechanism, differentiating between fault injection by reconfiguration and instrumented fault injection.

Due to the full controllability and high fault rates achieved, hardware emulation is the proper approach for the purpose of this thesis where massive fault injection campaigns are demanded for generating fault dictionaries. Next section is dedicated to a more in-depth analysis of hardware emulation techniques.

## 1.5 Hardware Emulators for Fault Injection

This section is a revision of several techniques for hardware emulation based on SRAM FPGAs. Firstly, two different approaches are introduced with the different variants that are commonly encountered in the specialized literature. Afterward a first classification is done of the different fault injection platforms operating in the context of a FARM [8] campaign. The FARM model implies the selection of the set of faults to be injected (F: Faults), establishing the set of test vectors to stimulate the system to be evaluated (A: Activation), compilation of observations (R: Readouts) and measuring the reliability of the system (M: Measurements).

The field of application of hardware emulators is in the RTL level of abstraction which turns to be a powerful scenario as discussed in the following.

Actual FPGAs allow for the emulation of systems made of thousands or even millions of equivalent logic gates and can be used to setup fault injections experiments in systems from the proper HDL description. Fault injection techniques in FPGAs also allow for a more accurate and flexible analysis than that from HWFI techniques, since it is possible to inject faults in a controlled manner in all the registers of the design with similar execution times. There are of course a remarkable advantage in execution times when comparing with SBFI techniques [54]. All the platforms described in this section use the bit-flip model but most of them can be tuned to also inject stuck-at faults and others. Stuck-at faults particularly are of great interest for dependability testing community and early works on hardware emulation were based on that fault model [20, 45].

Fault effects are generally classified with the following criteria:

- Failure. Fault induces a wrong behavior observed at the output ports during the execution of the test.

- Latent Fault. Fault modifies the internal logical state of the system with no effects at the outputs during the execution of the test.

- Silent Fault. Fault is removed by the design itself. The affected register is overwritten before fault propagates.

The duration of a fault injection campaign can be estimated by taking into account the number of flip-flops (FF) in the circuit and the number of clock cycles in the whole test-bench (C). If one wants to inject systematically in each and every single FF in the DUT, then the product FFxC is a low limit for the time in clock cycles required to complete such a campaign. Moreover, for systematic campaigns with faults induced in every FF but also in every clock cycle, the low limit is given by FFxCxC clock cycles<sup>3</sup>. As an example, for a set of test vectors with 10<sup>6</sup> clock cycles and a DUT with 10000 FFs, clocked to 10 Mhz, the resulting systematic campaign would take 31.7 years. So that test-benches and DUT size must be constrained to the capacity of the platform to be used. Anyway, speed optimization is achieved only by mean of hardware emulation. Chapter 4 deals in detail with fault injection works done for this thesis. There exist basically two different approaches to inject faults in systems emulated in FPGAs attending to the injection mechanism: **Instrumented Fault Injection** and **Fault Injection by Reconfiguration**.

<sup>&</sup>lt;sup>3</sup>There are platforms able to lower this limit by saving the whole state of the system before injection, resuming the emulation from this saved state for subsequent injections.

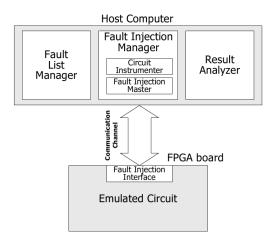

**Figure 1.9:** Schema with main blocks in an emulator system managed by a host computer. Source: [21]

#### 1.5.1 Instrumented Fault Injection

Instrumentation consists of adding specific injection blocks to the original HDL model of the DUT to have external access to the elements to be attacked by mean of extra ports. There are several tools based on this concept that have proven to be successful. Instrumentation, as it implies modification on the design to be tested, is intrusive, which is probably the major disadvantage of this approach. Moreover there is an area overhead that can't be neglected if injection is required to cover all the flip-flops of the design. On the other hand, execution times in these approaches is minimized and very high fault rates are achieved. The fault injection blocks are attached to FFs in the design and connected in a daisy chain or *scan-path*. The stimuli test vectors are stored in a buffer controlled by the host. Emulator applies test vectors to the instant previous to injection and then resume the execution to the end of test vectors. Failure is detected by comparison of DUT outputs with error-free outputs. Whenever the error is detected and classified before the end of the test vectors, the host stops the run. Fault injection rates reported are really high as in [21] where a score of  $100~\mu s$ /fault is achieved.

#### 1.5.1.1 Emulation Systems Depending on a Host

Researchers at the Instituto Politecnico di Torino developed a platform for instrumented fault injection [22] with a host computer managing the fault list, operation and result evaluation during the campaign. This architecture is depicted in Figure 1.9. *Fault Injection Manager* or FIM is the core of the system and is in charge of picking up faults from a fault list (optimized by the *Fault List Manager* which is able to perform fault collapsing [14] to some extent, to avoid faults leading

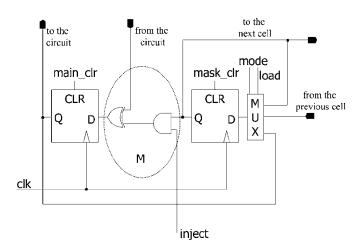

**Figure 1.10:** Fault Injector architecture for each FF in the design. Source: [22]

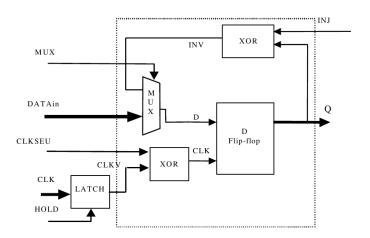

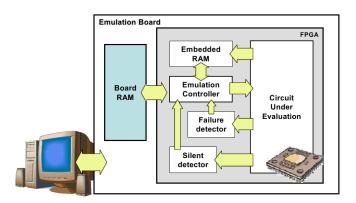

to identical results), fault injection in the emulated circuit and evaluation of the emulation results.