# **Integrated Circuit Implementation of Fuzzy Controllers**

J.L. Huertas, Fellow IEEE, S. Sánchez-Solano, I. Baturone\*, and A. Barriga

Dept. de Diseño de Circuitos Analógicos. Centro Nacional de Microelectrónica. Edificio CICA, Avda. Reina Mercedes s/n, 41012-Sevilla (Spain).

\* Author for correspondence

Phone # 34-5-4239923 FAX # 34-5-4624506 email: lumi@cnm.us.es

### **Abstract**

This paper presents mixed-signal current-mode CMOS circuits to implement programmable fuzzy controllers that perform the singleton or zero-order Sugeno's method. Design equations to characterize these circuits are provided to explain the precision and speed that they offer. This analysis is illustrated with the experimental results of prototypes integrated in standard CMOS technologies. These tests show that an equivalent precision of 6 bits is achieved. The connection of these blocks according to a proposed architecture allows fuzzy chips with low silicon area whose inference speed is in the range of 2 Mega FLIPS (fuzzy logic inferences per second).

## I.- Introduction.

The use of fuzzy systems is widespread, mainly in the control field. Most fuzzy microcontrollers presently used in industrial applications are digital implementations. However, fuzzy logic is intrinsically more like the multivalued and continuous analog world than the digital one. In addition, fuzzy systems process this continuous information in a massively parallel way. Regarding these features, analog implementations may offer a better 'silicon area / inference speed' ratio.

Adapting fuzzy concepts to meet microelectronics constraints, in terms of both architecture and circuitry, has been a major issue in this field. In particular, the selection of the inference method greatly determines the resulting hardware. Among the various inference methods reported in the literature, the singleton or zero-order Sugeno's method is very adequate for hardware implementations as well as to ensure efficient control [1]. A singleton fuzzy controller chip is adapted to solve a control problem by defining its rule base, that is, the parameters describing each antecedent's membership function and the parameter representing the singleton consequent. In the case of analog fuzzy chips, these parameters can be fixed prior to chip fabrication [2,3] or afterwards through programming [4-6].

This paper presents mixed-signal IC techniques to implement programmable singleton fuzzy controllers. Current-mode analog circuits are used to provide a high functional efficiency in the realization of the basic operations required (addition/subtraction, bounded difference, and division). Mixed-signal circuits, namely current-mode D/A converters (DAC), are used to implement the scaling operation and to offer the advantages of the digital world, such as ease of programming and capability of long-term storage for the controller parameters. Section II identifies the functional blocks required. The CMOS circuits to implement these blocks are presented in Section III. Their static and dynamic behavior are analyzed and illustrated with experimental results of prototypes integrated in standard CMOS technologies. These circuits constitute a set of analog building blocks (input-output compatible) that facilitates the design of programmable fuzzy chips according to the architecture discussed in Section IV.

### **II.-** Functional blocks.

The knowledge base of a singleton fuzzy controller consists of IF-THEN rules that relate fuzzy antecedents with crisp or singleton consequents. In the case of single-output controllers, these rules assume the form:

Rule i: IF

$$x_1$$

is  $A_I^i$  and ... and  $x_u$  is  $A_u^i$  THEN y is  $c_i$

where  $x_j$  (j=1,..., u) are controller input signals, y is the output,  $A_j^i$  are linguistic values defined by fuzzy sets on the input universe of discourse, and  $c_i$  are crisp values.

The global output is obtained from an average in which each consequent value,  $c_i$ , is weighted by the activation degree,  $h_i$ , of its corresponding rule:

output =

$$\frac{\sum_{i} h_{i} \cdot c_{i}}{\sum_{i} h_{i}}$$

(1)

The following functional blocks are necessary for hardware implementation of this algorithm:

- (a) Membership function circuits (MFCs) whose transfer characteristics represent the antecedents' membership functions. They provide the degree of matching between the controller input signals and the antecedents of the rules.

- (b) Minimum/maximum circuits (MIN/MAX) that connect the antecedents of a rule to compute its activation degree.

- (c) Consequent scaler circuits (CONSs) that weight the singleton consequent with the activation degree.

- (d) A divider (DIV) to obtain the overall output.

The use of current-mode techniques allows saving adder circuits to calculate the values of the numerator and denominator in Equation (1). They are obtained simply by leading the currents representing  $h_i$  and  $h_ic_i$  to a common low-impedance node.

### **III.-** CMOS implementation of functional blocks.

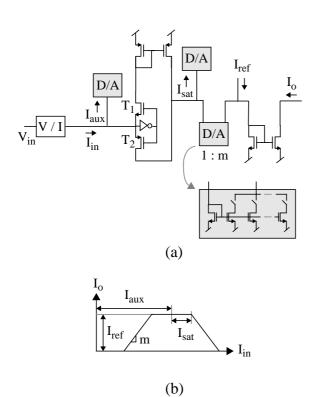

<u>Membership Function Circuits</u>: Figure 1a illustrates the schematic of an MFC which allows implementing triangular and trapezoidal membership functions (Figure 1b). These are defined by the parameters  $I_{aux}$  (central point of the fuzzy label),  $I_{sat}$  (saturation of the trapezoidal function), and m (the slope of the membership function), according to the expression:

$$MFC(I_{in}) = I_{ref} \Theta m( | I_{in} - I_{aux} | \Theta I_{sat})$$

(2)

where  $I_{ref}$  is the maximum degree of pertenence and  $\Theta$  is a rectification or bounded difference operator, defined as:

$$a \Theta b = \begin{cases} a - b & \text{if } a > b \\ 0 & \text{otherwise} \end{cases}$$

Digital programmability is added in a rather straightforward manner via current-mode DACs that are based on current mirrors. Two of them fix the values of  $I_{aux}$  and  $I_{sat}$ , while another performs as a programmable multiplier to implement the scaling by m. The diode-connected input transistor of this DAC also implements the bounded difference with  $I_{sat}$ .

The combination of  $T_1$ ,  $T_2$ , and the PMOS current mirror (proposed in [7]) is the simplest solution we have found to implement the absolute value operation in Equation (2). It avoids replication of  $I_{in}$  or  $I_{aux}$ , thus saving area and power consumption. What may cause systematic errors in the generation of  $I_{in}$  and  $I_{aux}$  are the large voltage swings at the input node (source of transistors  $T_1$  and  $T_2$ ): if  $T_1$  and  $T_2$  are biased with the same gate-voltage, as in [7], the voltage swing is at least  $V_{Tn}+|V_{Tp}|$ , being  $V_T$  the transistor threshold voltage. Voltage swing can be reduced if their gates are biased by voltages whose difference is approximately equal to  $V_{Tn}+|V_{Tp}|$  so that both transistors are at the edge of conduction [8]. Another solution is to include negative feedback, for instance via a simple inverter as depicted in Figure 1a [9].

Low voltage swings at nodes also allow high frequency behavior since the time delay to charge or discharge the parasitic capacitances is decreased. The transient response of the circuit is closely related with the transient response of the current mirrors which process the signals. Since the time constant of a current mirror is  $g_{mi}/C_{gs}$  [10] ( $g_{mi}$  is the transconductance of the input transistor and  $C_{gs}$  is the gate-to-source capacitance), the smaller the input current to the mirror ( $I_{aux}$  -  $I_{in}$  or |  $I_{in}$ -  $I_{aux}$  |  $\Theta$   $I_{sat}$ ), the longer the transient response.

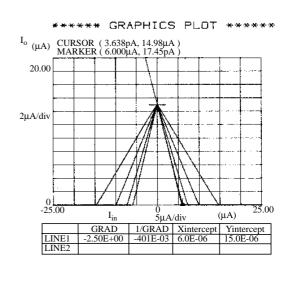

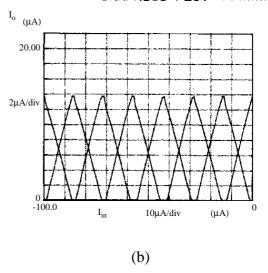

A prototype of this MFC has been integrated in a 1.5- $\mu$ m CMOS technology, occupying an active area of 0.07 mm<sup>2</sup> (Figure 2). It is programmed by an 8-bit word (4 bits to fix  $I_{aux}$  and 2 bits for  $I_{sat}$  and m). Experimental results obtained by programming the slope value are shown in Figure 3a. Figure 3b shows the test results from fixing a value of  $I_{sat}$  and m, and varying the digital code for  $I_{aux}$ . The response time of this MFC, to within 1% of the full scale output current and for input current steps greater than 0.5 $\mu$ A, has been estimated as less than 250ns. To provide this MFC with voltage input, the differential version of the voltage-to-current converter proposed in [11] has been employed.

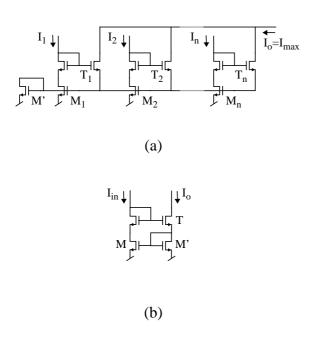

<u>Connective circuits</u>: Figure 4a shows the schematic of a multi-input MAX circuit [12]. It is used to implement a connective MIN between the rules antecedents, according to De Morgan's law:

$$Min (I_1, ..., I_n) = \overline{Max} (\bar{I}_1, ..., \bar{I}_n) = I_{ref} - Max (I_{ref} - I_1, ..., I_{ref} - I_n)$$

(3)

Therefore, in a fuzzy chip the bounded difference with  $I_{ref}$  (see Equation (2)) is not performed within each MFC, but after antecedent connection.

Transistors  $T_i$ , acting as voltage followers, compete to fix the voltage at their source node to the value needed by its corresponding  $M_i$  to operate in saturation conducting the input current  $I_i$ . This follows the idea proposed by Lazzaro et al. [13] to implement a WTA circuit and in [14] to realize a MAX circuit. The circuit in Figure 4a exploits another potential of transistors  $T_i$ , which is that the winner  $T_i$ , acting in a common-gate configuration, transfers the winner or maximum current from a low-impedance to a high-impedance node, thus avoiding loading errors at the output node, with no need of additional cascode or regulated output stages as used in [14].

The algorithm implemented by this circuit to calculate the maximum input current is:

$$I_{o} = A \Sigma_{i} (I_{i} \Theta I_{o})$$

$$(4)$$

This can be seen if the circuit is considered as the connection of improved Wilson current mirrors that share their output diode-connected transistor. According to the improved Wilson-mirror's schematic shown in Figure 4b, a small signal analysis leads to:

$$i_{o} = g_{mT} r_{dsM} \left( i_{in} - \frac{g_{mM}}{g_{mM'}} i_{o} \right)$$

(5)

where transistor output conductances,  $(r_{ds})^{-1}$ , have been neglected with respect to transistor transconductances,  $g_{m}$ .

Comparing (4) and (5), the gain value A, which governs the resolution of the circuit, is then equal to  $g_{mT}r_{dsM}$ . Improved Wilson current mirrors are connected instead of Wilson mirrors because the latter suffer from DC matching errors due to their asymmetrical biasing [15].

If there is only a maximum input current, only one  $T_i$  is conducting, so that the circuit operates like an improved Wilson mirror. Therefore, the output impedance is given by [15]:

$$r_o \cong g_{mM} \cdot r_{dsM} \cdot r_{dsT} \cdot \frac{g_{mT}}{g_{mM'}}$$

(6)

When there are p maximum input currents, the output impedance is increased approximately by a factor  $p^{1/2}$  because p transistors  $T_i$  are now conducting a current  $I_{max}/p$ . The precision of the circuit is slightly reduced in this situation due to the appearance of DC matching errors, however

their contribution, which can be approximated as:

$$\frac{I_{\text{out}}}{I_{\text{in}}} - 1 \cong -\lambda (V_{\text{GSM'}} - V_{\text{T}}) \left(\frac{1}{\sqrt{p}} - 1\right)$$

(7)

remains smaller than that of a Wilson mirror, given by [15]:

$$\frac{I_{\text{out}}}{I_{\text{in}}} - 1 \cong -\lambda V_{\text{GSM'}}$$

(8)

As to dynamic behavior, the transient response of this circuit (similar to that of an improved Wilson mirror) presents an overshoot with an underdamping coefficient related to  $g_m/C$ , where C is the total capacitance at the gate of transistors  $M_i$ . The typical trade-off 'speed/precision' of many analog circuits also appears in this case: precision (associated with  $g_{mT}r_{dsM}$ ) is proportional to  $I^{1/2}$  (transistors operating in saturation), while speed is proportional to  $I^{1/2}$ .

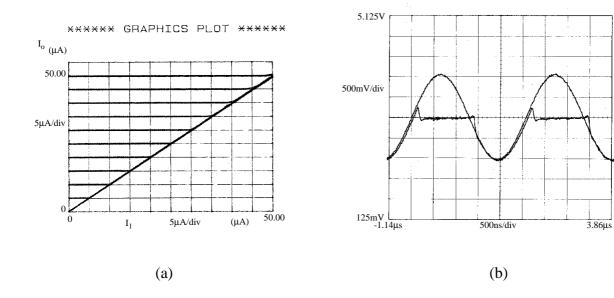

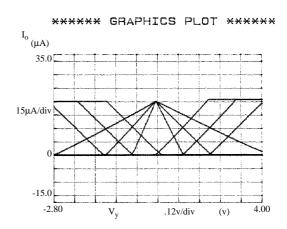

A 3-input MAX prototype has been integrated in a 2.4-µm CMOS technology (Figure 5). Figure 6a shows its static behavior, obtained by varying two of the input currents while the third current is fixed to zero. Absolute error of less than 1.16% of a full scale current of 30µA is achieved, which means an equivalent precision of 6 bits<sup>1</sup>. Another prototype was integrated with V-to-I and I-to-V converters at the input and output, respectively, thus performing as a voltage-mode MIN operator [16]. As shown in Figure 6b, transient responses of 160ns were measured.

<u>Consequent circuits</u>: According to the Singleton Method, the activation degree of each rule must be scaled by its corresponding consequent. The circuits to implement this scaling are current-mode DAC where the consequent value,  $c_i$ , is fixed by digital programming, like the block to generate m in the MFCs. Since these circuits are based on current mirrors, they display no offset, that is, the output current is zero if the input is zero. This is a very good feature because the influence of offset errors in the fuzzy controller output may be a source of troubles.

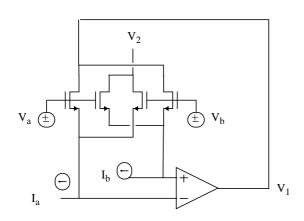

<u>Divider</u>: The numerator and denominator of Equation (1) are represented by currents. However, a voltage-mode controller output is preferable to enable simple interface with conventional control circuitry. For this reason, the transresistance amplifier in Figure 7 has been selected. It converts the difference of input currents into voltage through a voltage-controlled resistance made of four matched transistors biased in triode region. Its transfer characteristics are:

$$V_o = V_1 - V_2 = \frac{I_a - I_b}{\beta(V_a - V_b)}$$

(9)

where  $\beta$  is the transconductance of MOS transistors.

The four-transistor cell has been widely used in the literature [17-19]. It cancels the nonlinearities of MOS transistors and the dependence on the transistor threshold voltage, which only influences the output dynamic range, given by:

$$\max(V_1, V_2) \le \min(V_a - V_T, V_b - V_T)$$

(10)

Mobility reduction is the dominant second-order effect in the transistors of the resistance. It causes both harmonic distortion and increased transresistance. Other second-order effects are the

<sup>1.</sup> Equivalent\_bits  $\leq \log_2$  (full\_scale\_value / absolute\_error).

amplifier nonidealities, such as input voltage offset,  $V_{os}$ , and finite gain, A. Including these effects in Equation (9) and retaining only the first-order terms of  $\theta$  (the mobility degradation parameter), it follows that:

$$V_{o} = \frac{A}{A + \frac{1}{f}} \cdot \left\{ \frac{I_{a} - I_{b}}{\beta(V_{a} - V_{b})} \cdot \left[ 1 + \theta \left( V_{a} + V_{b} - v - 2V_{T} - \frac{V_{1} + V_{2}}{2} \right) \right] + \frac{V_{os} - \frac{V_{2}}{A}}{f} \right\}$$

(11)

where v is the voltage at the input of the amplifier and 1/f is the closed-loop voltage gain, given by  $(V_a+V_b-2v-2V_T)/(V_a-V_b)$ .

Regarding frequency behavior, the divider circuit dynamics are governed by the amplifier, since the four-transistor cell is self-compensated to MOS parasitics [17-18]. Considering a dominant-pole model for the amplifier, that is A=GB/s, where GB stands for the gain-bandwidth product, the dominant pole of this divider is:

$$s_{p} = -GB \cdot \frac{V_{a} - V_{b}}{V_{a} + V_{b} - 2v - 2V_{T}} = -GB \cdot f$$

(12)

so V<sub>a</sub> must be greater than V<sub>b</sub> to achieve stability.

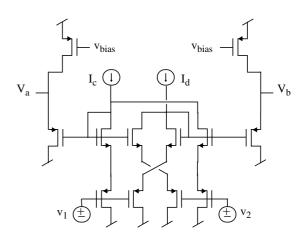

The circuit in Figure 7 has been used by some authors to implement a voltage-input voltage-output divider [18-19]. Since the aim of this application is a current-input voltage-output divider, an I-to-V converter is added so that  $V_a$ - $V_b$  is obtained from a difference of currents,  $I_c$ - $I_d$ . The CMOS structure in Figure 8 has been used, obtaining:

$$V_{o} = \frac{\beta'(v_{2} - v_{1})}{\beta} \cdot \frac{I_{a} - I_{b}}{I_{c} - I_{d}} = k_{d} \cdot \frac{I_{num}}{I_{den}}$$

(13)

where  $\beta$ ' is the equivalent transconductance of the CMOS pair [20].

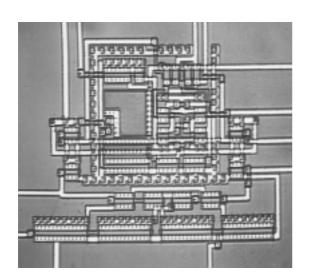

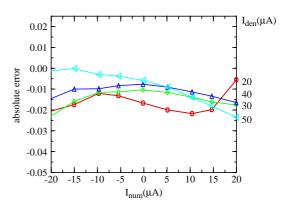

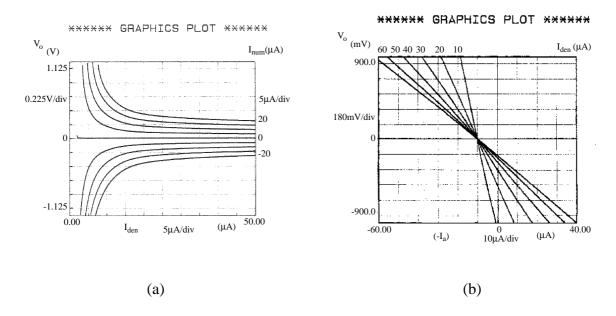

A prototype of this current-input voltage-output divider has been integrated in a 2.4- $\mu$ m CMOS technology, with a two-stage single-ended Miller opamp. The total active area is 0.0497mm². It is shown in the microphotograph of Figure 9. Figure 10a shows the experimental  $V_o\text{-}I_{den}$  curves obtained with  $I_{num}$  as a parameter. The two-quadrant behavior results from the bipolar nature of  $I_{num}$  that ranges from -20 $\mu$ A to 20 $\mu$ A. Figure 10b shows experimental  $V_o\text{-}I_a$  curves, where  $I_b$  is fixed to 10 $\mu$ A and  $I_{den}$  ranges from 10 $\mu$ A to 60 $\mu$ A. The nonlinearity of these curves is less than 1% for an output voltage range of 2v with a 5-v power supply. Figure 11 shows the absolute error resulting from the difference between experimental and theoretical values, the latter being calculated with  $k_d$  adjusted to experimental results. This infers that for a full scale output of 2 volts, 4 decades for  $I_{num}$  (from -20 $\mu$ A to 20 $\mu$ A), and 3 decades for  $I_{den}$  (from 20 $\mu$ A to 50 $\mu$ A), an equivalent precision of 6 bits is achieved. Within this range of operation, the step response to changes in  $I_{num}$  and  $I_{den}$  (with a 5-pF load at the output node) is less than 200ns.

## IV.- Fuzzy controller design.

The previously described circuits are input-output compatible blocks that can be connected following a selected architecture. The number of bits to program the MFCs' and CONSs' parameters must be known to choose the corresponding DACs. Precision and speed requirements of the

MFCs and MAX circuits must be considered to choose the geometries of their constituent transistors. The divider circuit requires more careful design. Equations (9) to (13) relate the different variables of the design space: ranges of  $V_o$ ,  $I_{num}$ , and  $V_a$ - $V_b$  (related in turn to the range of  $I_{den}$  and transresistance of the I-V converter), and values of  $\beta$ ,  $V_2$  (a bias voltage), A, GB, and  $V_{os}$ . An important issue in this design is the selection of an adequate opamp.

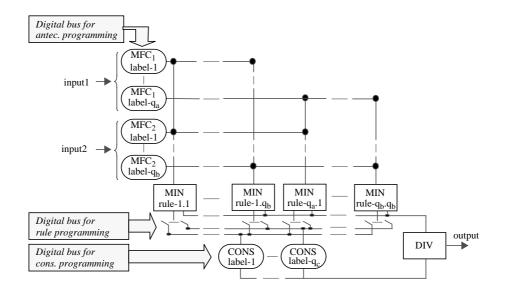

Many analog implementations associate MFCs and CONSs to each rule [3, 4, 14], with the drawback of possibly repeating blocks in different rules. Another solution is that all the rules share the MFCs, which is preferable when the number of rules is large compared to the number of antecedents' fuzzy sets. Figure 12 illustrates the resulting matrix-like architecture of a two-input fuzzy controller that implements the complete fuzzy rule set. This figure shows the MFCs completely connected by MIN/MAX circuits and the digital bus to easily program the antecedent parameters. Regarding the output space, sharing CONSs is also advantageous when the number of rules is large compared with the number of singleton values. In this case, the switches in the lower part of Figure 12 are programmed to conduct the values h<sub>i</sub> (represented by currents) to the input of their associated CONS.

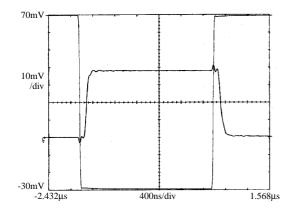

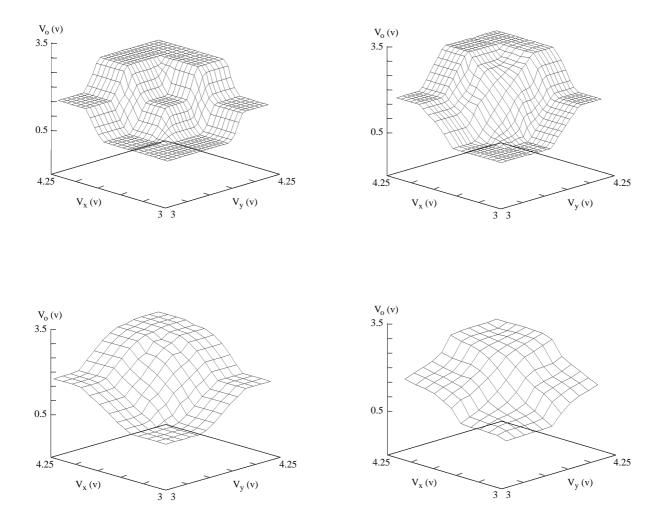

Following this architecture, a two-input one-output rule chip has been integrated in a 2.4-µm CMOS technology (Figure 13). Its analog core, which occupies 0.90 x 1.05 mm², contains six MFCs and three CONSs to generate the fuzzy labels that cover the discourse universe of input and output variables, and nine MAX circuits to implement the complete rule set (nine rules). Digital words to program antecedent and consequent parameters have 8 and 4 bits respectively, while the rule set is fixed to the typical arrangement depicted in Figure 14. The output signals provided by this rule chip (the numerator and denominator currents of Equation (1)) have a transient response to a step input voltage of less than 300ns, as shown in Figure 15 (a low resistive load was connected at the output). To illustrate the behavior of a whole controller, the rule chip was combined with the divider chip of Figure 9 and the parameters that define the antecedents and consequents were changed to obtain different control surfaces. Figure 16 illustrates several ways of covering the input variables with three fuzzy labels and Figure 17 shows measured control surfaces that basically depend on how these labels overlap each other. If the divider is included in the same chip, simulations predict a computation time for the controller of about 500ns.

### V.- Conclusions.

The behavior of current-mode circuits to implement singleton fuzzy controllers has been analyzed and confirmed with the experimental results of prototypes integrated in different CMOS technologies. The combination of these blocks following an efficient architecture results in small-area and low-power singleton fuzzy controllers with an equivalent precision of 6 bits and inference speed in the range of 2 MFLIPS. The internal processing is carried out in current-mode but input and output signals are represented by voltages to ease communication with conventional circuitry. The use of mixed-signal techniques allows flexible controllers that can be adapted to solve different control tasks via a digital programming interface. Measurements from the combination of a rule chip with a divider chip illustrate this issue.

## VI.- REFERENCES

- [1] T. YAMAKAWA, "A fuzzy inference engine in nonlinear analog mode and its application to a fuzzy logic control", IEEE Trans. on Neural Networks, vol. 4, no. 3, pp. 496-522, May 1993.

- [2] L. LEMAITRE, M. J. PATYRA, and D. MLYNEK, "Analysis and design of CMOS fuzzy logic controller in current mode", IEEE Jour. of Solid-State Circuits, vol. 29, no. 3, pp. 317-322, March 1994.

- [3] N. MANARESI, E. FRANCHI, R. GUERRIERI, and G. BACCARANI, "A modular analog architecture for fuzzy controllers", in Proc. European Solid-State Circuits Conf., pp. 288-291, 1994.

- [4] T. YAMAKAWA, "High-speed fuzzy controller hardware system: the mega FIPS machine", Elsevier Science Pub. Comp. Inc., Information Sciences 45, pp. 113-128, 1988.

- [5] J. W. FATTARUSO, S. S. MAHANT-SHETTI, and J. B. BARTON, "A fuzzy logic inference processor", IEEE Jour. of Solid-State Circuits, vol. 29, no. 4, pp. 397-402, April 1994.

- [6] I. BATURONE, S. SANCHEZ-SOLANO, A. BARRIGA and J.L. HUERTAS: "A switched capacitor based singleton fuzzy controller", Proc. 3rd IEEE Int. Conf. on Fuzzy Systems, pp. 1303-1307, Orlando, 1994.

- [7] Z. WANG, "Novel pseudo RMS current converter for sinusoidal signals using a CMOS precision current rectifier", IEEE Trans. Instrumentation and Measurement, vol. 39, no. 4, pp. 670-671, 1990.

- [8] J. L. HUERTAS, S. SANCHEZ-SOLANO, A. BARRIGA, and I. BATURONE, "A hardware implementation of fuzzy controllers using analog/digital techniques", Int. Journal of Computers and Electrical Engineering, vol. 20, no. 5, pp. 409-419, Sept. 1994.

- [9] R. DOMINGUEZ-CASTRO, A. RODRIGUEZ-VAZQUEZ, F. MEDEIRO, J. L. HUER-TAS, "High resolution CMOS current comparators", Proc. European Solid-State Circuits Conf., pp. 242-245, 1992.

- [10] D. G. NAIRN, "Analytic step response of MOS current mirrors", IEEE Trans. on Circuits and Systems, vol. 40, no. 2, pp. 133-135, Feb. 1993.

- [11] K. BULT and H. WALLINGA, "A class of analog CMOS circuits based on the square-law characteristic of an MOS transistor in saturation", IEEE Jour. of Solid-State Circuits, vol. 22, no. 3, pp. 357-365, June 1987.

- [12] I. BATURONE, J. L. HUERTAS, A. BARRIGA, and S. SANCHEZ-SOLANO, "Current-mode multiple-input max circuit", Electronics Letters, vol. 30, no. 9, pp. 678-680, April 1994.

- [13] J. LAZZARO, S. RYCKEBUSCH, M. A. MAHOWALD, and C. A. MEAD, "Winner-take-all network of O(n) complexity" in D. Touretzky (Ed.): "Advances in neural information processing systems 1" (Morgan Kaufmann, San Mateo, CA, 1989), pp. 703-711.

- [14] M. SASAKI, N. ISHIKAWA, F. UENO, and T. INOUE, "Current mode analog fuzzy hardware with voltage input interface and normalization locked loop", IEICE Trans. Fundamentals, vol. E75-A, no. 6, pp. 650-654, June 1992.

#### Integrated Circuit Implementation of Fuzzy Controllers

- [15] Z. WANG, "Analytical determination of output resistance and DC matching errors in MOS current mirrors", IEE Proc., Pt. G, vol. 137, no. 5, pp. 397-404, October 1990.

- [16] I. BATURONE, A. BARRIGA, and J. L. HUERTAS, "Multi-input voltage and current-mode min/max circuits", Proc. 3rd. Int. Conf. on Fuzzy Logic, Neural Networks and Soft Computing, pp. 649-650, Iizuka, Aug. 1994.

- [17] C. TOUMAZOU, F. J. LIDGEY, and D. G. HAIGH, "Analogue IC design: the current-mode approach", Peter Peregrinus Ltd., 1990. (Chapter 5).

- [18] N. KACHAB and M. ISMAIL, "Linearization techniques for nth-order sensor models in MOS VLSI technology", IEEE Trans. Circuits and Systems, vol. 38, no. 12, pp. 1439-1450, Dec. 1991.

- [19] Z. CZARNUL, "Novel MOS resistive circuit for synthesis of fully integrated continuous-time filters", IEEE Trans. Circuits and Systems, vol. 33, no. 7, pp. 718-721, July 1986.

- [20] E. SEEVINCK and R. F. WASSENAAR, "A versatile CMOS linear transconductor/square-law function circuit", IEEE Jour. of Solid-State Circuits, vol. 22, no. 3, pp. 366-377, June 1987.

# Integrated Circuit Implementation of Fuzzy Controllers

Fig 1: (a) Schematic of a programmable MFC. (b) Parameters to define a generic trapezoid.

Fig 2: Die photograph of an 8-bit programmable MFC.

(a)

#### \*\*\*\*\* GRAPHICS PLOT \*\*\*\*

Fig 3: Experimental results of the MFC prototype: (a) When varying the 2-bit word that programs the slope. (b) When varying the 4-bit word that programs the central point,  $I_{aux}$ .

Fig 4: (a) Schematic of a multi-input MAX circuit. (b) Schematic of an improved Wilson current mirror.

Fig 5: Die photograph of a 3-input MAX circuit.

Fig 6: Experimental results of the MAX/MIN prototypes: (a) MAX static behavior. (b) MIN dynamic behavior.

Fig 7: Schematic of a transresistance amplifier.

Fig 8: Schematic of the I-to-V converter used.

Fig 9: Microphotograph of a current-input voltage-output divider.

Fig 11: Absolute error in the divider prototype.

Fig 10: Experimental results of the divider: (a)  $V_o$ - $I_{den}$  curves with  $I_{num}$  as a parameter. (b)  $V_o$ - $I_a$  curves with  $I_{den}$  as a parameter.

Fig. 12: Matrix-like architecture with rule and membership functions programmability.

Fig 13: Microphotograph of the rule chip.

| yx | N | Z | P |

|----|---|---|---|

| N  | P | P | Z |

| Z  | P | Z | N |

| P  | Z | N | N |

Fig 14: Rule set implemented in the rule chip. P, Z, and N represent programmable fuzzy or singleton labels.

Fig 15: Pulse response of the rule chip.

Fig 16: Experimental results showing the programmability of the input fuzzy labels.

Fig 17: Experimental control surfaces corresponding to different sets of programmable parameters.