## Welding Data Adquisition based on FPGA

## R. Millán, J. M. Quero and L. G. Franquelo

Dpto. de Ingeniería Electrónica Escuela Superior de Ingenieros, Avda. Reina Mercedes s/n, Sevilla-41012 (SPAIN) Tel.: +34 (9)5 455 68 57

FAX: +34 (9)5 455 68 49 e-mail: millan@gte.esi.us.es

## Conference Topic: IC's for instrumentation and control

Abstract— This paper presents the use of FPGA in data acquisition and digital preprocessing of the electric current signal of resistance welding stations. This work demonstrates that electric current has enough information to classify this kind of welds in mass production industries. Parameters extracted with the FPGA excite a classifier that accept o reject the welding junction. This system has been developed using a neural classifier and installed in a welding station of General Motors in Cádiz (Spain). Results confirm the validity of this novel approach.

#### I. INTRODUCTION

Resistive welding has been considered as an inherently safe and reliable method for joining metals since its invention. Resistive welding techniques have reached a high degree of fiability and are widely employed as a manufacturing process. The destructive test have played a critically important role in quality control of resistive welding. In destructive tests a weld is qualified by measuring the failure load of the junction. However this kind of test can only be applied to a representative pieces. Competitiveness has obliged to use high productivity weldings in conjunction with quality controls of all welding junctions.

Non-destructive testing techniques find widespread applications for evaluating the integrity of critical components. Among them, ultrasonic waves and x-rays [1] are more often used because of their precision. However, these techniques are costly and unreliable and they have an adverse effect on the productivity. For these reasons they are not feasible for *on-line* applications. Studies of welding process modeling and control are based on the physics of the weld or the empirical data [2]. However, these approaches are not robust because of the existence of uncontrolled parameters.

This paper proposes a monitoring system based on FPGA to estimate, on-line, the failure load of the junction as a function of the welding parameters obtained directly during the process. If the failure load is under a certain bound, the piece is refused. The supervision system has been carried out using neural networks whose applications to several domains like pattern recognition or industrial process control have [3] been successful.

All the work presented have been developed using the welding stations installed in the suspension production lines of General Motors España in the factory at Puerto Real (Cádiz). These stations welds one rod to one reed. In figure 1 is shown a rod and reed before and after the weld process.

Figure 1: Pieces before and after the weld.

Below the welding process is described, with special emphasis in its control parameters and their relationship with the failure load. In section III, the data acquisition and process done by the FPGA is studied. Finally, in section IV, an on-line application is shown, analyzing the data obtained during the process.

### II. PARAMETERS OF THE WELDING PROCESS

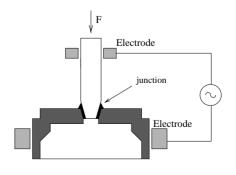

A scheme of the welding process is shown in fig. 2. The welding station has a PRODIGI controller of Pertron Controls Corp. [4]. This system can control accurately the heat given to the junction during the welding.

Figure 2: Welding scheme.

Many factors affect the failure load obtained in the

junction. Controlled parameters are the geometric and energetic, and among the uncontrolled parameters is necessary to take into account impurities, corrosion and surface treatments such as chromation, environmental pollution, etc. The presence of all these uncontrolled parameters justify the use of a system that supervises the quality of the welding.

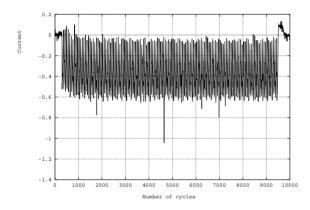

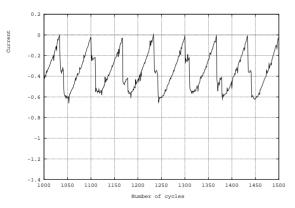

In this work we assume that the shape of the current waveform contains all the information about the junction. If there is not any defect during its execution, the current waveform is very regular. Any problem can be detected because the current waveform presents distortion. Figure 3 represents the current waveform involved in the generation of the junction and in figure 4 we can see a detail of the previous one. These waveforms have been captured using a digital oscilloscope with a base time of 50  $\mu s$ . The periodicity of this waveform corresponds to one sixth of the 50 Hz three phase supply voltage waveform.

Figure 3: Oscilloscope view of the welding current.

Figure 4: Detail of figure 3

It has been essayed 36 probes to study the relationship between the shapes of the recorded waves and their failure loads. These probes are divided in four groups according to the state of their surfaces. The resulting failure loads are shown in Table 1.

|   | Α    | В    | С    | D    |  |

|---|------|------|------|------|--|

| 1 | 5090 | 3886 | 3400 | 4500 |  |

| 2 | 4802 | 4402 | 3902 | 4850 |  |

| 3 | 5190 | 3872 | 4386 | 3966 |  |

| 4 | 5600 | 3786 | 4516 | 5010 |  |

| 5 | 4884 | 2810 | 3810 | 4896 |  |

| 6 | 4862 | 3358 | 4384 | 3792 |  |

| 7 | 5022 | 2390 | 2900 | 4138 |  |

| 8 | 4720 | 3610 | 4270 | 4026 |  |

| 9 | 5080 | 2450 | 4098 | 4672 |  |

Table 1: Failure loads. A: Normal; B:oxides; C,D: chromatted

The shape factor of the current wave is defined by

$$I_{csf} = \frac{\sqrt{\sum_{k=1}^{N} i_k^2}}{N}$$

(1)

where i is the sampled value of the current that goes across the welder electrodes and N is the number of samples. This equation has been applied to all current waveforms and the results are shown in Table 2, being normalized between 0 and 1.

|   | A      | В      | С      | D      |

|---|--------|--------|--------|--------|

| 1 | 0.3574 | 0.0122 | 0.2211 | 0.2960 |

| 2 | 0.4587 | 0.2283 | 0.2198 | 0.2977 |

| 3 | 0.5629 | 0.1170 | 0.3240 | 0.2877 |

| 4 | 0.4723 | 0.1348 | 0.3148 | 0.3133 |

| 5 | 0.4430 | 0.1140 | 0.2939 | 0.3586 |

| 6 | 0.4590 | 0.0830 | 0.2531 | 0.3980 |

| 7 | 0.4102 | 0.0168 | 0.1995 | 0.3176 |

| 8 | 0.3857 | 0.0000 | 0.3015 | 0.3068 |

| 9 | 0.3980 | 0.0456 | 0.3372 | 0.2954 |

Table 2: Current shape factors

The statistic analysis of Tables 1 and 2 based on T-Student function confirms the existence of a correlationship greater that 95 % between the failure load and  $I_{csf}$ , that validates the hypothesis of the existence of a function that relates both magnitudes.

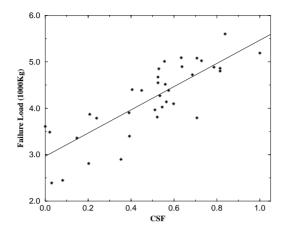

The relationship between the failure load and  $I_{csf}$  is shown in figure 5. The linear correlation coefficient between both variables is low (0.63), that indicates the necessity of using more complicated functions than the linear one, employing a larger volume of information and using a non-linear classifier.

Figure 5: Load failure vs. current shape factor.

To increase the volume of information involved, a discrete histogram has been used, dividing the sampled current curve in 8 level ranges of energy. One of the advantages of using this histogram is that it can be easily obtained with a simple digital circuitry, and therefore it can be calculated in real time. The histograms obtained for the probes in Table 1 are shown in Table 3.

The linear correlation coefficient between the histograms and the failure load is high (0.98). This study has been done excluding 3 columns because their values are practically constants. They are 0.5-1V, 2-2.5V and 2.5-3V respectively. The high value of the correlation coefficient indicates that these histograms contains all the information of the failure load so they can be used as a parameters for a neural classifier.

# III. DATA ACQUISITION AND DIGITAL PROCESSING USING FPGA

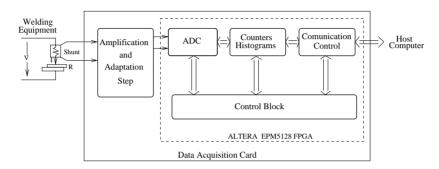

A Welding Monitoring System has been designed to test the validity of the formulated method. Basically, it has a data acquisition card connected to a computer which simulates the classifier. The electric current is sampled and a FPGA process the digital results of the A/D converter.

The whole digital preprocessing circuitry has been implemented using an Altera (EPM5128) FPGA [5]. It also supports the communication protocol with the computer.

In order to get the histograms of the current waveform, the FPGA has 8 counters that increase their values as a function of the analog/digital conversion of the current signal. The period of the samples is  $50\mu s$  during the whole process of welding (little less than 0.5 s). For this reason, the number of samples for each weld are 10000, equivalent to 0.5 seconds.

The ALTERA EPM5128 FPGA contains 128 macrocells that are enough to implement digital process-

| pro | be | 0-0.5V | 0.5-1V | 1-1.5V | 1.5-2V | 2-2.5V | 2.5-3V | 3-3.5V | 3.5-4V |

|-----|----|--------|--------|--------|--------|--------|--------|--------|--------|

|     |    |        |        |        |        |        |        |        | _      |

| A   | 1  | 16     | 2      | 4      | 34     | 240    | 240    | 144    | 0      |

|     | 2  | 15     | 3      | 3      | 25     | 240    | 240    | 216    | 0      |

|     | 3  | 16     | 2      | 5      | 22     | 240    | 240    | 227    | 26     |

|     | 4  | 16     | 2      | 3      | 25     | 240    | 240    | 224    | 4      |

|     | 5  | 15     | 3      | 2      | 16     | 240    | 240    | 240    | 71     |

|     | 6  | 16     | 2      | 3      | 28     | 240    | 240    | 229    | 0      |

|     | 7  | 16     | 2      | 5      | 37     | 240    | 240    | 198    | 0      |

|     | 8  | 16     | 2      | 4      | 30     | 240    | 240    | 163    | 0      |

|     | 9  | 16     | 2      | 5      | 33     | 240    | 240    | 184    | 0      |

|     | 1  | 18     | 2      | 9      | 230    | 240    | 240    | 0      | 0      |

|     | 2  | 17     | 2      | 5      | 46     | 240    | 240    | 18     | 0      |

|     | 3  | 17     | 2      | 9      | 121    | 240    | 240    | 0      | 0      |

|     | 4  | 17     | 2      | 8      | 113    | 240    | 240    | 1      | 0      |

| В   | 5  | 17     | 2      | 8      | 150    | 240    | 240    | 2      | 0      |

|     | 6  | 17     | 2      | 8      | 178    | 240    | 240    | 0      | 0      |

|     | 7  | 18     | 2      | 9      | 227    | 240    | 240    | 0      | 0      |

|     | 8  | 18     | 2      | 13     | 236    | 240    | 240    | 0      | 0      |

|     | 9  | 17     | 2      | 11     | 201    | 240    | 240    | 0      | 0      |

|     | 1  | 17     | 2      | 4      | 55     | 240    | 240    | 19     | 0      |

|     | 2  | 17     | 2      | 5      | 60     | 240    | 240    | 29     | 0      |

|     | 3  | 17     | 2      | 3      | 28     | 240    | 240    | 96     | 0      |

|     | 4  | 17     | 2      | 3      | 35     | 240    | 240    | 93     | 0      |

| С   | 5  | 17     | 2      | 4      | 37     | 240    | 240    | 75     | 0      |

|     | 6  | 17     | 2      | 4      | 46     | 240    | 240    | 49     | 0      |

|     | 7  | 17     | 2      | 4      | 72     | 240    | 240    | 8      | 0      |

|     | 8  | 17     | 2      | 4      | 37     | 240    | 240    | 84     | 0      |

|     | 9  | 17     | 2      | 3      | 31     | 240    | 240    | 117    | 0      |

| D   | 1  | 16     | 2      | 5      | 39     | 240    | 240    | 77     | 0      |

|     | 2  | 17     | 2      | 3      | 36     | 240    | 240    | 82     | 0      |

|     | 3  | 17     | 2      | 3      | 33     | 240    | 240    | 67     | 0      |

|     | 4  | 17     | 2      | 4      | 37     | 240    | 240    | 102    | 0      |

|     | 5  | 17     | 2      | 3      | 31     | 240    | 240    | 147    | 0      |

|     | 6  | 16     | 2      | 2      | 18     | 240    | 240    | 177    | 0      |

|     | 7  | 17     | 2      | 4      | 34     | 240    | 240    | 107    | 0      |

|     | 8  | 16     | 2      | 3      | 34     | 240    | 240    | 89     | 0      |

|     | 9  | 16     | 2      | 3      | 36     | 240    | 240    | 75     | 0      |

|     |    | 10     |        |        |        | 2-10   | 240    | ,,,    |        |

$\it Table~3:$  Current histograms of the probes employed in the learning phase.

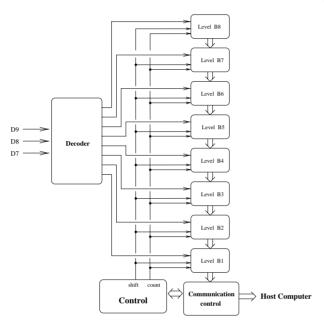

ing. First of all, it controls the A/D converter to acquire data every 50  $\mu$ s. The three most significant bits of the converter (D7, D8 and D9) are inputs to the FPGA (see figure 6). These bits divide the current waveform in 8 levels whose histograms the FPGA should calculate. Depending on the values of these bits a different counter is increased in one unit. The histogram of each level is the number of points stored in its counter when the weld has finished.

Figure 6: Logic to obtain the histograms

The FPGA, also, controls the communication protocol with the personal computer. To minimize digital logic, all counters are connected as a shift register to send their information to the PC. This structure avoid implementing a large multiplexer.

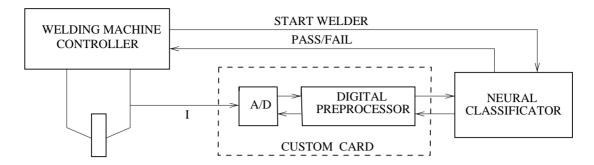

### IV. APPLICATION

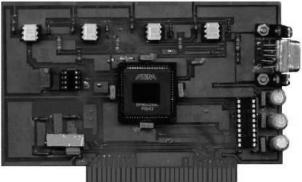

The functional diagram and the block diagram of the specific acquisition system proposed for this application is shown in figures 7 and 8 respectively. A data acquisition card (figure 9) has been designed to acquire and digital process the electric current. This card correspond with data acquisition system proposed in figure 7. The current input signal is filtered before being converted to a digital number. A low-pass filter has been defined to avoid aliasing in the sampled current signal. This specific hardware lets us calculate the histogram during the welding process and these results are read by the host computer at the end of the welding. The computer also emulates the behav-

ior of the neural network using the captured data

as stimulus, both in the learning and recognition

phases.

Figure 9: Data acquisition card.

In this work has been chosen a neural network as a classifier. The reasons for using this kind of classifier are their learning ability and abstraction capacity. The neural network used has been a multilayer perceptron that had one hidden layer of 25 units and output neuron. Basically, the learning process of a perceptron calculates the weight adjustment using the backpropagation method (equation 2) after each iteration. In equation 2, E is the sum of the squares of the differences between the neural network output and the expected output. The initial weight values were set to random numbers between 0 and 0.1.  $\epsilon$  and  $\alpha$  are parameters that affect the speed at which the network learns and its final accuracy.

$$\Delta\omega(t) = -\epsilon \frac{\partial E}{\partial\omega} + \alpha\Delta\omega(t-1)$$

(2)

The neural network has been configured in a learning phase, using the data of Table 3. The number of iterations needed in the learning phase has been 450000.

This system has been installed in a production line to test it. The number of essayed probes has been 450. 98% of the probes were correctly classified (438 were correctly welded and 3 had failure load less than the minimum), and the remaining 2% has given intermediate results in the neural network, that is, they belong to an uncertain area which has failure loads very close to the admissible minimum.

### V. CONCLUSIONS

Digital signal processing is one of the most outstanding applications of FPGAs. In our work we make use of them to calculate histograms of analog input signals. The proposed architecture is embedded in a a weld monitoring system based on neural networks. The system learns to classify the welds thanks to data obtained by the FPGA based card during the welding process. Once configured, the supervision system has been installed in

Figure 7: Weld quality monitor system.

Figure 8: Data acquisition system.

a production line allowing for the real time supervision of welding quality. It has been tested using 450 probes, having classified the vast majority of them correctly. Nowadays the same technique is being applied to continuous welding using sliding windows [6].

### VI. ACKNOWLEDGMENT

The authors thank General Motors España for the facilities given in the tests carried out in its production line of its factory in Puerto Real (Cádiz). Moreover, They also thank Mr Manuel Maraver for his valuable advises and dedication in the elaboration of this research work.

#### REFERENCES

- [1] Hull, B., John, V.: Non-destructive testing. MacMillan Education. London 1988.

- [2] Andersen, K., Cook, G.E., Karsai, G., Ramswamy, K.: Artificial Neural Networks Applied to Arc Welding Process Modeling and Control. IEEE Trans. on Industry Applications, vol. 26 no 5, September/October, 1990.

- [3] J.M. Quero, L.G. Franquelo and E.F. Camacho. "Networks for constrained Predictive Control". *IEEE Trans. on Circuits and Systems*, vol. 40, 621-626, 1993.

- [4] Weld Quality Monitor Instruction Manual. SRL Controls Division, 1981

- [5] Data book. Altera Corporation, 1992.

- [6] J.A. ANDERSON and E. ROSENFELD. *Neuro-computing*. MIT press, 1988.