Depósito de investigación de la Universidad de Sevilla

https://idus.us.es/

This is an Accepted Manuscript of an article published by IEEE in IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I - REGULAR PAPERS on 2023, available at: <u>https://doi.org/10.1109/TCSI.2023.3336719</u>

"© 2023 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other Works"

# On the use of FIR Feedback in Bandpass Delta-Sigma Modulators

Javad Gorji, Student Member, IEEE, Shanthi Pavan, Fellow, IEEE, and José M. de la Rosa, Fellow, IEEE

Abstract—This paper presents a new architecture for bandpass delta-sigma modulators (BP $\Delta \Sigma Ms$ ) featuring finite impulse response (FIR) filters in the feedback path. The effectiveness of FIR feedback in lowpass delta-sigma modulators (LP $\Delta \Sigma$ Ms) has been well-established in improving loop-filter linearity and robustness to clock jitter. Building upon these findings, we explore the application of bandpass FIR filters in single-bit BP $\Delta \Sigma$ Ms. By contrast to conventional BP $\Delta \Sigma$ Ms, the proposed technique significantly reduces out-of-band quantization error contents in the feedback signal. This approach is applicable to both discretetime and continuous-time implementations. Further, we show that performance does not improve by increasing the number of FIR taps beyond a certain point. However, we can enhance filtering performance by employing non-equal coefficients within the filter. To validate the efficacy of the presented approach, the paper includes electrical simulation of a 4th-order active-RC BP $\Delta \Sigma M$ .

Index Terms—Analog-to-digital conversion, delta-sigma modulation, continuous-time circuits, FIR DAC, clock jitter.

## I. INTRODUCTION

**B** ANDPASS  $\Delta \Sigma Ms$  digitize signals placed in an arbitrary band by applying band-stop filtering to quantization noise. Consequently, the noise is pushed out of a bandwidth (BW) centered around the frequency  $f_n$  (also called the *notch* frequency) [1]. Their main application is to digitize intermediate-frequency (IF) or radio-frequency (RF) signals in wireless receivers, thus placing the analog-to-digital converter (ADC) closer to the antenna. This way, most of the signal processing can be moved to the digital domain and benefit from technology downscaling and higher programmability [2]– [8].

As RF ADCs need sampling frequencies in the GHz range, state-of-the-art BP $\Delta\Sigma$ Ms are dominated by continuous-time (CT) circuits [6]–[8]. CT $\Delta\Sigma$ Ms can operate at higher speeds when compared to their discrete-time (DT) counterparts while consuming less power. Furthermore, they are easy to drive and possess the property of inherent anti-aliasing [9], [10]. The choice of the number of quantizer levels is perhaps the

Manuscript received July 31, 2023; revised September 25, 2023.

Javad Gorji and José M. de la Rosa are with the Institute of Microelectronics of Seville, IMSE-CNM (CSIC/University of Seville), C/ Américo Vespuccio 28, 41092 Sevilla, Spain (e-mail: gorji@imse-cnm.csic.es; jrosa@imse-cnm.csic.es).

Shanthi Pavan is with the Department of Electrical Engineering, Indian Institute of Technology Madras (IIT Madras), Chennai 600036, India (e-mail: shanthi@ee.iitm.ac.in).

first choice that needs to be made in any  $\Delta \Sigma M$  design. A multi-bit quantizer enables the use of a noise transfer function (NTF) with large out-of-band gain (OBG). However, a multibit ADC is difficult to drive, particularly at the high sampling rates needed in an RF ADC. A multi-bit DAC has problems with element mismatch, which needs to be addressed with techniques such as dynamic element matching. This increases the hardware complexity and makes it difficult and costly to reach the required performance in GHz-range applications.

A single-bit quantizer, on the other hand, has the advantage of an ADC that is easy to drive and an inherently linear feedback DAC [11], [12]. Unfortunately, however, the rail-torail feedback DAC waveform necessitates increased loop-filter power dissipation to achieve the desired linearity. Furthermore, the modulator's sensitivity to clock jitter is greatly increased.

This work follows up on the approach presented in [13] and proposes to address these problems in a single-bit BP $\Delta\Sigma$ M using bandpass FIR (BP-FIR) feedback. The motivation is similar to that in LP $\Delta\Sigma$ Ms [14], [15]. Like in the lowpass case, BP-FIR feedback in a BP $\Delta\Sigma$ M reduces the height of the steps in the feedback DAC waveform, thereby reducing the magnitude of the error signal that drives the loop-filter. Furthermore, FIR feedback implemented using a semi-digital FIR DAC maintains the inherent linearity of the single-bit quantizer. Finally, sensitivity to clock jitter and comparator metastability are reduced.

Alternatively, infinite impulse response (IIR) filtering has been applied to the feedback path of a BP $\Delta\Sigma$ M before [16]. Apart from needing a multi-bit feedback DAC whose performance is degraded due to element mismatch, the internal feedback needed to implement an IIR filter also appears challenging. An FIRDAC avoids these problems.

Following this introduction, the article is organized as follows: Section II describes the proposed BP $\Delta\Sigma$ M with FIR filtering, considering a DT implementation. Section III extends this approach to CT BP $\Delta\Sigma$ Ms and compares them with conventional implementations. We consider two case studies: a second- and a fourth-order loop-filter, and in this context, we have discussed the calculation of coefficients using two different methods. In Section IV, a comparison is made between the use of FIR filter in LP $\Delta\Sigma$ Ms and BP $\Delta\Sigma$ Ms. We will show how, in both cases, using proper FIR filtering will emulate multi-bit operation. The considerations for the optimum design of the FIR filter are addressed in Section V. Finally, mapping these system-level concepts to circuit implementation is discussed in Section VI, and conclusions are drawn in Section VII.

This work was supported in part by Grants PID2019-103876RB-I00, PID2022-1380780B-I00, funded by MCIN/AEI/10.13039/501100011033, by the European Union ESF Investing in your future, by ERDF A way of making Europe, and in part by the Center of Excellence in RF, Analog and Mixed-Signal ICs (CERAMIC), IIT Madras.

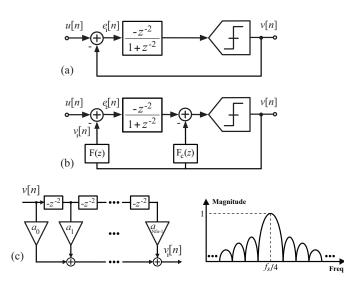

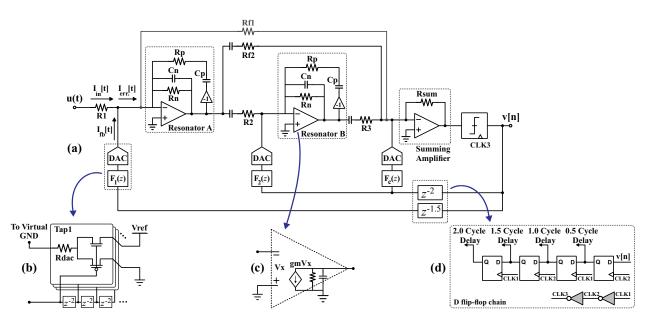

Fig. 1. Block diagram of a DT BP $\Delta\Sigma$ M. (a) Conventional. (b) Proposed with BP-FIR feedback. (c) BP-FIR filter structure and frequency response.

#### II. DISCRETE-TIME BP $\Delta\Sigma$ MS with BP-FIR FEEdback

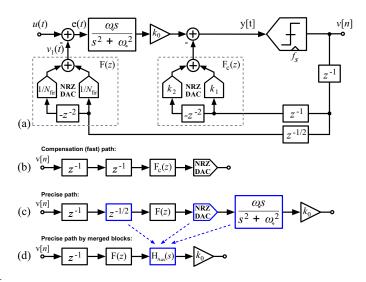

To build insight, we first consider a second-order discretetime BP $\Delta\Sigma$ M with a center frequency  $f_s/4$  as shown in Fig. 1(a). The NTF of the modulator is NTF $(z) = 1 + z^{-2}$  [9], [10]. The objective is to add an FIR filter to the feedback [see Fig. 1(b)] and rebuild the loop in such a way that the NTF is restored. The input signal is at  $f_n = f_s/4$  rather than DC, hence a BP-FIR filter centered at  $f_n$  [see Fig. 1(c)] must be used for F(z) to filter the 2-level quantizer output sequence before driving the feedback in the main path.

We can start by considering the general form of a lowpass FIR (LP-FIR) filter with the following transfer function

$$\operatorname{FIR}_{\operatorname{LP}}(z) = a_0 + a_1 \cdot (z^{-1}) + a_2 \cdot (z^{-1})^2 + \dots + a_{N_{\operatorname{fir}}-1} \cdot (z^{-1})^{(N_{\operatorname{fir}}-1)}$$

(1)

where  $N_{\text{fir}}$  is the number of taps in the FIR filter and  $a_i$  are the filter coefficients. The equivalent BP-FIR filter with a passband centered at  $f_s/4$ , is obtained by applying a  $z \rightarrow -z^2$  transformation to a LP-FIR filter (1), yielding

$$\operatorname{FIR}_{\operatorname{BP}}(z) = a_0 + a_1 \cdot (-z^{-2}) + a_2 \cdot (-z^{-2})^2 + \dots + a_{N_{\operatorname{fir}}-1} \cdot (-z^{-2})^{(N_{\operatorname{fir}}-1)}.$$

(2)

The gain in the passband of the filter is determined by summing all the coefficient values together. For simplicity, the tap weights of the FIR filter F(z) are considered to be the same and equal to  $1/N_{\text{fir}}$ , so that the gain of the signal transfer function (STF) at  $f_s/4$  is unity. Based on (2), we can write the transfer function for this filter as follows

$$F(z) = \frac{1}{N_{\text{fir}}} \cdot \sum_{n=0}^{N_{\text{fir}}-1} (-z^{-2})^n.$$

(3)

The delay introduced by the FIR filter would render the loop unstable without a compensation path around the quantizer [15]. This is shown in Fig. 1(b). For the modulators in

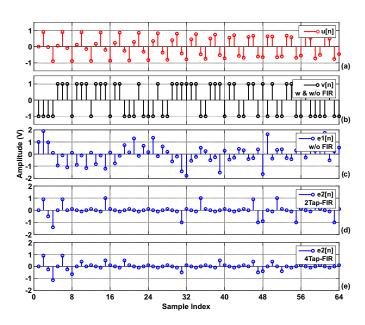

Fig. 2. Impact of BP-FIR feedback in DT BP $\Delta\Sigma$ M sequences. (a) Input to the modulator, u[n] ( $f_{in} = f_s/4 + BW/3$ ). (b) Output, v[n]. (c) Resonator input of a conventional BP $\Delta\Sigma$ M,  $e_1[n]$ . (d), (e) Resonator input of the proposed BP $\Delta\Sigma$ M,  $e_2[n]$  for  $N_{\rm fir} = 2$  and  $N_{\rm fir} = 4$ .

Figs. 1(a) and (b) to have identical NTFs, we see that the following has to be satisfied

$$F(z) \cdot \left(\frac{-z^{-2}}{1+z^{-2}}\right) + F_c(z) = \left(\frac{-z^{-2}}{1+z^{-2}}\right) \tag{4}$$

hence,  $F_c(z)$  is calculated as

$$F_c(z) = [1 - F(z)] \cdot \left(\frac{-z^{-2}}{1 + z^{-2}}\right)$$

(5)

since F(z) has a unity gain at z = j (corresponding to  $f = f_s/4$ ), [1 - F(z)] has zeros at  $z = \pm j$ . Consequently, we can write it as

$$[1 - F(z)] = (1 + z^{-2}) \cdot P(z)$$

(6)

where P(z) is a polynomial. Using (6) in (5),  $F_c(z)$  is seen to be

$$F_c(z) = (-z^{-2}) \cdot P(z).$$

(7)

From the above discussion, it can be concluded that  $F_c(z)$  is also an FIR filter. This indicates that the original NTF can be restored exactly. Furthermore, the taps of  $F_c(z)$  are not identical in general.

For a 2-tap FIR, where  $F(z) = (-z^{-2})[0.5 + 0.5(-z^{-2})]$ ,  $F_c(z)$  turns out to be  $(-z^{-2})[1 + 0.5(-z^{-2})]$  which demonstrates a BP-FIR followed by two delays in each path. The simulation results of Fig. 1(a) and (b) are shown in Fig. 2. The output of the modulator remains identical in both cases, as the NTFs are the same. The main difference lies in the error signal fed into the resonator. Thanks to FIR feedback,  $e_2[n]$ is considerably smaller with 2- and 4-tap FIR feedback when compared to the case without an FIR filter (i.e.,  $e_1[n]$ ). The reasoning can be extended to arbitrary NTFs and to the CT domain.

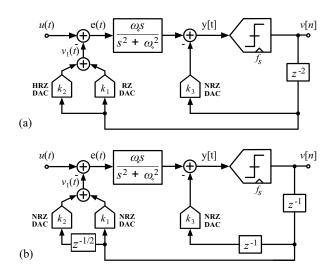

Fig. 3. Conventional 2nd-order CT BP $\Delta\Sigma$ Ms with a multi-path feedback loop based on: (a) Different DAC (RZ/HRZ) waveforms [17]. (b) Identical DAC (NRZ) with different delays [18].

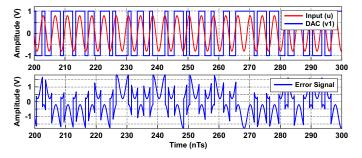

Fig. 4. Input signal ( $f_{in} = f_s/4 + BW/3$ ), DAC output signal, and modulator input error signal in a conventional 2nd-order single-bit CT BP $\Delta\Sigma$ M.

#### III. Continuous-Time BP $\Delta \Sigma Ms$

Fig. 3 shows the block diagram of the two common approaches for implementing CT BP $\Delta\Sigma$ Ms with multi-path feedback, utilizing an ideal resonator with a transfer function  $H_{\text{Res}}(s) = \omega_o s/(s^2 + \omega_o^2)$ . Here,  $\omega_o = 2\pi f_n$  is the center frequency. A 2nd-order loop-filter made up of a resonator with  $f_n = f_s/4$  is considered. The feedback loop can be implemented in multiple ways. For example, Fig. 3(a) [17] uses two different DAC pulse shapes, return-to-zero (RZ) and half-delayed return-to-zero (NRZ), while Fig. 3(b) [18] includes a non-return-to-zero (NRZ) DAC with a different delay for each path. In both cases, multiple feedback paths are required to implement the desired NTF.

In the main path of a conventional CT  $BP\Delta\Sigma M$  (Fig. 3), the feedback signal allows passing both the digitized signal (placed around  $f_n = f_s/4$ ) as well as most of the out-ofband frequency components of the shaped quantization error. As a consequence, the DAC output  $v_1(t)$  does not approach the input signal u(t). Accordingly, the error signal at the input node of the modulator e(t), which coincides with the input of the resonator, displays considerable changes. This is illustrated in Fig. 4 for a 2nd-order  $BP\Delta\Sigma M$  with a maximally flat NTF with an OBG of 1.5.

As previously stated, this phenomenon imposes limitations on the signal-to-noise ratio (SNR) in BP $\Delta\Sigma$ Ms, particularly

Fig. 5. (a) Proposed 2nd-order CT BP $\Delta\Sigma$ M with 2-tap BP-FIR DAC. (b) Compensation path around the quantizer. (c) Precise path. (d) Precise path redefined by merging half delay, CT resonator, and the NRZ DAC into an auxiliary block.

when opting for single-bit quantization to simplify the system in high-speed design. However, this simplification is not restricted to high speeds; even a low-speed design benefits. In such scenarios, employing FIR feedback proves highly beneficial, as it effectively filters the quantization error and converts a high-speed 1-bit stream into a multi-level waveform.

## A. 2nd-order CT $BP\Delta\Sigma M$ with 2-tap BP-FIR DAC

Let us consider the simplest case of a 2nd-order BP $\Delta\Sigma$ M as shown in Fig. 5(a). The forward path is made up of a resonator and a 1-bit quantizer, and the feedback paths are implemented using delayed 2-tap BP-FIR DAC. While in DT BP $\Delta\Sigma$ M with FIR feedback we had the same delay of 2, before F(z) and  $F_c(z)$ , it turns out that another degree of freedom is needed in the CT domain to match the loop-filter transfer function with an equivalent DT BP $\Delta\Sigma$ M. This is accomplished by applying different delays to the main feedback path (1.5-cycle delay) and the compensation path around the quantizer (2cycle delay).

The objective is to find the coefficients that restore the correct NTF. Schreier's toolbox [19] is used to get the desired NTF(z) with an OBG of 1.5. The 2nd-order DT loop-filter transfer function can be easily obtained from  $L_d(z) = 1/\text{NTF}(z) - 1$  as follows

$$L_d(z) = \frac{-0.6667}{(z^2 + 1)}.$$

(8)

The equivalent DT loop-filter transfer function of the desired CT BP $\Delta\Sigma$ M, denoted as  $L_c(z)$ , is derived using a method similar to that found in [20]. The loop-filter of the modulator consists of a fast path around the quantizer Fig. 5(b), which is entirely in the discrete-time domain, and a precise path that is responsible for the noise shaping in the modulator Fig. 5(c). The precise path consists of both discrete-time and continuous-time components. For simplification purposes, we can aggregate the half delay, the CT resonator, and the

NRZ DAC into an auxiliary block, denoted as  $H_{Aux}(s)$ , and redefine the precise path as shown in Fig. 5(d). Based on these assumptions, the loop-filter of the modulator in Fig. 5(a) can be written in the z-domain:

$$L_c(z) = \underbrace{k_0 \cdot \mathcal{Z}\{H_{\text{Aux}}(s)\} \cdot F(z) \cdot z^{-1}}_{\text{Precise path}} + \underbrace{F_c(z) \cdot z^{-2}}_{\text{Fast path}}$$

(9)

where  $k_0$  represents the scaling gain of the resonator output. Based on (9), to determine  $L_c(z)$  all we need to do is calculate  $H_{Aux}(z)$ , which can be expressed as follows

$$H_{\text{Aux}}(z) = \mathcal{Z} \left[ H_{\text{Res}}(s) \cdot H_{\text{DAC}}(s) \right]$$

(10)

where  $H_{\text{Res}}(s)$  represents the resonator transfer function and  $H_{\text{DAC}}(s)$  denotes the transfer function for a half-delayed NRZ DAC pulse shape. In the s-domain, we define an arbitrary rectangular DAC pulse as

$$H_{\rm DAC}(s) = \frac{e^{-t_d s} - e^{-(t_d + \tau)s}}{s}$$

(11)

here  $\tau$  denotes the pulse width, and  $t_d$  signifies the applied delay to the pulse. In the case of an NRZ DAC pulse delayed by half,  $\tau$  and  $t_d$  take values of 1 and 0.5, respectively. Substituting (11) into (10), we obtain

$$H_{\text{Aux}}(z) = \mathcal{Z}\left[\frac{H_{\text{Res}}(s) \cdot e^{-0.5s}}{s}\right] - \mathcal{Z}\left[\frac{H_{\text{Res}}(s) \cdot e^{-1.5s}}{s}\right].$$

(12)

In (12), we have delays that are not integer multiples of the sampling period. Therefore, the use of a modified z-transform is required [21]. Hence, we can rewrite (12) as

$$H_{\text{Aux}}(z) = \mathcal{Z}_{\text{ml}}\left[\frac{H_{\text{Res}}(s)}{s}\right] - \mathcal{Z}_{\text{m2}}\left[\frac{H_{\text{Res}}(s)}{s}\right]$$

(13)

where  $m_i = 1 - t_d$  is the fractional delay parameter and is valid for  $0 < m_i < 1$ . In the case of a half-delayed NRZ DAC,  $m_1 = 0.5$  and  $m_2 = -0.5$ . Here we can eliminate a complete delay from  $m_2$  and consider that  $m_2$  is a fractional delay in the first sampling phase, so  $m_2 = 0.5$ . We will take into account the impact of this delay in our further calculations. Given these, (13) can be derived using the residue theorem [22] as follows

$$H_{\text{Aux}}(z) = \sum_{\text{poles of } \frac{H_{\text{Res}}(s)}{s}} \text{Residues} \left[ \frac{H_{\text{Res}}(s)}{s} \cdot \frac{e^{m_1 s}}{z - e^s} \right] - \left( \sum_{\text{poles of } \frac{H_{\text{Res}}(s)}{s}} \text{Residues} \left[ \frac{H_{\text{Res}}(s)}{s} \cdot \frac{e^{m_2 s}}{z - e^s} \right] \right) \cdot (z^{-1})$$

(14)

here the delay that is multiplied in the second part of (14) is due to the assumption we made for  $m_2$ . Therefore,  $H_{\text{Aux}}(z)$ is determined as

$$H_{\text{Aux}}(z) = \frac{1}{\sqrt{2}} \cdot \frac{z^{-1}(1-z^{-2})}{1+z^{-2}}.$$

(15)

By substituting (15) in (9) and equating  $L_c(z) = L_d(z)$ , the values of  $k_0$ ,  $k_1$ , and  $k_2$  are obtained as -0.47, -0.5, and -0.17, respectively. By following a similar procedure, the

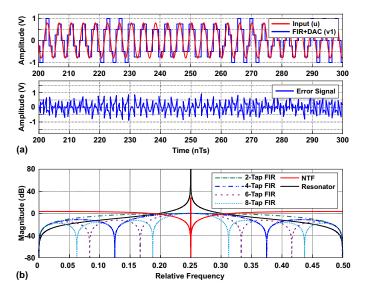

Fig. 6. The impact of the proposed BP-FIR DAC in a 2nd-order single-bit CT BP $\Delta\Sigma$ M: (a) Input signal ( $f_{in} = f_s/4 + BW/3$ ), FIR+DAC output signal, and modulator input error signal for  $N_{\text{fir}} = 8$ . (b) NTF and FIR filter transfer function for different number of taps.

Fig. 7. Comparison of the proposed 2nd-order BP $\Delta\Sigma$ M with  $N_{\rm fir} = 8$  and its DT counterpart: (a) Output PSD. (b) SNR versus input amplitude.

coefficients for CT BP $\Delta\Sigma$ M assisted with BP-FIR with more taps can be determined.

As illustrated in Fig. 6(a), the error processed by the loopfilter, which is  $e(t) = u(t) - v_1(t)$ , is significantly reduced with respect to conventional BP $\Delta\Sigma$ Ms with single-bit quantizer (see Fig. 4). As a result, the linearity requirement of the resonator in the loop-filter is relaxed, just like in CT $\Delta\Sigma$ Ms with multi-bit quantization. The presence of F(z) accounts for this functionality. As depicted in Fig. 6(b), F(z) is a bandpass filter with a passband frequency centered at  $f_n = f_s/4$ . Thus, the input signal component of v[n] is not affected, though the power of the shaped noise is diminished. Therefore, the DAC output,  $v_1(t)$ , has reduced out-of-band (quantization error) content and only contains frequency components close to the

Fig. 8. Proposed 4th-order CT BP $\Delta\Sigma$ M with  $N_{\text{fir}}$ -tap BP-FIR DAC in: (a) CRFB structure, and (b) CRFF-B structure. (c) Open-loop impulse response analysis of the modulator paths.

input u(t) around  $f_s/4$ .

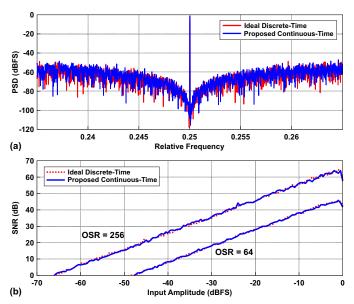

Fig. 7(a) and (b) illustrate the power spectral density (PSD) of the output and the SNR versus input amplitude of the modulator in Fig. 5, respectively. In both cases, excellent alignment is observed between the  $CT\Delta\Sigma M$  and its DT counterpart. Achieving this remarkable agreement involves compensating for the degradation induced by sinc(1/4), as is the case in CT BP $\Delta\Sigma M$  with NRZ DACs and  $f_n = f_s/4$  sampling. To achieve this, a degradation ( $\approx 0.9$ ) is applied to the input before reaching the summation node. Through this approach, the maximum stable amplitude (MSA) is matched to that of the DT BP $\Delta\Sigma M$ .

## B. 4th-order CT BP $\Delta \Sigma M$ with $N_{fir}$ -tap BP-FIR DAC

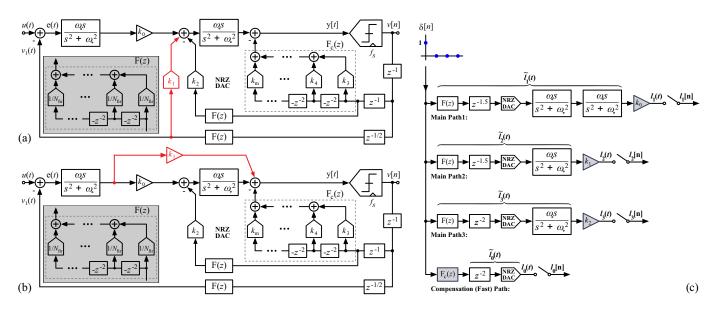

The presented approach can be applied to high-order BP $\Delta\Sigma$ Ms with  $N_{\rm fir}$ -tap BP-FIR filtered DACs. This is illustrated for a 4th-order BP $\Delta\Sigma$ M with two different structures: a cascade of resonators with feedback (CRFB) shown in Fig. 8(a), and a cascade of resonators with feedforward and feedback (CRFF-B) shown in Fig. 8(b).

The process starts by obtaining a 4th-order DT loop-filter transfer function. For a maximally flat NTF with an OBG of 1.5, we have

$$L_d(z) = \frac{-0.7749z^2 - 0.5585}{(z^2 + 1)^2}.$$

(16)

Regardless of the structure type, the coefficients can be determined using the technique discussed in the previous section. However, performing mathematical calculations for higherorder NTFs can be tedious and impractical in real designs. This is due to the complexity of the transfer function, which includes additional poles and zeros caused by finite gainbandwidth (GBW) in the active blocks (such as op-amps or transconductors) and parasitics of the circuit. Determining the exact locations of these additional poles and zeros from circuit simulations is a challenging task that is not straightforward. Therefore, in this section, we follow a robust numerical method known as "closed-loop fitting" [23] to determine the coefficients and taps of the compensation FIRDAC. The main idea behind this method is based on rewriting the relationship between NTF and the loop-filter transfer function as

$$L_d(z) \times \text{NTF}(z) = 1 - \text{NTF}(z).$$

(17)

Let us denote the impulse response corresponding to  $L_d(z)$ and NTF(z) by l[n] and h[n], respectively. We can express equation (17) in time domain as follows

$$l[n] * h[n] = \delta[n] - h[n].$$

(18)

According to Fig. 8(c), depicting the various paths of the 4th-order modulator, we can determine that  $l[n] = [\tilde{l}_1[n] \ \tilde{l}_2[n] \ \tilde{l}_3[n] \ \tilde{l}_0[n]] \begin{bmatrix} K \\ Fc \end{bmatrix}$ . Further, let  $h_0[n] = \tilde{l}_0[n] * h[n]$ ,  $h_1[n] = \tilde{l}_1[n] * h[n]$ ,  $h_2[n] = \tilde{l}_2[n] * h[n]$ , and  $h_3[n] = \tilde{l}_3[n] * h[n]$ . Subsequently, (18) can be written as

$$\begin{bmatrix} h_{1}[1] & h_{2}[1] & h_{3}[1] & h_{0}[1] & 0 & 0 & \cdots \\ h_{1}[2] & h_{2}[2] & h_{3}[2] & h_{0}[2] & 0 & 0 & \cdots \\ h_{1}[3] & h_{2}[3] & h_{3}[3] & h_{0}[3] & h_{0}[1] & 0 & \cdots \\ h_{1}[4] & h_{2}[4] & h_{3}[4] & h_{0}[4] & h_{0}[2] & 0 & \cdots \\ h_{1}[5] & h_{2}[5] & h_{3}[5] & h_{0}[5] & h_{0}[3] & h_{0}[1] & \cdots \\ h_{1}[6] & h_{2}[6] & h_{3}[6] & h_{0}[6] & h_{0}[4] & h_{0}[2] & \cdots \\ \vdots & \vdots & \vdots & \vdots & \vdots & \vdots & \ddots \\ \end{bmatrix} \begin{bmatrix} k_{0} \\ k_{1} \\ k_{2} \\ Fc \end{bmatrix}$$

$$= \begin{bmatrix} 1 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ \vdots \end{bmatrix} - \begin{bmatrix} h[1] \\ h[2] \\ h[3] \\ h[4] \\ h[5] \\ h[6] \\ \vdots \end{bmatrix} .$$

$$(19)$$

|          | 2-Tap  | 3-Tap  | 4-Tap  | 5-Tap  | 6-Tap  | 7-Tap  | 8-Tap  |

|----------|--------|--------|--------|--------|--------|--------|--------|

| $k_0$    | -0.097 | -0.097 | -0.097 | -0.097 | -0.097 | -0.097 | -0.097 |

| $k_1$    | -0.662 | -0.739 | -0.815 | -0.892 | -0.968 | -1.045 | -1.121 |

| $k_2$    | 0.054  | 0.054  | 0.054  | 0.054  | 0.054  | 0.054  | 0.054  |

| $k_3$    | -0.527 | -0.591 | -0.623 | -0.643 | -0.656 | -0.665 | -0.672 |

| $k_4$    | -0.193 | -0.405 | -0.511 | -0.574 | -0.617 | -0.647 | -0.670 |

| $k_5$    | -      | -0.147 | -0.344 | -0.463 | -0.542 | -0.598 | -0.640 |

| $k_6$    | -      | -      | -0.123 | -0.308 | -0.431 | -0.518 | -0.584 |

| $k_7$    | -      | -      | -      | -0.109 | -0.283 | -0.408 | -0.501 |

| $k_8$    | -      | -      | -      | -      | -0.1   | -0.266 | -0.391 |

| $k_9$    | -      | -      | -      | -      | -      | -0.094 | -0.253 |

| $k_{10}$ | -      | -      | -      | -      | -      | -      | -0.089 |

In a practical implementation, these impulse responses can be easily obtained through simulation, which takes into account the impact of all non-idealities. By solving the equation mentioned above, we can determine the weighting coefficients. Table I summarises the calculated coefficients for a 4th-order CT BP $\Delta\Sigma M$  with 2-tap to 8-tap FIR filter.

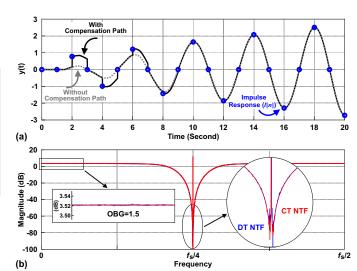

Analyzing the impulse response of the CT system and comparing it with the DT system is essential for identifying the expected matching crossing points. Fig. 9(a) illustrates this concept in the context of a 4th-order CT BP $\Delta\Sigma$ M with a 4tap FIR filter. The additional delay introduced by F(z) affects samples 2, 4, 6, and 8. However, as discussed in Section II, by employing a BP-FIR filter with an equal number of taps  $F_c(z)$ , we can effectively compensate for this distortion. Fig. 9(b) demonstrates the conformity of the CT NTF with the DT NTF after this compensation process.

The first tap in the FIR filter plays a critical role, as it is the closest stage to the quantizer and is particularly susceptible to data-dependent jitter resulting from comparator metastability. However, in all the cases discussed, the proposed structure incorporates a sufficient delay between the output of the modulator and the first tap in the FIR filter. This characteristic alleviates the requirements for quantizer in terms of metastability.

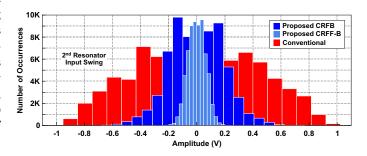

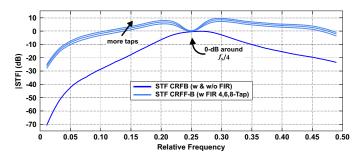

The decision between CRFB and CRFF-B structures depends on the intended application of the ADC. CRFF-B is preferred for two reasons. Firstly, this structure offers the advantage of removing one of the FIRDACs from the feedback, resulting in power and area savings. Secondly, the incorporation of a forward path around the second resonator contributes to better reducing the input swing of the second resonator. Therefore, we can highlight that in the proposed architecture, the benefits of the BP-FIR DAC in reducing error signal swings extend beyond just the input of the first resonator and also apply to the input of the second resonator. This is depicted in Fig. 10, where the input swing of the second resonator exhibits a remarkable reduction when compared to the conventional case without FIR filtering. However, the main limitation of the feedforward approach, in general, is its inability to effectively handle close to in-band interferer. As demonstrated in Fig. 11, the proposed CRFF-B exhibits STF peaking near  $f_s/4$ . This peaking can potentially lead the modulator to saturate when the ADC needs to operate in the presence of strong blockers close to in-band, as is the case in

Fig. 9. 4th-order CT BP $\Delta\Sigma$ M with 4-tap BP-FIR DAC: (a) Impulse response of y(t) and the influence of  $F_c(z)$  on its restoration. (b) Restored flat CT NTF with OBG = 1.5, in comparison to the DT NTF.

Fig. 10. Comparison of the proposed 4th-order CT BP $\Delta\Sigma$ M with 6-tap BP-FIR DAC with conventional implementation in terms of input swing in the second resonator.

Fig. 11. STF in CRFB and CRFF-B structures for a 4th-order CT BP $\Delta\Sigma$ M.

certain radio applications.

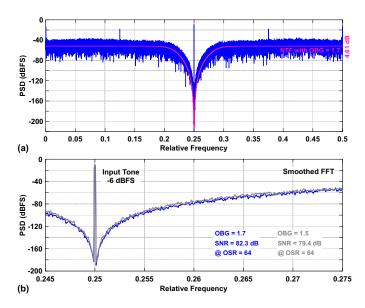

Considering that we are restoring the original NTF with this approach, it does not result in an improvement in SNR. However, we can apply the same approach to synthesize a more aggressive NTF with a higher-order and/or a higher OBG while considering the stability of the system. A higher OBG corresponds to lower in-band gain for the NTF, which can lead to an enhanced SNR. This effect is demonstrated in Fig. 12 for the PSD of a 6th-order CT BP $\Delta\Sigma$ M with OBGs of 1.5 and 1.7, using 8-tap BP-FIR feedback.

Fig. 12. (a) PSD and NTF of a 6th-order CT BP $\Delta\Sigma$ M with 8-tap BP-FIR DAC (flat NTF with OBG = 1.7). (b) PSDs of the same modulator with OBGs of 1.5 and 1.7.

## IV. Comparison between LP $\Delta\Sigma Ms$ and BP $\Delta\Sigma Ms$ with FIR Feedback

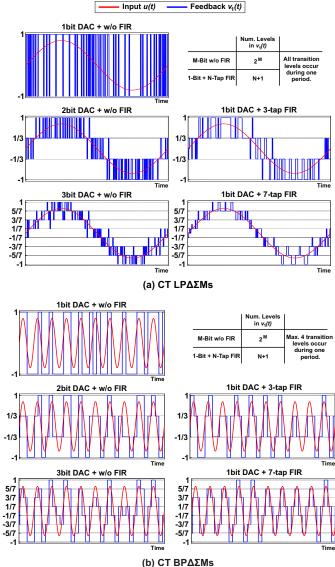

In general, for a single-bit operation, assuming that the modulator output bitstream is  $v[n] = \pm 1$ , the magnitude of transitions in v[n] is 2. In a LP $\Delta\Sigma$ M assisted with FIRDAC, this is decreased to  $2/N_{\text{fir}}$  thanks to the action of F(z). As a result, the step magnitudes are  $N_{\rm fir}$  times smaller, and in the input summation node the signals are similar to a multibit LP $\Delta \Sigma M$  [see Fig. 13(a)]. The same condition applies to BP $\Delta\Sigma$ M. As shown in the previous sections, we can emulate multi-bit operation by using a single-bit DAC and assisting it with a BP-FIR filter. In this case, the magnitude of transitions decreased, but not in a manner similar to the LP $\Delta\Sigma$ M. Due to the limitation imposed by  $f_n = f_s/4$ , the sampling occurs only four times during one period of the input signal. As a result, the signal can vary a lot from sample to sample. In such a situation, although we have levels in between, these levels are separated in the time domain [see Fig. 13(b)]. These discussions hold significance when aiming to explore the jitter performance of the modulator, since clock jitter is proportional to the height of the transitions in the DAC output [24]. Generally, the jitter is composed of an input related component and a quantization noise related component. In both cases of LP/BP $\Delta\Sigma$ Ms, no matter whether using multibit operation without FIRDAC or single-bit with FIRDAC, the jitter component associated with the quantization noise is reduced since this part of the jitter is proportional to the height of the transitions in the DAC output, while the jitter component related to the input signal is not changed. Bearing in mind that the variation in the input signal of a BP $\Delta\Sigma$ M is much more than that of a LP $\Delta\Sigma$ M. Recall that even multi-bit BP $\Delta\Sigma$ M has the same limitation.

Fig. 13. Feedback signal to the modulator  $[v_1(t)]$  in single-bit operation, multi-bit operation, and single-bit assisted with FIRDAC in: (a) LP $\Delta\Sigma$ Ms. (b) BP $\Delta\Sigma$ Ms.

#### V. BP-FIR FILTER CONSIDERATIONS

#### A. Number of FIR taps

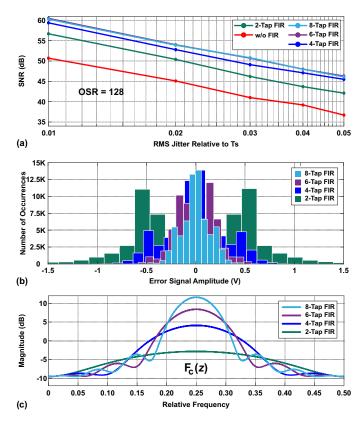

The jitter performance of a 4th-order BP $\Delta\Sigma$ M with FIR-DAC is shown in Fig. 14(a) for a -7 dBFS input. The result matches our expectations based on the discussion in the previous section. The performance of the system will not improve much after 6-tap, while in a similar case of LP $\Delta\Sigma$ M with FIRDAC, jitter immunity improves by increasing number of FIR taps up to 10-12 taps. Another metric in the decision for the number of FIR taps is the modulator input error signal swing, e(t), that is shown in Fig. 14(b) for a -5 dBFS input. Note that the signal swing is reduced with  $N_{\rm fir}$ . However, this reduction becomes less effective again after 6-tap. In addition, as seen from Table I,  $k_1$  increases with  $N_{\rm fir}$  and it turns out that the passband gain of the calculated  $F_c(z)$  increases with  $N_{\rm fir}$ as shown in Fig. 14(c). This phenomenon increases the second

Fig. 14. Impact of number of FIR taps  $(N_{\text{fir}})$  on: (a) Jitter performance. (b) Histogram of e(t). (c) Transfer function of  $F_c(z)$ .

resonator output swing. This extra swing can be compensated by adding a feedforward path around the resonators, although this would lead to a higher STF peak. Therefore, there will be a trade-off between hardware complexity, STF peaking, and signal swing.

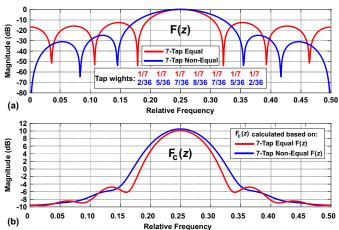

## B. Non-equal FIR taps

To this point, all the discussion was based on considering equal taps  $(1/N_{\rm fir})$  for the F(z) filter. We can improve the performance of the filter by using non-equal coefficients. This technique was used before in LP $\Delta\Sigma$ Ms (see [14] and [25]), but like other concepts in this paper, we can apply it to BP $\Delta\Sigma$ Ms. All we need to do is keep the sum of all the filter coefficients equal to 1 to maintain the unity gain in the passband. As an example, a 7-tap FIR with equal coefficients is compared with an optimized non-equal version of it in Fig. 15(a). The optimized F(z) shows better out-of-band rejection – similar to an FIR with more taps. Although the coefficients  $(a_{1-7})$ are not equal, we can still implement the filter by using unit elements. Considering the value of a unit element 1/36, the coefficients are  $a_{1,7} = 2$ unit,  $a_{2,6} = 5$ unit,  $a_{3,5} = 7$ unit, and  $a_4 = 8$ unit. With these changes in mind, a new set of coefficients should be calculated for  $F_c(z)$  to keep the NTF correct, as depicted in Fig. 15(b). In the next section, we will use this optimized filter for our circuit implementation.

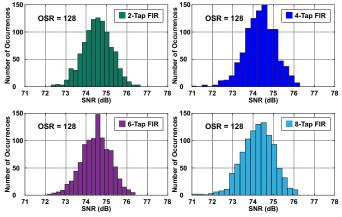

## C. Mismatch between FIR taps

At first glance, it might seem that by applying complicated feedback with a lot of weights (the FIR filter), the robustness

Fig. 15. Comparison between FIR with equal taps and FIR with non-equal taps for optimal out-of-band rejection: (a) Frequency response of F(z). (b) Frequency response of corresponding calculated  $F_c(z)$ .

Fig. 16. Monte Carlo SNR simulation results for a 4th-order CT BP $\Delta\Sigma$ M (CRFF-B) with BP-FIR DAC and 10% random mismatch in all tap weights.

of the system will degrade. However, this is not a correct assumption; random mismatch only alter the filter response. We performed Monte Carlo simulation by adding variation to the coefficients in all three FIR filters of a CRFF-B structure [see Fig. 8(b)] and determined the variation in ADC SNR. Fig. 16 shows the result for 1000 runs, considering different number of FIR taps. The tight distribution demonstrates the design's sturdiness.

#### VI. CIRCUIT IMPLEMENTATION

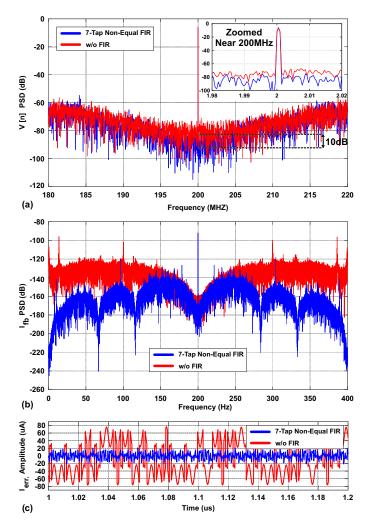

In this section, we will show how this system-level concept can easily be applied to well-known BP $\Delta\Sigma$ M circuit structures. We will present a case study of a single-bit CT BP $\Delta\Sigma$ M with a 7-tap BP-FIR DAC featuring non-equal coefficients  $[F(z) = (2/36) - (5/36)z^{(-2)} + (7/36)z^{(-4)} - (8/36)z^{(-6)} + (7/36)z^{(-8)} - (5/36)z^{(-10)} + (2/36)z^{(-12)}]$  using a CRFF-B structure. Fig. 17(a) illustrates the schematic of the circuit. The calculated coefficients ( $k_0$  to  $k_9$ ) for such a system are -0.097, -1.045, 0.054, -0.732, -0.793, -0.727, -0.561, -0.350, -0.158, and -0.036. The modulator is tuned for  $f_n = 200$  MHz when clocked at  $f_s = 800$  MHz. A fullydifferential circuit – not shown in Fig. 17(a) for simplicity

Fig. 17. (a) Single-ended schematic of a 4th-order CT BP $\Delta\Sigma$ M with 7-tap BP-FIR (negative values of delay and coefficients will be implemented using inversion in the fully differential circuit). (b) BP-FIR resistive DAC. (c) Limited gain, 1-pole macromodel of the op-amp. (d) 1.5 and 2-cycle delay elements.

Fig. 18. Single op-amp resonator with positive feedback [3].

– is implemented, and a 1-pole macromodel with main nonideal effects is considered for the op-amps [see Fig. 17(c)] in this example. The final result will be compared to a BP $\Delta\Sigma$ M of the same order and structure but in convectional form and without FIRDAC that is implemented with identical macromodel building blocks to have a fair comparison.

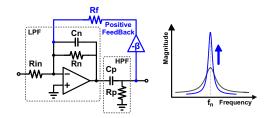

#### A. Resonator Circuit

The first step involves choosing between different structures for the resonator, a decision that should be made by considering the frequency range of operation. In this case, we will use positive-feedback single op-amp resonators [3] (see Fig. 18). This type of resonator is formed by wrapping positive feedback around a bandpass filter created by serially connecting an active lowpass filter and a passive highpass filter. Due to the imperfection of the circuit in a real implementation – finite GBW of amplifiers – the resonator experiences degradation in terms of gain in the passband. Several methods to overcome this limitation were suggested in [6] and [26]. This structure can be simplified and implemented in differential mode, and the transfer function of this resonator can be expressed as

$$H_{\text{Res}}(s) = \alpha \cdot \frac{\omega_o s}{s^2 + 2\zeta\omega_o s + \omega_o^2}$$

(20)

where  $\omega_o = 1/\sqrt{R_n R_p C_n C_p}$  is the resonant frequency. It has been demonstrated in [3] that when the values of capacitors and resistors are selected such that  $C_p = 2C_n$ and  $R_n = 2R_p$ , the damping factor ( $\zeta$ ) becomes zero. In this scenario, the outcome is an ideal resonator transfer function, and  $\alpha$  simplifies to  $-2R_p/R_{in}$ .

## B. BP-FIR DAC

There are several methods for implementing feedback DACs. Resistive DACs are more common with these types of resonators based on amplifiers. By properly choosing the resistor value at the input node of the modulator, we can adjust the noise level to an optimum value. Here, we choose a resistive DAC with reference switching [see Fig. 17(b)] for all three FIRDACs. The coefficients of the outermost FIR filter  $[F_1(z)]$  are  $R_{\text{dac}_{1,7}} = (36/2)R_1$ ,  $R_{\text{dac}_{2,6}} = (36/5)R_1$ ,  $R_{\text{dac}_{3,5}} = (36/7)R_1$ , and  $R_{\text{dac}_4} = (36/8)R_1$ . The second FIR filter  $[F_2(z)]$  also has the same coefficient, but with a scaling  $(k_2)$  compared to the first FIR. The third FIR filter  $[F_c(z)]$ has different coefficients for all the taps:  $R_{\rm dac_1} = R_3/k_3$ ,  $R_{\text{dac}_2} = R_3/k_4$ , ..., and  $R_{\text{dac}_7} = R_3/k_9$ . The forward coefficients  $k_0$  and  $k_1$  will be implemented using  $R_2$  and  $R_{f_2}$ , respectively, and a non-inverting amplifier in the summation node. As described in Section V, we may need a forward path around both resonators to compensate for the high output swing of the second resonator due to the gain in the passband of  $F_c(z)$ . This is carried out using  $R_{f_1}$ .

In order to complete the feedback loop, some additional delays are needed, implemented by D flip-flops. If we pass the output sequence through a D flip-flop, it will be delayed by 0.5-cycle. One cycle delay is achieved by serializing two D flip-flops with inverting clocks. In a similar manner, we can make a 2- and 1.5-cycle delay in the output, as shown in Fig. 17(d). It is clear that the system is sensitive to jitter in both the negative and positive edges of the main clock signal to the ADC, but the feedback loop filtering effectively suppresses it.

Fig. 19. Simulation results of a 4th-order CT BP $\Delta\Sigma$ M: (a) Effect of white clock jitter (1% relative RMS jitter) on the in-band output PSD. (b) PSD of feedback current to the first resonator [ $I_{\rm fb}$  in Fig. 17(a)]. (c) Swing of error current to the first resonator [ $I_{\rm err.}$  in Fig. 17(a)].

#### C. Simulation results

The output PSD of the overall BP $\Delta\Sigma$ M is shown in Fig. 19(a). The jitter performance of the single-bit modulator for white clock jitter, with an RMS value of 12.5 ps (1% relative RMS jitter), is improved by about 10 dB when compared with the conventional form. Another important improvement is shown in the PSD of the feedback current to the first resonator, which indicates that out-of-band components around dc and  $f_s/2$  are suppressed by more than 100 dB thanks to the filtering of the FIRDAC. This reduces the amplifier's input current swing by more than 3.5 times, as illustrated in Fig. 19(c). This relaxes the linearity requirement and could offer a subsequent advantage in terms of power consumption during circuit implementation.

## VII. CONCLUSION

A new kind of BP $\Delta\Sigma$ M has been proposed that uses a bandpass FIR filter in the feedback loop. This approach reduces the magnitude of the error signal at the modulator input node. As a result, loop-filter resonators mostly process error signals, thereby relaxing their requirements for dealing with signal excursions, including linearity and clock jitter. A systematic methodology is shown for the calculation of coefficients, both through a mathematical method and a more practical approach based on the analysis of the open-loop impulse response. It has been shown that using non-equal coefficients can improve the FIR filter performance. Additionally, the optimal number of FIR taps has been discussed, revealing that the improvement achieved through the FIR filter saturates after 6–8 taps, which is lower compared to LP $\Delta\Sigma$ M, where the choice of FIR taps is usually higher than 10-tap. The presented technique is versatile and can be applied to any arbitrary BP $\Delta\Sigma$ M architecture implemented with either DT or CT circuits.

#### REFERENCES

- R. Schreier and M. Snelgrove, "Bandpass sigma-delta modulation," Electron. Lett., vol. 25, no. 23, pp. 1560–1561, Nov. 1989.

- [2] H. Ghaedrahmati, J. Zhou, and R. B. Staszewski, "A 38.6-fJ/Conv.step inverter-based continuous-time bandpass ΔΣ ADC in 28 nm using asynchronous SAR quantizer," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 68, no. 9, pp. 3113–3117, Sep. 2021.

- [3] H. Chae, J. Jeong, G. Manganaro, and M. P. Flynn, "A 12 mW low power continuous-time bandpass ΔΣ modulator with 58 dB SNDR and 24 MHz bandwidth at 200 MHz IF," *IEEE J. Solid-State Circuits*, vol. 49, no. 2, pp. 405–415, Feb. 2014.

- [4] L. Jie, H. -W. Chen, B. Zheng, and M. P. Flynn, "A 100MHz-BW 68dB-SNDR tuning-free hybrid-loop DSM with an interleaved bandpass noiseshaping SAR quantizer," *in IEEE ISSCC Dig. Tech. Papers*, Feb. 2021, pp. 167–169.

- [5] A. Ashry and H. Aboushady, "A 4th order 3.6 GS/s RF ΣΔ ADC with a FoM of 1 pJ/bit," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 10, pp. 2606–2617, Oct. 2013.

- [6] R. Lu, and M. P. Flynn, "A direct frequency-interleaving continuoustime bandpass delta-sigma ADC," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 70, no. 10, pp. 3821–3831, Oct. 2023.

- [7] S. Gupta, D. Gangopadhyay, H. Lakdawala, J. C. Rudell, and D. J. Allstot, "A 0.8–2GHz fully-integrated QPLL-timed direct-RF-sampling bandpass ΣΔ ADC in 0.13 μm CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 5, pp. 1141–1153, May 2012.

- [8] A. Sayed, T. Badran, M.-M. Louërat, and H. Aboushady, "A 1.5-to-3.0GHz tunable RF sigma-delta ADC with a fixed set of coefficients and a programmable loop delay," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 9, pp. 1559–1563, Sep. 2020.

- [9] S. Pavan, R. Schreier, and G. C. Temes, Understanding Delta-Sigma Data Converters. Wiley-IEEE Press, 2nd ed., 2017.

- [10] J. M. de la Rosa, *Sigma-Delta Converters: Practical Design Guide*. Wiley-IEEE Press, 2nd ed., 2018.

- [11] J. Harrison, M. Nesselroth, R. Mamuad, A. Behzad, A. Adams, and S. Avery, "An LC bandpass ΔΣ ADC with 70dB SNDR over 20MHz bandwidth using CMOS DACs," *in IEEE ISSCC Dig. Tech. Papers*, Feb. 2012, pp. 146–148.

- [12] J. Ryckaert, J. Borremans, B. Verbruggen, L. Bos, C. Armiento, J. Craninckx and G. Van der Plas, "A 2.4 GHz low-power sixth-order RF bandpass ΔΣ converter in CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 11, pp. 2873–2880, Nov. 2009.

- [13] J. Gorji, S. Pavan, and J. M. de la Rosa, "Bandpass ΔΣ modulators with FIR feedback," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2023, pp. 1–5.

- [14] O. Oliaei, "Sigma-delta modulator with spectrally shaped feedback," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 50, no. 9, pp. 518–530, Sep. 2003.

- [15] S. Pavan, "Finite-impulse-response (FIR) feedback in continuous-time delta-sigma converters," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Apr. 2018, pp. 1–8.

- [16] J. Chi, J. Wagner, J. Anders, and M. Ortmanns, "Digital interferer suppression and jitter reduction in continuous-time bandpass ΣΔ modulators," *in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2017, pp. 1–4.

- [17] O. Shoaei and W. M. Snelgrove, "Design and implementation of a tunable 40 MHz-70 MHz Gm-C bandpass ΔΣ modulator," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 44, no. 7, pp. 521– 530, July 1997.

- [18] N. Beilleau, H. Aboushady, and M.M. Loureat, "Using finite impulse response feedback DACs to design ΣΔ modulators based on LC filters," *in Proc. IEEE Int. Midwest Symp. Circuits Syst. (MWSCAS)*, Aug. 2005, pp. 696–699.

- [19] R. Schreier, Delta Sigma Toolbox. [Online]. Available: https://www.mathworks.com/matlabcentral/fileexchange/19-deltasigma-toolbox, 2023.

- [20] H. Aboushady and M.-M. Louerat, "Systematic approach for discretetime to continuous-time transformation of ΣΔ modulators," *in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2002, pp. 229–232.

- [21] M. Ortmanns, and F. Gerfers, Continuous-Time Sigma-Delta A/D Conversion, Fundamentals, Performance Limits and Robust Implementations. Springer, 2006.

- [22] K. Ogata, Discrete-Time Control Systems. Prentice-Hall, 1987.

- [23] S. Pavan, "Systematic design centering of continuous time oversampling converters," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 3, pp. 158–162, Mar. 2010.

- [24] H. Tao, L. Toth, and J. M. Khoury, "Analysis of timing jitter in bandpass sigma-delta modulators," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 46, no. 8, pp. 991–1001, Aug. 1999.

- [25] A. Abdelaal, M. Pietzko, M. A. Mokhtar, J. G. Kauffman, and M. Ortmanns, "FIR filter with symmetric non-equal coefficients for CT deltasigma modulators," *in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2021, pp. 1–5.

- [26] S. Kim, C. Rhee, and S. Kim, "A wide dynamic range multi-mode bandpass continuous-time delta-sigma modulator employing single-opamp resonator with positive resistor-feedback," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 2, pp. 235–239, Feb. 2020.

Javad Gorji (Student Member, IEEE) received the B.S. degree in electrical engineering from Azad University, Tehran, in 2013, and the M.S. degree (with honors) in electrical engineering from Shahed University, Tehran, in 2017. He is currently pursuing a Ph.D. degree at the University of Seville. In 2021, he joined the Institute of Microelectronics of Seville (IMSE-CNM) as a research scholar supported by an FPI scholarship from the Ministry of Science and Innovation of Spain, where he is involved in the design of analog-to-digital converters for RF

applications. His research interests include analog and mixed-signal integrated circuit designs for high-speed data converters and frequency synthesizers.

Shanthi Pavan (Fellow, IEEE) obtained the B.Tech degree in Electronics and Communication Engineering from the Indian Institute of Technology, Madras in 1995 and the M.S and Sc.D degrees from Columbia University, New York in 1997 and 1999 respectively. From 1997 to 2000, he was with Texas Instruments in Warren, New Jersey, where he worked on high speed analog filters and data converters. From 2000 to June 2002, he worked on microwave ICs for data communication at Bigbear Networks in Sunnyvale, California. Since July 2002, he has been

with the Indian Institute of Technology-Madras, where he is now the NT Alexander Institute Chair Professor of Electrical Engineering. His research interests are in the areas of high speed analog circuit design and signal processing.

Dr. Pavan is the recipient of several awards, including the IEEE Circuits and Systems Society Darlington Best Paper Award (2009), the Shanti Swarup Bhatnagar Award (2012) and the Swarnajayanthi Fellowship (2009) (from the Government of India). He is the author of Understanding Delta-Sigma Data Converters (second edition), with Richard Schreier and Gabor Temes, which received the Wiley-IEEE Press Professional Book Award for the year 2020. Dr. Pavan has served as the Editor-in-Chief of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS, and on the editorial boards of both parts of the IEEE Transactions on Circuits and Systems. He has served on the technical program committee of the International Solid State Circuits Conference, and been a Distinguished Lecturer of the Solid-State Circuits and Circuits-and-Systems Societies. He currently serves as the Vice President of Publications for the IEEE Solid-State Circuits Society, and on the editorial boards of the IEEE JOURNAL OF SOLID-STATE CIRCUITS and the IEEE SOLID-STATE CIRCUITS LETTERS. He is a fellow of the Indian National Academy of Engineering, the Indian National Academy of Science and an IEEE fellow

José M. de la Rosa (Fellow, IEEE) received the M.S. degree in Physics in 1993 and the Ph.D. degree in Microelectronics in 2000, both from the University of Seville, Spain. Since 1993 he has been working at the Institute of Microelectronics of Seville (IMSE), which is in turn part of the Spanish Microelectronics Center (CNM) of the Spanish National Research Council (CSIC). He is also a Full Professor at the Dpt. of Electronics and Electromagnetism of the University of Seville. His main research interests are in the field of analog and mixed-signal integrated

circuits, especially high-performance data converters. In these topics, Dr. de la Rosa has participated in a number of Spanish and European research and industrial projects, and has co-authored over 270 international publications, including journal and conference papers, book chapters and the books *Systematic Design of CMOS Switched-Current Bandpass Sigma-Delta Modulators for Digital Communication Chips* (Kluwer, 2002), *CMOS Cascade Sigma-Delta Modulators for Sensors and Telecom: Error Analysis and Practical Design* (Springer, 2006), *Nanometer CMOS Sigma-Delta Modulators for Software Defined Radio* (Springer, 2011) and *CMOS Sigma-Delta Converters: Practical Design Guide* (Wiley-IEEE Press, 2013, 2nd Edition, 2018). He is in the World's Top 2% Scientists List from Stanford University (editions 2019, 2020 and 2022).

Dr. de la Rosa is an IEEE Fellow and member of the IEEE Circuits and Systems Society (CASS) and the IEEE Solid-State Circuits Society (SSCS). He is a Member-at-Large of the IEEE-CASS Board of Governors (BoG) for the 2023-2025 term. He served as a Distinguished Lecturer of IEEE-CASS (term 2017-2018), and as Chair of the Spain Chapter of IEEE-CASS during the term 2016-2017. He was at the front of the Editorial Board of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, where he served as Deputy Editor-in-Chief since 2016 to 2019, and as Editorin-Chief in the term 2020-2021. He is a member of the TechRxiv Editorial Advisory Board since 2022. He also served as Associate Editor for IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I: REGULAR PAPERS, where he received the 2012-2013 Best Associate Editor Award and was Guest Editor for the Special Issue on the Custom Integrated Circuits Conference (CICC) in 2013 and 2014. He served as Guest Editor of the Special Issue of the IEEE J. on Emerging and Selected Topics in Circuits and Systems on Next-Generation Delta-Sigma Converters. He is a member of the Analog Signal Processing Technical Committee of IEEE-CASS and of the Steering Committee of IEEE MWSCAS. He has also been involved in the organizing and technical committees of diverse international conferences, among others IEEE ISCAS, IEEE MWSCAS, IEEE ICECS, IEEE LASCAS, IFIP/IEEE VLSI-SoC, DATE and ESSCIRC. He served as TPC chair of IEEE MWSCAS 2012, IEEE ICECS 2012, IEEE LASCAS 2015 and IEEE ISICAS (2018, 2019). He has been a member of the Executive Committee of the IEEE Spain Section (terms 2014-2015 and 2016-2017), where he served as Membership Development Officer during the term 2016-2017. He has been appointed as Editor-in-Chief of IEEE TCAS-I for the term 2024-2025.