### **TESIS DOCTORAL**

# ANALISIS Y SINTESIS DE CIRCUITOS DIGITALES ESTOCASTICOS PARA LA REALIZACION DE SISTEMAS ANALOGICOS

por

Sergio L. Toral Marín

Ingeniero Industrial por la E.S. de Ingenieros de la Universidad de Sevilla

Presentada en la

Escuela Superior de Ingenieros

de la

Universidad de Sevilla

para la obtención del

Grado de Doctor Ingeniero Industrial

Sevilla, Septiembre de 1999

### **TESIS DOCTORAL**

# ANALISIS Y SINTESIS DE CIRCUITOS DIGITALES ESTOCASTICOS PARA LA REALIZACION DE SISTEMAS ANALOGICOS

Autor: Sergio L. Toral Marín

Director: José Manuel Quero Reboul

"La piedra de toque de una inteligencia de primera clase es la aptitud para mantener dos ideas opuestas en la mente y conservar al mismo tiempo la capacidad para actuar"

F. Scott Fitzgerald

# Agradecimientos

Quiero expresar mi agradecimiento a todas aquellas personas que han colaborado en el desarrollo de esta Tesis Doctoral. En primer lugar quiero citar a mi Director de Tesis, **D. José M. Quero Reboul** por la constante supervisión del trabajo que estaba realizando, su aportación personal en muchas de las ideas que se exponen y por las muchas horas que ha dedicado a discutir conmigo infinidad de detalles.

Quiero agradecer también al Director del Grupo de Tecnología Electrónica, **D. Leopoldo García Franquelo**, la ayuda prestada durante la realización de la Tesis.

También hago extensivos los agradecimientos a todos mis compañeros del Grupo de Tecnología Electrónica que, en mayor o menor medida, han servido de estímulo en los momentos de mayor desorientación y que con sus comentarios han ayudado a aclarar las ideas en numerosas ocasiones.

Finalmente, quiero agradecer a mi familia y a Rocío su apoyo y ánimo constante.

Sevilla, 5 de Septiembre de 1999.

# Resumen de la Tesis

El procesamiento estocástico constituye una de las líneas de investigación del Grupo de Tecnología Electrónica (GTE). Los sistemas estocásticos se encuentran caracterizados porque la información se representa mediante un conjunto de trenes de pulsos aleatorios síncronos. El valor de una variable real perteneciente al intervalo [0,1] se codifica de una manera muy especial: es la probabilidad de que, en un ciclo de reloj dado, el tren de pulsos asociado a la señal tome un valor lógico alto. Aprovechando las similitudes entre el álgebra de probabilidades y el álgebra de Boole, es posible desarrollar circuitos electrónicos digitales capaces de implementar, de una manera muy simple, operaciones aritméticas básicas. En particular, la suma y el producto son las operaciones más profundamente estudiadas por dos motivos: son las operaciones mayoritariamente involucradas en cualquier cálculo aritmético y además se encuentran especialmente presentes en las redes neuronales, que es una de las aplicaciones donde el procesamiento estocástico ha encontrado mayor eco. La implementación hardware de redes neuronales es un problema no resuelto de manera definitiva, y que ha sido extensamente tratado en tesis precedentes realizadas dentro del Grupo. Otras aportaciones de estos trabajos dentro del campo del procesamiento estocástico son convertidores entre los dominios analógico y estocástico y estudios sobre las posibilidades de la lógica estocástica como plataforma de implementación de controladores borrosos. Como continuación de tesis doctorales anteriores, esta Tesis pretende estudiar las posibilidades de la lógica estocástica para implementar sistemas analógicos. La idea es volver al concepto de lo que significa una codificación mediante trenes de pulsos aleatorios: se trata de una codificación que es cuantizada en cuanto a su forma de representación (señal bipolar, como en los diseños digitales) pero no en cuanto a la interpretación del valor codificado, que es continuo, pues se trata de la esperanza matemática de tener un valor lógico a nivel alto, es decir, de una probabilidad. Dado que la codificación estocástica es intrínsecamente bipolar, todos los circuitos propuestos son totalmente digitales. Frente a otras alternativas de implementación del procesamiento estocástico mediante una circuitería analógica o mixta, propuesta en otros grupos de investigación, se ha optado por una implementación digital por un motivo muy simple: los circuitos digitales resultan año a año más potentes y baratos con unas escalas de integración y velocidades que se duplican cada 18 meses y unos precios que bajan proporcionalmente. Además, los sistemas

de desarrollo de los circuitos digitales se encuentran mucho más avanzados que los analógicos, permitiendo el desarrollo e implementación de sistemas complejos. Los circuitos y aplicaciones propuestos en la Tesis tienen en los dispositivos programables digitales su medio natural de implementación. Visto desde el punto de vista contrario, los dispositivos programables digitales tienen en el procesamiento estocástico propuesto una puerta de acceso a una funcionalidad digital integrada dentro del propio dispositivo.

La Tesis doctoral se encuentra dividida en dos partes claramente diferenciadas, como se desprende del título:

- Una primera de análisis. donde se definen los bloques constructivos básicos que implementan funciones analógicas utilizadas habitualmente: sistemas de primer orden, integradores, circuitos de cálculo de divisiones y raíces cuadradas. Se propone una extensión de la aritmética tradicional estocástica, basada en productos y sumas, como medio de implementar sistemas analógicos complejos. Asimismo, se estudian las interfases adecuadas entre los dominios analógico, digital y estocástico para llegar a un sistema de procesamiento cerrado.

- Una segunda de síntesis donde se proponen tres aplicaciones que conjugan los bloques previamente analizados.

Tras un capítulo introductorio donde se introducen el concepto, la aritmética básica y aplicaciones generales del procesamiento estocástico, se pasa a caracterizar los bloques constructivos básicos que se utilizarán posteriormente. En primer lugar, se presenta un bloque constructivo básico consistente en un sistema de primer orden. Este bloque constructivo se caracteriza como si de un sistema analógico se tratase, es decir, mediante la atenuación y el desfase de la señal de salida con respecto a la de entrada. Como circuito de aplicación inmediato se propone un circuito detector de envolvente, basado en un circuito seguidor que actúa sobre un contador que incrementa de manera mucho más rápida que decrementa, de forma análoga a un circuito típico analógico detector de envolvente, donde la constante de carga del condensador es mucho más pequeña que la de descarga.

Este bloque se denomina básico porque sobre él se introducen varias generalizaciones:

- Conexión en cascada, para lograr sistemas de orden superior

- Introducción de ceros

- Introducción de un factor de ganancia

Esta última generalización permite desarrollar circuitos que implementan funciones no lineales como son los circuitos de cálculo de divisiones y de raíces cuadradas.

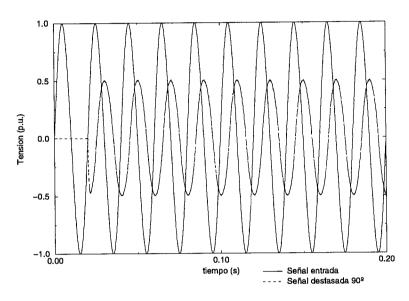

Finalmente, se presenta un circuito integrador que permite la resolución de ecuaciones diferenciales, como se verá en una de las aplicaciones. Como ejemplo de aplicación, se propone un circuito desfasador de 90°.

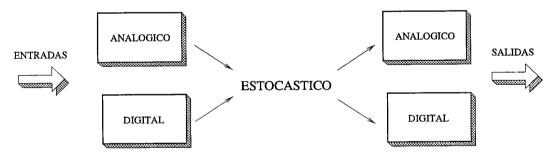

Todos los circuitos anteriores forman, junto a la suma y el producto, los elementos básicos que se van a utilizar en las aplicaciones propuestas a continuación y constituyen el procesamiento estocástico propiamente dicho. No obstante, para disponer de un sistema cerrado es preciso disponer de unas interfases adecuados entre los dominios analógico, digital y estocástico. De este modo, dadas unas variables de entrada al problema, bien analógicas, bien digitales, son convertidas a trenes de pulsos aleatorios, procesados mediante los bloques constructivos anteriores para recuperar finalmente las señales analógicas o digitales que constituyen las señales de salida.

En este sentido, para las variables de entrada se definen:

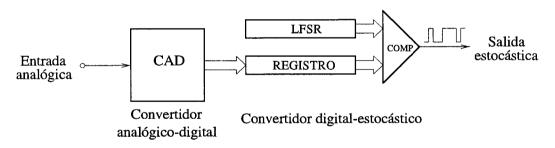

- Conversión digital-estocástica.

Realizada base de unos generadores de números pseudo-aleatorios, consistentes en registros de desplazamiento realimentados linealmente (LF-SR), estudiados ampliamente en la bibliografía.

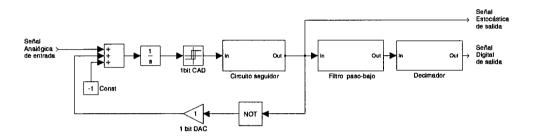

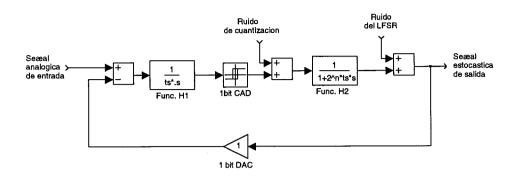

- Conversión analógica-estocástica.

Existen algunos esquemas definidos en la bibliografía, pero tienen el inconveniente de que su ancho de banda es demasiado limitado para las aplicaciones que se pretenden realizar. Aprovechando los esquemas típicos de convertidores sobremuestreados, se propone una realización mixta, con una pequeña circuitería analógica externa, que mejora las prestaciones de los esquemas existentes.

Por su parte, para las variables de salida se definen:

- Conversión estocástica-digital.

No consiste más que en un contador que estima la probabilidad a partir de la frecuencia relativa de valores lógicos a nivel alto en una secuencia relativamente larga.

- Conversión estocástica-analógica.

Similar a la anterior pero con una red RC. Aprovechando las posibilidades de redundancia en la información del cálculo estocástico y el carácter pseudo-aleatorio de los LFSRs, se propone un esquema que mejora las prestaciones del anterior.

En la segunda parte de la Tesis, dedicada a aplicaciones, se sintetizan los bloques definidos en tres ejemplos de aplicación, que pretenden demostrar las posibilidades del cálculo estocástico para implementar sistemas analógicos. La caracterización de los bloques constructivos de los capítulos II y III ha detallado para cada uno de ellos sus parámetros de diseño y sus limitaciones. En base a ello, se propone un método general de diseño que se utilizará en las aplicaciones.

En general, las dinámicas que se pueden procesar son varios órdenes de magnitud inferiores a la frecuencia de trabajo digital, por lo que, cuanto más rápidos sean los dispositivos digitales (tendencia que crece año tras año) proporcionalmente aumenta el ancho de banda que la lógica estocástica puede soportar.

La primera de las aplicaciones propuestas es la realización de filtros de orden n, conectando en cascada varios de los sistemas de primer orden. Con las interfases de entrada y salida es posible contar con un sistema digital, sobre un dispositivo programable, con una señal analógica de entrada y la correspondiente señal filtrada a la salida.

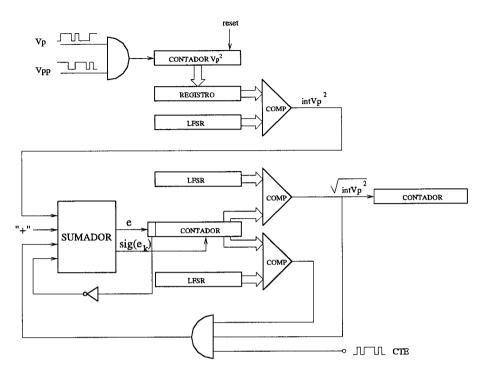

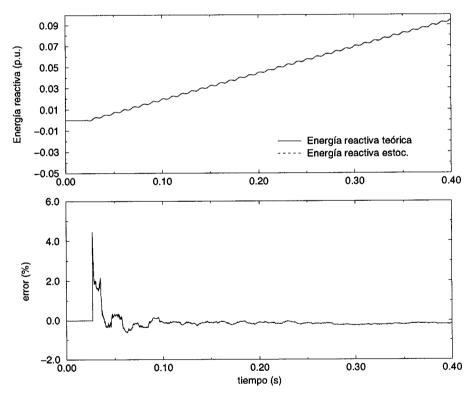

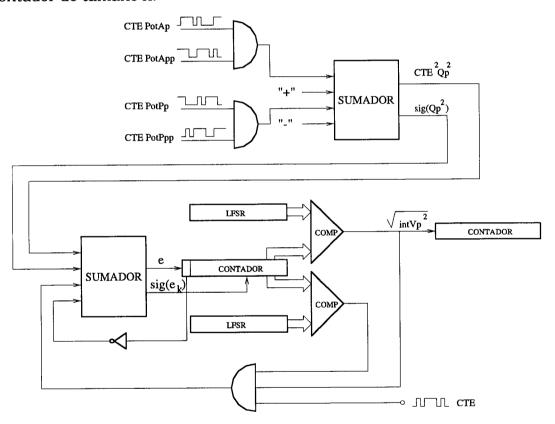

La segunda aplicación se refiere a la realización de un medidor de potencia, capaz de suministrar los parámetros típicos de un sistema de potencia: energía y potencia activa y reactiva, factor de potencia, potencia aparente y valores máximos y eficaces. En este caso, las variables de entrada son la intensidad y la tensión, y los de salida se proporcionan digitalmente.

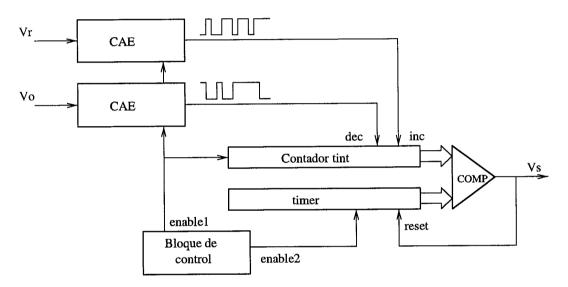

La última de las aplicaciones es un control integral y por pasividad de un convertidor serie resonante. En definitiva, se trata de resolver un conjunto de ecuaciones diferenciales, mucho más complejo en el caso del control por pasividad. Las variable de entrada son la referencia y la salida de la fuente, mientras que la de salida es una señal PWM que actúa sobre el convertidor.

Como se desprende de las aplicaciones propuestas, se ha elegido el campo de la electrónica de potencia para dos de ellas. Esto se debe a que, en primer lugar, la electrónica de potencia proporciona un elevado número de aplicaciones donde no se requieren dinámicas excesivamente elevadas. A esto hay que unir la experiencia existente en el Grupo de Tecnología Electrónica en este campo para justificar su utilización.

En general, se puede pensar en una gran multitud de aplicaciones en las que no se requieren dinámicas muy elevadas y donde el cálculo estocástico representa una alternativa de bajo coste, eficiente en área, frente a otras opciones como procesadores de propósito general.

# Índice General

| 1 | Intr | roducción                                                      | 1  |  |  |  |

|---|------|----------------------------------------------------------------|----|--|--|--|

|   | 1.1  | Consideraciones previas                                        |    |  |  |  |

|   | 1.2  | Procesamiento estocástico                                      | 2  |  |  |  |

|   | 1.3  | Aritmética estocástica                                         | 3  |  |  |  |

|   |      | 1.3.1 Producto                                                 | 3  |  |  |  |

|   |      | 1.3.2 Suma                                                     | 5  |  |  |  |

|   | 1.4  | Generación de trenes de pulsos estocásticos                    | 9  |  |  |  |

|   |      | 1.4.1 Métodos digitales de generación de trenes de pulsos es-  |    |  |  |  |

|   |      | tocásticos                                                     | 9  |  |  |  |

|   |      | 1.4.2 Métodos analógicos de generación de trenes de pulsos es- |    |  |  |  |

|   |      | tocásticos                                                     | 12 |  |  |  |

|   | 1.5  | Aplicaciones                                                   | 13 |  |  |  |

|   | 1.6  | Objetivos                                                      | 15 |  |  |  |

| 2 | Doo  | alizaciones estocásticas de sistemas continuos                 | 18 |  |  |  |

| _ | 2.1  |                                                                | 18 |  |  |  |

|   | 2.2  | Realización digital de un sistema de primer orden              | 19 |  |  |  |

|   | ۷.۷  | 2.2.1 Descripción del bloque básico                            | 19 |  |  |  |

|   |      | 2.2.2 Suma con signo                                           | 21 |  |  |  |

|   |      | 2.2.3 Caracterización                                          | 22 |  |  |  |

|   |      | 2.2.4 Respuesta en frecuencia                                  | 24 |  |  |  |

|   |      | 2.2.5 Aplicación: circuito estocástico detector de pico        | 26 |  |  |  |

|   | 2.3  | Introducción de un factor de ganancia                          | 28 |  |  |  |

|   | 2.3  | Extensión a sistemas de orden n                                | 32 |  |  |  |

|   | 2.4  | Introducción de ceros                                          | 35 |  |  |  |

|   | 2.6  | Circuitos de cálculo de funciones no lineales                  | 36 |  |  |  |

|   | 2.0  | 2.6.1 Circuito de cálculo de divisiones                        | 36 |  |  |  |

|   |      | 2.6.2 Circuito de cálculo de divisiones                        | 37 |  |  |  |

|   | 0.7  | = · • · · ·                                                    | 38 |  |  |  |

|   | 2.7  | Circuito integrador                                            |    |  |  |  |

|   |      | 2.7.1 Aplicación: circuito desfasador                          | 40 |  |  |  |

| 3 | Cor  | nversión analógica-digital-estocástica                         | 42 |  |  |  |

|   | 3.1  | <del></del>                                                    | 42 |  |  |  |

|   | 3.2  | Conversión estocástica digital                                 | 45 |  |  |  |

|   | 3.3 | Conve                  | ersión analógica estocástica                                   | 47  |  |  |  |  |

|---|-----|------------------------|----------------------------------------------------------------|-----|--|--|--|--|

|   |     |                        | Realización física                                             |     |  |  |  |  |

|   | 3.4 |                        | ersión Estocástica Analógica                                   |     |  |  |  |  |

| 4 | Apl | icacio                 | nes                                                            | 60  |  |  |  |  |

|   | 4.1 | Introducción           |                                                                |     |  |  |  |  |

|   |     |                        | Método de diseño                                               | 62  |  |  |  |  |

|   | 4.2 |                        | zaciones digitales de filtros analógicos                       |     |  |  |  |  |

|   | 4.3 |                        | las de potencia                                                |     |  |  |  |  |

|   |     | 4.3.1                  | Medidas de potencia activa                                     |     |  |  |  |  |

|   |     |                        | Medidas de potencia reactiva                                   |     |  |  |  |  |

|   |     |                        | Circuitos estocásticos básicos                                 |     |  |  |  |  |

|   |     | 4.3.4                  |                                                                |     |  |  |  |  |

|   |     | 4.3.5                  | Realización física                                             | 87  |  |  |  |  |

|   | 4.4 |                        | ación del cálculo estocástico a la realización digital de sis- |     |  |  |  |  |

|   |     | s analógicos complejos |                                                                |     |  |  |  |  |

|   |     | 4.4.1                  | Introducción                                                   |     |  |  |  |  |

|   |     | 4.4.2                  | · · · · · · · · · · · · · · · · · · ·                          |     |  |  |  |  |

|   |     | 4.4.3                  |                                                                |     |  |  |  |  |

|   |     | 4.4.4                  | Implementación estocástica de un control integral              |     |  |  |  |  |

|   |     |                        | Implementación estocástica de un control por pasividad .       |     |  |  |  |  |

|   |     | 4.4.5                  | implementación estocastica de un control por pasividad.        | J(  |  |  |  |  |

| 5 | Coı | nclusio                | ones y futuras líneas                                          | 103 |  |  |  |  |

# Capítulo 1

# Introducción

### 1.1 Consideraciones previas

El procesamiento de señales aleatorias fue presentado por primera vez por von Newmann en 1956 [1]. En sus trabajos, von Newmann trataba de explicar algunos fenómenos del sistema nervioso siguiendo principios estadísticos. Su intención no era tanto modelar comportamientos neurofisiológicos sino demostrar que a partir de una representación inexacta de la información y mediante unidades de procesamiento muy sencillas, era posible llegar a resultados precisos aprovechando la redundancia de la información. Hacia finales de los años 60, la proliferación de trabajos en este campo fue muy abundante. La mayoría se centraban en buscar realizaciones hardware capaces de resolver ecuaciones diferenciales o de imitar el comportamiento del sistema nervioso. A este respecto, hay que destacar los trabajos de Gaines [2], [3] y Ribeiro [4], que ya proponen algunas arquitecturas para la realización de computadores estocásticos. La idea de emplear la probabilidad de un tren de pulsos digitales como una cantidad analógica era utilizada para simular elementos típicos de computadoras analógicas: multiplicadores, sumadores, inversores, integradores...De esta manera se introducía la nueva aproximación de computadoras estocásticas como una vía alternativa a las tradicionales realizaciones analógicas, digitales o incluso mixtas. El principal inconveniente del procesamiento estocástico estaba en la limitación tecnológica en cuanto al ancho de banda que los computadores estocásticos eran capaces de procesar. Hay que tener en cuenta que el hecho de representar una cantidad analógica como una probabilidad supone implícitamente la necesidad de que ésta se manifieste como una frecuencia relativa en una secuencia lo suficientemente larga. En consecuencia, la velocidad de procesamiento estocástico deberá ser mucho mayor que la dinámica de la señal analógica que queremos procesar. Como resultado de lo anterior, las aplicaciones de la lógica estocástica se dirigieron fundamentalmente al campo de procesamiento paralelo de la información, en particular, redes neuronales. Interés que llega hasta fechas actuales, como demuestran recientes trabajos en esta línea [5], [6], [7], [8]. El avance de la tecnología, sobre todo en lo que se refiere a dispositivos programables, cuyas velocidades y tamaños aumentan a pasos agigantados, permite retomar aquellas ideas de los años 60 para llegar a implementaciones que, siendo totalmente digitales, permiten un procesamiento, en determinados casos, mucho más simple y eficientes que el cálculo tradicional [9]-[11].

### 1.2 Procesamiento estocástico

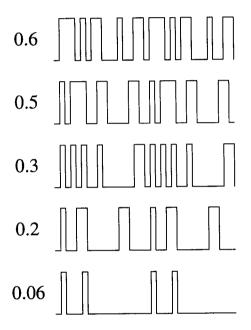

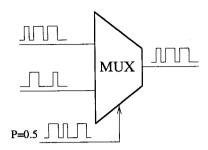

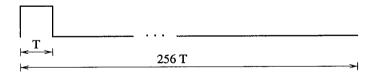

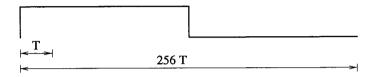

El procesamiento de señales binarias pseudo aleatorias se basa en codificar un valor digital o analógico como un tren de pulsos aleatorios en el que la información viene representada por la media de ese tren de pulsos (figura 1.1). Dicho de otra forma, la probabilidad de que aparezca un pulso a un nivel lógico alto es el valor que se ha codificado. Una probabilidad no puede ser

Figura 1.1: Codificación estocástica de la información

medida exactamente. Tan sólo puede ser estimada por la frecuencia relativa de eventos "valores lógicos a nivel alto" en una secuencia lo suficientemente larga. En consecuencia, el procesamiento estocástico va a introducir errores en la forma de desviaciones típicas al intentar estimar la probabilidad de una secuencia finita. Nótese que la probabilidad es una variable continua que no va a estar sujeta a errores de redondeo o discretización, sino a un error estadístico en la forma de una desviación típica.

Estadísticamente, la secuencia de valores lógicos que codifican un valor es un proceso estocástico discreto [12], formado por una sucesión de variables aleatorias de Bernouilli. Si consideramos una secuencia formada por N bits en

la que k de ellos son valores lógicos altos, diremos que el valor codificado por esa secuencia es  $\hat{p}=k/N$ , con una desviación típica asociada a la estimación de la probabilidad de  $\sigma(\hat{p})=\sqrt{p(1-p)}/N$ , siendo p la probabilidad de un valor alto. La precisión en la estimación de la media con la frecuencia relativa aumenta con la raíz cuadrada de la longitud N de la secuencia. De acuerdo con la expresión matemática de la varianza, el caso más desfavorable desde el punto de vista de la precisión ocurre para p=1/2. Se puede demostrar fácilmente [13] que, en este caso, la longitud de la secuencia necesaria para llegar a una precisión de n bits viene dada por  $N=2^{2n-2}$ , siendo N la longitud de la secuencia.

### 1.3 Aritmética estocástica

La analogía que existe entre el álgebra de probabilidades y el álgebra de Boole es aprovechada para obtener unas unidades de procesamiento muy simples. Las dos operaciones básicas descritas en la literatura son la suma y el producto. El motivo es que son las operaciones fundamentales involucradas en las redes neuronales, que es una de las aplicaciones donde ha encontrado mayor resultado una codificación estocástica de la información.

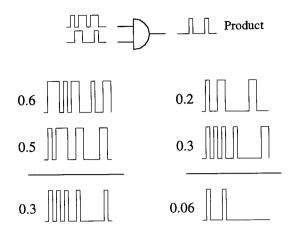

### 1.3.1 Producto

El álgebra elemental de probabilidades establece que si dos eventos son estadísticamente independientes, la probabilidad de la intersección de ambos eventos es igual al producto de las probabilidades de cada uno de ellos. Electrónicamente, dados dos trenes de pulsos estocásticos, una puerta AND realiza el producto de ambos (figura 1.2). La probabilidad de tener un "1" lógico a la salida será igual al producto de las probabilidades de los trenes de pulsos de entrada, puesto que sólo cuando coincidan dos "1" lógicos a la entrada aparecerá éste a la salida. La única condición imprescindible es que ambas codificaciones sean estadísticamente incorreladas. La incorrelación deberá ser además espacial y temporal. La incorrelación espacial garantiza obtener a la salida un tren de pulsos cuya probabilidad de tener un valor lógico alto es el producto de las probabilidades de los trenes de entrada. La incorrelación temporal permite obtener a la salida una secuencia con buenas propiedades estadísticas para continuar su posterior procesamiento estocástico El resultado anterior es extensible al producto de n trenes de pulsos estocásticos utilizando una puerta AND de n entradas.

Para realizar una aritmética con signo, existen tres posibilidades diferentes:

La primera consiste en tratar el signo como un bit aparte, de modo que para codificar una señal con signo harían falta dos líneas: el tren de pulsos y el signo. La aritmética del signo en el producto sería una puerta XOR.

Figura 1.2: Aritmética estocástica: producto

• La segunda opción fue propuesta por Gaines [3] y consiste en utilizar dos trenes de pulsos, uno que codifique la parte positiva y otro la negativa, de modo que el valor codificado viene dado por la diferencia de ambos. El máximo valor positivo vendría dado por el tren positivo siempre a nivel alto y el negativo a cero. El valor cero vendría codificado por ambos trenes a nivel bajo, o bien con la misma probabilidad. El producto de dos trenes con signo sería igual a dos trenes, el positivo o+ y el negativo o-:

$$o^{+} = a^{+}b^{+} + a^{-}b^{-}$$

$o^{-} = a^{+}b^{-} + a^{-}b^{+}$  (1.1)

• La última posibilidad es llevar el signo implícito en el propio tren de pulsos [11]. Considérense dos trenes de pulsos  $v_1$  y  $v_2$  comprendidos en el intervalo [-1,1]. Dado que no es posible codificar densidades de pulsos negativas, se codifican estocásticamente las cantidades  $p_1$  y  $p_2$  definidas como:

$$p_1 = \frac{v_1 + 1}{2}$$

$$p_2 = \frac{v_2 + 1}{2}$$

(1.2)

La operación se lleva a cabo mediante una puerta XOR. A la salida se obtiene un tren de pulsos con una probabilidad:

$$p_0 = p_1(1-p_2) + p_2(1-p_1)$$

Poniendo esta expresión en función de  $v_1$  y  $v_2$ :

$$p_0 = \frac{1}{2} - \frac{1}{2}v_1v_2$$

Aplicando la transformación inversa, esto es,  $v_0=2p_0-1$ , resulta:

$$v_0 = -v_1 v_2 (1.3)$$

La principal ventaja que tiene este esquema es que los signos de los términos a multiplicar vienen codificados implícitamente en el propio tren de pulsos. El inconveniente es que sólo se pueden multiplicar dos términos.

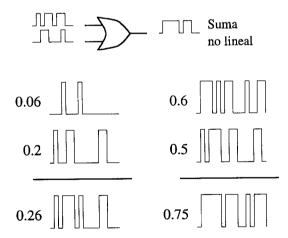

#### 1.3.2 Suma

La suma es una operación más compleja de realizar estocásticamente. La forma más simple, que sería una puerta OR, presenta problemas de saturación con densidades de pulsos elevadas, por lo que en la bibliografía se han introducido otras técnicas basadas en multiplexores, contadores reversibles o en la transformación exponencial.

#### **Puertas OR**

Supóngase que se tienen dos trenes de pulsos aleatorios que se desean sumar. Si se utiliza una puerta OR [14], a la salida tendremos un tren de pulsos con una probabilidad que, en general, será inferior a la suma de las probabilidades de los pulsos de entrada (figura 1.3). La razón es que, cuando se produce un solape en los trenes de pulsos de entrada, esto es, cuando ambos están simultáneamente a nivel alto, a la salida tan sólo se genera un pulso a nivel alto y no dos. Cuanto mayor sea la densidad de pulsos en las entradas de la puerta OR, mayor será la probabilidad de solape y, en consecuencia, mayor el error en la suma. Para encontrar la relación que existe entre la probabilidad

Figura 1.3: Aritmética estocástica: suma mediante puerta OR

de salida de la puerta OR en función de las probabilidades de los términos de entrada, consideremos n procesos estocásticos de Bernouilli que constituyen las n entradas de la puerta OR. Sean  $a_i$ , con i=1 ... n las probabilidades de estos n trenes de pulsos aleatorios. La probabilidad de que en un instante de

tiempo una o más de las entradas se encuentre a nivel alto es:

$$P(1 \ o \ mas \ pulsos \ ON) = \sum_{k=1}^{n} \binom{n}{k} \left(\frac{\sum_{i} a_{i}}{n}\right)^{k} \left(1 - \frac{\sum_{i} a_{i}}{n}\right)^{n-k}$$

(1.4)

donde k representa el número de entradas a nivel alto y  $(\sum_i a_i/n)$  es la probabilidad media de que cualquier entrada esté a nivel alto.

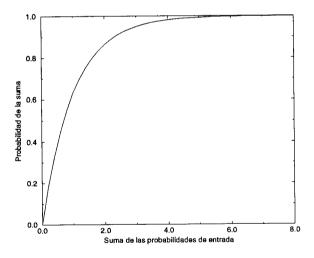

Esta ecuación no es sencilla de evaluar. Sin embargo, mediante la aproximación límite del teorema de Poisson tenemos:

$$P(1 \ o \ mas \ pulsos \ ON) = \sum_{k=1}^{\infty} \frac{e^{-\sum_{i} a_{i}} (\sum_{i} a_{i})^{k}}{k!} =$$

$$= 1 - \frac{e^{-\sum_{i} a_{i}} (\sum_{i} a_{i})^{0}}{0!} = 1 - e^{-\sum_{i} a_{i}}$$

(1.5)

La ecuación 1.5 se representa en la figura 1.4. Como puede observarse, la curva tiene la forma de la mitad superior de una función sigmoidal, por lo que esta forma de realizar la suma resulta ideal en aplicaciones relativas a redes neuronales, donde se usa la función sigmoidal como función de activación.

Figura 1.4: Saturación de la suma estocástica mediante una puerta OR

### Suma multiplexada

Una alternativa que permite evitar la saturación de la puerta OR es realizar una suma multiplexando los trenes de pulsos de entrada. En este caso la suma no satura, pero la información se reduce a la mitad. En consecuencia, el resultado será la mitad del valor de la suma. Como señal de selección del multiplexor puede utilizarse una secuencia de bits pseudoaleatoria, de

Figura 1.5: Aritmética estocástica: suma multiplexada

probabilidad 0.5, lo que reduce la correlación en el tren de pulsos aleatorios resultante [15]. En general, dados n trenes de pulsos estocásticos de entrada, la técnica de multiplexación permite obtener la n-ésima parte del valor de la suma.

#### Contadores reversibles

La suma estocástica también puede evaluarse utilizando un contador reversible [16], aunque esta técnica tiene el inconveniente de que la suma no se calcula en paralelo. Se fija un horizonte temporal durante el que se va a evaluar la influencia de cada uno de los sumandos. Secuencialmente se va teniendo en cuenta el valor de cada sumando: si el sumando es positivo, cada vez que haya un valor lógico alto, el contador se incrementa en una unidad. Si, en cambio, es negativo, el contador se decrementará en una unidad cuando exista un valor lógico alto en ese sumando. De este modo, una vez que se han tenido en cuenta a todos los sumandos en ese horizonte de tiempo, en el contador habrá un valor representativo de la suma.

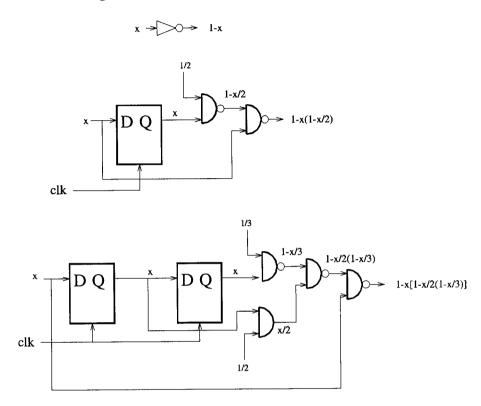

### Transformación exponencial

Dado que el producto es una operación elemental cuando se trabaja con trenes de pulsos estocásticos, resulta interesante la idea de buscar algún tipo de transformación capaz de convertir las sumas en productos [17], [18]. Esta transformación es la exponencial:

$$\prod_{i=1}^{n} e^{-x_i} = e^{\sum_{i=1}^{n} -x_i} \tag{1.6}$$

donde los términos  $x_i$  se suponen positivos. En consecuencia, si se calcula estocásticamente la función exponencial cambiándoles previamente el signo y se multiplican, a la salida tendremos un tren de pulsos representativo de la suma. Los términos positivos y negativos se calculan separadamente y después se combinan para calcular la suma total.

Esta técnica se ha aplicado con éxito en al realización física de redes neuronales artificiales con signo, donde no es necesario calcular el valor de la suma

sino tan sólo su signo. De este modo, la suma final de los términos positivos y negativos se reduce a averiguar cuál de los dos trenes de pulsos es más denso. La transformación exponencial se realiza acudiendo a diferentes aproximaciones de la función exponencial, según se incluyan más o menos términos de su desarrollo en serie (figura 1.6).

Figura 1.6: Aproximaciones de la función exponencial

# Codificación estocástica basada en la razón de pulsos a nivel alto y bajo

Una alternativa a la codificación estocástica tradicional consiste en codificar el valor de la señal, no como el número de pulsos a nivel alto en una secuencia lo suficientemente larga, sino como la razón entre los pulsos a nivel alto y los pulsos a nivel bajo en dicha secuencia [19]. En [20] se proponen diversos circuitos que realizan las operaciones aritméticas básicas, entre ellas la suma, siguiendo esta forma alternativa de interpretación de un tren de pulsos estocásticos.

La principal ventaja de esta forma de codificación reside en que es posible codificar valores analógicos en todo el rango positivo numérico, sin limitarnos únicamente al intervalo [0,1], como ocurre con la codificación tradicional. Es decir, no es necesario escalar previamente todo los valores con los que se va a trabajar, siendo posible además sumar trenes de pulsos cuyo resultado

supere la unidad. En teoría, cabría pensar en la posibilidad de realizar una suma lineal. No obstante, los circuitos propuestos en [20] no resuelven el solapamiento de los trenes de pulsos sumandos, produciéndose nuevamente las saturaciones a la salida.

### 1.4 Generación de trenes de pulsos estocásticos

Los circuitos encargados de generar los trenes de pulsos estocásticos pueden ser digitales ó analógicos.

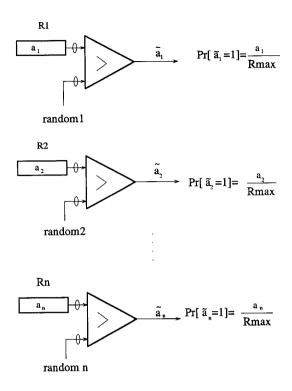

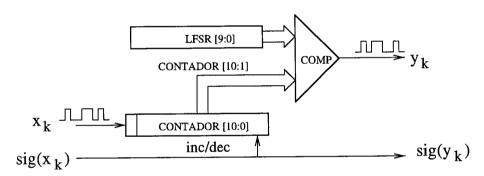

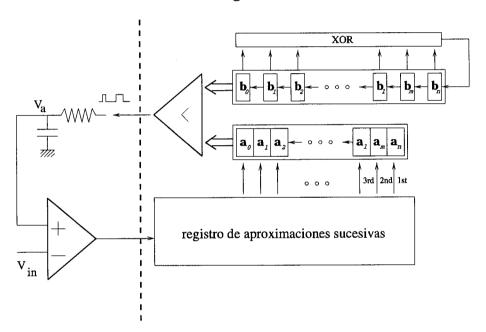

### 1.4.1 Métodos digitales de generación de trenes de pulsos estocásticos

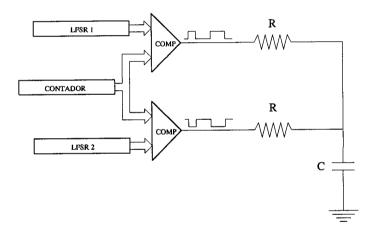

Digitalmente, la forma más simple de generar los trenes de pulsos consiste en utilizar un generador de números pseudo-aleatorios y un comparador. El número aleatorio se compara con nuestro valor codificado digitalmente. Si queda por debajo, generamos un "1" lógico a la salida del comparador. Si queda por encima, generamos un "0" lógico. Dado que la distribución de los números aleatorios es uniforme, la probabilidad de que a la salida del comparador digital haya un nivel lógico alto es proporcional al número cuya codificación por pulsos se está obteniendo. En la figura 1.7 se indica cómo se generarían los trenes de pulsos estocásticos asociado a los valores  $R_1, R_2, \ldots R_n$ . Un esquema alternativo puede encontrarse en [13].

Digitalmente tan sólo podemos generar secuencias de números pseudo - aleatorios, ya que el carácter determinista de la computación digital provoca que, antes o después, se acabe repitiendo cíclicamente la misma secuencia de números. Por pseudo-aleatorio entendemos que la secuencia de números tenga "apariencia" de aleatoriedad. La teoría estadística nos proporciona una medida cuantitativa de aleatoriedad a modo de "test", como por ejemplo, el test Chi-cuadrado, el test de frecuencia o el de correlación. No obstante, ninguno de ellos es definitivo: una secuencia que se comporte aleatoriamente respecto a los tests  $T_1, T_2, \ldots T_n$ , puede fallar con otro test  $T_{n+1}$ . En la práctica, si la secuencia pasa con éxito los test más adecuados, se considera como pseudo-aleatoria. Para una completa descripción de los tests estadísticos, [21] es un consulta obligada.

Desde el punto de vista de la computación estocástica, las propiedades más deseables que debe tener un generador de números pseudo-aleatorios son las siguientes:

Incorrelación: la secuencia de números deberá ser incorrelada. Cualquier subsecuencia de números aleatorios no deberá estar correlada con cualquier otra subsecuencia.

Figura 1.7: Generación digital de trenes de pulsos

- Longitud máxima: la longitud de la secuencia que se repite cíclicamente deberá ser la máxima posible. Si se generan números aleatorios entre 0 y N, el generador de números pseudo-aleatorios deberá recorrer todos los valores intermedios dentro del intervalo [0,N].

- Uniformidad: la secuencia de números debe encontrarse uniformemente repartida en todo el rango de posibles valores. Cualquier subsecuencia de números debe "caer" en intervalos uniformemente repartidos en todo el rango de valores.

- Eficiencia: el generador de números aleatorios debe ser eficiente en área para su implementación digital.

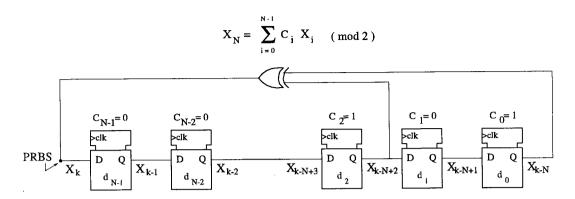

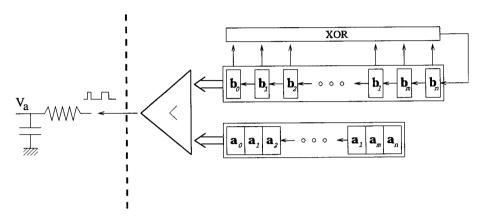

En la bibliografía pueden encontrarse multitud de generadores de números pseudo-aleatorios [22]. No obstante, el más utilizado en el procesamiento estocástico, sobre todo por motivos de eficiencia, es el registro de desplazamiento con realimentación lineal (LFSR).

Un LFSR consiste, básicamente, en un registro de desplazamiento cuyo bit más significativo se realimenta, a partir de algunos de los restantes bits, mediante puertas XOR (figura 1.8). Para un registro de n bits, realimentando de una manera adecuada y partiendo de una semilla inicial distinta de cero, el sistema recorre, sin repetición, todos los números comprendidos entre 1 y  $2^n - 1$ , repitiendo cíclicamente esa misma secuencia. Evidentemente, entre dos números consecutivos existe una cierta correlación, ya que cada número

Figura 1.8: Generador de números pseudoaleatorios

se obtiene a partir del anterior dividiendo por dos y sumando  $2^{n-1}$  si el bit más significativo recibe un "1" lógico o sumando cero si el bit más significativo recibe un "0" lógico. No obstante, a medida que tomamos dos subsecuencias más distanciadas, la correlación se va haciendo menor, de tal manera que para retrasos del orden del tamaño del LFSR, la correlación es muy pequeña. Esta característica puede aprovecharse para, a partir de un único LFSR, obtener varias subsecuencias de números aleatorios incorreladas, que puedan aprovecharse para la codificación estocástica. A partir de un bloque lógico hecho a base de puertas XOR [23], [24] se puede obtener una subsecuencia suficientemente alejada dentro del ciclo de repetición. En [25] pueden encontrarse tabulados LFSRs de tamaños hasta 45 bits. Otros estudios sobre características y propiedades de los LFSRs pueden encontrarse en [26], [27] y [28].

La utilización de un generador de números pseudo-aleatorio como el LFSR presenta el inconveniente de que la secuencia de pulsos no es claramente independiente, ya que un LFSR de n bits genera enteros entre 1 y  $2^n-1$  tales que un determinado valor aparece únicamente una vez en todo el período. En consecuencia, la distribución de trenes de pulsos estocásticos no debería ser modelada con una función de probabilidad de Bernouilli, sino como una hipergeométrica [29]. Supongamos que queremos generar un tren de pulsos estocásticos representativo del valor x=1/N, donde l es un entero entre 0 y N, y N es el período del LFSR, esto es,  $2^n-1$ . Si X es una variable aleatoria discreta que indica el número de pulsos que ocurren en una secuencia, su función de probabilidad en m ciclos de reloj vendrá dada por la ecuación (1.7).

$$P(X=k) = \frac{\binom{l}{k}\binom{N-l}{m-k}}{\binom{N}{m}}$$

(1.7)

La información del valor digital viene dada por la variable aleatoria discreta  $\hat{x} = X/m$ , que nos da el valor digital como una probabilidad entre 0 y 1. Su media y desviación típicas vienen dadas por la ecuaciones (1.8) y (1.9), respec-

tivamente.

$$E(\hat{x}) = \frac{E(X)}{n} = \frac{1}{m} \sum_{k=0} NkP(X=k) = \frac{m}{m}l/N = l/N = x$$

(1.8)

$$Var(\hat{x}) = \frac{1}{m^2} Var(X) = \frac{1}{m^2} E(X^2) - E(X)^2 = \frac{x(1-x)}{m} \frac{N-m}{N-1}$$

(1.9)

De esta expresión se extraen dos propiedades importantes cuando se trabaja con generadores como los LFSRs:

- Para valores grandes de N (LFSR de período largo), la distribución hipergeométrica se puede aproximar por una binomial

- Cuando m=N, la varianza se hace cero

Esta última conclusión es bastante importante, pues significa que, gracias precisamente al carácter pseudoaleatorio del LFSR, es posible obtener una representación del valor digital con una precisión de n bits, procesando únicamente  $2^n-1$  ciclos de reloj, en lugar de  $2^{2n-2}$ , como predice la estadística caso de usar un verdadero generador de números aleatorios.

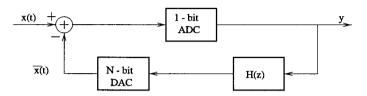

# 1.4.2 Métodos analógicos de generación de trenes de pulsos estocásticos

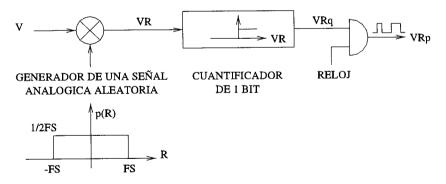

La generación de trenes de pulsos estocásticos también es posible realizarla desde una aproximación analógica. La figura 1.9 muestra el esquema básico de un convertidor analógico-estocástico [30]. La señal analógica de entrada V

Figura 1.9: Generador analógico de un tren de pulsos estocástico

es mezclada con una señal analógica aleatoria uniformemente distribuida entre +FS y -FS. La señal analógica VR a la salida se encuentra uniformemente distribuida en torno al valor V. Esta señal es cuantificada en un bit para producir un tren de pulsos aleatorios VRq, que toma el valor "1" si  $VR \geq 0$  ó "-1" si VR < 0. Finalmente, los pulsos son sincronizados con la señal de reloj del

sistema digital. La media del tren de pulsos estocástico a la salida viene dado por la ecuación (1.10).

$$E(VRp) = 1 \cdot p(VR \ge 0) + (-1) \cdot p(VR < 0) = \frac{FS + V}{2 \cdot FS} - \frac{FS - V}{2 \cdot FS} = \frac{V}{FS}$$

(1.10)

Existen distintas técnicas para generar señales analógicas aleatorias:

- Latch en estado metastable [31]. Consiste en diseñar un latch en el que la evolución a cualquiera de los dos estados sea equiprobable. El inconveniente principal son las restricciones que hay que imponer al diseño: el circuito debe ser totalmente simétrico, hay que forzar exactamente el estado metastable y las cargas a la salida deben ser idénticas.

- Corriente inversa de saturación de una unión p-n [32]. Se trata de aprovechar el ruido asociado a la corriente inversa de saturación de una unión p-n para generar secuencias de bits aleatorios. Normalmente, estas señales deben ser amplificadas y comparadas con una referencia para obtener bits aleatorios. En [33] se propone utilizar el efecto avalancha de diodos Zener como fuente de ruido. El principal inconveniente es que requiere de procesos de fabricación caros, con varias capas de dopado.

- Evolución de sistemas caóticos [34]. Son osciladores cuya fase evoluciona caóticamente. Si el sistema caótico se muestrea a intervalos de tiempo mayores que el tiempo crítico de evolución del sistema, el resultado es impredecible. En [35] se propone una técnica para generar ruido utilizando caos Hamiltoniano.

### 1.5 Aplicaciones

Históricamente, las principales aplicaciones de la computación estocástica se centran en el campo de las redes neuronales, como plataforma alternativa para llevar a cabo una realización física eficiente. El principal punto a favor de la computación estocástica estriba en su capacidad para realizar un procesamiento paralelo de la información gracias a utilizar unas unidades de procesamiento muy simples. Los primeros intentos de aplicar la codificación estocástica en el campo de las redes neuronales pueden encontrarse en [36], [37]. En estos trabajos ya se apunta la posibilidad de utilizar la codificación estocástica como una forma de representar una información analógica, pero con la ventaja de tratarse de señales puramente digitales. Desde entonces, la profusión de trabajos encaminados a llegar a realizaciones físicas de redes neuronales ha sido bastante abundante. [16] y [38] proponen arquitecturas digitales que implementan redes de Hopfield. En este caso, existe una serialización parcial, al utilizarse contadores reversibles para llevar a cabo la suma. En la bibliografía pueden encontrarse arquitecturas puramente digitales, [10], [39], [40], [29], analógicas, [37], [41] e incluso mixtas [5], [42]. Dentro de las distintas posibilidades que existen en la codificación de señales mediante trenes de pulsos [43], la única red neuronal comercial implementada es precisamente mediante trenes de pulsos estocásticos [44] (RN-200, de Ricoh).

Otras aplicaciones interesantes de la codificación estocástica se centran en la implementación física de filtros digitales. En [10] y [15] pueden encontrarse realizaciones estocásticas totalmente digitales de filtros de respuesta impulsional finita. En el primer caso se utiliza la transformación exponencial para llevar a cabo la suma, en tanto que en el segundo se utiliza la técnica de multiplexación.

El cálculo estocástico se ha utilizado también en el campo de la electrónica de potencia. Así, por ejemplo, se ha utilizado para realizar controladores clásicos de motores. En [45] se describe un controlador proporcional integral para regular la velocidad de un motor de continua. El propio tren comanda al circuito troceador, sustituyendo a una señal PWM. Cuanto mayor sea la densidad de los pulsos, mayor será la velocidad del motor. En [46] se describe un sistema de control vectorial de la velocidad de un motor de inducción, donde nuevamente se sustituye una señal PWM por un tren de pulsos, para reducir la componente de armónicos indeseables de la señal PWM.

Finalmente, otros problemas resueltos recientemente mediante lógica estocástica se refieren a temas de posicionamiento de alta precisión [47] o separación de fuentes [48].

Todas estas aplicaciones descritas tienen en común la utilización de la lógica estocástica como una herramienta de cálculo. Dados unos valores analógicos o digitales que requieren un procesamiento hardware complejo, se llega a una aproximación estocástica como técnica capaz de realizar ese procesamiento con un coste en área pequeño y una precisión razonable. No obstante, en ningún momento se aprovecha la capacidad de la lógica estocástica para representar una información analógica variable en el tiempo. Esta información puede ser procesada, mediante circuitos puramente digitales, como si de una señal analógica se tratase, con unas dinámicas que pueden ser caracterizadas como sistemas continuos en el tiempo. Así pues, la representación estocástica de la información se puede encuadrar como una técnica de procesamiento intermedia, capaz de aprovechar las ventajas tanto del procesamiento analógico como del procesamiento digital. La únicas limitaciones intrínsecas al procesamiento estocástico de la información son dos:

- 1. El procesamiento estocástico requiere unas velocidades de procesamiento mayores que las dinámicas de las señales que se desean procesar. A mayor velocidad, mayor precisión.

- 2. El procesamiento estocástico requiere un escalado completo de todo el problema a valores comprendidos entre 0 y 1.

### 1.6 Objetivos

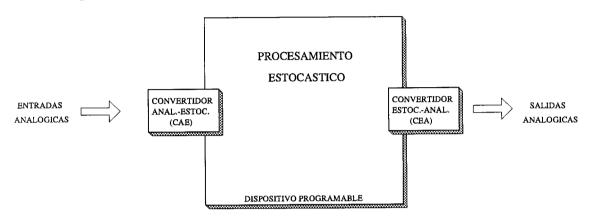

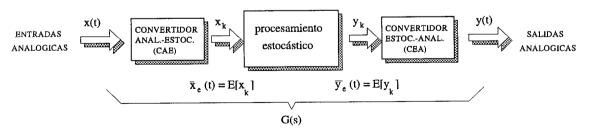

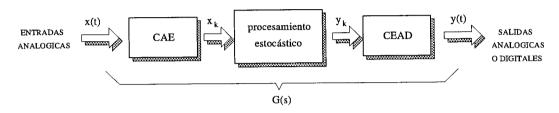

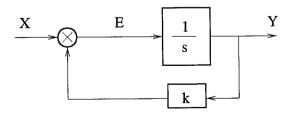

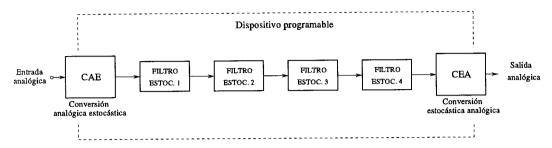

El objetivo de la tesis consiste en aportar circuitos electrónicos basados en lógica estocástica que permitan procesar la información analógica contenida en la probabilidad de tener un valor lógico alto en un tren de pulsos estocástico. Este procesamiento incluye las conversiones desde el dominio analógico al estocástico y viceversa, así como el procesamiento interno propiamente dicho, dando lugar al sistema cerrado de la figura 1.10. En el capítulo II se definen

Figura 1.10: Diagrama de bloques del procesamiento estocástico

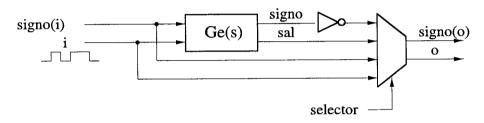

los elementos que forman parte del bloque central de la figura 1.10. Dado un tren de pulsos estocástico cuya probabilidad puede variar en el tiempo, se define un bloque constructivo básico que se caracteriza en términos de un sistema continuo, como si se trabajase en el dominio analógico. La salida de este bloque es otro tren de pulsos estocástico cuya probabilidad, variable en el tiempo, se comporta con una dinámica definida por una función de transferencia con respecto a la probabilidad del tren de entrada. La figura 1.11 ilustra esta idea. El conjunto se caracteriza con una función de transferencia en G(s), siendo el procesamiento interno totalmente estocástico. Además de este bloque se definen otras operaciones no lineales que amplían el álgebra tradicionalmente utilizada en la computación estocástica. En el capítulo III

Figura 1.11: Procesamiento estocástico con entradas y salidas analógicas

se analizan los otros dos bloques presentes en las figuras 1.10 y 1.11, es decir, los que se refieren a una conversión entre el dominio analógico y el estocástico.

Para la conversión analógica estocástica se aprovechan los esquemas de convertidores sobremuestreados puesto que, en definitiva, el cálculo estocástico se basa en trabajar con trenes de pulsos de frecuencias mucho mayores que las dinámicas de las señales a procesar. Por lo que respecta a la conversión estocástica analógica, ya tratada en trabajos previos [9], [10], se propone una mejora utilizando las posibilidades de redundancia en la información codificada en un tren de pulsos y el carácter pseudo-aleatorio de los LFSRs.

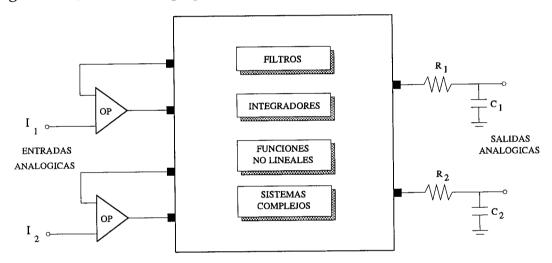

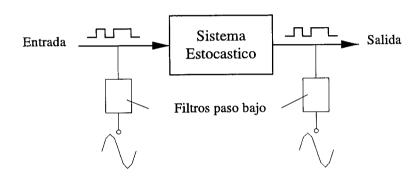

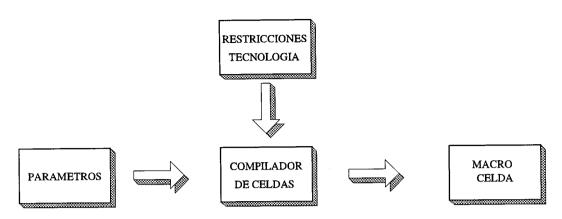

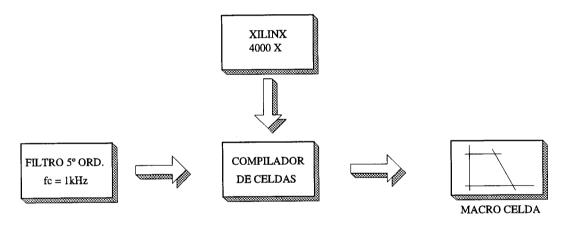

El análisis de los bloques constructivos desarrollados en los capítulos II y III se plasma en tres aplicaciones propuestas en el capítulo IV. Los distintos bloques caracterizados se sintetizan en un sistema capaz de resolver unas expresiones matemáticas dadas, como si de una realización analógica se tratase (figura 1.12). Salvo una pequeña circuitería externa necesaria para la conver-

Figura 1.12: Sistema estocástico

sión analógico estocástico y estocástico analógico, el resto del procesamiento es totalmente digital y, en consecuencia, implementable en dispositivos digitales como FPGAs o CPLDs. Existen trabajos [49], [50], [51] donde se propone una implementación analógica de los circuitos que soportan el procesamiento estocástico. Esta alternativa presenta la ventaja de no requerir una señal de reloj y de permitir utilizar verdaderos generadores de números aleatorios. Frente a estas ventajas, una implementación digital de los circuitos de procesamiento estocástico aprovecha las crecientes escalas de integración de los dispositivos digitales, completos sistemas de desarrollo, síntesis automática desde descripciones en alto nivel, portabilidad de diseños ...lo que permite orientar el procesamiento estocástico hacia aplicaciones más complejas de las que se pueden implementar desde una implementación analógica. Este es el motivo por el que se ha optado por los circuitos digitales como plataforma óptima de implementación de los circuitos propuestos en la Tesis. Las aplicaciones propuestas en el capítulo IV son la siguientes:

• Realización de filtros analógicos

En base a los circuitos descritos en el capítulo II, se propone la realización de filtros paso bajo y paso alto con un procesamiento totalmente digital.

- Control integral y por pasividad de un convertidor serie resonante Se desarrollarán circuitos estocásticos capaces de resolver un conjunto de ecuaciones diferenciales que definen el controlador.

En particular, el campo de la electrónica de potencia presenta la ventaja de no requerir de unas dinámicas excesivamente elevadas, lo que lo convierte en un terreno ideal para la codificación y posterior procesamiento estocástico. En general, cualquier proceso con unas dinámicas varios órdenes de magnitud inferior a la frecuencia de trabajo digital se puede abordar mediante un procesamiento estocástico. Como plataforma de trabajo se van a utilizar dispositivos electrónicos programables de bajo coste, en lugar de procesadores digitales genéricos, microcontroladores o circuitos integrados de aplicación específica. Finalmente, el capítulo V está dedicado a las conclusiones y futuras líneas de investigación.

# Capítulo 2

# Realizaciones estocásticas de sistemas continuos

# 2.1 Consideraciones previas

La representación de la información mediante un tren de pulsos estocástico no es solamente un método de codificación que permite un procesamiento digital de bajo coste [52], sino que esta idea puede generalizarse a la realización de sistemas continuos en el tiempo, con unas dinámicas perfectamente definidas en función de parámetros internos del circuito. El concepto fundamental es que a través de secuencias binarias estamos representando una variable aleatoria con una probabilidad que puede variar de forma continua en el tiempo. El objetivo de la tesis consiste en llegar a realizaciones que, siendo totalmente digitales, permitan realizar un procesamiento de la información como si se tratasen de sistemas analógicos. Para ello se introducirán una serie de bloques constructivos básicos que amplían la aritmética tradicional empleada en el cálculo estocástico. Al tratarse de un procesamiento totalmente digital, se aprovechan todas las ventajas del mismo: inmunidad al ruido, programabilidad, entornos de desarrollo fáciles de usar, tiempos de diseño menores, etc.

La aproximación estocástica puede encuadrase como una vía intermedia entre el procesamiento digital y el analógico. Frente al analógico presenta la ventaja de que la información se representa como un tren de pulsos estocásticos que es, en definitiva, una secuencia binaria. Frente al procesamiento digital presenta la ventaja de permitir trabajar con bloques constructivos definidos por una función de transferencia.

Circuitos de medida y control que trabajan con señales continuas en el tiempo tienen en el procesamiento estocástico una plataforma de implementación hardware óptima.

A continuación definiremos el bloque básico, que no es más que la realización digital de un sistema continuo de primer orden. Una vez caracterizado, realizaremos su extensión a sistemas de orden n, acabando el capítulo con circuitos

electrónicos de aplicación, como filtros y otros circuitos de cálculo.

# 2.2 Realización digital de un sistema de primer orden

### 2.2.1 Descripción del bloque básico

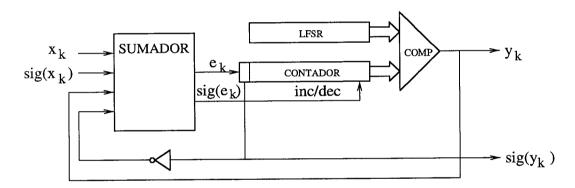

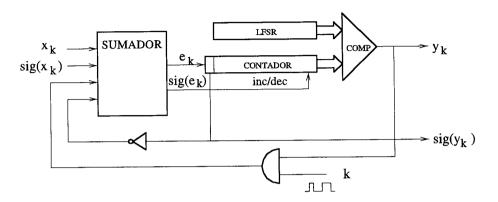

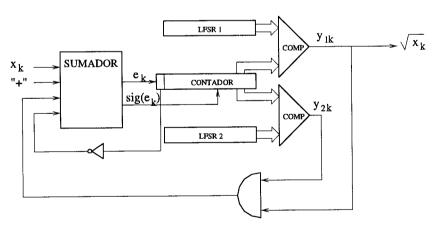

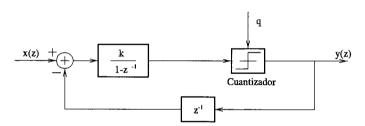

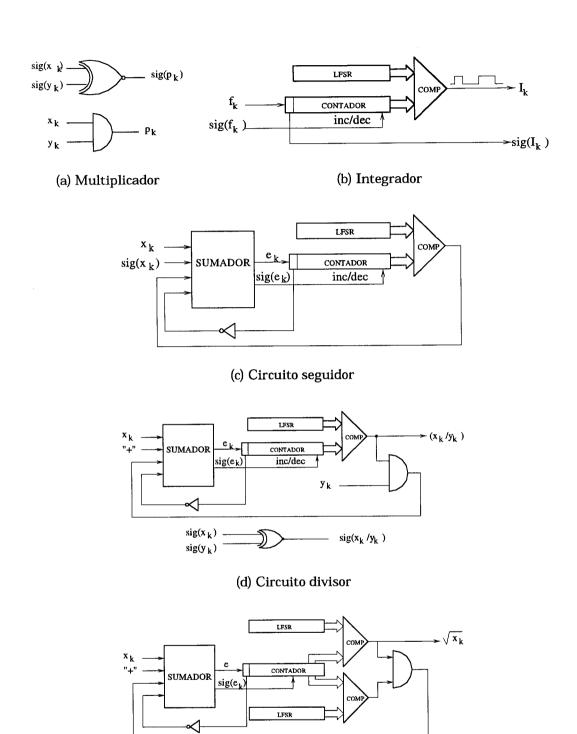

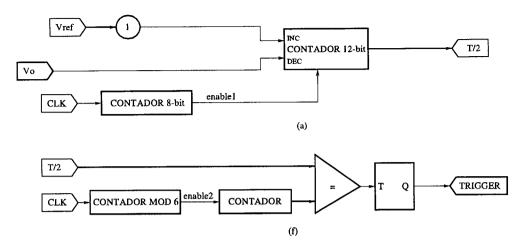

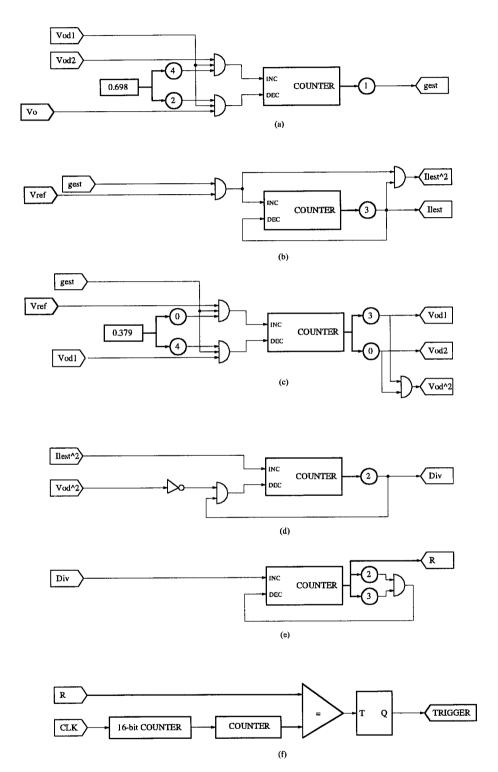

La figura 2.1 muestra el esquema de un sistema de primer orden. El tren de pulsos  $x_k$  a la entrada es la representación estocástica de una señal analógica cualquiera. La entrada se compara con la salida  $y_k$  mediante un bloque sumador con signo (bloque SUMADOR), generando un error  $e_k$  que se integra mediante un contador. El valor digital del contador se convierte a un tren estocástico mediante un LFSR, que nos proporciona la salida  $y_k$  del bloque. Al tratarse de una estructura realimentada, la salida tiende a parecerse a la entrada buscando un error nulo. En un instante de tiempo k, el valor alma-

Figura 2.1: Sistema de primer orden

cenado en el contador dependerá de su valor anterior y del resultado de la diferencia entre el tren de pulsos de entrada y el tren de pulsos generado a partir del valor del propio contador

$$y_k = y_{k-1} + \frac{1}{2^n}(x_k - y_{k-1}) = y_{k-1} + (1 - \alpha)(x_k - y_{k-1})$$

(2.1)

donde  $x_k$  e  $y_k$  son las probabilidades de los trenes de pulsos en el instante k, n es el número de bits del contador y  $\alpha=1-1/2^n$ . Esta es la ecuación característica de un promediado exponencial [53]. En efecto, la ecuación (2.1) puede reescribirse como:

$$y_k = (1 - \alpha)x_k + \alpha y_{k-1} = (1 - \alpha)x_k + \alpha \{(1 - \alpha)x_{k-1} + \alpha(1 - \alpha)x_{k-2} + \ldots\} = \sum_{i=0}^k a_i x_{k-i}$$

(2.2)

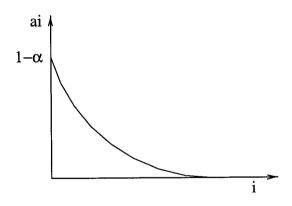

donde

$$a_{0} = 1 - \alpha$$

$$a_{1} = \alpha(1 - \alpha)$$

$$a_{2} = \alpha^{2}(1 - \alpha)$$

$$\vdots$$

$$a_{k} = \alpha^{k}(1 - \alpha)$$

(2.3)

La entrada se promedia con unos coeficientes  $a_i$ , i=1...k que siguen una progresión geométrica, y que dependen del valor del contador a través de la constante  $\alpha$ . Para tener un promediado de la señal de entrada es necesario que la suma de los coeficientes de la función de peso sea la unidad. La suma de una progresión geométrica resulta:

$$\sum_{i=0}^{k} a_i = (1 - \alpha) \frac{1 - \alpha^k}{1 - \alpha} = 1 - \alpha^k$$

(2.4)

Tomando límite para  $k \to \infty$

$$\lim_{k \to \infty} \left( \sum_{i=0}^{k} a_i \right) = 1 \tag{2.5}$$

En consecuencia, nuestro esquema de primer orden realiza un promediado exponencial de la señal de entrada, con un "factor de olvido  $\alpha$ ", que depende de la dimensión del contador, y por medio del cual seguimos a la entrada. En definitiva, introducimos una dinámica en la señal de salida con respecto a la entrada, dinámica que depende de dos parámetros:

Figura 2.2: Coeficientes de la función de peso

- La frecuencia de reloj con que trabaja nuestro sistema digital, que es la velocidad de procesamiento estocástico.

- La dimensión del contador donde se efectúa la integral.

Ajustando la relación entre estos dos parámetros, tendremos una constante de tiempo característica del sistema, que define el comportamiento dinámico del mismo. Gráficamente, la función de peso en un promediado exponencial es de la forma indicada por la figura 2.2.

Otras funciones de promediado pueden encontrarse en [54] y [55]. No obstante, la exponencial es la más fácilmente implementable desde un punto de vista electrónico.

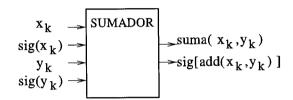

### 2.2.2 Suma con signo

El bloque SUMADOR de la figura 2.3 se encarga de calcular el error entre la referencia y la salida.

Figura 2.3: Bloque sumador con signo

| bloque $SUMADOR$ |    |   |    |     |      |  |  |  |  |  |

|------------------|----|---|----|-----|------|--|--|--|--|--|

| X                | SX | у | sy | xmy | sxmy |  |  |  |  |  |

| 0                | 0  | 0 | 0  | 0   | -    |  |  |  |  |  |

| 0                | 0  | 0 | 1  | 0   | -    |  |  |  |  |  |

| 0                | 0  | 1 | 0  | 1   | 0    |  |  |  |  |  |

| 0                | 0  | 1 | 1  | 1   | 1    |  |  |  |  |  |

| 0                | 1  | 0 | 0  | 0   | -    |  |  |  |  |  |

| 0                | 1  | 0 | 1  | 0   | -    |  |  |  |  |  |

| 0                | 1  | 1 | 0  | 1   | 0    |  |  |  |  |  |

| 0                | 1  | 1 | 1  | 1   | 1    |  |  |  |  |  |

| 1                | 0  | 0 | 0  | 1   | 0    |  |  |  |  |  |

| 1                | 0  | 0 | 1  | 1   | 0    |  |  |  |  |  |

| 1                | 0  | 1 | 0  | 1   | 0    |  |  |  |  |  |

| 1                | 0  | 1 | 1  | 0   | -    |  |  |  |  |  |

| 1                | 1  | 0 | 0  | 1   | 1    |  |  |  |  |  |

| 1                | 1  | 0 | 1  | 1   | 1    |  |  |  |  |  |

| 1                | 1  | 1 | 0  | 0   | -    |  |  |  |  |  |

| 1                | 1  | 1 | 1  | 1   | 1    |  |  |  |  |  |

Tabla 2.1: Tabla de verdad del bloque sumador con signo

Se trata de un sumador con signo. Dado que la salida de este bloque es una señal de error, la densidad del tren de pulsos a la salida será baja, y por tanto,

la técnica de la suma mediante una puerta OR se encuentra totalmente justificada. Básicamente, el bloque SUMADOR implementa una suma mediante una puerta OR, pero teniendo en cuenta los signos de los trenes estocásticos de entrada. Es un bloque totalmente combinacional, que implementa las siguientes ecuaciones lógicas (2.6).

$$add(x_k, y_k) = x_k \oplus y_k + x_k \overline{(sig(x_k) \oplus sig(y_k))}$$

$$sig[add(x_k, y_k)] = x_k sig(x_k) + y_k sig(y_k)$$

(2.6)

La salida puede ser un "1" ó un "0" lógico con signo positivo o negativo. La codificación del signo es la siguiente: un signo cero es positivo y un signo a uno es negativo. La suma se realiza de una manera totalmente simétrica, tal y como se observa en la tabla de verdad (2.1).

El solape de la información se producirá únicamente en dos casos: al sumar dos "1" positivos o al restar dos "1" negativos. Como las señales de entrada son próximas y de signo opuesto, la probabilidad de que se produzca ese solape es pequeña y, en consecuencia, la suma se realiza con suficiente exactitud.

### 2.2.3 Caracterización

La constante de tiempo del sistema viene fijada por el contador, en función de su tamaño y de la frecuencia a la que trabaje. Si T es el período de la señal de reloj y n el número de bits del contador, de la ecuación (2.1) se tiene que la constante de tiempo del circuito de la figura 2.1 es [56]:

$$\tau = 2^n T = \frac{2^n}{F_{clk}} \tag{2.7}$$

siendo  $F_{clk}$  la frecuencia de la señal de reloj. Este resultado también puede obtenerse utilizando la aproximación de Euler. La probabilidad del tren de pulsos estocástico de salida en el instante k es igual a:

$$y_k = \frac{c_k}{2^n} \tag{2.8}$$

donde  $c_k$  es el valor del contador en el instante k. Por su parte, el contador integra el tren de pulsos estocástico resultado de restarle la salida a la entrada:

$$c_k = \sum_{j=1}^k (x_j - y_{j-1}) \tag{2.9}$$

De las ecuaciones (2.8) y (2.9) se tiene que:

$$2^{n}y_{k} = \sum_{j=1}^{k} (x_{j} - y_{j-1})$$

(2.10)

Multiplicando y dividiendo por el período de reloj T:

$$y_k = \frac{F_{clk}}{2^n} \sum_{j=1}^k (x_j - y_{j-1})T$$

(2.11)

que es la integral por Euler de la diferencia de la entrada y la salida con una constante de tiempo de  $2^n/F_{clk}$ .

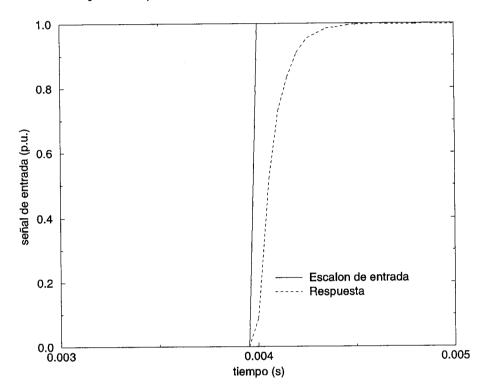

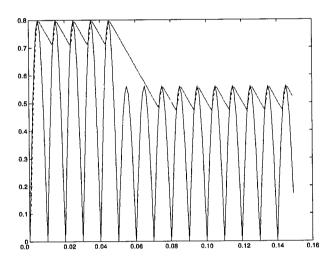

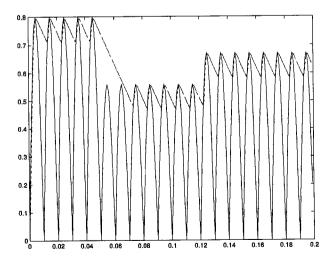

Figura 2.4: Respuesta a un escalón. n=10,  $F_{clk}$ =12 MHz

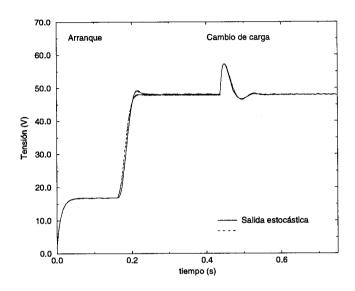

La figura 2.4 muestra la respuesta a un escalón de un sistema estocástico de primer orden, para una frecuencia de reloj de 12 MHz y un contador de 10 bits. Gráficamente, el valor de la constante de tiempo puede calcularse como el tiempo en que la respuesta del sistema tarda en alcanzar 0.632 veces la referencia. Se obtiene un valor de  $8.5 \cdot 10^{-5}$  s, que coincide con el valor teórico dado por la ecuación 2.12

$$\tau_{10bits,12MHz} = \frac{2^{10}}{12 \cdot 10^6} = 8.53 \cdot 10^{-5} \tag{2.12}$$

Como la frecuencia e trabajo de la lógica estocástica es varios órdenes de magnitud la frecuencia de las señales variables en el tiempo que estamos procesando, se puede modelar el sistema estocástico de primer orden por una función de transferencia continua de la forma de la ecuación (2.13).

$$G_e(s) = \frac{1}{1 + \tau s} \tag{2.13}$$

En consecuencia, dado un tren de pulsos de entrada de probabilidad  $x_k$  variable en el tiempo, el sistema de primer orden definido suministra a la salida un tren de pulsos  $y_k$ , también variable en el tiempo, cuya dinámica viene modelada por la función de transferencia  $G_e(s)$ . Si codificamos la señal analógica de entrada como una probabilidad en una secuencia binaria y extraemos la probabilidad de la secuencia binaria de salida a partir de la frecuencia relativa, dispondremos de un sistema completo de procesamiento estocástico, implementable digitalmente, y con el que podemos realizar una función analógica como la indicada por la función de transferencia  $G_e$ . La figura 2.5 ilustra es-

Figura 2.5: Sistema de procesamiento estocástico

ta idea. Las referencias CAE y CEAD son los bloques de conversión entre el dominio analógico y estocástico y el estocástico con el analógico/digital, respectivamente, que serán detallados en el capítulo siguiente.

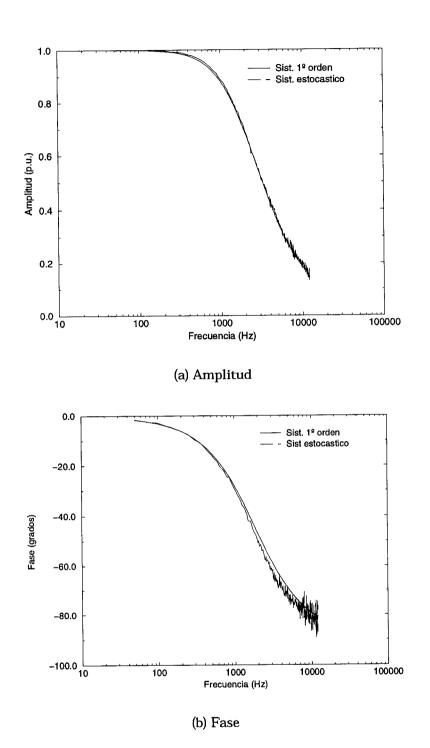

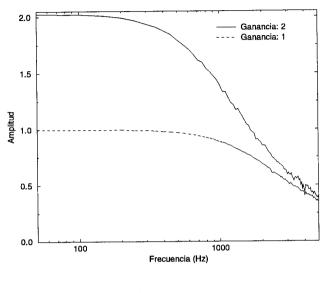

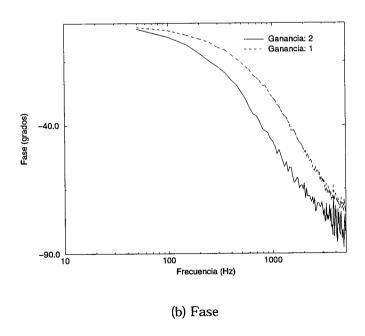

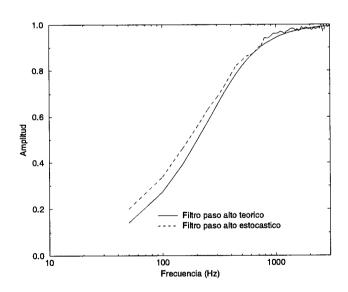

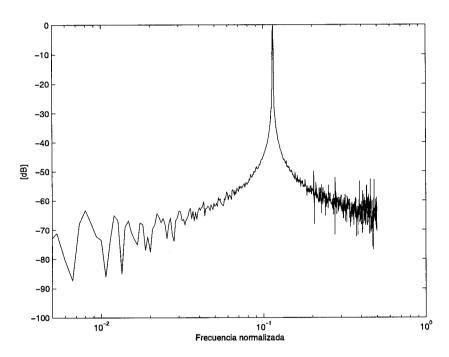

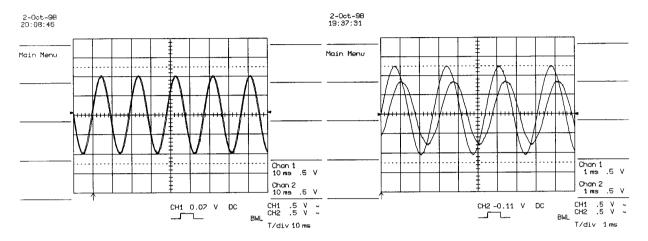

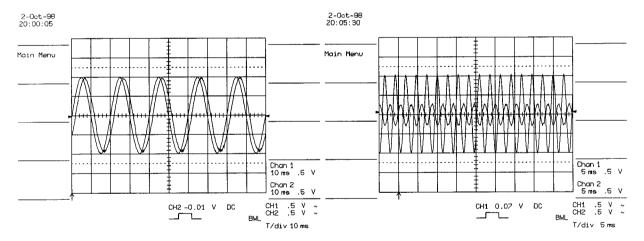

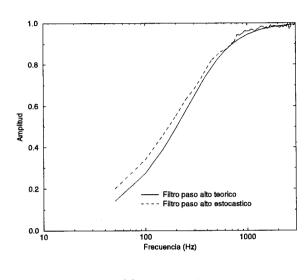

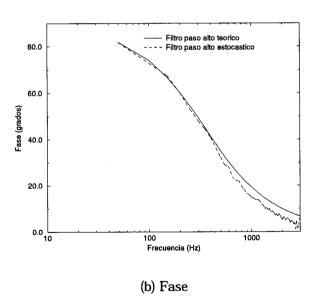

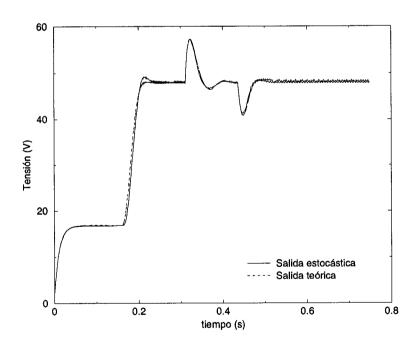

### 2.2.4 Respuesta en frecuencia

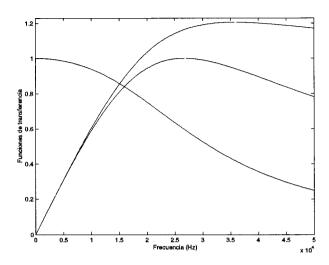

Siguiendo la idea de la figura 2.5 podemos comparar la aproximación estocástica con un sistema analógico utilizando el diagrama de BODE. En general, un sistema de primer orden se caracteriza dinámicamente en función de la atenuación y el desfase que produce sobre una señal senoidal de entrada, al variar la frecuencia. Utilizando los bloques de conversión de la figura 2.5, se ha obtenido el diagrama de BODE de la figura 2.6 para la amplitud y la fase. Este diagrama ha sido obtenido para una frecuencia de trabajo de 12 MHz, con un contador de 10 bits, lo que supone una frecuencia de corte de aproximadamente, 1865 Hz. Para esta frecuencia se puede observar que se tiene una ganancia de, aproximadamente, 0.707 y un desfase de unos  $45^{\circ}$ .

En general, para frecuencias por debajo de la frecuencia de corte, el comportamiento se aproxima bastante al sistema teórico. Para frecuencias mayores, aparecen unas oscilaciones fundamentalmente en la fase. Estas oscilaciones se deben a que estas frecuencias son del orden de las frecuencias de repetición de los generadores de números aleatorios utilizados. Los períodos de las senoides de entrada se reducen tanto que sólo damos muy pocas vueltas al LFSR.

Figura 2.6: Diagrama de Bode de un sistema de primer orden,  $F_{clk}$ =12 MHz, 10 bits.

En consecuencia, el valor obtenido para la fase se vuelve dependiente de la semilla inicial. En cualquier caso, ese ruido es filtrado al recuperar el valor analógico o digital del tren de pulsos de salida. Variando el número de bits del contador y la frecuencia de trabajo, podemos obtener la frecuencia de corte en el rango deseado.

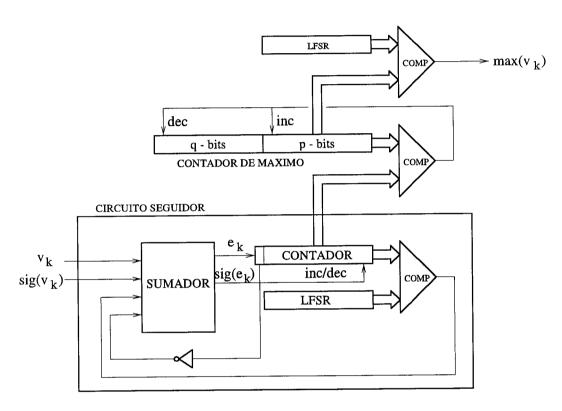

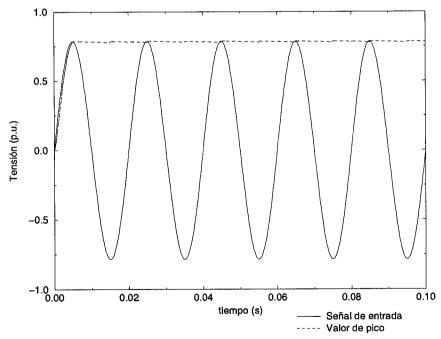

### 2.2.5 Aplicación: circuito estocástico detector de pico

Figura 2.7: Circuito detector de pico

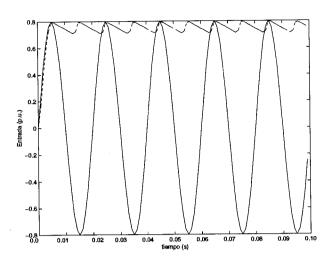

En la figura 2.7 se detalla el circuito detector de pico. Se basa en un circuito seguidor (recuadrado en la figura) más un contador de p+q bits. Este contador incrementa la palabra constituida por los p bits más significativos siempre que su valor se encuentre por debajo del circuito seguidor y decrementa la palabra constituida por los q bits menos significativos cuando su valor esté por debajo del contador del circuito seguidor. Dicho de otra forma, cuando la señal de entrada se incrementa, el contador de máximo sigue a la señal de entrada, pero cuando ésta decrece, el contador de máximo se decrementa con un factor de  $2^{-q}$ . El comportamiento es similar al de un detector de envolvente analógico, donde la constante de tiempo de carga es mucho mayor que la de descarga del condensador.

(a) Señal de entrada de amplitud constante

(b) Señal de entrada de amplitud variable

(c) Señal de entrada de amplitud constante

Figura 2.8: Resultado de la detección del valor máximo

El circuito seguidor debe ser diseñado para ser capaz de seguir la dinámica de la señal de entrada. La figura 2.8(a) es la respuesta del circuito detector ante una entrada senoidal, con unos valores de 12 y 8 para p y q, respectivamente. El circuito seguidor tiene una frecuencia de corte de 466 Hz. La figuras 2.8(b) y 2.8(c) constituyen el resultado obtenido para una señal de entrada variable en amplitud.

## 2.3 Introducción de un factor de ganancia

Una de las restricciones básicas del cálculo estocástico estriba en que el rango de trabajo se encuentra entre 0 y 1. Esto significa que cualquier problema a resolver debe ser escalado en este rango de actuación. No obstante, en muchas aplicaciones puede resultar interesante (y, a veces, indispensable) disponer de una manera de introducir un factor de ganancia mayor que la unidad. Como ya hemos visto, un factor de ganancia menor que uno se obtiene fácilmente sin más que multiplicar con una puerta AND por un tren estocástico que represente el factor de atenuación. Sin embargo, multiplicar por una cantidad mayor que uno no es trivial. Una primera aproximación al problema podría

Figura 2.9: Introducción de un factor de ganancia doble

ser integrar mediante un contador y efectuar una multiplicación digital para, posteriormente, convertir de nuevo ese contador en un tren estocástico. En el caso más simple de multiplicar por dos, bastaría con desplazar el contador hacia la izquierda (figura 2.9).

Figura 2.10: Sistema de primer orden con factor de ganancia

(a) Sistema de primer orden con ganancia 1/k

(b) Respuesta de un sistema de primer orden con ganancia 2.  $F_{clk}$ =12 MHz, 10 bits

Figura 2.11: Introducción de un factor de ganancia en un sistema de primer orden

Como se puede ver para este caso tan simple, la introducción del factor de ganancia se realiza de una forma bastante ineficiente, pues obliga a utilizar de nuevo el conjunto "contador - LFSR - comparador".

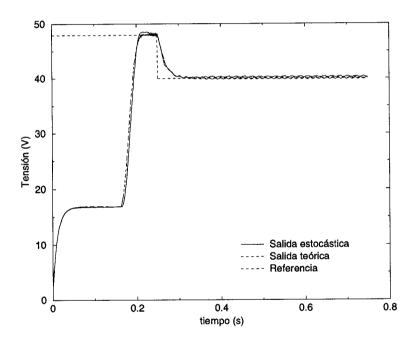

Una alternativa mucho más eficiente consiste en introducir un factor de ganancia en el bucle de realimentación, tal y como se indica en el diagrama de bloques de la figura 2.10. k sería una constante menor que la unidad, que, por tanto, es muy sencilla de implementar estocásticamente. Para un sistema continuo, la introducción de un factor k en el bucle de realimentación supondría modificar, no sólo la ganancia, sino también la constante de tiempo. La nueva función de transferencia para el sistema de la figura 2.11(a) viene dada por la ecuación 2.14.

$\frac{Y}{X} = \frac{1/k}{1 + \frac{1}{k}s} \tag{2.14}$

El efecto es similar en nuestro sistema estocástico de primer orden: obtenemos ganancia a costa de hacer más lento el comportamiento dinámico. Evidentemente, y dado que funcionamos con valores entre cero y uno, el valor amplificado no puede superar la unidad. En cualquier caso, no se trata de una limitación muy grande, ya que se evita realizando un escalado adecuado al problema en cuestión. El esquema detallado de un sistema estocástico de primer orden con ganancia 1/k se muestra en la figura 2.11. Se trata de un sistema esencialmente igual que el de la figura 2.1 salvo en el factor k que se introduce mediante una puerta AND en el bucle de realimentación. Buscamos a la salida una señal estocástica tal que, atenuada por un factor k, se aproxime a la entrada. Los cálculos son, por tanto, muy similares a los realizados en las ecuaciones de (2.8) a (2.11). El contador realiza la integral del error que hay de la referencia a la señal atenuada.

$$c_k = \sum_{j=1}^k (x_j - k \cdot y_{j-1})$$

(2.15)

El valor que se obtiene a la salida es entonces el tren de pulsos estocásticos amplificado según el factor 1/k.

$$y_k = \frac{c_k}{2^n} = \frac{1}{2^n} \sum_{j=1}^k (x_j - k \cdot y_{j-1})$$

(2.16)

Multiplicando y dividiendo por  $kF_{clk}$ :

$$y_k = \frac{F_{clk}}{(1/k)2^n} \sum_{j=1}^k (\frac{x_j}{k} - y_{j-1}) \frac{1}{F_{clk}}$$

(2.17)

(a) Amplitud

Figura 2.12: Diagrama de Bode de un sistema de primer orden de ganancia doble.  $F_{clk}$ =12 MHz, 10 bits.

Comparando las ecuaciones (2.11) y (2.17) se concluye que, si bien conseguimos una amplificación, ésta se realiza a costa de ralentizar el comportamiento, de forma similar a lo que ocurría en un sistema continuo. La constante de tiempo del sistema estocástico de primer orden con factor de ganancia resulta ser:

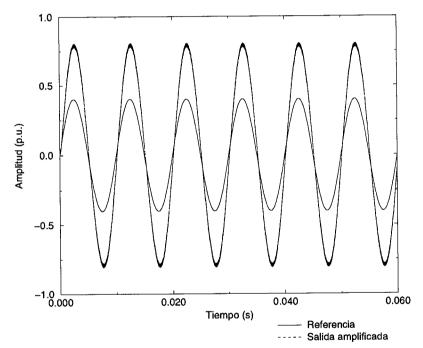

$\tau_e = \frac{\frac{1}{k}2^n}{F_{clk}} \tag{2.18}$

La figura 2.11(b) muestra la respuesta de un sistema estocástico con un factor de ganancia. Dicho resultado ha sido obtenido a partir de un sistema de primer orden estocástico definido por un contador de 10 bits y una frecuencia de trabajo de 12 MHz. La señal de entrada es de 100 Hz, con un valor de 0.4 por unidad, y el factor de ganancia es de 2. Como puede observarse, la salida amplificada se va al doble del valor de la referencia, esto es, amplitud máxima de 0.8 por unidad.

Como ya se ha señalado, la introducción de un factor de ganancia limita el comportamiento dinámico. La constante de tiempo y, por tanto, la frecuencia de corte, disminuye proporcionalmente al valor de la ganancia. La figura 2.12 compara los diagramas de BODE de un mismo sistema para diferentes ganancias. Al aumentar la ganancia, el sistema se vuelve más lento.

No obstante, hay que señalar que siempre es posible aumentar la frecuencia de reloj para mejorar el rango dinámico del sistema. Actualmente es posible encontrar dispositivos programables con tecnologías por debajo de las  $0.23\mu m$  que admiten frecuencias de trabajo que legan a superar los  $100~\mathrm{MHz}$ . Además, la tendencia de los próximos años es ir mejorando estas prestaciones.

### 2.4 Extensión a sistemas de orden n

El sistema de primer orden estocástico caracterizado en el apartado anterior presenta una particularidad especialmente interesante para llegar a realizaciones más complejas. Esta particularidad consiste en que se pueden serializar varios bloques semejantes, sin perder la ganancia con la que se esté trabajando. Haciendo un símil analógico, sería como si se tuviese una impedancia de entrada infinita y una impedancia de salida cero.

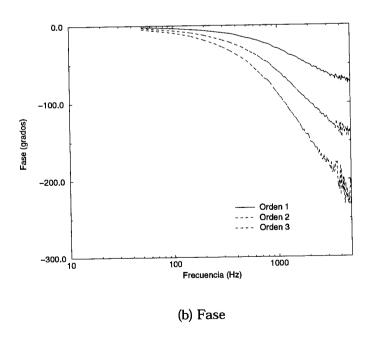

El esquema analógico equivalente a la serialización de dos bloques de primer orden se ilustra en la figura 2.14.

Poniendo en cascada varios bloques de primer orden obtenemos sistemas de orden superior. El resultado es análogo al que se obtiene del circuito de la figura 2.14, incluyendo el desacoplo de impedancias.

Figura 2.13: Diagramas de Bode de sistemas de primer, segundo y tercer orden.  $F_{clk}$ =12 MHz, 10 bits.

Figura 2.14: Sistema analógico equivalente con aislamiento de impedancias

A medida que serializamos bloques de primer orden, la respuesta se vuelve más lenta, pues cada uno de los bloques va modificando la dinámica de la señal que ve a su entrada.

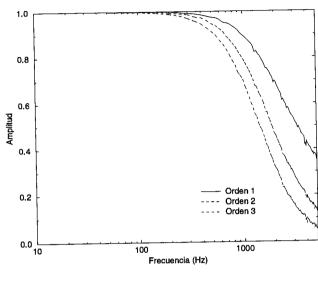

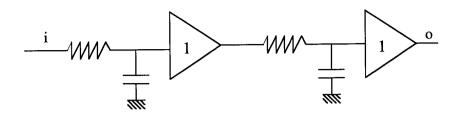

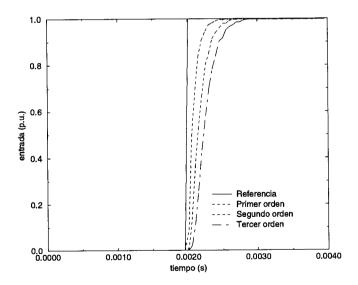

Sin embargo, la ganancia final se mantiene y es independiente del número de bloques que coloquemos en cascada. La figura 2.13 muestra el diagrama de BODE para un sistema de primer, segundo y tercer orden, formados a partir de un bloque integrador caracterizado por un contador de tamaño 10 y una frecuencia de reloj de 12 MHz. La pendiente de caída es más pronunciada al ir incrementando el orden, como corresponde a un sistema de orden n formado por n bloques de primer orden en cascada, y la fase tiende a 90º, 180º y 360º respectivamente para frecuencias muy superiores a la de corte. La figura 2.15 muestra la respuesta de los tres sistemas ante un escalón de entrada.

Figura 2.15: Respuesta a un escalón de sistemas de orden 1, 2 y 3

### 2.5 Introducción de ceros

Hasta el momento se ha caracterizado un bloque básico consistente en un circuito estocástico con un comportamiento modelado por la función de transferencia:

$G_e(s) = \frac{1}{1 + \tau s} {(2.19)}$

Sobre este esquema se ha introducido la posibilidad de añadir un factor de ganancia o de agrupar varios de estos bloques en cascada. En todos ellos únicamente se contemplan polos del sistema. También es posible introducir ceros de una manera simple, a partir de un circuito de resta por multiplexación (figura 2.16).

Figura 2.16: Introducción de ceros

Figura 2.17: Diagrama de BODE del sistema de la ecuación 2.20

La función de transferencia que implementa la figura 2.16 es:

$$G_{e2}(s) = 1 - G_e(s) = \frac{\tau s}{1 + \tau s}$$

(2.20)

con lo que conseguimos introducir un cero en el origen. La figura 2.17 es la respuesta de este circuito en frecuencia.

## 2.6 Circuitos de cálculo de funciones no lineales

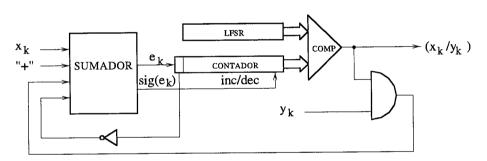

#### 2.6.1 Circuito de cálculo de divisiones

Como aplicación del esquema con un factor de ganancia se puede obtener de forma inmediata un circuito de cálculo de divisiones. En efecto, y refiriéndonos a la figura 2.18, mediante la realimentación negativa se genera una señal de error de la forma:

$$e_k = x_k - (x_k/y_k) \cdot y_k \tag{2.21}$$

Figura 2.18: Circuito estocástico de cálculo de divisiones

Figura 2.19: Ejemplo de cálculo de una división

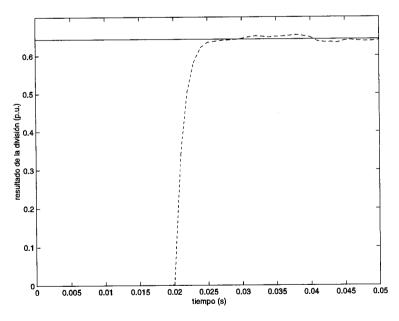

Se puede demostrar que este error tiende a cero. Consideremos el término  $e_k^2$  que es siempre positivo. Su derivada viene dada por:

$$\frac{d}{dt}e_k^2 = 2e_k y_k \frac{d}{dt}(x_k/y_k) < 0 \tag{2.22}$$

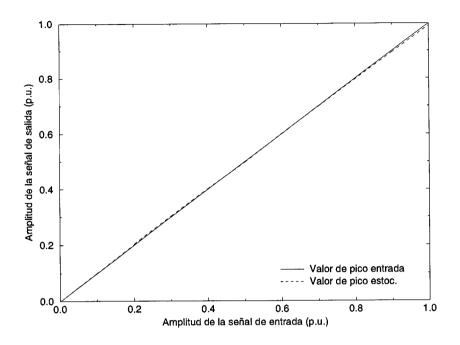

la expresión de la ecuación (2.22) es negativa puesto que un error positivo supone una disminución en  $y_k$  y viceversa. En consecuencia el error tiende a cero y, de (2.21), el tren de pulsos de salida es igual al cociente de  $x_k$  e  $y_k$ . La figura 2.19 es un eemplo de cálculo de una división, utilizando los valores 0.177 y 0.275 como dividendo y divisor, respectivamente. El resultado tiende al valor teórico de 0.645.

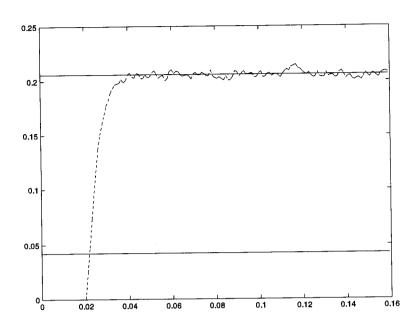

#### 2.6.2 Circuito de cálculo de raíces cuadradas

Con la misma idea anterior, también es posible obtener un circuito de cálculo de raíces cuadradas. Pero a diferencia de antes, ahora tenemos que multiplicar en la realimentación el tren de pulsos de salida por sí mismo. Para que el producto se realice correctamente, es necesario que ambas secuencias representativas del mismo valor sean incorreladas. Una posibilidad consistiría en introducir un retraso el tren de pulsos antes de multiplicarlo por sí mismo. El principal inconveniente estriba en que este retraso debe ser lo suficientemente largo como para que las dos secuencias decaladas sean incorreladas. La otra solución consiste en utilizar un segundo generador de números aleatorios para obtener la segunda secuencia, incorrelada con la primera; por ejemplo, mediante el bloques a base de puertas XOR descrito en [23] y [24].

Figura 2.20: Circuito de cálculo de raíces cuadradas

Las dos salidas  $y_{1k}$  e  $y_{2k}$  son dos secuencias incorreladas que representan el mismo valor, que es precisamente la raíz cuadrada del valor representado por el tren de entrada  $x_k$ . En este caso, el error es igual a:

$$e_k = x_k - y_k \cdot y_k \tag{2.23}$$

Figura 2.21: Ejemplo de cálculo de una raíz cuadrada

Igual que antes, comprobamos que la derivada del error al cuadrado es negativa, lo que significa que el error tiende a cero.

$$\frac{d}{dt}e_k^2 = 4e_k y_k \frac{d}{dt} y_k < 0 (2.24)$$

De la ecuación (2.24) se deduce que la cualquiera de los trenes de salida  $y \downarrow_k$  o  $y \downarrow_k$  es igual a la raíz cuadrada del tren de pulsos de entrada. La figura 2.21 es un ejemplo de cálculo de la raíz cuadrada del valor 0.041, cuyo valor teórico es 0.2158.

Dado que tanto el circuito de cálculo de divisiones como el de raíces cuadradas se han obtenido a partir del esquema de la figura 2.11, la dinámica de ambos viene descrita por la dinámica de un sistema de primer orden con ganancia.

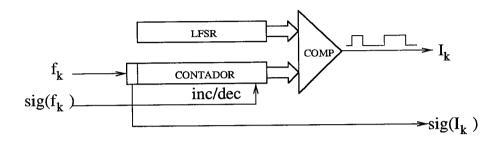

## 2.7 Circuito integrador

La integral de un tren de pulsos estocásticos  $[f_k, sig(f_k)]$  se obtiene digitalmente utilizando un contador (Fig. 2.22). Utilizando una aproximación por Euler, la integral del valor analógico definido por la probabilidad del tren de pulsos estocástico se relaciona con el valor del contador que efectúa la integral según la ecuación (2.25).

$$I(t_o) = \int_0^{t_o} f(t)dt = \sum_{k=0}^n f\left(\frac{k}{F_{clk}}\right) \left(\frac{1}{F_{clk}}\right) = \frac{f_{esc}}{F_{clk}} \sum_{k=0}^n \frac{f\left(\frac{k}{F_{clk}}\right)}{f_{esc}} = \frac{f_{esc}}{F_{clk}} \sum_{k=0}^n p_k = \frac{f_{esc}}{F_{clk}} \cdot C, \qquad t_0 = \frac{n}{F_{clk}}$$

$$(2.25)$$

donde  $p_k$  es la probabilidad de tener un nivel lógico alto en el tren de pulsos estocástico de entrada,  $F_{clk}$  es la frecuencia de reloj, n es el número de integraciones estocásticas efectuadas en el tiempo  $t_0$  y C es el valor digital del contador de la figura 2.22, que incrementa o decrementa su valor en función de la señal  $sig(f_k)$ . El parámetro  $f_{esc}$  es un factor de escala igual al valor máximo de f, que nos permite acotar los valores de la función en el intervalo [0,1] y hablar en términos de probabilidades. Siguiendo con la figura 2.22, el va-

Figura 2.22: Circuito integrador

lor digital del contador se convierte a un nuevo tren de pulsos estocástico por comparación con un LFSR. El tren de pulsos  $I_k$  a la salida, representativo de la integral, se relaciona con el valor digital del contador por la ecuación (2.26).

$$\frac{I(t_o)}{2^{N_b}} = \frac{f_{esc}}{F_{clk}} \cdot \frac{C}{2^{N_b}} = \frac{f_{esc}}{F_{clk}} \cdot I_k \tag{2.26}$$

donde  $N_b$  es el tamaño del contador y  $\mathcal{I}_k$  es la probabilidad de tener un nivel alto a la salida.

Así pues, el tren de pulsos estocástico de salida nos integra la señal de entrada con una constante de  $2^{Nb}/F_{clk}$ , según se indica en la ecuación 2.27.

$$I_{k} = \frac{1}{\frac{2^{Nb}}{F_{clk}}} \int_{0}^{t_{0}} \frac{f}{f_{esc}} dt$$

(2.27)

Si la señal de entrada es senoidal  $f(t) = A \cdot sen(\omega t)$ , entonces el valor máximo de la integral es  $2A/\omega$ . El valor máximo debe corresponder a una probabilidad unidad a la salida del integrador. Sustituyendo en la ecuación (2.26), se obtiene como condición para evitar la saturación:

$$\frac{2A/\omega}{2^{N_b}} = \frac{f_{esc}}{F_{clk}} \tag{2.28}$$

Dado que  $f_{esc}=A$ , obtenemos a la salida del circuito integrador  $I_k=\omega I(t)/2$ , cuyo valor máximo es una probabilidad unidad. El signo de salida viene dado por el signo del contador.

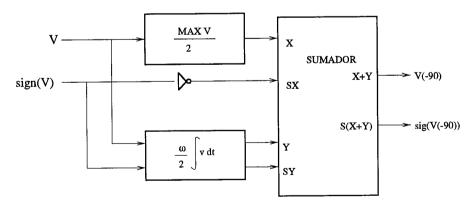

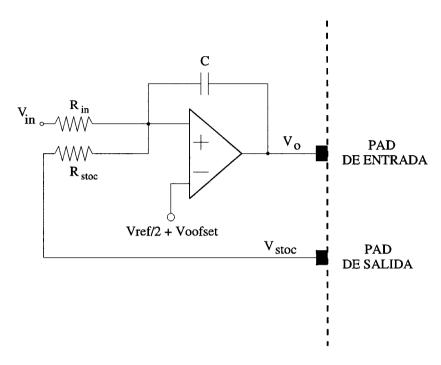

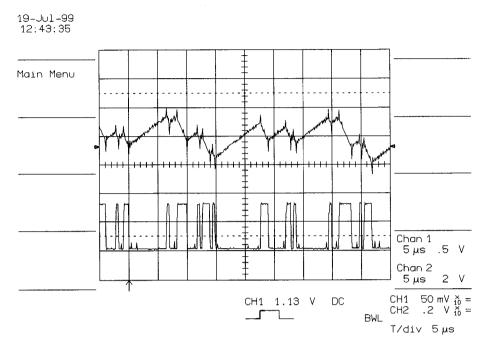

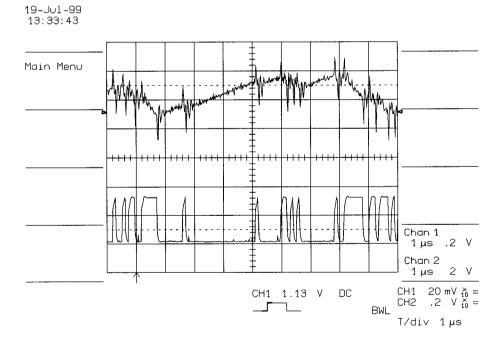

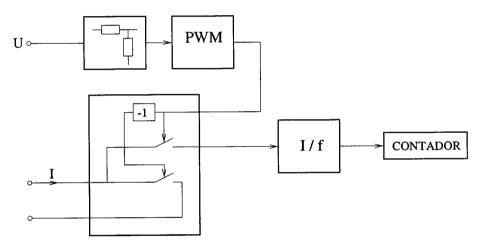

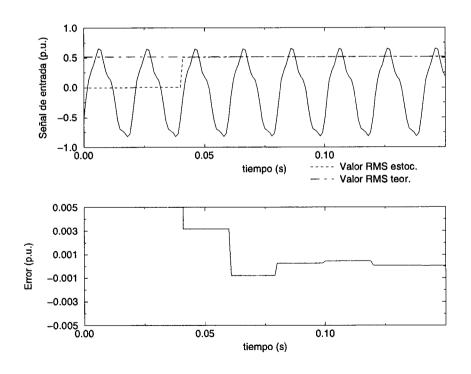

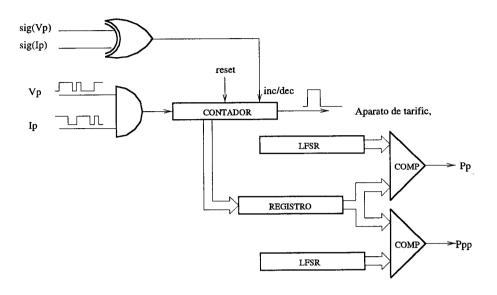

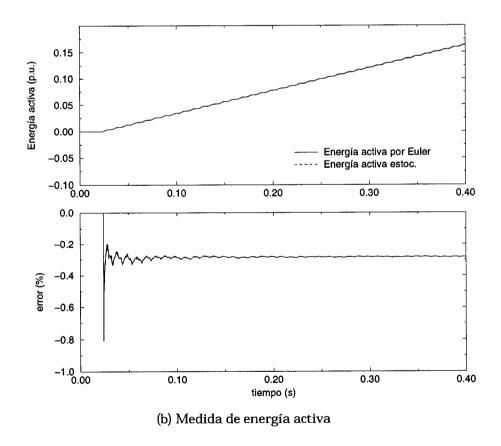

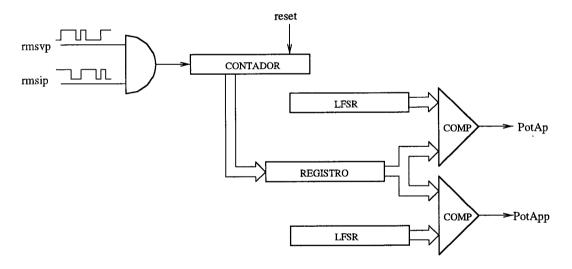

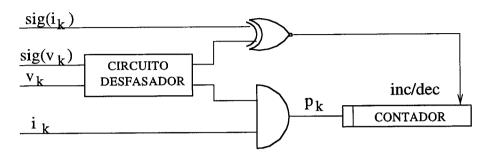

## 2.7.1 Aplicación: circuito desfasador