# An Amplified Offset Compensation Scheme and its Application in a Track and Hold Circuit

Shirin Pourashraf, *Member*, *IEEE*, Jaime Ramirez-Angulo, *Fellow*, *IEEE*, Alfonso R. Cabrera-Galicia, *Member*, *IEEE*, Antonio J. Lopez-Martin, and Ramon González-Carvajal, *Senior Member*, *IEEE*

Abstract - This paper proposes a fully differential track and hold circuit using a new DC offset compensation scheme. It stores an amplified version of the offset during the hold phase, which is used in attenuated fashion during the track phase to compensate offset. This scheme is less sensitive to charge injection and other errors than conventional offset compensation schemes. Experimental results of a test chip in 0.18  $\mu m$  CMOS technology verify the proposed scheme.

Index Terms -Sample and hold (S/H), Differential difference amplifier (DDA), Mixed-signal circuits, Offset compensation.

## I. INTRODUCTION

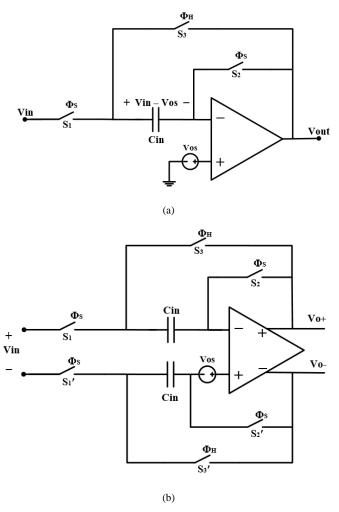

C offsets drastically limit the performance and accuracy of analog and mixed-signal blocks, such as sample-and-hold (S/H) circuits. A common S/H circuit that cancels the input offset voltage of the op-amp [1] is shown in Fig. 1a and it operates as follows: 1) During the sample phase  $\Phi_S$ ,  $S_1$  and  $S_2$ are closed and S<sub>3</sub> is open, so, the op-amp is connected with unity gain feedback and the capacitor stores the value  $V_{Cin}=V_{in}-V_{os}$ . 2) During the hold phase  $\Phi_H$ ,  $S_1$  and  $S_2$  are open and  $S_3$  is closed, so,  $C_{in}$  is connected to the output of the op-amp and the output voltage takes a value  $V_{Cin}+V_{os}=V_{in}$ . An advantage of this scheme is that the inputs of the op-amp always remain at a constant voltage (close to mid supply) and do not change with the applied input signal. Disadvantages of this scheme are that the accuracy of offset compensation is affected by charge injection  $Q_{inj}$  from  $S_2$  when it opens. This introduces and error  $\Delta V_o = Q_{inj}/C_{in}$  in the voltage  $V_{Cin}$  that leads to a modified value  $V_{Cin}$ '= $V_{Cin}+\Delta V_o=V_{in}-V_{os}+\Delta V_o$ . Given that the offset voltage is very small, the charge injection error  $\Delta V_o$  can be comparable to  $V_{os}$  unless large capacitors  $C_{in}$  are used. Increasing  $C_{in}$  (which is in the signal path) is detrimental to speed because it adds non-dominant poles. Also, the output resets to zero during the sample phase and this imposes a speed limitation. The fully differential (FD) configuration of the circuit shown in Fig. 1b alleviates the charge injection problem, however, the mismatch of charge injection of S2 and S2' and of the input capacitors still limits the accuracy in the offset cancellation. This scheme is representative of most offset cancellations schemes that store the relatively small value  $V_{os}$  at **face value** during one phase and compensates it during a second phase [2]-[4].

S. Pourashraf and J. Ramirez-Angulo are with the VLSI Laboratory, Klipsch School of Electrical and Computer Engineering, New Mexico State University, Las Cruces, NM, 88003, USA (e-mail: shirin\_p@nmsu.edu; jairamir@nmsu.edu).

A. R. Cabrera-Galicia is with the Electronics Department, National Institute for Astrophysics, Optics, and Electronics, Puebla 72840, Mexico (e-mail: alfonso\_cabrera@outlook.com).

Fig. 1. Simple switched- capacitor sample and hold. (a): Single ended. (b): Fully differential

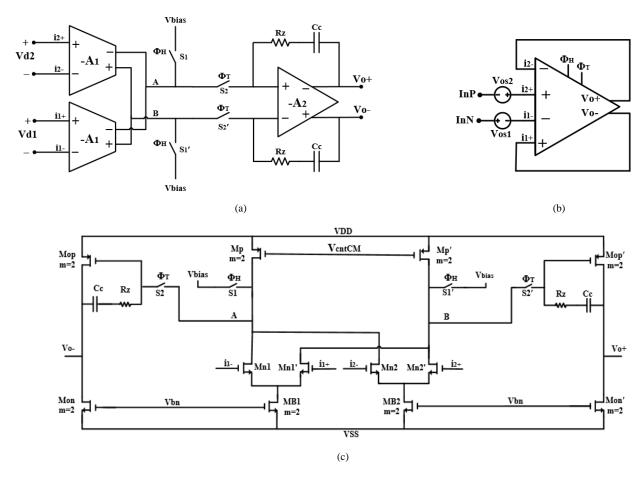

A simple, non-offset compensated fully differential track and hold (T/H) circuit [1], [5] that does not reset the output of the op-amp to zero is shown in Fig. 2a. It is based on a two-stage Miller op-amp with two differential input stages (differential difference amplifier) [6]-[7] whose outputs are connected in parallel at nodes A and B to common active loads. The transistor level implementation of Fig. 2a is shown in Fig. 2c. Nodes A and B drive a FD output stage.

- A. J. Lopez-Martin is with Department of Electrical and Electronic Engineering, Public University of Navarra, 31006 Pamplona, Spain (e-mail: antonio.lopez@unavarra.es).

- R. Carvajal is with the Departamento de Ingeniería Electrónica, Escuela Superior de Ingenieros, Universidad de Sevilla, E-41092, Spain (e-mail: carvajal@gte.esi.us.es).

Fig. 2. Clocked fully differential conventional T/H. (a): Internal structure. (b): Voltage follower configuration. (c): Transistor level schematic.

It operates as follows: During the track phase, switch  $S_2$ ,  $S_2$ ' are closed and  $S_1$ ,  $S_1$ ' are open. This connects the op-amp as a FD voltage follower (Fig. 2b), and the output voltage follows the input voltage including the offset error  $V_o = V_{in} + V_{os1} + V_{os2}$ . At the end of the track cycle, when  $S_2$ ,  $S_2$ ' opens, the output voltage is held during the hold phase in the compensation capacitors  $C_c$  and the outputs of the first stage ( $A_1$ ) are connected to DC voltages  $V_{bias}$  in order to prevent their saturation. A sample and hold can be implemented by cascading two track and hold circuits with complementary control phases. This scheme allows higher operating speed since the output of the op-amp does not go to zero during the track phase  $\Phi_T$ . An additional advantage is that no capacitors are inserted in series with the signal path.

In section II of this paper we present a modified offset compensated version of this circuit. It includes additional auxiliary circuitry that stores an amplified version of the total offset. This makes the scheme less sensitive to charge injection, and to other errors. Simulation and experimental results are discussed in section III. Summary and conclusions are given in section IV.

# II. PROPOSED OFFSET COMPENSATED MILLER T/H

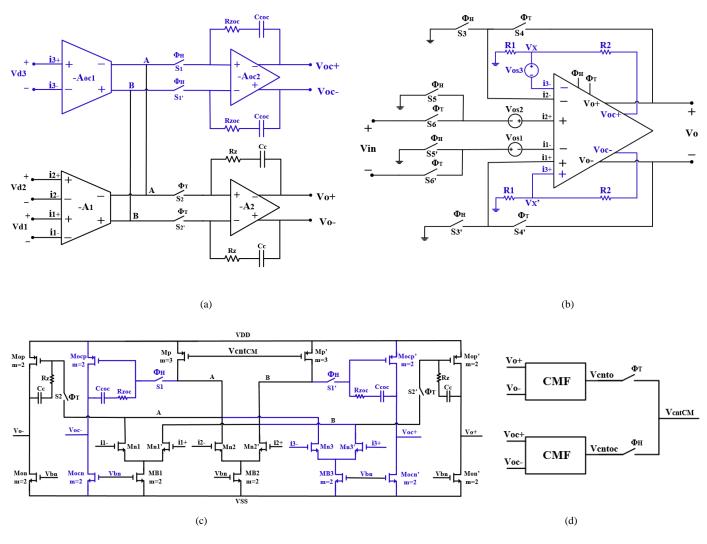

The track and hold (T/H) circuit of Fig. 3 is a modified version of the circuit of Fig. 2 that is able to compensate offset

by storing its amplified version. This is done in order to make offset compensation less sensitive to charge injection and to other errors. A differential input stage  $(A_{ocl})$  and an auxiliary differential output stage  $(A_{oc2})$  have been added in order to store an amplified version of the total offset voltage. The outputs of three input stages (terminals A and B) are connected in parallel. Fig. 3c shows the transistor level schematic of the proposed T/H. The auxiliary input stage  $(A_{ocl})$  is formed by transistors  $M_{n3}$ , and  $M_{n3}$  while the auxiliary output stage  $(A_{oc2})$  is formed by  $M_{ocp}$ ,  $M_{ocn}$ ,  $M_{ocp}$ , and  $M_{ocn}$ . The proposed circuit works as follows:

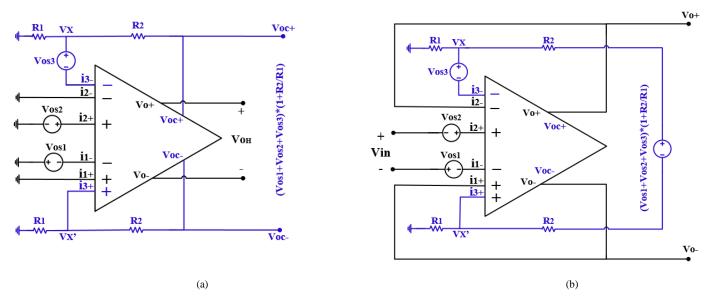

- 1) During the hold phase  $\Phi_H$ , switches S<sub>3</sub>, S<sub>3</sub>', S<sub>5</sub>, and S<sub>5</sub>', are closed (Fig. 4a). This connects the inputs of the main amplifier to ground while the auxiliary amplifier implements an amplifier with gain  $G_{oc}=1+R_2/R_1$ . Its output voltage is given by  $V_{oc}=(1+R_2/R_1)(V_{os1}+V_{os2}+V_{os3})$ .

- 2) During the track phase the main amplifier is connected as a FD buffer and the amplified offset V<sub>oc</sub> is held by the compensation capacitors C<sub>coc</sub> (Fig. 3b). In this case V<sub>oc</sub> performs as a DC voltage source that generates a voltage V<sub>X</sub>-V<sub>X</sub>'=V<sub>os1</sub>+V<sub>os2</sub>+V<sub>os3</sub> at the input of the auxiliary amplifier. This compensates the offset of all input stages and leads to an offset free main amplifier output V<sub>o</sub>=V<sub>in</sub>.

Fig. 3. Clocked fully differential offset compensation T/H. (a): Internal structure. (b): Voltage follower configuration. (c): Transistor level schematic. (d): Implementation of CMF in FD T/H.

Fig. 4. Proposed T/H circuit including offset voltages. (a): During hold phase  $\Phi_H$ . (b): During track phase  $\Phi_T$ .

## Remarks:

- a) The proposed scheme is less sensitive to charge injection errors than conventional schemes since it stores an amplified version of the total offset  $V_{oc}$  in  $C_c$ . In practice,  $G_{oc}$  is subject to gain errors due to the finite gain of the DC loop and to resistive loading. Given that the offset compensation voltage  $V_X$ - $V_X$ '= $V_{oc}$ / $G_{oc}$  is an attenuated version of  $V_{oc}$  the gain errors are cancelled out and do not affect the accuracy of the proposed scheme.

- b) Output offset compensation schemes in multistage comparators also store an amplified version of the input offset in capacitors in the signal path [8]. However, they are feedforward structures that have no global feedback.

- Conventional auto zero techniques also use an auxiliary amplifier to store an offset compensation  $V_{oscomp}$  in a capacitor given  $V_{oscomp} = (A_m/A_a)V_{osm} + V_{osa}$  where  $A_m$  and  $A_a$  are the gains of the main and auxiliary amplifiers respectively and  $V_{osm}$  and  $V_{osa}$  are their associated offsets [8]. It can be seen that  $V_{osm}$  is amplified by a factor  $A_m/A_a$  (typically about 10) while  $V_{osa}$  is not amplified. Due to this, the cancellation of  $V_{osa}$  remains sensitive to charge injection errors. Also, in auto-zeroing techniques the switches connected to the offset storage capacitors have a charge injection error that depends on the stored amplified offset voltage ( $V_{oscomp}$ ). The switches do not have the same charge injection since their gate-source voltages are not equal. This is due to the fact that the switches transfer complementary voltages  $(V_{oscomp}/2, -V_{oscomp}/2)$  to the offset storage capacitors. This also makes conventional auto-zero techniques sensitive to charge injection even without mismatch in the switches. The approach proposed here is less sensitive to charge injection because all switches driving  $C_{coc}$ , and  $C_c$  (S<sub>1</sub>, S<sub>1</sub>', S<sub>2</sub>, and S<sub>2</sub>') have equal and constant gate-source voltages that do not depend on the amplified offset voltage  $V_{oc}$  stored in the Miller capacitor  $C_{oc}$ .

- d) Note that the proposed scheme, as opposed to a ping-pong architecture, i.e. [9], stores an amplified version of the total offset during one phase. Ping-pong architectures use two independent auto zeroing stages operating with alternative phases.

- e) The DC offset compensation loop (auxiliary stage) in the proposed scheme increases power consumption and area. Since the output of the auxiliary stage is not connected to a capacitive load, the compensation capacitor  $C_{coc}$  can be small. (Fig. 3c) and  $A_{oc2}$  can operate with low quiescent current and down scaled transistor sizes i.e. by a factor of 5 but at the same time with the same bandwidth as the main feedback loop. This allows to decrease the power and area requirements of the DC offset compensation circuitry and the quiescent power dissipation by %20.

- f) In order to improve the accuracy of the offset compensation without the risk of saturating the output of the auxiliary amplifier, a moderate gain  $G_{oc}$ =20 was selected. In this case, with typical offsets  $V_{os}\sim 5-10$ mV the output  $V_{oc}$  still represents an essentially amplified version of the total offset  $V_{os}=V_{os1}+V_{os2}+V_{os3}$ .

- g) The proposed circuit uses two common mode feedback networks (CMF). Their common mode control voltages  $V_{cnto}$  and  $V_{cntoc}$  are connected alternatively to  $V_{cntCM}$  as shown in Fig. 3.

- h) Resistors  $R_1$ , and  $R_2$  in Fig. 3 contribute to input noise. In order to reduce this contribution, a capacitor (in parallel with  $R_2$ ) can be used to limit the resistor's noise bandwidth.

## III. SIMULATION AND EXPERIMENTAL RESULTS

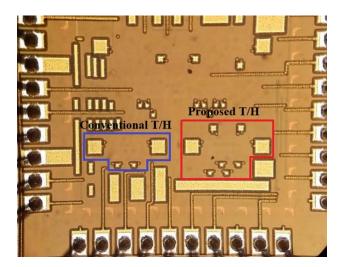

A test chip prototype including a non-overlapping clock generator, and both the conventional and offset compensated Miller T/H circuits of Figs. 3 and 4 respectively were fabricated in 0.18  $\mu$ m CMOS technology with NMOS and PMOS threshold voltages of approximately 0.45 V.

Fig.5. Photograph of test chip including offset compensator and conventional T/H designs.

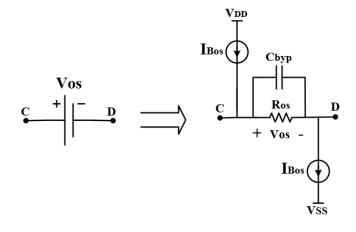

Fig. 6. Floating battery acting like an externally controllable DC offset source for test purposes.

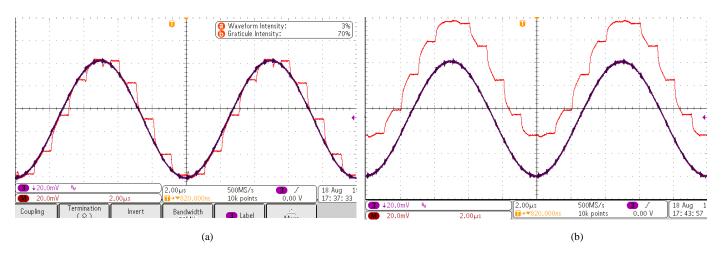

Fig. 7. Experimental Input and output differential waveforms of fabricated circuit (100 mVpp at 100 kHz input signal, 1 MHz input clock, and 40 mV total offset). Horizontal scale 2 µs/div., vertical scale 20 mV/div. (a) Proposed T/H. (b) Conventional T/H.

The unit transistor dimensions in micrometer are (W/L)p=(100/0.7) and (W/L)n=(20/0.7). Sizes of PMOS and NMOS transistors of NAND and Inverter gates used in digital non-overlapping clock generator are respectively  $(W/L)p_{(NAND,INV)}=(0.88/0.22)$ , and  $(W/L)n_{(NAND,INV)}=(0.44/0.22)$ . PMOS and NMOS transistors in the complementary switches (W/L)psw=(W/L)nsw=(0.22/0.22).had dimensions Capacitances and resistors have values  $C_c=10$  pF,  $C_{coc}=2$  pF,  $R_z$ =3 k $\Omega$ ,  $R_{zoc}$ =1 k $\Omega$ ,  $R_I$ =8 k $\Omega$ ,  $R_2$ =150 k $\Omega$ . Fig. 5 shows the micrograph of the fabricated chip. The dimensions of the conventional and offset compensated circuits  $372~\mu m \times 190~\mu m \ (0.07~mm^2)$  and  $400~\mu m \times 270~\mu m$ (0.11 mm<sup>2</sup>) respectively. Three independently controllable floating batteries generating offsets  $V_{os1}$ ,  $V_{os2}$  and  $V_{os3}$  were included in the circuit for testing purposes. They were implemented as shown in Fig. 6 using two matched DC current sources  $I_{Bos}$  and a resistor  $R_{os}$ =5 k $\Omega$  in parallel with a small bypass capacitor  $C_{byp}=1$  pF. The circuit was simulated and tested with dual supplies  $\pm 0.9 \text{ V}$ ; a bias current  $I_{bias}=200 \mu\text{A}$  and load capacitance  $C_L$ =23 pF. Simulations of the circuit of Fig. 3 (with  $\Phi_H$  set to  $V_{SS}$  and  $\Phi_T$  to  $V_{DD}$ ) led to a DC open loop gain  $A_{ol}$ =53 dB and gain-bandwidth GB=40 MHz. The circuit was able to remove accurately large offsets even when the peak-peak input signal was as small as 50 mV and the total offset around 40 mV ( $V_{os2}=V_{os3}=V_{os3}=13.5$  mV). Figs. 7a and 7b show the experimental input and output waveforms of the proposed offset compensated and conventional T/H. The circuits were tested with 100 mVpp 100 kHz input signal with a 1 MHz clock and a load capacitance  $C_L$ =23 pF. The total applied offset (controlled externally) was approximately 40 mV. Harmonic distortion measurements with the presence of total applied offset Vos=40 mV shows that SFDR is 7 dB higher in the proposed scheme (68 dB) than in the scheme without offset compensation (61 dB).

## IV. CONCLUSION

A method for offset compensation in Miller (Integrating) sample and holds was presented. It stores an amplified version

of the total offset in Miller capacitors and this amplification reduces its sensitivity to charge injection. Experimental results of a test chip in 0.18  $\mu m$  CMOS technology validated experimentally that the circuit can compensate large DC offset voltages.

## REFERENCES

- T. C. Carusone, D. A. Johns, and K. Martin, "Analog integrated circuit design." 2<sup>nd</sup> ed, NY, USA: Wiley, 2012.

- [2] C. Sawigun, and W. A. Serdijn, "Analysis and Design of a Low-Voltage, Low-Power, High-Precision, Class-AB Current-Mode Subthreshold CMOS Sample and Hold Circuit." *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 58, no. 7, pp. 1615 – 1626, July, 2011.

- [3] H. G. Wei, U. F. Chio, Y. Zhu, S. W. Sin, U. Seng-Pang, and R. P. Martins, "A Rapid Power-Switchable Track-and-Hold Amplifier in 90-nm CMOS." *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 57, no. 1, pp. 16-20, Jan, 2010.

- [4] F. Centurelli, P. Monsurro, S. Pennisi, G. Scotti, and A. Trifiletti, "Design solutions for sample-and-hold circuits in CMOS nanometer technologies." *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 56, no. 6, pp. 459-463, June, 2009.

- [5] J. Ramirez-Angulo, C. I. Lujan-Martinez, C. Rubia-Marcos, R. G. Carvajal, and A. Lopez-Martin, "Rail-to-rail fully differential sample and hold based on differential difference amplifier." *Electronics Letters*, vol. 44, no. 11, May, 2008.

- [6] E. Sackinger, and W. Guggenbuhl, "A versatile building block: the CMOS differential difference amplifier." *IEEE J. Solid-State Circuits-SC*, vol. 22, no. 2, pp. 287-294, April, 1987.

- [7] J. Ramirez-Angulo, and F. Ledesma. "The universal opamp and applications in continuous-time resistorless and capacitorless linear weighted voltage addition." *IEEE Transactions on Circuits and Systems* II: Express Briefs, vol. 53, no. 5, pp. 404-408, May, 2006.

- [8] B. Razavi, Principles of Data Conversion System Design. New York: IEEE Press, 1995.

- [9] M.A. Pertijs, and W.J. Kindt, "A 140 dB-CMRR current-feedback instrumentation amplifier employing ping-pong auto-zeroing and chopping." *IEEE Journal of Solid-State Circuits*, vol. 45, no. 10, pp. 2044-2056, Oct, 2010.