# Tesis Doctoral/Doctoral Thesis Doctorado en Ciencias y Tecnologías Físicas

# Study of variability phenomena on CMOS technologies for its mitigation and exploitation

A PhD Dissertation by Pablo Sarazá Canflanca

Advisors: **Francisco V. Fernández Fernández Rafael Castro López** Date:

September 10, 2021

## Acknowledgements Agradecimientos

Son muchas las personas que me han ayudado durante los últimos cuatro años a desarrollar el trabajo que ha desembocado en la escritura de esta tesis. Me gustaría empezar agradeciendo su ayuda a mis directores, Paco y Rafa, y a Eli, que ha sido también mi directora en todo menos en el nombre. Estoy seguro de que sin su ayuda, su paciencia, su generosidad hacia mí, nuestras innumerables discusiones y sus incontables revisiones de mi trabajo esta tesis no existiría. Creo haber aprendido mucho de ellos, y espero que en el futuro nuestros caminos sigan entrelazados.

Quisiera agradecer también su apoyo a todas las personas que me han acompañado durante estos años en el IMSE. Nunca me ha faltado una ayuda desinteresada cuando la he necesitado, y puedo decir que he recibido mucho más de lo que he dado. Espero poder equilibrar la balanza en el futuro, aunque no será fácil. Quisiera agradecer su ayuda a las Unidades Técnicas, en especial a Joaquín y Antonio Ragel, a la Unidad de Administración, a Juanma y Juan por su ayuda en el laboratorio, a Piedad por su ayuda en un campo que era nuevo para todos nosotros, y a los jóvenes veteranos Luis Camuñas y Juan Núñez por su ayuda y amistad. Aunque es imposible nombrar a todo el mundo, gracias también al resto de personas que me han acompañado y ayudado durante estos años, ya sea durante nuestras comidas en cafetería, en los pasillos del IMSE, o por las tardes, cuando el IMSE se vaciaba (gracias, María José, por tu compañía).

Como no, quisiera agradecer también el apoyo técnico continuo y, sobre todo, el cariño personal, de todos mis compeñaros de grupo y de despacho, en especial de Antonio Toro, Fabio, Dani, Héctor, José Fernando, Macarena y, más recientemente, Andrés y Eros. En este grupo incluyo también a Manu, que no ha sido compañero de despacho pero sí vecino, y a Diego, compañero de tantos desayunos. Todos ellos han hecho del IMSE un segundo hogar para mí, y lamento que la situación del último año y medio no nos haya permitido vernos tanto como hubiéramos deseado.

Aunque he realizado mi trabajo en el IMSE, gran parte del mismo se ha desarrollado en colaboración con la UAB. En este sentido, quisiera agradecer su ayuda a Montse, Javi Martín y Rosana. He disfrutado (y creo que aprendido) mucho de nuestras discusiones, y espero que volvamos a colaborar en el futuro.

Proveniente también de la UAB, quisiera hacer una mención especial a Javi Díaz. Primero por toda su ayuda en el laboratorio y por videollamada cuando trabajaba todavía en la UAB. Después, por ayudarme a realizar una estancia de tres meses en IMEC durante mi doctorado, y, finalmente, por ser en gran parte responsable de mi próxima etapa vital. Quisiera dar las gracias también al resto de personas con las que trabajé en IMEC por su ayuda, y en especial a Erik Bury.

Finalmente, quisiera agradecer a mi familia todo lo que ha hecho por mí para que yo haya podido llegar hasta aquí. No sólo, ni especialmente, durante estos últimos cuatro años, sino durante toda mi vida. Gracias a mi madre, a mi padre, a mi hermano Juan y a mi hermana Amaia.

A mi aituna y mi amona, y a mis abuelos.

## Publications and awards related to this Thesis

#### International journal papers as first author:

- P. Saraza-Canflanca, J. Martin-Martinez, R. Castro-Lopez, E. Roca, R. Rodriguez, M. Nafria and F.V. Fernandez, "A detailed study of the gate/drain voltage dependence of RTN in bulk pMOS transistors", Microelectronic Engineering, vol. 215, 111004, 2019.

- P. Saraza-Canflanca, J. Diaz-Fortuny, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria and F.V. Fernandez, "A robust and automated methodology for the analysis of Time- Dependent Variability at transistor level" Integration, the VLSI Journal, vol. 72, pp. 13-20, 2020.

- P. Saraza-Canflanca, H. Carrasco-Lopez, A. Santana-Andreo, P. Brox, R. Castro-Lopez, E. Roca and F.V. Fernandez, "Improving the reliability of SRAM-based PUFs under varying operation conditions and aging degradation" Microelectronics Reliability, vol. 118, 114049, 2021.

- P. Saraza-Canflanca, J. Martin-Martinez, R. Castro-Lopez, E. Roca, R. Rodriguez, F. V. Fernandez and M. Nafria "Statistical characterization of Time-Dependent Variability defects using the Maximum Current Fluctuation", IEEE Transactions on Electron Devices, 2021.

#### Contributions to conferences as first author:

- P. Saraza-Canflanca, J. Diaz-Fortuny, A. Toro-Frias, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria and F.V. Fernandez, "Automated massive characterization of RTN using a transistor array chip", in International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), 2018.

- P. Saraza-Canflanca, D. Malagon, F. Passos, A. Toro, J. Nuñez, J. Diaz-Fortuny, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria and F.V. Fernandez, "Design considerations of an SRAM array for the statistical validation of time-dependent variability models", in International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), 2018.

- P. Saraza-Canflanca, J. Diaz-Fortuny, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria, F.V. Fernandez, "New method for the automated massive characterization of Bias Temperature Instability in CMOS transistors", in Design Automation and Test in Europe (DATE), 2019.

- P. Saraza-Canflanca, J. Diaz-Fortuny, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria and F.V.Fernandez, "TiDeVa: A toolbox for the automated and robust analysis of Time-Dependent Variability at transistor level", in International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), 2019.

- P. Saraza-Canflanca, H. Carrasco-Lopez, P. Brox, R. Castro-Lopez, E. Roca and F.V.Fernandez, "Improving the reliability of SRAM-based PUFs in the presence of aging", in International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), 2020.

- P. Saraza-Canflanca, H. Carrasco-Lopez, P. Brox, R. Castro-Lopez, E. Roca and F. V. Fernandez, "Improving the reliability of SRAM-based PUFs under varying conditions", in Conference on Design of Circuits and Integrated Systems (DCIS), 2020.

- P. Saraza-Canflanca, E. Camacho-Ruiz, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria and F.V.Fernandez, "Simulating the impact of Random Telegraph Noise on integrated circuits", in International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), 2021.

### Co-authored international journal papers:

- J. Diaz-Fortuny, **P. Saraza-Canflanca**, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, F.V. Fernandez and M. Nafria, "Flexible setup for the measurement of CMOS Time-Dependent Variability with array-based integrated circuits", IEEE Transactions on Instrumentation and Measurement, vol. 69, no. 3, pp. 853-864, 2019.

- J. Diaz-Fortuny, **P. Saraza-Canflanca**, R. Rodriguez, J. Martin-Martinez, R. Castro-Lopez, E. Roca, F.V. Fernandez and M. Nafria, "Statistical threshold voltage shifts caused by BTI and HCI at nominal and accelerated conditions", Solid State Electronics, p. 108037, 2021.

- G. Pedreira, J. Martin-Martinez, **P. Saraza-Canflanca**, R. Castro-Lopez, R. Rodriguez, E. Roca, F.V. Fernandez and M. Nafria, "Unified RTN and BTI statistical compact modeling from a defect-centric perspective", Solid State Electronics, p. 108112, 2021.

### Co-authored conference contributions:

• J. Diaz-Fortuny, **P. Saraza-Canflanca**, A. Toro-Frias, R. Castro-Lopez, J. Martin-Martinez, E. Roca, R. Rodriguez, F.V. Fernandez and M. Nafria, "A

model parameter extraction methodology including Time-Dependent Variability for circuit reliability simulation", in International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), 2018.

- G. Pedreira, J. Martin-Martinez, J. Diaz-Fortuny, **P. Saraza-Canflanca**, R. Rodriguez, R. Castro-Lopez, E. Roca, F.V. Fernandez and M. Nafria., "A new time efficient methodology for the massive characterization of RTN in CMOS devices", in IEEE International Reliability Physics Symposium (IRPS), 2019.

- A. Toro-Frias, **P. Saraza- Canflanca**, F. Passos, P. Martin-Lloret, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria and F.V. Fernandez, "Generation of lifetime-aware pareto-optimal fronts using a stochastic reliability simulator", in Design Automation and Test in Europe (DATE), 2019.

- , M. Nafria, J. Diaz-Fortuny, P. Saraza-Canflanca, J. Martin-Martinez, E. Roca, R. Castro-Lopez, R. Rodriguez, P. Martin-Lloret, A. Toro-Frias, D. Mateo, E. Barajas, X. Aragones and F. V. Fernandez, "Circuit reliability prediction: challenges and solutions for the device time-dependent variability characterization roadblock", in IEEE Latin America Electron Devices Conference (LAEDC), 2021.

- E. Camacho-Ruiz, **P. Saraza-Canflanca**, R. Castro-Lopez, E. Roca, and F.V.Fernandez, "A study of SRAM PUFs reliability using the Static Noise Margin", in International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), 2021.

### Contributions to book chapters:

• J. Martin-Martinez, J. Diaz-Fortuny, A. Toro-Frias, P. Martin-Lloret, P. Saraza-Canflanca, R. Castro-Lopez, R. Rodriguez, E. Roca, F. V. Fernandez, M. Nafria, "Modeling of variability and reliability in analog circuits", chapter from "Modelling methodologies in analogue Integrated Circuit design".

### Awards:

- EDA Competition Winner in the SMACD2019 Conference, held in Lausanne on July 2019, for the work "TiDeVa: a toolbox for the automated and robust analysis of Time-Dependent Variability at transistor level", co-authored by J. Diaz-Fortuny, R. Castro-López, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria and F. V. Fernandez.

- Best Paper Award in the DCIS2020 Conference, held virtually on November 2020, for the work "Improving the reliability of SRAM-based PUFs under varying conditions", co-authored by H. Carrasco-Lopez, P. Brox, R. Castro-Lopez, E. Roca and F. V. Fernandez.

• Best Paper Award Runner-Up in the SMACD2021 Conference, held virtually on July 2021, for the work "Simulating the impact of Random Telegraph Noise on integrated circuits", co-authored by E. Camacho-Ruiz, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, M. Nafria and F.V.Fernandez.

## List of abbreviations

- **BER:** Bit Error Rate

- BL: Bitline

- BTI: Bias Temperature Instability

- **CDF**: Cumulative Distribution Function

- CMOS: Complementary Metal-Oxide-Semiconductor

- **CRP:** Challenge Response Pair

- **CUT:** Circuit Under Test

- **DRV:** Data Retention Voltage

- **DUT:** Device Under Test

- ECC: Error Correcting Code

- GPIB: General Purpose Interface Bus

- HCI: Hot-Carrier Injection

- HDA: Helper Data Algorithm

- IC: Integrated Circuit

- IID: Independent and Identically-Distributed

- **IoT:** Internet of Things

- MCF: Maximum Current Fluctuation

- MLE: Maximum Likelihood Estimation

- MSE: Mean Squared Error

- MTSV: Maximum Trip Supply Voltage

- NBTI: Negative Bias Temperature Instability

- NMOS: N-channel Metal-Oxide-Semiconductor

- NVM: Non-Volatile Memory

- **PBTI:** Positive Bias Temperature Instability

- **PDF:** Probability Density Function

- **PDO:** Probabilistic Occupancy Model

- **PMOS:** P-channel Metal-Oxide-Semiconductor

- **PSO:** Particle Swarm Optimization

- **PUF:** Physical Unclonable Function

- **PV:** Process Variability

- **RAD:** Reliability-Aware Design

- **RFID:** Radio-Frequency Identification

- **RNG:** Random Number Generator

- **RTN:** Random Telegraph Noise

- SRAM: Static Random-Access Memory

- TCAD: Technology Computer Aided Design

- **TDDB:** Time-Dependent Dielectric Breakdown

- **TDV**: Time-Dependent Variability

- **TRNG:** True Random Number Generator

- **TZV:** Time-Zero Variability

- WL: Wordline

# Contents

| 1 | Intr | roduction                                                                           | 24 |

|---|------|-------------------------------------------------------------------------------------|----|

|   | 1.1  | Motivation                                                                          | 24 |

|   | 1.2  | Time-Zero Variability in CMOS technologies                                          | 26 |

|   | 1.3  | Time-Dependent Variability                                                          | 27 |

|   |      | 1.3.1 Random Telegraph Noise                                                        | 27 |

|   |      | 1.3.2 Bias Temperature Instability                                                  | 30 |

|   |      | 1.3.3 Hot Carrier Injection                                                         | 31 |

|   | 1.4  | A model for Time-Dependent Variability: the Probabilistic Defect<br>Occupancy model | 32 |

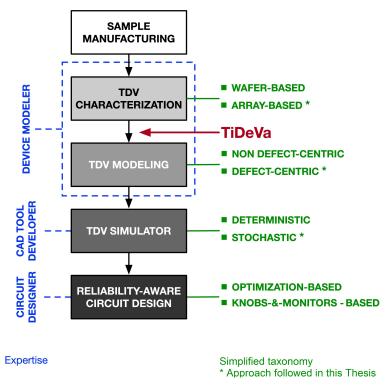

|   | 1.5  | A complete flow towards reliability-aware circuit design                            | 34 |

|   | 1.6  | Exploiting variability in hardware security applications                            | 36 |

|   |      | 1.6.1 Why PUFs?                                                                     | 36 |

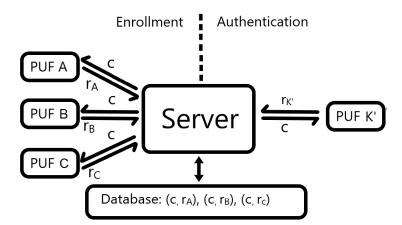

|   |      | 1.6.2 What are PUFs? $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 37 |

|   |      | 1.6.3 PUF applications                                                              | 38 |

|   |      | 1.6.4 Non-ideal behavior of PUF reliability                                         | 40 |

|   |      | 1.6.5 PUF implementations                                                           | 41 |

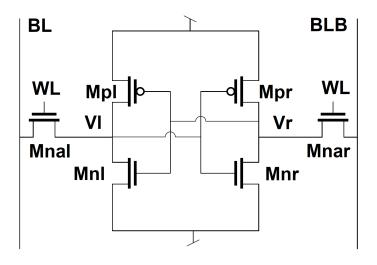

|   | 1.7  | The SRAM PUF                                                                        | 41 |

|   | 1.8  | Main contributions of this Thesis                                                   | 44 |

|   | 1.9  | Structure of the rest of this Thesis                                                | 45 |

| 2 | Var  | riability characterization framework                                                | 47 |

|   | 2.1  | Strategy for the characterization of TDV at the device level                        | 48 |

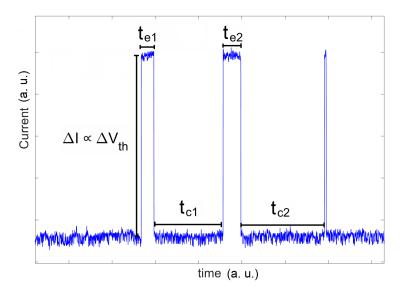

|   |     | 2.1.1  | Random Telegraph Noise                                                                                                                   | 49  |

|---|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |     | 2.1.2  | Aging phenomena                                                                                                                          | 50  |

|   | 2.2 | Requir | rements for the characterization of TDV at the device level                                                                              | 52  |

|   | 2.3 |        | ance: a transistor array for variability characterization at the level                                                                   | 53  |

|   | 2.4 | Setup  | for the characterization of variability at the device level $\ldots$ .                                                                   | 54  |

|   | 2.5 |        | a: a toolbox for the automated analysis of Time-Dependent ility                                                                          | 55  |

|   |     | 2.5.1  | Existing methods for the TDV defect parameter extraction                                                                                 | 57  |

|   |     | 2.5.2  | TDV parameter extraction using a Maximum Likelihood Es-<br>timation method                                                               | 59  |

|   |     | 2.5.3  | Some examples of TDV characterization at the device level performed by TiDeVa                                                            | 65  |

| 3 | Ran | dom T  | Celegraph Noise: characterization methods and results                                                                                    | 69  |

|   | 3.1 | Ampli  | tude distributions                                                                                                                       | 69  |

|   |     | 3.1.1  | Correlation between the amplitudes associated to trapping/de-trapping events and the time constants $\ldots \ldots \ldots \ldots \ldots$ | 71  |

|   | 3.2 | Numbe  | er of active defects                                                                                                                     | 73  |

|   | 3.3 |        | erent approach to RTN characterization: Maximum Current ation analysis                                                                   | 74  |

|   |     | 3.3.1  | Generation of MCF values                                                                                                                 | 77  |

|   |     | 3.3.2  | MCF optimization procedure to retrieve the RTN parameters                                                                                | 81  |

|   |     | 3.3.3  | Verification of the MCF-based methodology                                                                                                | 87  |

|   | 3.4 | Impact | t of the probability of occupation on the characterization of RTN                                                                        | 88  |

|   |     | 3.4.1  | Theoretical approach to the influence of the probability of occupation on the measurement of RTN                                         | 89  |

|   |     | 3.4.2  | Experimental results on the influence of the probability of oc-<br>cupation on the measurement of RTN                                    | 95  |

|   |     | 3.4.3  | Concluding remarks on the impact of the Probability of Oc-<br>cupation on the RTN characterization tests                                 | 100 |

| 4        | Con | struct   | ing the PDO model and applications                                                                       | 102   |

|----------|-----|----------|----------------------------------------------------------------------------------------------------------|-------|

|          | 4.1 |          | t approach to the determination of the defect time constants of DO model                                 | . 102 |

|          |     | 4.1.1    | Time constants distribution                                                                              | . 103 |

|          |     | 4.1.2    | Probability of occupation                                                                                | . 106 |

|          |     | 4.1.3    | Probability of a single emission event                                                                   | . 110 |

|          | 4.2 |          | ond, more efficient approach to the determination of the defect constants of the PDO model               | . 111 |

|          | 4.3 | PDO      | model time constants: optimization procedure and results $\$                                             | . 117 |

|          |     | 4.3.1    | Optimization procedure                                                                                   | . 118 |

|          |     | 4.3.2    | Results when each stress condition is considered independently                                           | y 122 |

|          |     | 4.3.3    | Results when all the stress conditions are considered together                                           | 123   |

|          | 4.4 | Simula   | ation of Time-Dependent Variability phenomena                                                            | . 126 |

|          |     | 4.4.1    | Random Telegraph Noise                                                                                   | . 126 |

|          |     | 4.4.2    | Aging phenomena                                                                                          | . 131 |

|          | 4.5 | Emula    | ation of TDV phenomena for their experimental characterization                                           | n 132 |

|          |     | 4.5.1    | Accounting for the impact of the instrumentation on the measurements                                     | . 133 |

|          |     | 4.5.2    | Generation of RTN traces that emulate experimental charac-<br>terization                                 | . 135 |

|          |     | 4.5.3    | Concluding remarks on the generation of current traces that<br>emulate the behavior of experimental data | . 140 |

|          | 4.6 |          | uding remarks on the characterization and modeling of TDV mena                                           | . 141 |

| <b>5</b> | Exp | oloiting | g TZV through the utilization of SRAM PUFs                                                               | 142   |

|          | 5.1 | KipT:    | an IC for the evaluation of the reliability of SRAM PUFs $$                                              | . 143 |

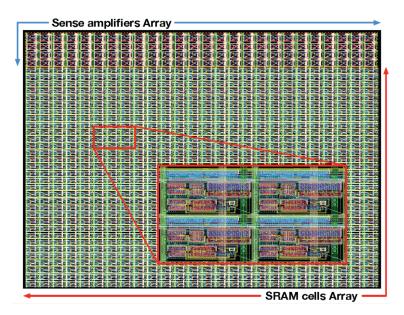

|          |     | 5.1.1    | The SRAM cell array in the KipT chip                                                                     | . 143 |

|          | 5.2 | PUF ]    | properties and metrics                                                                                   | . 148 |

|          |     | 5.2.1    | Bit Error Bate                                                                                           | . 148 |

|   |     | 5.2.2  | Hamming Distance                                                     |

|---|-----|--------|----------------------------------------------------------------------|

|   |     | 5.2.3  | Percentage of (un)stable bits                                        |

|   |     | 5.2.4  | Hamming Weight                                                       |

|   |     | 5.2.5  | Minimum Entropy                                                      |

|   | 5.3 |        | ous Dark-Bit Masking methods to improve the reliability of<br>I PUFs |

|   |     | 5.3.1  | Multiple Evaluation approach                                         |

|   |     | 5.3.2  | Data Remanence approach                                              |

|   |     | 5.3.3  | Exploiting the power supply ramp rate                                |

|   | 5.4 | Maxin  | num Trip Supply Voltage method                                       |

|   | 5.5 | Exper  | imental strategy                                                     |

|   | 5.6 | Some   | preliminary considerations                                           |

|   | 5.7 | PUF r  | response reliability under different conditions                      |

|   |     | 5.7.1  | Reliability under nominal conditions                                 |

|   |     | 5.7.2  | Reliability under supply voltage variations                          |

|   |     | 5.7.3  | Reliability under temperature variations                             |

|   |     | 5.7.4  | Reliability after circuit aging                                      |

| 6 | Cor | clusio | ns 163                                                               |

#### 14

# List of Figures

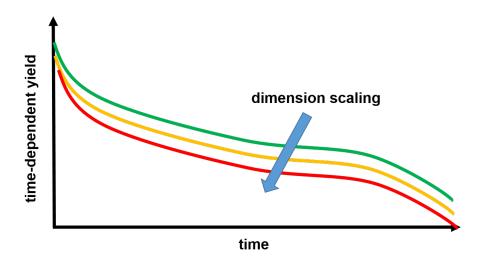

| 1.1  | Representation of the evolution of yield with time, together with the impact that transistor scaling can have on it                                                                                                                                               | 25 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

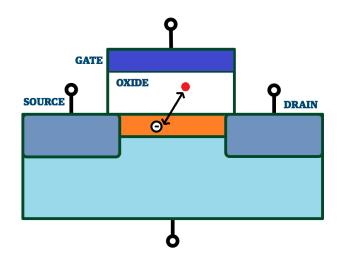

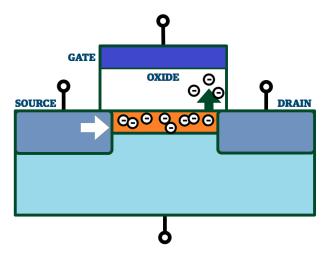

| 1.2  | Representation of the trapping/detrapping of charge carriers that originate RTN                                                                                                                                                                                   | 28 |

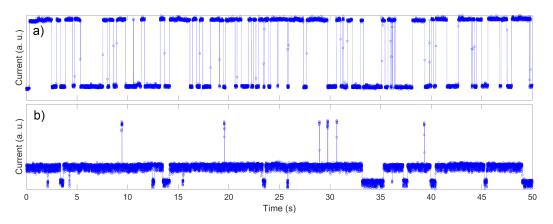

| 1.3  | Two current traces displaying RTN. In a), only one defect is giving rise to detectable RTN; in b), two.                                                                                                                                                           | 28 |

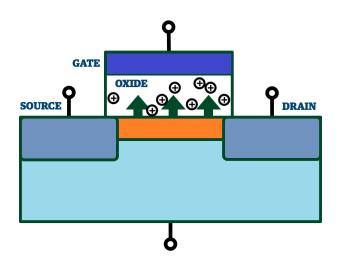

| 1.4  | Representation of the trapping of charge carriers that originate BTI                                                                                                                                                                                              | 31 |

| 1.5  | Representation of the injection of hot carriers into the oxide that originates HCI.                                                                                                                                                                               | 32 |

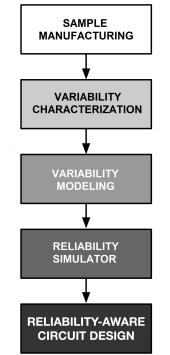

| 1.6  | Block diagram for the development of RAD solutions                                                                                                                                                                                                                | 35 |

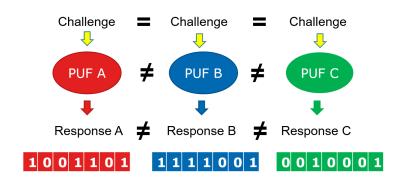

| 1.7  | Representation of the property of uniqueness of PUFs                                                                                                                                                                                                              | 38 |

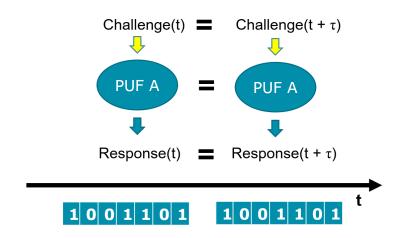

| 1.8  | Representation of the property of reliability of PUFs                                                                                                                                                                                                             | 38 |

| 1.9  | Block representation of the enrollment and authentication phases of<br>a PUF used for device authentication                                                                                                                                                       | 39 |

| 1.10 | Schematic of a 6T SRAM cell                                                                                                                                                                                                                                       | 42 |

| 2.1  | Block diagram for the development of RAD solutions, indicating a simple taxonomy of each stage and the different areas of expertise that RAD involves. TiDeVa is the tool developed for the automated analysis of TDV tests and will be presented in Section 2.5. | 48 |

| 2.2  | Current trace displaying RTN events measured with the chip used in<br>this work and the characterization setup presented in this Chapter.<br>The RTN parameters have been indicated.                                                                              | 50 |

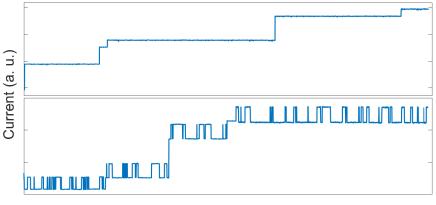

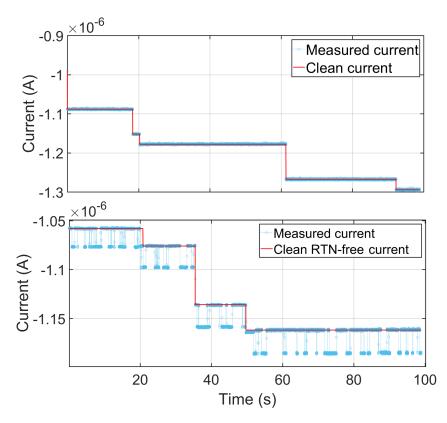

| 2.3  | BTI recovery traces measured with the Endurance chip and the setup<br>presented in this work. At the top, only BTI detrapping events are<br>present. At the bottom, the BTI detrapping events are mixed with<br>RTN transitions. The coexistence of such differents types of behavior<br>can make the parameter extraction challenging                    | 51 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.4  | Schematic representation of the experimental setup used in this work.                                                                                                                                                                                                                                                                                     | 55 |

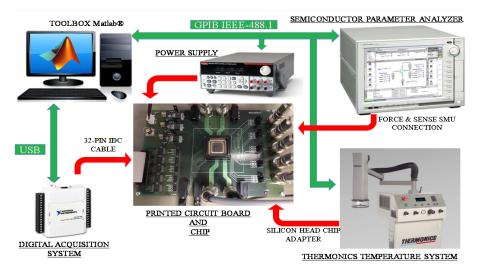

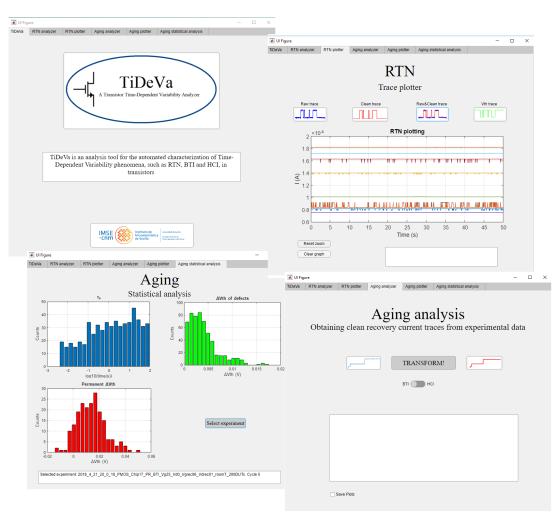

| 2.5  | Some tabs of the TiDeVa toolbox. Clockwise, starting from the top-<br>left corner: i) initial tab, ii) tab for the graphical visualization of<br>the RTN current traces, iii) tab for the analysis of aging experiments<br>data, and iv) tab for the visualization of the statistical distributions<br>obtained for the parameters of an aging experiment | 56 |

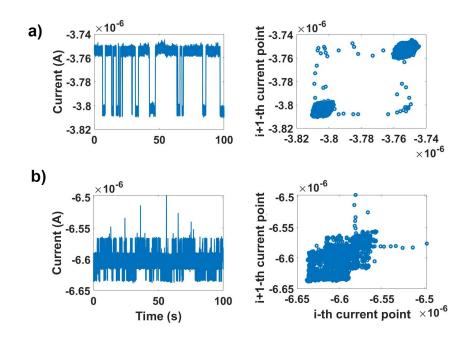

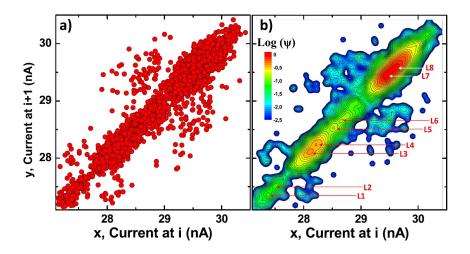

| 2.6  | Current trace and the corresponding TLP for a device with one detectable RTN defect (a) and a device with several RTN defects (b).                                                                                                                                                                                                                        | 58 |

| 2.7  | TLP of a current trace that displays RTN (a), together with the corresponding wTLP (b). Taken from [104]                                                                                                                                                                                                                                                  | 59 |

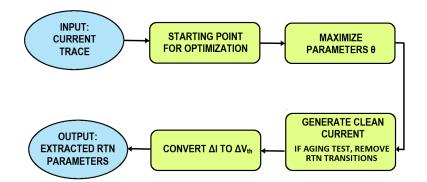

| 2.8  | Flow diagram of the main steps of the MLE-based algorithm used to extract the RTN parameters.                                                                                                                                                                                                                                                             | 60 |

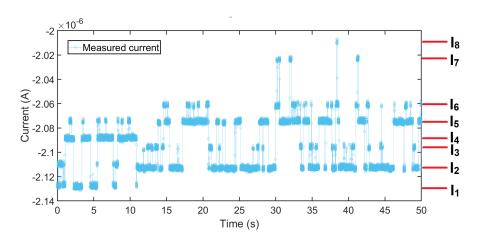

| 2.9  | Measured current trace for a PMOS device in the Endurance chip displaying RTN, and the corresponding current levels extracted by the MLE method                                                                                                                                                                                                           | 62 |

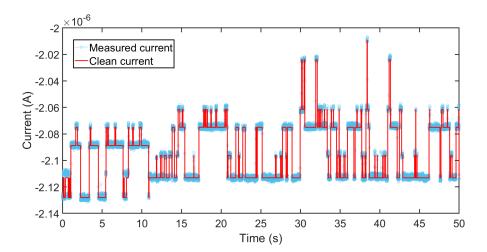

| 2.10 | Experimentally measured current trace (blue), together with the processed clean current trace (red).                                                                                                                                                                                                                                                      | 62 |

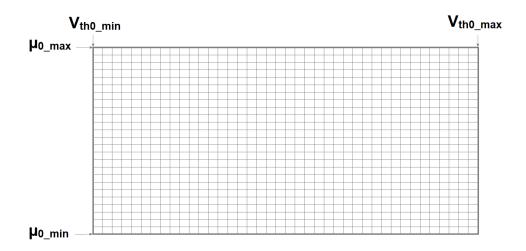

| 2.11 | Representation of the grid that contains all possible combinations of the $\mu_0$ and $_{th0}$ parameters.                                                                                                                                                                                                                                                | 64 |

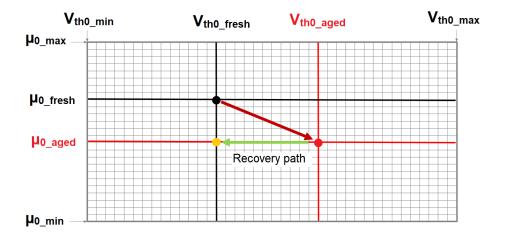

| 2.12 | Representation of the expected evolution of the transistor parameters<br>in an aging test                                                                                                                                                                                                                                                                 | 65 |

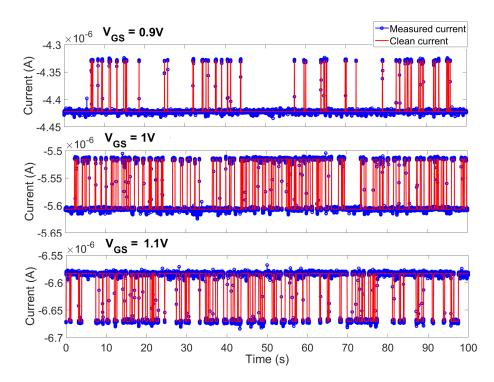

| 2.13 | Current traces of one 80nmx60nm PMOS device measured at $ V_{DS}  = 0.1V$ and various $ V_{GS} $ displaying RTN transitions. The blue lines correspond to the raw experimental data, the red ones to the "clean" traces processed by TiDeVa.                                                                                                              | 66 |

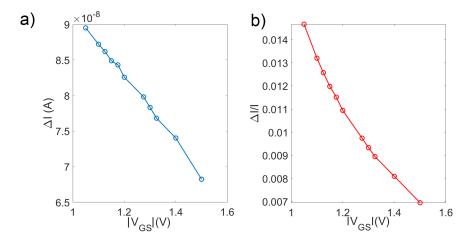

| 2.14 | Absolute (a) and relative (b) current amplitude of a defect monitored at different gate voltages                                                                                                                                                                                                                                                          | 66 |

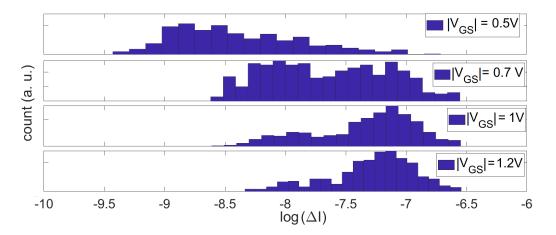

| 2.15 | Experimental distribution of the amplitude of RTN defects at $ V_{DS}  = 0.1V$ and various $ V_{GS} $ values. The defects extracted by the TiDeVa tool from 500 transistors have been used to construct these histograms.                                                                                                                                 | 67 |

| 2.16 | BTI recovery traces measured at $ V_{GS}  = 0.6V$ and $ V_{DS}  = 0.1V$ after<br>a stress phase at $ V_{GS}  = 2.5V$ and $ V_{DS}  = 0V$ . The processing has<br>been performed with the TiDeVa toolbox.                                                                                                                                                  | 68 |

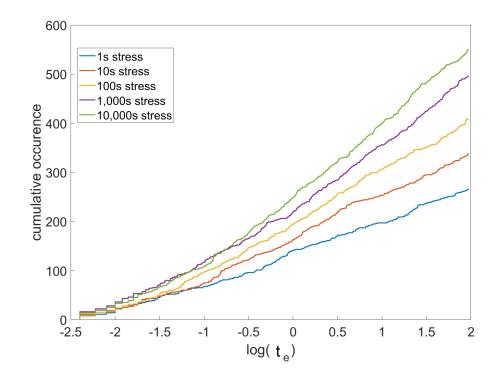

| 2.17 | Cumulative occurrence of the emission times for each of the five recovery phases in a BTI experiment with $ V_{GS}  = 2.5V$ and $V_{DS} = 0V$ during the stress phase, and $ V_{GS}  = 0.6V$ and $ V_{DS}  = 0.1V$ during the recovery phase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Experimental current trace measured for an 80x60nm PMOS device at $ V_{DS}  = 0.1V$ and $ V_{GS}  = 0.7V$ . Three distinct RTN defects have been detected, and their amplitudes have been extracted by TiDeVa.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70 |

| 3.2  | a) Histogram of the extracted RTN-induced current shift amplitudes for 500 devices measured at $ V_{DS}  = 0.1V$ and $ V_{GS}  = 1V$ and b) CDFs of the extracted RTN-induced current shift amplitudes for 500 devices measured at $ V_{DS}  = 0.1V$ and various $ V_{GS} $ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71 |

| 3.3  | a) Defect amplitude vs. emission time, and b) defect amplitude vs capture time. The defects have been extracted from current measurements performed at $ V_{DS}  = 0.1V$ and $ V_{GS}  = 1V.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 72 |

| 3.4  | Amplitude of the current shifts associated to emission events vs. times<br>at which the emissions occur during one of the recovery phases of one<br>of the BTI tests. No noticeable correlation can be observed between<br>the parameters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73 |

| 3.5  | Histograms of the number of active defects found at $ V_{\rm DS} =0.1V$ and various $ V_{\rm GS} .$ The red lines are the fitted Poisson distributions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74 |

| 3.6  | Measured current trace of a transistor from the chip in [95]. The MCF, defined as the difference between the cumulative current maximum and the cumulative current minimum from $t_0$ (in this case $t_0 = 0$ s) up to a time $t$ , is depicted for two instants in time, $t_1$ and $t_2$ . The red line represents the evolution of the lower envelope of the current values, the green one represents the upper envelope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76 |

| 3.7  | $ \begin{array}{l} \mbox{Evolution of the MCF for 20 devices measured during 50s at }  V_{GS}  = \\ 0.6V \mbox{ and }  V_{DS}  = 0.1V. \hfill 0.1V.$ | 77 |

| 3.8  | CDFs of the MCFs obtained for 500 devices measured at $ V_{GS}  = 0.6V$ , $ V_{DS}  = 0.1V$ for t = 1s and t = 50s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77 |

| 3.9  | Schematic representation of the generation of the component of the MCF associated to RTN defects for a device by sampling the corresponding distributions. In the example, the generated device has 4 active RTN defects, with the indicated associated amplitudes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 78 |

| 3.10 | a) Probability density function and b) cumulative distribution function of a Gaussian background noise with $\sigma = 1$ nA, and c) cumulative distribution function of the largest order statistic of that Gaussian distribution if $n_{points} = 25,000$ is considered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 3.11 | Comparison between the experimental and obtained CDFs at three different bias conditions and at three different time instants                                                                                                                                                                                                          | 83 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.12 | Probability density functions obtained for the amplitudes associated<br>to RTN defect trapping/detrapping through the MCF-based opti-<br>mization procedure                                                                                                                                                                            | 84 |

| 3.13 | Temporal evolution of the mean number of active defects in devices $\langle N \rangle$ , evaluated with the corresponding distribution retrieved through the MCF-based optimization behavior.                                                                                                                                          | 85 |

| 3.14 | Comparison between the experimental and obtained CDFs at three different bias conditions and at three different time instants when the amplitudes obtained through the MLE-based methodology are fixed through the optimization procedure.                                                                                             | 86 |

| 3.15 | Comparison between the experimental CDFs at $V_{GS} = 1.2V$ and the ones generated using the parameters obtained from the optimization procedure using only the first 10s, at three different time instants                                                                                                                            | 88 |

| 3.16 | Map of the probability of occupation of defects depending on their time constants at the start of the measuring window when the measurement starts immediately after the biasing of the devices (Scenario 1).                                                                                                                          | 91 |

| 3.17 | Map of the probability of occupation of defects depending on their time constants at the end of the measuring window when the measurement starts immediately after the biasing of the devices (Scenario 1).                                                                                                                            | 92 |

| 3.18 | Difference of probability of occupation at the end of the measurement with respect to the start of the measurement when the measurement starts immediately after the biasing of the devices (Scenario 1)                                                                                                                               | 93 |

| 3.19 | Map of the probability of occupation of defects depending on their time constants at the beginning (a) and at the end (b) of the measuring window when the measurement starts 10,000s after the biasing of the devices (Scenario 2).                                                                                                   | 94 |

| 3.20 | Map of the probability of occupation of defects depending on their time constants at the beginning (a) and at the end (b) of the measuring window when the measurement starts immediately (Scenario1) and (c), (d) 10,000s after the biasing of the devices (Scenario 2). The biasing conditions are $V_{GS} = 0.6V$ , $V_{DS} = 0.1V$ | 95 |

| 3.21 | Drain current traces measured for some devices when the first (a) and the second (b) scenario is considered, with $ V_{GS}  = 1.2$ V and $ V_{DS}  = 0.1$ V                                                                                                                                                                            | 97 |

|      |                                                                                                                                                                                                                                                                                                                                        |    |

| 3.22 | Total drain current for the 392 devices in the first (top) and second (bottom) scenario in linear and logarithmic time scales. The biasing values are $ V_{GS}  = 1.2$ V and $ V_{DS}  = 0.1$ V                                        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.23 | Total drain current for the 392 devices in the first (top) and second (bottom) scenarios in linear and logarithmic time scales. The biasing values are $ V_{GS}  = 0.6$ V and $ V_{DS}  = 0.1$ V                                       |

| 3.24 | Cumulative distribution functions of the MCF values for both scenar-<br>ios after 10s (top) and 100s (bottom) of measurement. The biasing<br>values are $V_{GS} = 0.6$ V and $V_{DS} = 0.1$ V                                          |

| 4.1  | Example of a bivariate lognormal probability distribution for the time constants of defects                                                                                                                                            |

| 4.2  | pdf of the time-to-emissions $t_e$ for a defect characterized by an emission time constant $\tau_e = 100$ s, represented for linear (a) and logarithmic (b) variables                                                                  |

| 4.3  | Representation of the parallelization scheme of a MSM test of 5 cycles.<br>107 $$                                                                                                                                                      |

| 4.4  | Probability of occupation maps at the beginning of each phase for a BTI test of 5 SM cycles                                                                                                                                            |

| 4.5  | Probability that a defect exists $(D_{def})$ and is occupied $(P_{occ})$ at the beginning of each of the measurement phases. This is obtained by multiplying $D_{def}$ in Fig. 4.1 by $P_{occ}$ in the central column of Fig. 4.4. 109 |

| 4.6  | Probability that a defect with certain time constants experiences a single emission event within that phase                                                                                                                            |

| 4.7  | Probability that a defect with certain time constants exists, is occu-<br>pied at the beginning of the measurement window and experiences a<br>single emission event during said window, for the five cycles 113                       |

| 4.8  | Probability density functions of the emission time constants of the defects that undergo a single emission event at each of the five measurement phases                                                                                |

| 4.9  | Probability for a defect with emission time constant $\tau_e$ that experi-<br>ences an emission during the time window, to undergo that emission<br>event at a given time $t_e$                                                        |

| 4.10 | Probability for a defect with a given $\tau_e$ to exist, be occupied at the beginning of the measurement phase, and undergo a single emission event at $t_e$ between $t_{min}$ and $t_{max}$ , for each of the five cycles 116         |

| 4.11 | Cumulative distribution functions of the single emission events within<br>each of the 5 cycles of the considered test                                                                                                                  |

| 4.12 | Example of experimental and generated CDFs of the single emission events for the five recovery cycles of a MSM test                                                                                                                                                                         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.13 | Experimental CDFs of the single emission events obtained for the first recovery cycle of two measurements in which the stress gate voltage was 1.2V (a) and for the last recovery cycle of two measurements in which the stress gate voltage was 2.5V (b)                                   |

| 4.14 | Experimental CDFs of the single emission events obtained for all the recovery cycles of the measurements at each of the stress conditions, together with the CDF generated for the parameters obtained through the optimization using the data from the $ V_{GS}  = 2.5V$ measurements. 123 |

| 4.15 | Time constant distribution found when the results obtained at dif-<br>ferent conditions are used in a combined manner in the optimization<br>process                                                                                                                                        |

| 4.16 | Experimental CDFs of the single emission events obtained for each recovery cycle of measurements at each of the stress conditions, to-<br>gether with the CDF generated for the parameters in Table 4.4 125                                                                                 |

| 4.17 | Experimental CDFs of the single emission events obtained for each recovery cycle for a BTI test with stress gate voltage of 1.8V, together with the CDF generated for the parameters in Table 4.4                                                                                           |

| 4.18 | Schematic representation of the emulation of the impact of RTN on<br>a transistor through the inclusion of a variable voltage source at the<br>gate of the device                                                                                                                           |

| 4.19 | Flow diagram depicting the necessary steps for the generation of the $\Delta V_{th}$ traces used for the simulation of the impact of RTN on circuits. 128                                                                                                                                   |

| 4.20 | Some examples of threshold voltage shift traces generated by sampling<br>the different RTN parameter distributions and used to simulate the<br>impact of RTN on circuits                                                                                                                    |

| 4.21 | Simulated output current for a constant input current (a) and the corresponding copy factor (b) for the simple PMOS current mirror depicted in the inset                                                                                                                                    |

| 4.22 | Experimentaly measured output current for a constant input current (a) and the corresponding copy factor (b) for one of the PMOS current mirrors in [123]                                                                                                                                   |

| 4.23 | Simulation flow of the stochastic reliability simulator, which includes<br>a set of intermediate time steps to update the stress conditions to<br>account for the link between aging and biasing                                                                                            |

| 4.24 | Current traces measured for the same device, at the same bias con-<br>ditions and with the same measurement step when 4 (top) or 100<br>(bottom) averaging samples are used. Increasing the number of av-<br>eraging sample significantly reduces the noise level, which facillitates<br>the detection of the RTN transitions |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.25 | Current trace measured in the laboratory displaying "intermediate RTN levels", which arise from the averaging of the actual RTN levels. 135                                                                                                                                                                                   |

| 4.26 | Flow diagram depicting the necessary steps for the generation of the traces that emulate the real measurements of RTN performed in the laboratory                                                                                                                                                                             |

| 4.27 | From top to bottom: ideal current trace; emulated experimental current trace when 1 averaging sample is employed; emulated experimental current trace when 20 averaging samples are employed                                                                                                                                  |

| 4.28 | From top to bottom: ideal current trace; emulated experimental current trace when 1 averaging sample is employed; emulated experimental current trace when 20 averaging samples are employed                                                                                                                                  |

| 4.29 | From top to bottom: ideal current trace; emulated experimental current trace when 1 averaging sample is employed; emulated experimental current trace when 20 averaging samples are employed                                                                                                                                  |

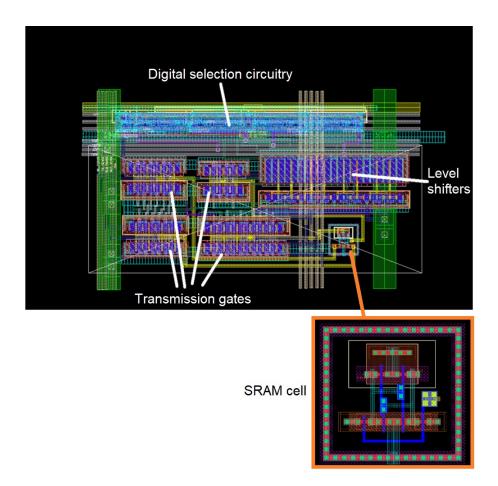

| 5.1  | Annotated layout of the SRAM array in the KipT chip                                                                                                                                                                                                                                                                           |

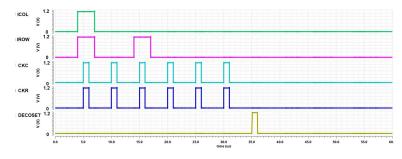

| 5.2  | Digital signals used to select an SRAM cell of the KipT chip 144                                                                                                                                                                                                                                                              |

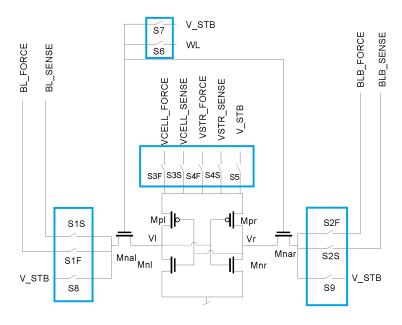

| 5.3  | Schematic representation of the SRAM cell with the transmission gates for the connection of the analog paths to the cell terminals 146                                                                                                                                                                                        |

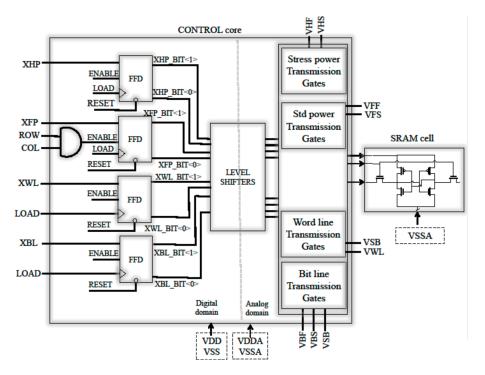

| 5.4  | Block diagram of the SRAM unit cell in the KipT chip                                                                                                                                                                                                                                                                          |

| 5.5  | Layout of the SRAM unit cell in the KipT chip                                                                                                                                                                                                                                                                                 |

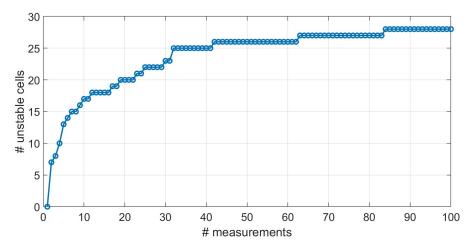

| 5.6  | Number of unstable cells (i.e., cells that have at least one erroneous power-up value) against the number of power-up evaluations 151                                                                                                                                                                                         |

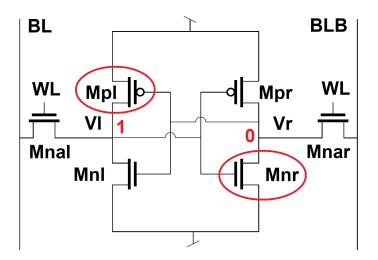

| 5.7  | Transistors degraded during a hold stress with a '1' stored 160 $$                                                                                                                                                                                                                                                            |

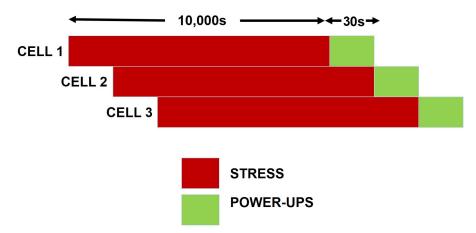

| 5.8  | Schematic representation of the application of stress to the SRAM cells in a parallelized manner                                                                                                                                                                                                                              |

# List of Tables

| 3.1 | Parameters of the two-lognormal distribution of the RTN-induced<br>current shift amplitudes obtained through the MLE-based parameter<br>extraction procedure                                                                                                                                            |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | Parameters of the two-lognormal distribution of the RTN-induced<br>current shift amplitudes, the lognormal evolution of the number of<br>defects with time, and the background noise, obtained through the<br>MCF-based optimization procedure                                                          |

| 3.3 | Parameters of the two-lognormal distribution of the RTN-induced<br>current shift amplitudes obtained through the MLE-based technique,<br>and those of the lognormal evolution of the number of defects with<br>time, and the background noise, obtained through the MCF-based<br>optimization procedure |

| 3.4 | Parameters of the two-lognormal distribution of the RTN-induced<br>current shift amplitudes, the lognormal evolution of the number of<br>defects with time, and the background noise, obtained through the<br>MCF-based optimization when only the first 10s of measurement are<br>considered           |

| 4.1 | Duration of the cycles during the MSM procedure                                                                                                                                                                                                                                                         |

| 4.2 | Information about the experimental tests performed to obtain the data used during the optimization processes. The stress $ V_{GS} $ was kept at 0V, since these are BTI tests                                                                                                                           |

| 4.3 | Total number of defects in devices, and parameters of the time con-<br>stant distribution and its bias dependencies, obtained through an<br>individual optimization process for each distinct stress conditions 122                                                                                     |

| 4.4 | Total number of defects in devices, and parameters of the time con-<br>stant distribution and its bias dependencies, obtained through an<br>optimization process in which the results from the tests performed at<br>all the stress conditions are considered together                                  |

| 5.1 | Values at which the four control bits have to be set in order to enable<br>each of the possible operation modes for a given cell in the array 146                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2 | Hamming Weight calculated for the power-up response of five different chip instances, and their mean value                                                                             |

| 5.3 | BER obtained for all the cells of the array, and for the different groups considered, after 2,000 power-ups at nominal conditions                                                      |

| 5.4 | BER obtained for all the cells of the array, and for the different groups considered, after 200 power-ups taking $V_{DD}$ to different values around its nominal one                   |

| 5.5 | BER obtained for all the cells of the array, and for the different groups considered, after 200 power-ups performed at different temperatures 158                                      |