# A thermal analysis for two modulation and control approaches for five-level diode-clamped rectifiers

Pablo Montero-Robina, Francisco Gordillo

Abstract—This paper compares two recently published modulation and control approaches for a grid-connected five-level diode-clamped rectifier in terms of conducting losses. In this way, a prior analysis of the conducting time at steady state is presented for both approaches, and the usage of the most stressed switching device is calculated. The usage for this switching device is then compared with a typical nearest-two-level modulation strategy to show the efficiency of the studied approaches. Some simulations are also carried out to validate this comparison.

*Index Terms*—Multilevel converters, Thermal analysis, Diode-clamped converter, Power control and modulation

#### I. INTRODUCTION

The increasingly demand of cleaner, more flexible and more reliable electric energy is making a revolution in the power electronic scenario as new devices, topologies and algorithms are arising as a response to this demand [1]–[3]. In this context, device temperature concern is leading a new concept of power converter designing known as thermal management [4]. This is due to the undesired effects that high temperature or temperature changes may have on power device reliability and durability [5]. Consequently, temperature is a key point that has to be taken into account in order to extend power device lifetime [6].

The current going through each power device creates a power flow that yields cyclic heating and cooling intervals. Considering the different thermal expansions coefficients of the components inside the power device, these intervals create mechanical stress that are translated to aging and, consequently, reduced lifetime expectancy [5], [7]. Therefore, it is critical to reduce its magnitude such as to reduce long-term expenses [8]. In this sense, active thermal control (ATC) takes into account these effects to modify the overall performance such as to reduce the amplitude of these cycles or the averaged temperature level [9]. At the same time, the device temperature monitoring and the junction temperature estimation have become of great importance to estimate the power device health state and also to allow the active thermal control to act accordingly [10].

On the other hand, an appealing topology of converters, referred as multilevel ones, offers several advantages regarding grid current distortion and power device voltage limits, although the use of them entails more semiconductors devices in the system [11]. Depending on the topology, some semiconductors might be closed longer than others which entails more conducting losses and therefore bigger thermal aging effects. As a consequence, these devices are more likely to reach its lifetime end than the others which highly increase the cost of maintenance. As a result, several studies have been carried out to consider the thermal management into the control of multilevel converter [12]–[14].

One of the most common multilevel converter topologies used in the industry is the diode-clamped converter (DCC) [15]. In this regard, the three-level kind has been well accepted and spread along plenty of industrial applications [16]. However, the actual research on the five-level one has still room for improvements. That is why this paper focuses on the five-level diode-clamped converter topology and analyzes two of the modulation and control approaches previously published [17] that tackles the capacitor voltage unbalance issue. In the cited publication, the approaches are based on considering the duty ratios of each voltage level for each phase and modelling the current control and capacitor voltage unbalance with these variables. As a result, they consider all possible levels within a switching period. This fact could yield higher switching losses than other ones, although it could make the dissipated power to be more equally distributed among the semiconductors, reducing the thermal cycles and aging. Therefore, this paper revisits the two proposed approaches and compares them in terms of thermal effects.

The outline of the paper is as follows: Sect. II summarizes the used model, control and modulation

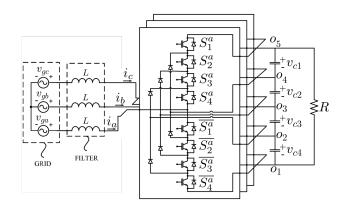

Fig. 1. Schematic of 5-level DCC

approaches; Sect. III presents a thermal analysis of this topology with the cited approaches; Sect. IV presents several simulations and its main comparisons; and, finally, Sect. V draws some conclusions about the contribution.

## II. MODEL, CONTROL AND MODULATION APPROACHES

This paper focuses on a five-level DCC shown in Fig.1. The modelling, control and modulation approaches used in this paper are retrieved from [17] and summarized in the next subsections.

#### A. Five-level DCC Model

The dynamics of the system are modelled using variables averaged over a switching period T referred as duty ratios. These duty ratios  $d_{ij} \in [0, 1]$ are labelled for each phase  $i = \{a, b, c\}$  and each level  $j = \{1, 2, 3, 4, 5\}$  and reflects the part of a period T that phase i output is connected to level j, therefore  $\sum_{i}^{5} d_{ij} = 1$  which is a restriction for each phase. By performing a Clarke transformation using the power invariant form, the duty ratios can be expressed in  $\alpha\beta\gamma$  frame instead of the *abc* one. The main advantage of doing so in a three-phase system is that variables  $d_{\gamma j}$  are related to the zero-sequence component of the voltage output and therefore, they do not appear in the current dynamic. In this way, their value do not affect the current controller as long as saturation is avoided—i.e.  $0 \leq d_{ij} \leq 1$  and they will be considered as degrees of freedom.

Defining the desired normalized output voltage of each phase as  $u_k$  for  $k = \{\alpha, \beta\}$ , its value can be achieved in averaged terms by fulfilling  $u_k = -2d_{k1} - d_{k2} + d_{k4} + 2d_{k5}$ , (1) where duty ratios  $d_{k3}$  do not appear and therefore they will be obtained in *abc* frame by applying the  $\sum_j^5 d_{ij} = 1$  restrictions. As a consequence, there are still 8 duty ratio values to obtain. Notice that component  $\gamma$  has been omitted due to the reason stated previously. Regarding the capacitor voltage unbalance, there are four signals to balance which yield three unbalancing signals referred as  $\{v_{d1} = v_{c4} - v_{c1}, v_{d2} = v_{c3} - v_{c2}, v_{d3} = v_{c2} - v_{c1}\}$ . Considering the previous definition of duty ratio in  $\alpha\beta$  frame, the dynamics of these signals can be expressed accordingly,

$$C\frac{dv_{d1}}{dt} = -i_{\alpha}(d_{\alpha 5} + d_{\alpha 1}) - i_{\beta}(d_{\beta 5} + d_{\beta 1}) \quad (2)$$

$$C\frac{dv_{d2}}{dt} = -i_{\alpha} \sum_{j=\{1,2,4,5\}} d_{\alpha j} - i_{\beta} \sum_{j=\{1,2,4,5\}} d_{\beta j}$$

(3)

$$C\frac{dv_{d3}}{dt} = -i_{\alpha}d_{\alpha4} - i_{\beta}d_{\beta4} \tag{4}$$

#### B. Control Algorithm

Usually, in grid-connected rectifier applications, variables  $u_{\alpha}$ ,  $u_{\beta}$  come from the application of the current controller such as to achieve current and dc-link voltage regulation. Accordingly, it is assumed that a PI Controller, for the dc-link voltage regulation, is set in cascade with a proportionalresonant current controller [18] that results in the values of  $u_{\alpha}$ ,  $u_{\beta}$ . In summary, once that variables  $u_{\alpha}$ ,  $u_{\beta}$  are known, two restrictions are obtained from (1). The remaining six conditions comes from the balancing control. Inspired by (2)–(4), control signals { $u_3$ ,  $u_4$ ,  $u_5$ ,  $u_6$ ,  $u_7$ ,  $u_8$ } and their corresponding control laws are defined such that

$$u_{3} = (d_{\alpha 5} + d_{\alpha 1}) = k_{\text{bal}} i_{\alpha} v_{d1}$$

(5)

$$u_4 = (d_{\beta 5} + d_{\beta 1}) = k_{\text{bal}} i_\beta v_{d1} \tag{6}$$

$$u_5 = \sum_{j=\{1,2,4,5\}} d_{\alpha j} = k_{\text{bal}} i_{\alpha} v_{d2} \tag{7}$$

$$u_5 = \sum_{j=\{1,2,4,5\}} d_{\beta j} = k_{\text{bal}} \, i_\beta v_{d2} \tag{8}$$

$$u_7 = d_{\alpha 4} = k_{\text{bal}} i_\alpha v_{d3} \tag{9}$$

$$u_8 = d_{\beta 4} = k_{\text{bal}} \, i_\beta v_{d3},\tag{10}$$

where  $k_{\text{bal}}$  is the balancing control parameter. In this way, the balancing is achieved at the same time that the 8 duty ratios are fully determined.

#### C. Modulation Stage

The duty ratios computation is straightforward but for the value of  $d_{\gamma j}$  left as a degree of freedom until this stage. Considering the previous steps, duty ratios  $d_{\alpha j}, d_{\beta j}$  for  $j = \{1, 2, 4, 5\}$  are known so it can be returned to *abc* frame once the corresponding  $d_{\gamma j}$  is also known. In this sense, two approaches are presented: the first one considers fixed values of  $d_{\gamma j}$ , whereas the second one selects the values of  $d_{\gamma j}$  that makes one duty ratio  $d_{ij}$  equal to zero. By doing so, the phase *i* with a duty ratio  $d_{ij} = 0$ does not commute at level *j*, avoiding additional commutations.

• Approach 1:

$$d_{\gamma i} = k_{\gamma i}$$

• Approach 2:

$$d_{\gamma j} = \max\left(\!\!-\sqrt{2}d_{\alpha j}, \frac{d_{\alpha j}}{\sqrt{2}} - d_{\beta j}\sqrt{\frac{3}{2}}, \frac{d_{\alpha j}}{\sqrt{2}} + d_{\beta j}\sqrt{\frac{3}{2}}\right),$$

for  $j = \{1, 2, 4, 5\}$ , where  $k_{\gamma j}$  are constant values and max is the function that retrieves the maximum value. However, in [17], approach 2 for  $j = \{2, 4\}$ is not always applied as it could introduce "large jumps" within one switching period. Thus, duty ratio  $d_{i2}$  or  $d_{i4}$  could be equal to zero only in case  $d_{i1}$  or  $d_{i5}$  turned out to be also zero respectively, otherwise it applies the same law than approach 1 for the corresponding level. For the theoretical comparison, this latter restriction is skipped such as to emphasize the differences in both approaches. In this way, the values of  $d_{ij}$  for each phase *i* and  $j = \{1, 2, 4, 5\}$  are obtained by using the inverse Clarke transformation. The remaining duty ratios  $d_{i3}$ are obtained from the  $\sum_{i=1\rightarrow 5} d_{ij} = 1$  restriction.

Finally, once all duty ratios are known, the levels they generate can be sequenced in a saw-tooth or stair-shaped waveform within a switching period to generate the voltage output of each phase.

### III. CONDUCTING LOSSES OF THE STUDIED APPROACHES

It can be noted that the previous modulations will yield different losses profiles as the conducting time and turning-on/off cycles of the power devices differ depending on the levels used. The higher the duty ratio, the higher the conducting time of the power devices. Regarding the switching losses, they highly depends on the switching frequency, the point of operation and how the levels are sequenced, however in multilevel converter, as the device blocking voltage is reduced by the introduction of several levels, its effect is considerably reduced in comparison with two level topologies. Nevertheless, a tradeoff comparison dependant of the operating point has to be made to determine which is the most suitable approach. Because of this, the switching losses has not been considered in this analysis as it would not yield any straight conclusion. Thus, the analysis will focus on a generic phase i and the conducting losses of the four upper semiconductors  $\{S_1^i, S_2^i, S_3^i, S_4^i\}$  considering that the lower ones will have a symmetrical behaviour. Also, no dead time is considered as it can be emulated as an extension of the duty ratios [19]. Notice that whenever a switching device  $S_n^i$  is open, its complementary lower-side one  $\overline{S_n^i}$  is closed. Hence, it is straightforward that four switching devices will be always connected. It is also worth to mention that the current will not always go through the switching device but through the anti-parallel diode depending on its direction, changing the losses profile. However, considering the periodical behaviour of the phase current and that this paper aims for a comparative analysis, it can be made assuming the worst-case conducting losses, usually the ones that are generated by the switching devices  $(i_i \leq 0)$ . In this way, a variable called switching device usage  $S_n^{i^u}$  can be modelled as

$$S_{1}^{iu} \doteq \begin{cases} d_{i5}|i_{i}| & \text{if } i_{i} \leq 0\\ 0 & \text{if } i_{i} \geq 0 \end{cases}$$

$$S_{2}^{iu} \doteq \begin{cases} (d_{i5} + d_{i4})|i_{i}| & \text{if } i_{i} \leq 0\\ 0 & \text{if } i_{i} \geq 0 \end{cases}$$

$$S_{3}^{iu} \doteq \begin{cases} (d_{i5} + d_{i4} + d_{i3})|i_{i}| & \text{if } i_{i} \leq 0\\ 0 & \text{if } i_{i} \geq 0 \end{cases}$$

$$S_{4}^{iu} \doteq \begin{cases} (d_{i5} + d_{i4} + d_{i3} + d_{i2})|i_{i}| & \text{if } i_{i} \leq 0\\ 0 & \text{if } i_{i} \geq 0 \end{cases}$$

(11)

which represents the averaged current that goes through the device  $S_n^i$  over a switching period. The greater this value, the greater the conducting losses. A well-known approach to estimate the module's lifetime is the Coffin-Manson-Arrhenius model [20] that provides the number of cycles to fail (N). This model highlights the importance of the cycling effect on the lifetime expectancy: the greater the temperature range of the cycle or the maximum reached temperature the smaller the value of N. Consequently, these two parameters would have to be managed to provide thermal management of the devices. To retrieve how  $d_{\gamma j}$  affect them, let us consider that the value of  $d_{\gamma j}$  increases monotonically the value of all duty ratios of level j. Notice that at steady state,

$$u_{\alpha} = \sqrt{\frac{3}{2}}U\cos(\omega t), \quad i_{\alpha} = \sqrt{\frac{3}{2}}I\cos(\omega t + \sigma)$$

$$u_{\beta} = \sqrt{\frac{3}{2}}U\sin(\omega t), \quad i_{\beta} = \sqrt{\frac{3}{2}}I\sin(\omega t + \sigma)$$

$$u_{3,\dots,8} \approx 0 \tag{12}$$

where U, I are the amplitude of the normalized output voltage and the phase currents in *abc* respectively;  $\sigma$  is the phase-shift of the currents; and  $\omega t$ is the grid angle. Also, consider that from (12) and (5)–(10), variables  $d_{\alpha j}$  and  $d_{\beta j}$  for  $j = \{2, 3, 4\}$  are equal to zero. Therefore, from (1) and (11)

$$S_{n}^{i\,u} = \left( T_{\alpha\beta \to i} [d_{\alpha5} \, d_{\beta5}]^{\mathrm{T}} + \sum_{j=\{5,\dots,6-n\}} d_{\gamma j} / \sqrt{3} \right) |i_{i}| \quad (13)$$

$$d_{\alpha 5} = \frac{u_{\alpha}}{4}; \quad d_{\alpha 1} = -\frac{u_{\alpha}}{4} \tag{14}$$

$$d_{\beta 5} = \frac{u_{\beta}}{4}; \quad d_{\beta 1} = -\frac{u_{\beta}}{4}, \tag{15}$$

for  $n = \{1, 2, 3, 4\}$ ,  $i_i \leq 0$  and being  $T_{\alpha\beta\rightarrow i}$ the transformation vector from  $\alpha\beta$  to phase *i*. Hence, the differences in the switching devices usage among phases is highly dependant on the values of the product  $\sum d_{\gamma j} |i_i|$ . On the other hand, the differences in the device usage within the same phase at steady state relies mainly in the  $d_{\gamma j}$  value. The lower its value for level *j*, the more similar the usage for devices inside range n < 6 - j and range  $n \geq 6 - j$ .

According to the studied approaches and the steady state conditions, the value of  $\sum d_{\gamma j} |i_i|$  are:

- Approach 1:

$$\sum_{j=\{5,...,6-n\}} (d_{\gamma j})|i_i| = \sum_{j=\{5,...,6-n\}} (k_{\gamma j})|i_i| \qquad (16)$$

- Approach 2:

$$\sum_{j=\{5,\dots,6-n\}} (d_{\gamma j})|i_i| = \begin{cases} d_{\gamma 5}^{\text{App2}}|i_i| & n \le 2\\ (d_{\gamma 5}^{\text{App2}} + d_{\gamma 3}^{\text{App2}})|i_i| & n > 2 \end{cases}$$

(17)

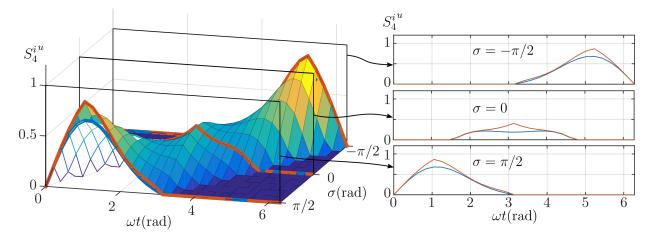

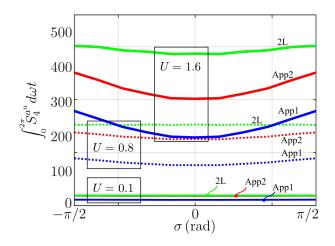

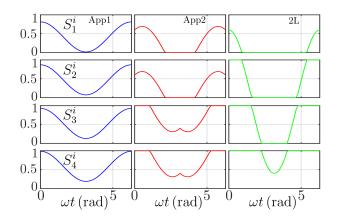

where  $d_{\gamma j}^{\text{App2}}$  is the value of  $d_{\gamma j}$  according to the second approach. Notice that  $d_{\gamma 2}^{\text{App2}} = d_{\gamma 4}^{\text{App2}} = 0$ because of the steady state condition. The values of the first approach depends on the user, but the second ones are retrieved from the approach algorithm. Besides, notice that  $d_{\gamma 3}$  for any approach can be obtained from applying the Clarke transformation to the restriction of  $\sum_{j=1}^{5} d_{ij} = 1$  which results in the condition  $\sum_{j=1}^{5} d_{\gamma j} = \sqrt{3}$ . Therefore, the second approach can be applied at steady state in (17) and, in addition to (16), replaced into (13) to retrieve the general usage for the switching device  $S_n^{i u}$ . For the sake of comparison, the usage of  $S_4^{iu}$ —the most used switching device among the upper ones-will be depicted. Figure 2 shows the value of the usage  $S_4^{i^u}$  when U = 1.60 and normalized current along a grid period and different values of  $\sigma$ . The first approach is depicted as a mesh, while the second one is depicted as a surface. On the other hand, Fig. 3 depicts the results of integrating  $S_4^{i^u}$  over a grid period as a function of  $\sigma$  for different values of U for the first and second approach and also for the two nearest level modulation. Notice that  $\sigma$  is directly related to the power factor as  $PF = cos(\sigma)$ . Such as to picture the different performance of the approaches and the two nearest level modulation, Fig. 4 depicts the duty ratios of each switching device  $S_{1,\ldots,4}^i$ .

It can be seen that the PF barely changes the overall usage and that the first approach offers a lower usage compared to the 2nd approach and two-level modulation. The first being better than the second is due to the minimization of the  $d_{\gamma 5}$  and  $d_{\gamma 1}$  values that reduces the commutations, but increases considerably the value of  $d_{\gamma 3}$  which yields to more conducting time of the devices  $S_3^i$  and  $S_4^i$ . Besides, the bigger the duty ratios of levels 2, 3, 4, the greater the usage for  $S_j^i$  with  $j = \{2, 3, 4\}$  in comparison with  $S_1^i$  which yields in different number of cycles to fail.

#### **IV. SIMULATION RESULTS**

This section will present some results from applying the mentioned approaches into a model. The modulation algorithm is directly extracted from [17] and straightly applied to the model. The simulation parameters and circuit parameters are presented in Table I. To simulate different values of  $\sigma$ , three tests for each approach have been carried out where

Fig. 2. Usage  $S_4^{i^u}$  for U = 1.60 and normalized current along a grid period and different values of  $\sigma$ . Approach 1 is depicted as a mesh (red) while approach 2 is depicted as a surface (blue).

Fig. 3. Integral of the usage over a grid period considering different values of  $\sigma$  and U for the first approach, the second approach and the two nearest level modulation.

Fig. 4. Duty ratios of switching devices  $\{S_1^i, S_2^i, S_3^i, S_4^i\}$  for the first approach (App1), the second approach (App1) and the nearest two level modulation (2L).

the reactive power reference  $(Q^r)$  and the dc-link resistor value (R) change as shown in Table I.

TABLE I SIMULATION AND CIRCUIT PARAMETERS

| Parameter          | Value               | Parameter        | Value                     |

|--------------------|---------------------|------------------|---------------------------|

| L                  | 2 mH                |                  | 3300 µF                   |

| $v_{dc}$           | 800 V               | $v_{\rm grid}$   | 220 V <sub>rms</sub>      |

| $k_{\mathrm{bal}}$ | $2 \cdot 10^{-4}$   | $k_{\gamma 2,4}$ | 0.1                       |

| $k_{\gamma 1,5}$   | $(\sqrt{3}-0.25)/2$ | R                | $[\inf, 43, \inf] \Omega$ |

| $Q^{r}$            | [-25,-10,5] kVA     | $f_{sw}$         | 10 kHz                    |

Similarly, these applied conditions resulted in the values of  $U = \{1.4, 1.47, 1.6\}$  at steady state.

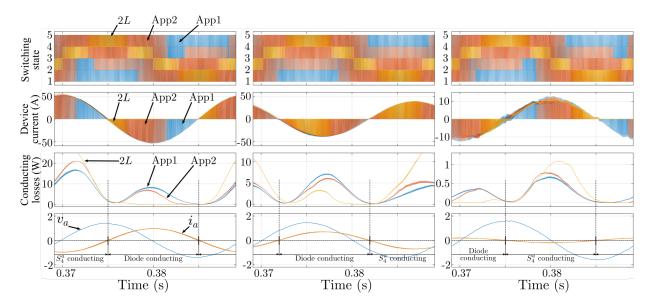

Figure 5 summarizes the results of the simulations where the main differences in the two approaches and the nearest two level modulation can be seen. The switching states are depicted in the first graph where it can be seen that, whereas the Approach 1 (App1) use all level every switching period, Approach 2 (App2) skip some of them. Similarly, the second graph shows the current through  $S_4^a$ including the anti-parallel diode. Notice again that Approach 1 conducts every period, in contrast to Approach 2. However, by looking at the third graph where the conducting losses are depicted according to the integrated IGBT model 5SNA1600N170100, it can be seen that the overall conducting losses are worse for Approach 2 when the current goes through the device  $(i_a \leq 0)$ . Considering this, it can be said that Approach 1 offers a better profile for the conducting losses that, in global terms, will yield less thermal stress for the device. On the other hand, the conducting losses when the current goes through the diode is worse for the Approach 1 than the Approach 2, although diodes has usually

Fig. 5. Simulation results for the two approaches and the two level modulation approach for the three test considered in phase a. Upper graphs show the switching states; upper-mid graphs show the current thorugh the device  $S_4^a$ ; lower-mid graphs show the conducting losses computed in simulation; and lower graphs show the normalized current and output voltage for phase a.

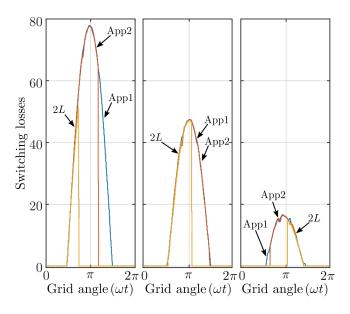

Fig. 6. Switching losses (W) of the approaches considered with a switching frequency of 10 kHz. The turn-on and turn-off energy has been retrieved from the datasheet of model 5SNA1600N170100 at 25 °C.

longer life expectancy and less voltage drop than the switching devices. Therefore, its impact on the equipment life expectancy is less strident. In any case, both approaches offer a better profile for the conducting losses than the two level modulation approach. Not only its integral is smaller but also the conducting losses are more "spread" over a grid period, reducing the thermal cycling effect.

In spite of not considering the switching losses

in the analysis, for the approaches considered here, the first one yields a large number of commutations: 4 transitions per switching period; the second one yields less commutations: between 2 and 4 transitions per period; whereas the nearest two level modulation offers the best performance in this regard: 1 transition per period. Nevertheless, for the sake of comparison, Fig. 6 shows the switching losses of device  $S_4^a$  using the same IGBT model for these approaches under the three tests carried out. It can be seen that two nearest level modulation could cut down the switching losses to a 25% of those of the Approach 1, whereas the second could do so down to 67% depending on the test considered. It is also worth to mention that the two nearest level modulation offers the lowest switching losses but it could not be applied with no modification as it does no tackle the capacitor voltage balance issue. Any other approach which does so will increase the switching losses as more transitions will be inserted. Consequently, once the operating conditions are known, a trade-off comparison between conducting losses and switching losses has to be considered such as to select the more appropriate algorithm.

#### V. CONCLUSIONS

A brief conducting losses analysis of two modulations approaches for grid-connected five-level DCC has been presented in this paper. The results are also compared with the well-known two nearest level modulation approach resulting in one modulation offering the better profile in terms of conducting losses. Not only the overall conducting losses are more reduced but also they are more distributed along a grid period, reducing both the maximum reached temperature and the cycling thermal effect. Because of the dependence to the operating conditions, switching losses were not considered in this analysis but it must no be skipped in a proper thermal design which will result in a trade-off for these modulation approaches.

#### REFERENCES

- [1] J. I. León, S. Kouro, L. G. Franquelo, J. Rodriguez, and B. Wu, "The essential role and the continuous evolution of modulation techniques for voltage-source inverters in the past, present, and future power electronics," *IEEE Transactions on Industrial Electronics*, vol. 63, no. 5, pp. 2688–2701, May 2016.

- [2] A. Ipakchi and F. Albuyeh, "Grid of the future," *IEEE Power and Energy Magazine*, vol. 7, no. 2, pp. 52–62, March 2009.

- [3] F. Blaabjerg, Zhe Chen, and S. B. Kjaer, "Power electronics as efficient interface in dispersed power generation systems," *IEEE Transactions on Power Electronics*, vol. 19, no. 5, pp. 1184–1194, Sep. 2004.

- [4] E. Laloya, O. Lucía, H. Sarnago, and J. M. Burdío, "Heat management in power converters: From state of the art to future ultrahigh efficiency systems," *IEEE Transactions on Power Electronics*, vol. 31, no. 11, pp. 7896–7908, Nov 2016.

- [5] M. Andresen, K. Ma, G. Buticchi, J. Falck, F. Blaabjerg, and M. Liserre, "Junction temperature control for more reliable power electronics," *IEEE Transactions on Power Electronics*, vol. 33, no. 1, pp. 765–776, Jan 2018.

- [6] A. Marquez, J. I. Leon, S. Vazquez, L. G. Franquelo, G. Buticchi, and M. Liserre, "Power device lifetime extension of dcdc interleaved converters via power routing," in *IECON 2018* - 44th Annual Conference of the IEEE Industrial Electronics Society, Oct 2018, pp. 5332–5337.

- [7] I. F. Kovacevic, U. Drofenik, and J. W. Kolar, "New physical model for lifetime estimation of power modules," in *The 2010 International Power Electronics Conference - ECCE ASIA -*, June 2010, pp. 2106–2114.

- [8] T. Herrmann, M. Feller, J. Lutz, R. Bayerer, and T. Licht, "Power cycling induced failure mechanisms in solder layers," in 2007 European Conference on Power Electronics and Applications, Sep. 2007, pp. 1–7.

- [9] N. Baker, M. Liserre, L. Dupont, and Y. Avenas, "Junction temperature measurements via thermo-sensitive electrical parameters and their application to condition monitoring and active thermal control of power converters," in *IECON 2013* - 39th Annual Conference of the IEEE Industrial Electronics Society, Nov 2013, pp. 942–948.

- [10] H. Chen, B. Ji, V. Pickert, and W. Cao, "Real-time temperature estimation for power mosfets considering thermal aging effects," *IEEE Transactions on Device and Materials Reliability*, vol. 14, no. 1, pp. 220–228, March 2014.

- [11] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats, "The age of multilevel converters arrives," *IEEE Industrial Electronics Magazine*, vol. 2, no. 2, pp. 28–39, June 2008.

- [12] T. Bruckner, S. Bernet, and P. K. Steimer, "Feedforward loss control of three-level active npc converters," *IEEE Transactions* on *Industry Applications*, vol. 43, no. 6, pp. 1588–1596, Nov 2007.

- [13] K. Ma and F. Blaabjerg, "Modulation methods for neutral-pointclamped wind power converter achieving loss and thermal redistribution under low-voltage ride-through," *IEEE Transactions* on *Industrial Electronics*, vol. 61, no. 2, pp. 835–845, Feb 2014.

- [14] A. K. Sadigh, V. Dargahi, and K. A. Corzine, "Analytical determination of conduction and switching power losses in flying-capacitor-based active neutral-point-clamped multilevel converter," *IEEE Transactions on Power Electronics*, vol. 31, no. 8, pp. 5473–5494, Aug 2016.

- [15] M. Marchesoni and P. Tenca, "Diode-clamped multilevel converters: a practicable way to balance dc-link voltages," *IEEE Transactions on Industrial Electronics*, vol. 49, no. 4, pp. 752– 765, Aug 2002.

- [16] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A survey on neutral-point-clamped inverters," *IEEE Transactions* on *Industrial Electronics*, vol. 57, no. 7, pp. 2219–2230, July 2010.

- [17] P. Montero-Robina, F. Umbría, F. Salas, and F. Gordillo, "Integrated control of five-level diode-clamped rectifiers," *IEEE Transactions on Industrial Electronics*, vol. 66, no. 9, pp. 6628–6636, Sep. 2019.

- [18] R. Teodorescu, F. Blaabjerg, M. Liserre, and P. C. Loh, "Proportional-resonant controllers and filters for grid-connected voltage-source converters," *IEE Proceedings - Electric Power Applications*, vol. 153, no. 5, pp. 750–762, Sep. 2006.

- [19] S. R. Minshull, C. M. Bingham, D. A. Stone, and M. P. Foster, "Compensation of nonlinearities in diode-clamped multilevel converters," *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2651–2658, Aug 2010.

- [20] H. Cui, "Accelerated temperature cycle test and coffin-manson model for electronic packaging," in *Annual Reliability and Maintainability Symposium*, 2005. Proceedings., Jan 2005, pp. 556–560.