## **Analog-to-Digital Converters for Efficient Portable Devices**

## Memoria presentada por

## **Sohail Asghar**

Para optar al grado de Doctor por la Universidad de Sevilla

Sevilla, Noviembre de 2020

## **Analog-to-Digital Converters for Efficient Portable Devices**

# Memoria presentada por SOHAILASGHAR

## para optar al grado de Doctor por la Universidad de Sevilla

## LOS DIRECTORES

**Dr. José Manuel de la Rosa Utrera**Catedrático de Universidad,

Universidad de Sevilla, Sevilla

España

**Dr. Ivan O' Connell**Principal Investigator,

Microelectronic Circuits Centre

Ireland (MCCI), Cork, Ireland

Departamento de Electrónica y Electromagnetismo UNIVERSIDAD DE SEVILLA

#### **RESUMEN**

La transformación digital en la que se encuentra inmersa nuestra sociedad no hubiese sido posible sin el desarrollo experimentado por la industria de la Microelectrónica. El escalado tecnológico dictado por la ley de Moore ha hecho posible que se puedan integrar en un único chip miles de millones de componentes electrónicos (principalmente transistores) con unas dimensiones que se acercan a la escala de unos cuantos átomos de silicio. Además de los beneficios en términos de coste de producción y prestaciones, el aumento de los niveles de integración ha propiciado que el procesamiento de las señales sea realizado cada vez más por circuitos digitales, ya que éstos obtienen una mejora del rendimiento con el escalado de los procesos de fabricación en comparación con los sistemas electrónicos analógicos.

Una de las consecuencias de esta evolución es que la frontera entre el dominio analógico y el digital se ha ido desplazando con los años cada vez más al punto en el que se sensa o adquiere la información del entorno – como por ejemplo las señales electromagnéticas captadas por una antena en un teléfono móvil – o cualquier otra magnitud física detectada por un sensor de cualquier dispositivo. Todo ello tiene como consecuencia que los circuitos que realizan la transformación analógica a digital o ADC (de *Analog-to-Digital Converter*), sean unos elementos cada vez más esenciales en cualquier dispositivo electrónico. Sin embargo, el diseño de ADC eficientes en tecnologías CMOS nanométricas – más adecuadas para realizar circuitos digitales rápidos que circuitos analógicos precisos – supone afrontar una serie de retos científicotécnicos desde el nivel de abstracción más alto hasta su realización física en un chip de silicio.

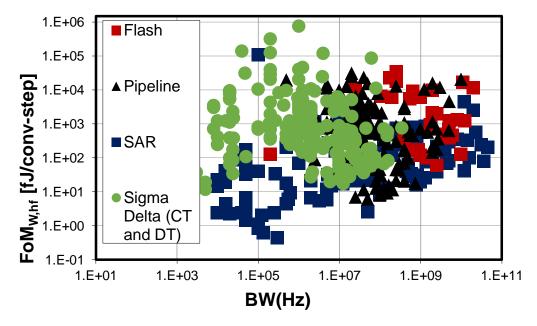

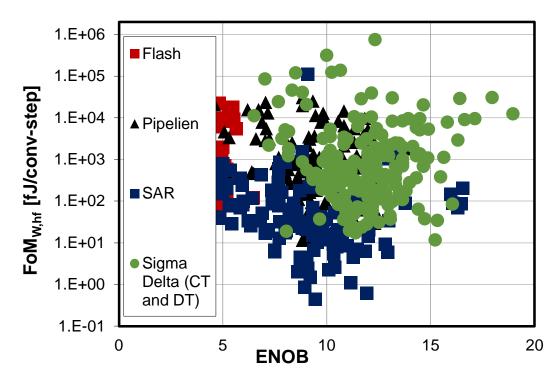

De entre las diversas arquitecturas de ADC, el estado del arte está dominado por diversas técnicas de conversión que son más eficientes en función del ancho de banda de la señal que se necesita digitalizar y la precisión (resolución) de dicha digitalización. De todas ellas, las

denominadas Pipeline, SAR (de *Successive Approximation Register*) y Modulación Sigma-Delta ( $\Sigma\Delta M$ ), o una combinación híbrida de ellas, son las que ofrecen unas mejores métricas de rendimiento. Este proyecto de tesis se centra en el diseño de dos de estos tipos de ADC: SAR y  $\Sigma\Delta M$ , considerando diseños en dos procesos tecnológicos diferentes, con aplicación en comunicaciones inalámbricas y en gestión de circuitos de energía para dispositivos portátiles.

Tras una introducción al contexto de la investigación desarrollada y una descripción de los fundamentos de ADC, se presenta la primera contribución de esta tesis, consistente en el diseño de ADC basados en ΣΔM reconfigurables para aplicaciones de sistemas de comunicación móvil. La primera parte de este estudio aborda los denominados convertidores de radiofrecuencia (RF) a digital, o RF-digital para aplicaciones de radio definida por software (SDR de Software-Defined Radio). Concretamente se presenta el procedimiento de síntesis y diseño a nivel de sistema de un modulador de tipo paso de banda (BP- $\Sigma\Delta M$ ), implementado mediante técnicas de circuito de tiempo continuo, con una frecuencia central es programable de forma continua de 0 a 0.25f<sub>s</sub>, siendo f<sub>s</sub> la frecuencia de muestreo. La arquitectura del modulador es de lazo único con un filtro de tiempo continuo de cuarto orden y un cuantizador de 15 niveles. El lazo de realimentación está formado por un convertidor digital-analógico (DAC) con función de transferencia senoidal implementada con un filtro FIR con un menor número de coeficientes que las mostradas en el estado del arte, lo que facilita su programabilidad, al mismo tiempo que aumenta la robustez y reduce el consumo de potencia con respecto a otras aproximaciones similares. Estas características se combinan con técnicas de submuestreo para lograr una digitalización más robusta y eficiente energéticamente de las señales centradas en 0.455 a 5 GHz, con una resolución efectiva escalable de 8 a 15 bits dentro del ancho de banda de la señal de 0.2 a 30 MHz.

La segunda contribución en el ámbito de ADC de tipo ΣΔM, es un diseño e implementación en una tecnología CMOS de 90nm de un modulador reconfigurable pasobaja/paso-banda (LP/BP) con frecuencia sintonizable, lo que lo hace especialmente apropiado para receptores altamente programables con aplicación en sistemas de comunicación basados en SDR. Los resultados experimentales validan el rendimiento del modulador en un rango de frecuencia de DC a 18 MHz, con una SNDR de 45 a 64 dB dentro de un ancho de banda de señal de 1 MHz, mientras que el consumo de potencia de 22.8-28.8 mW.

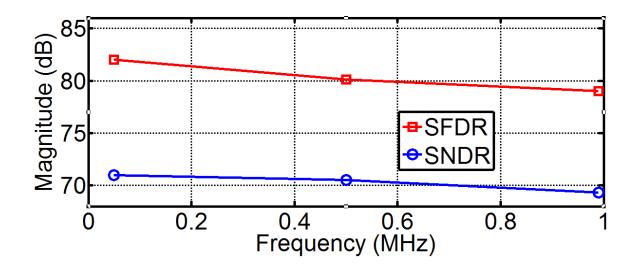

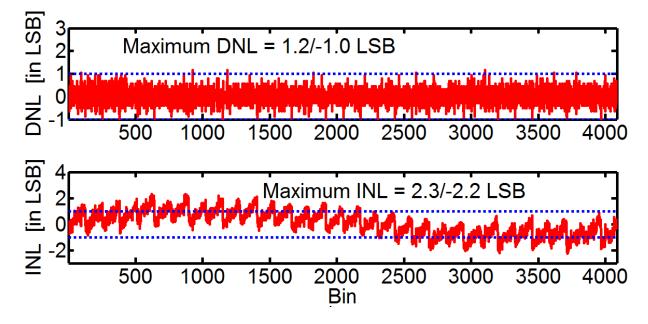

La segunda contribución de esta tesis es un ADC de tipo SAR para su uso en gestión de la potencia de convertidores DC/DC empleados en chips PMIC (de "Power Management Integrated Circuits"). El convertidor que se propone hace uso de dos técnicas desarrolladas en esta tesis doctoral y que dotan a este tipo de circuitos de ventajas en eficiencia energética con respecto al estado del arte. La primera técnica se basa en emplear un rango de entrada que se extiende por encima de la tensión de referencia en un factor de 1.33 V, lo que permite digitalizar señales de 3.2V de amplitud con una referencia de 1.2 V. Además, se propone una técnica de compensación del offset del comparador que no requiere calibración y permite obtener un offset residual de 0.5LSB. El chip ha sido diseñado y fabricado en una tecnología CMOS de 130nm, obteniendo SNDR=69.3 dB, SFDR=79 dB y una linealidad de DNL=1.2/-1.0 LSB, INL=2.3/-2.2LSB, con un consumo de potencia de 0.9mW. Estas prestaciones lo sitúan entre los mejores ADC reportados para este tipo de aplicaciones.

La calidad de la investigación desarrollada en esta tesis ha sido reconocida por la comunidad científica internacional como se demuestra por las publicaciones en diversos foros de IEEE y que se recogen al final de este documento. Entre otras, cabe destacar un artículo en la revista *IEEE Transactions on Circuits and Systems –I: Regular Papers*, con un índice de impacto

de 3.934, situada en el primer cuartil de su categoría en el *Journal Citation Reports* (JCR) en la categoría de *Electrical and Electronic Engineering*.

## **Abstract**

Recent advancements in complementary metal oxide semiconductor (CMOS) process technology and CAD tools for the designs of digital circuits have led to an enormous increase in the processing capabilities of digital signal processors in all types of electronics applications. In order to fully exploit these two advances, more and more signal processing is being shifted to the digital domain. Therefore, all types of electronic applications, ranging from highly sophisticated telecommunications systems and high-end servers to consumer electronics and handheld portable devices, require efficient digitization of the analog signals to enable the subsequent signal processing in the digital domain through the use of analog-to-digital converters (ADCs). As a result of this, new design techniques ranging from architectural to the physical level are required to fully exploit the advancements in the CMOS technology, particularly in smaller geometry nodes. This thesis project focuses on the design of ADCs in CMOS technology for two application areas i.e. wireless communication and power management integrated circuits (PMICs).

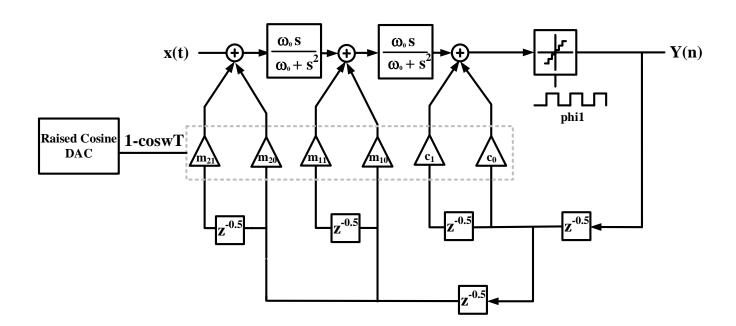

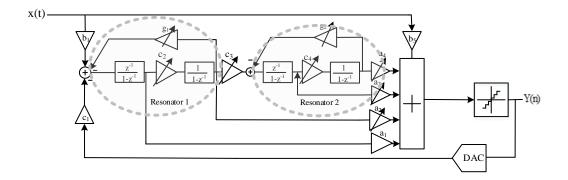

The first part of the thesis deals with two types of sigma delta modulators ( $\Sigma\Delta M$ ) for wireless communication. Initially, a design methodology and modelling of a continuous-time 4<sup>th</sup>-order band-pass (BP)  $\Sigma\Delta M$  for digitizing radio frequency (RF) signals in software-defined-radio (SDR) mobile systems is presented. The modulator architecture comprises two resonators and a 15-level quantiser in the feedforward path and a raised-cosine finite-impulse response (FIR) feedback digital-to-analog converter (DAC). The latter is implemented with a reduced number of filter coefficients as compared to previous approaches, which allows increasing the notch frequency ( $f_N$ ) programmability of an ADC (operating with a sampling frequency of  $f_s$ ) from

0.0375f<sub>s</sub>-to-0.25f<sub>s</sub>. These features are combined with sub-sampling technique to achieve an efficient and robust digitization of 0.455-to-5 GHz signals with scalable 8-to-15 bits effective resolution within 0.2-to-30 MHz signal bandwidth. Following this architecture, the modelling, design and implementation of a switched-capacitor (SC) fourth-order single-loop modulator with a 5-level embedded quantiser is presented. The loop filter in this modulator consists of a cascade of resonator with feedforward (CRFF) coefficients, which can be programmed to make the zeros of the noise transfer function (NTF) variable. As a result, the modulator can be reconfigured either as a low-pass (LP) or band-pass (BP) ADC with a tuneable f<sub>N</sub> and an optimised loop-filter zero placement. The chip has been designed and implemented in a 1.2 V 90-nm CMOS technology. Experimental results validate the performance of the modulator over a frequency range of DC-to-18 MHz, featuring a Signal-to-Noise and Distortion ratio (SNDR) of 45-to-64 dBs within a signal bandwidth of 1 MHz while the power consumption is 22.8-28.8mW.

In the second part of this thesis, a 12-bit successive approximation register (SAR) ADC with an extended input range for a digital controller intended for controllers of DC/DC converter of power management integrated circuits (PMIC) is presented. Employing an input-sampling scaling technique, the presented ADC can digitize the signals with an input range of 3.2  $V_{pp-d}$  ( $\pm 1.33~V_{REF}$ ). The circuit also includes a comparator-offset compensation technique that results in a residual offset of less than 0.5 LSB. The chip has been designed and implemented in a 0.13- $\mu$ m CMOS process and demonstrates the state-of-the-art performance, featuring a SNDR of 69.3 dB and the Spurious Free Dynamic Range (SFDR) of 79 dB without requiring any calibration. Total power consumption of the ADC is 0.9 mW, with a measured differential non-linearity (DNL) of 1.2/–1.0 LSB and integral non-linearity (INL) of 2.3/–2.2 LSB.

## Acknowledgements

This journey has been quite long and daunting and would not have been possible without the support of lot of people. First of all, I am really grateful to my supervisors, Dr. José Manuel de la Rosa Utrera and Dr. Ivan O'Connel for giving me opportunity to work under their supervision. They helped me to develop my thesis with their constructive comments, curiosity and support. At some points, PhD seemed to be an impossible task, but their encouragement and guidance kept me on track. Their patience, dedication and support have been amazing through all the years of PhD.

I am indebted to Professor Rocío del Río Fernández. She provided a lot of supervision during my stay at IMSE, Spain and especially for her support in the design and implementation of my first chip.

Also, special thanks are due to Dr. Alonso Morgado, for his guidance at the start of my PhD. I would also like to appreciate the help of my fellow students and researchers at IMSE, Spain and MCCI, Ireland. During my stay at IMSE, I got lot of support from Gerardo Molina Salgado, Laurentiu Acasandrei, Alberto Villegas, J. Gerardo Garcia and Luis I. Guerrero. I would also like to acknowledge the work of all the people from the IT/CAD, test laboratory and admin at IMSE. My fellow colleagues at MCCI, Anu Pillai, Sohaib Afridi, Girish Waghmare, Kapil, Paolo Scognamiglio, Asfandyar Awan and Alberto Dicataldo provided lot of help during the design/testing phase of the second chip. I really appreciate that. I would also like to acknowledge the support provided by Tony Dunne, John Ryan and Dimo Tonchev from ROHM Powervation, Ireland.

I would like to thank all my friends in Spain, Ireland and Pakistan for the great time that we shared. Particularly, I am thankful to Naveed, Zubair, Oscar, Fransico, Asif, Saquib, Ijaz, Afzal Mand, Qaisar, Farhan, Asfand, Girish, Anu, Waqar Ahmed, Waqas Warraich, Izhaar Bacha, Naved, Waseem, Asad, Kashi, Saeed, Khurram, Muhammad Waqar, Ammad and Nido for all their good wishes, encouragement and support over the last few years.

I want to express my sincere gratitude to my brother Nadeem and his family, Farhat Phupho, my uncle Muhammad Anwar and especially to my wife Laraib and my daughter Ummamah for their unconditional love, support and sacrifices. My parents are no more with me but their role in my life is immense. I dedicate this thesis to the loving memory of my father Ali Asghar and mother Musarrat Bibi.

Most importantly, I am thankful to Allah for my health, life and work.

Sohail Asghar

Cork, Ireland

November 2020

## **Table of Contents**

| Chapter | 1: Introduction                                                                             | 1  |

|---------|---------------------------------------------------------------------------------------------|----|

| 1.1     | Background                                                                                  | 1  |

| 1.2     | Motivation                                                                                  | 2  |

| 1.3     | Thesis Organisation.                                                                        | 6  |

| Chapter | 2: ADCs Background Study                                                                    | 9  |

| 2.1     | Introduction                                                                                | 9  |

| 2.2     | Basic Concepts of ADCs                                                                      | 9  |

| 2.3     | ADC Performance Metrics                                                                     | 13 |

| 2.4     | Nyquist-rate ADCs.                                                                          | 20 |

| 2.5     | Nyquist-rate ADC Architectures                                                              | 22 |

| 2.6     | Oversampled ADCs                                                                            | 26 |

| 2.7     | Figures of Merit                                                                            | 28 |

| 2.8     | Conclusion                                                                                  | 32 |

| Chapter | : 3: ΣΔM ADCs                                                                               | 33 |

| 3.1     | Introduction                                                                                | 33 |

| 3.2     | Working Principle of $\Sigma\Delta M$ ADCs                                                  | 34 |

| 3.3     | Multibit ΣΔM ADCs                                                                           | 44 |

| 3.4     | BP-ΣΔM ADCs                                                                                 | 47 |

| 3.5     | Continuous Time ΣΔM ADCs                                                                    | 50 |

| 3.6     | Timed-Encoded Quantiser Based ΣΔM ADCs                                                      | 54 |

| 3.7     | Conclusion                                                                                  |    |

| Chapter | 24: ΣΔM Based SDR Receivers                                                                 | 57 |

| 4.1     | Introduction                                                                                | 57 |

| 4.2     | Multistandard Receivers                                                                     | 58 |

| 4.3     | BP-ΣΔM ADCs for SDR Based Receivers                                                         | 61 |

| 4.4     | Modulator Specifications                                                                    | 64 |

| 4.5     | Sub-sampling                                                                                | 67 |

| 4.6     | Proposed RF-to-Digital ΣΔM ADC Architecture                                                 | 73 |

| 4.7     | Design Methodology for CT BP- $\Sigma\Delta M$ with Reconfigurable $f_N$ (0-to-0.25 $f_S$ ) | 75 |

| 4.8     | Simulation Results                                                                          | 82 |

| 4.9     | Conclusions                                                                                 | 88 |

| Chanta  | • 5· A 4 <sup>th</sup> -Order Variable Notch Frequency CRFF ΣΑΜ ΑDC                         | 01 |

| 5.1              | Introduction                                                             | 91  |

|------------------|--------------------------------------------------------------------------|-----|

| 5.2              | Modulator Architecture                                                   | 92  |

| 5.3              | Impact of Circuit Errors and High-Level Sizing                           | 98  |

| 5.4              | Parametric Analysis of Op-amps Non-idealities                            | 103 |

| 5.5              | Transistor-Level Design                                                  | 111 |

| 5.6              | Layout Design                                                            | 126 |

| 5.7              | Experimental Characterization                                            | 127 |

| 5.8              | Conclusion                                                               | 137 |

| Chapte<br>Manage | r 6: Design of a 12-Bit SAR ADC with Improved Linearity and O            |     |

| 6.1              | Introduction                                                             |     |

| 6.2              | ADCs for Controller of DC/DC Converters of PMICs                         |     |

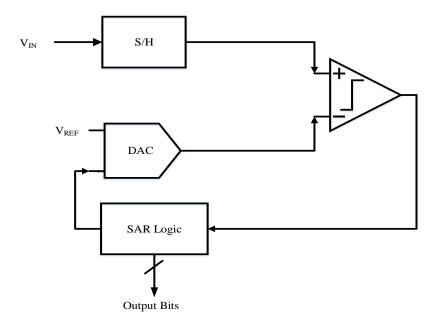

| 6.3              | Basic SAR ADC Operation                                                  |     |

| 6.4              | Design Considerations for SAR ADCs                                       | 145 |

| 6.5              | Background on Linearity Analysis of SAR ADCs                             |     |

| 6.6              | ADC Architecture and Input Scaling                                       | 157 |

| 6.7              | DAC Segmentation for Improved Linearity                                  | 161 |

| 6.8              | Comparator                                                               | 170 |

| 6.9              | ADC Layout                                                               | 173 |

| 6.10             | Experimental Characterization                                            | 177 |

| 6.11             | Conclusion                                                               | 186 |

| Chapte           | r 7: Conclusions and Future Work                                         | 187 |

| 7.1              | Conclusions                                                              | 187 |

| 7.2              | Future Work                                                              | 189 |

| List of          | Publications Derived from this PhD Dissertation                          | 191 |

| Referer          | nces                                                                     | 192 |

| Append           | lices                                                                    | 208 |

| APPI             | ENDIX A                                                                  | 209 |

| Math             | ematica Code for Coefficients of 4th-order CT BP-ΣΔM                     | 209 |

|                  | ENDIX B                                                                  |     |

| Matla            | ab Code for 4 <sup>th</sup> -Order Variable Notch Frequency CRFF ΣΔM ADC | 226 |

# **List of Figures**

| Figure 1.1. Evolution of different wireless communication standards [6]                                    | 2    |

|------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2. Ideal SDR based receiver architecture as proposed in [11].                                     | 4    |

| Figure 1.3. A simplified block level representation of PMIC [20].                                          | 5    |

| Figure 1.4. A digital controller of DC/DC converter with ADC.                                              | 6    |

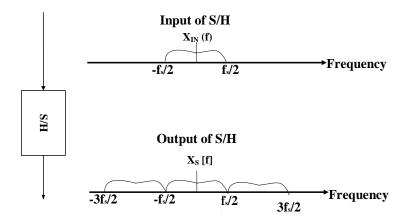

| Figure 2.1. Input and output of an S/H.                                                                    | 10   |

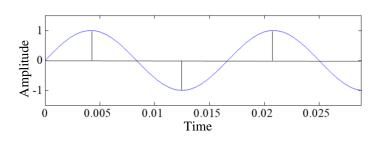

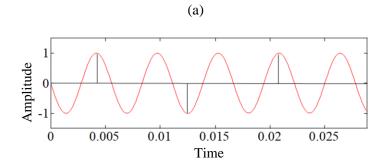

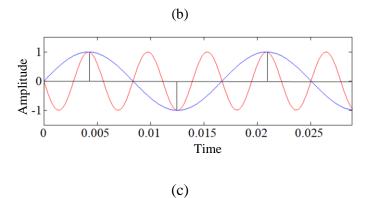

| Figure 2.2. Aliasing due to two sinusoids (a) Input sinusoid at a frequency $f_S/2$ (b) Input sinu         | soid |

| at a frequency $3f_S/2$ and (c) Output of the S/H.                                                         | 10   |

| Figure 2.3. Time and corresponding frequency domain plots of an S/H with a preceding AAF                   | 711  |

| Figure 2.4. (a) Input-output characteristic of a quantiser (b) The corresponding $E_Q$                     |      |

| Figure 2.5. (a) Linear quantiser white noise model and (b) The associated white noise spectra              | ıl   |

| density                                                                                                    |      |

| Figure 2.6. AC performance metrics on a typical SNR curve of a $\Sigma\Delta M$ ADC [28]                   | 14   |

| Figure 2.7. Input-output characteristic of a 3-bit ADC having 1 LSB DNL                                    | 17   |

| Figure 2.8. Input-output characteristic of a 3-bit ADC with INL, shown as cumulative sum of                |      |

| DNL                                                                                                        |      |

| Figure 2.9. Input-output characteristic of a 3-bit ADC having (a) Positive offset (b) Negative             |      |

| offset                                                                                                     |      |

| Figure 2.10. Input-output characteristic of a 3-bit ADC with positive and negative gain error.             |      |

| Figure 2.11. Arrangement of blocks in a Nyquist ADC                                                        |      |

| Figure 2.12. Time and frequency domain plots of signal at different nodes of Nyquist-rate AI               |      |

| (a) Input signal (b) Output of AAF (c) Output of S/H (c) Output of quantiser                               |      |

| Figure 2.13. Flash ADC.                                                                                    |      |

| Figure 2.14. Basic SAR ADC.                                                                                |      |

| Figure 2.15. Pipeline ADC                                                                                  |      |

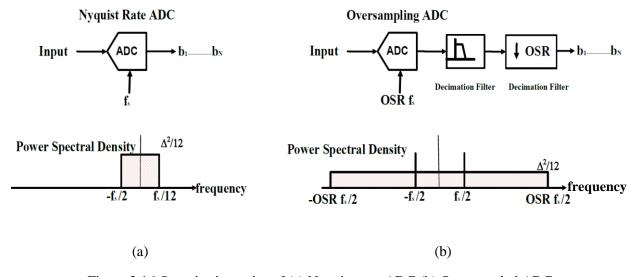

| Figure 2.16.Quantisation noise of (a) Nyquist-rate ADC (b) Oversampled ADC                                 |      |

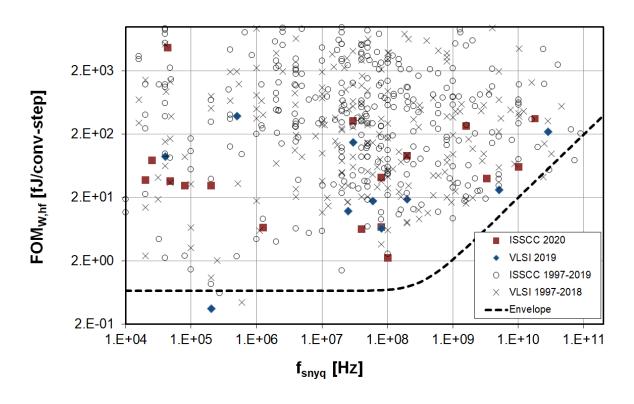

| Figure 2.17. FoM <sub>W</sub> versus DOR for different ADCs published in VLSI and ISSCC [5]                |      |

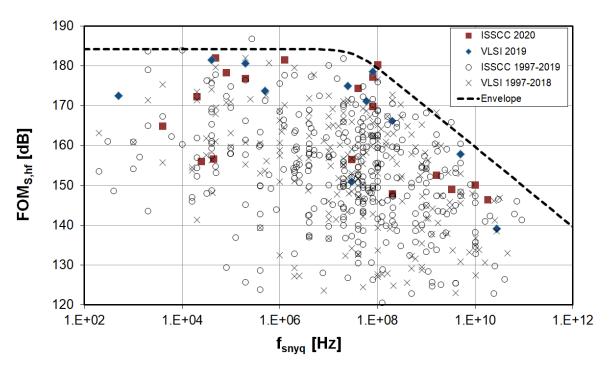

| Figure 2.18. FoMs versus DOR for different ADCs published in VLSI and ISSCC [5]                            |      |

| Figure 2.19. FoM <sub>W</sub> versus BW plot of the reported architectures in [5].                         |      |

| Figure 2.20. FoM <sub>S</sub> versus DR plot of the reported architectures in [5].                         |      |

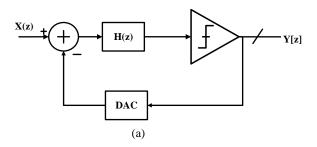

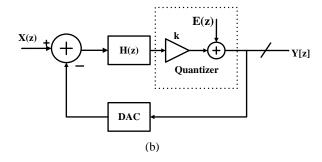

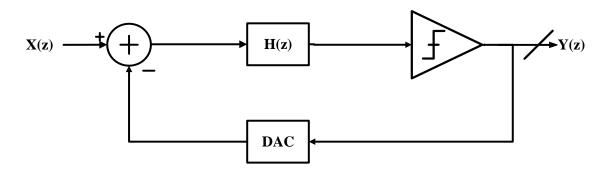

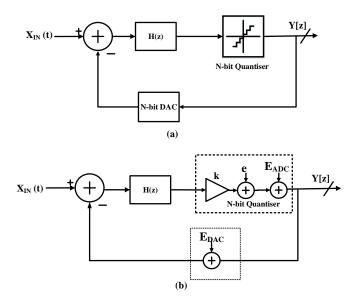

| Figure 3.1. (a) A basic $\Sigma \Delta M$ ADC (b) Linearised model of $\Sigma \Delta M$ ADC                |      |

| Figure 3.2. First-order $\Sigma \Delta M$ .                                                                |      |

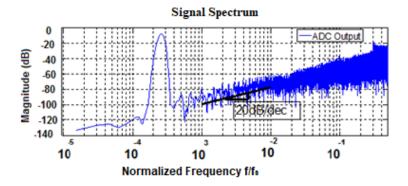

| Figure 3.3. Magnitude spectrum of a first-order $\Sigma\Delta M$ depicting a noise shaping with a slope of | of   |

| 20 dB/dec                                                                                                  | 38   |

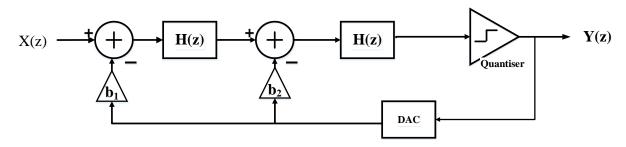

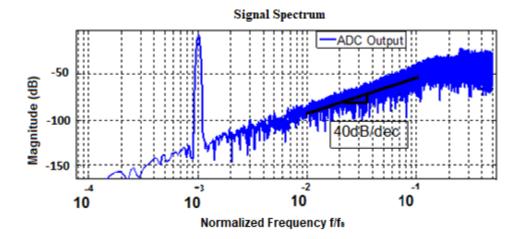

| Figure 3.4. Second-order $\Sigma \Delta M$ .                                                               | 39   |

| Figure 3.5. Magnitude spectrum of a second-order $\Sigma\Delta M$ depicting noise shaping with a slope     | of   |

| 40 dB/dec                                                                                                  |      |

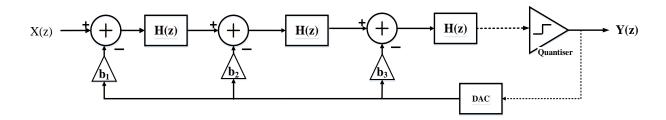

| Figure 3.6. A higher order $\Sigma \Delta M$ .                                                             | 41   |

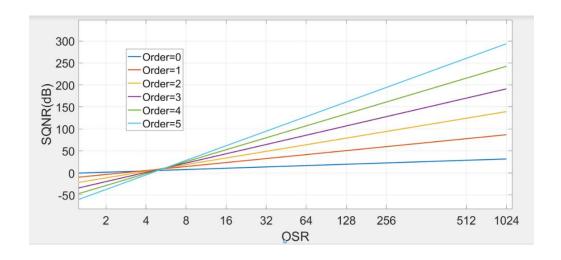

| Figure 3.7. Achievable SQNR <sub>MAX</sub> of a $\Sigma\Delta M$ ADC over a wide range of OSR and order    | 42   |

| Figure 3.8. A 1-1-1 cascaded $\Sigma\Delta M$ .                                                            |      |

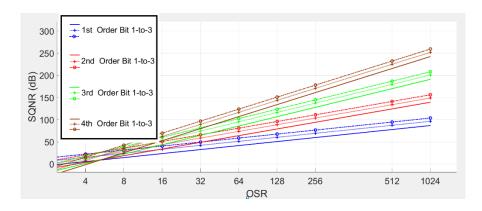

| Figure 3.9. Achievable SONR <sub>MAX</sub> over a range of OSR, order and quantiser bits                   |      |

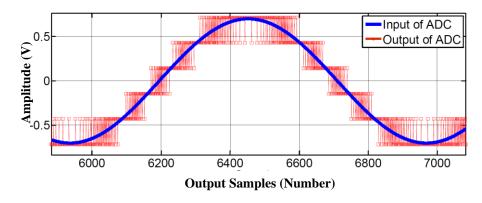

| Figure 3.10. Input and output of first-order of $\Sigma\Delta M$ ADC having multibit quantiser4                                                                             | -5  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.11. (a) A simple model of $\Sigma\Delta M$ ADC having multibit quantiser and DAC (b) Linearise                                                                     | d   |

| model of $\Sigma\Delta M$ ADC with multibit quantiser and DAC4                                                                                                              | -6  |

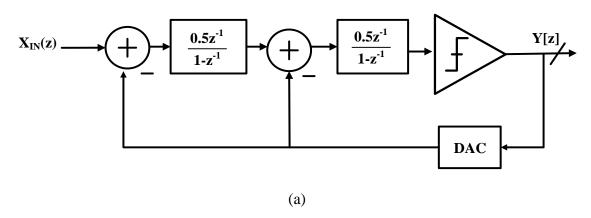

| Figure 3.12 (a) Second-order LP- $\Sigma$ ΔM ADC (b) Equivalent 4 <sup>th</sup> -order BP- $\Sigma$ ΔM ADC4                                                                 | .9  |

| Figure 3.13. Spectrum plots of ADCs outputs (a) A second-order LP-ΣΔM ADC (b) Fourth order                                                                                  |     |

| BP-ΣΔM ADC4                                                                                                                                                                 | 9   |

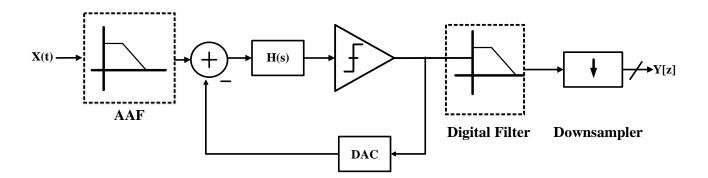

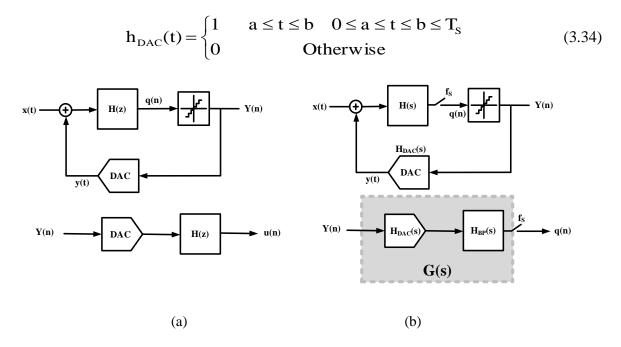

| Figure 3.14. Arrangement of different blocks in a CT-ΣΔM ADC with AAF5                                                                                                      |     |

| Figure 3.15. Loop filter in $\Sigma\Delta Ms$ for (a) DT and (b) CT implementations                                                                                         |     |

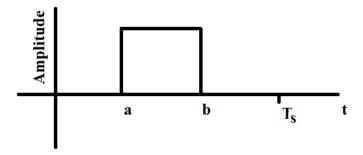

| Figure 3.16. Rectangular shaped DAC waveform5                                                                                                                               |     |

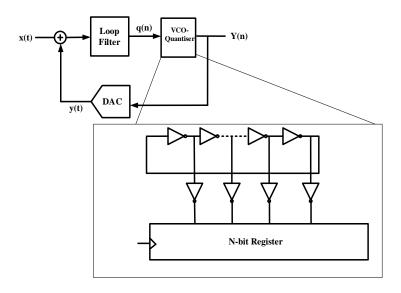

| Figure 3.17. A VCO-quantiser based ΣΔM ADC5                                                                                                                                 |     |

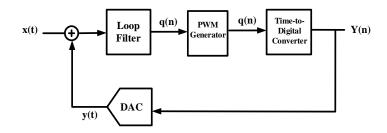

| Figure 3.18. A PWM-quantiser based $\Sigma \Delta M$ ADC                                                                                                                    |     |

| Figure 4.1. Ideal SDR bases receiver architecture as proposed in [11]5                                                                                                      |     |

| Figure 4.2. A direct-conversion multistandard RF receiver                                                                                                                   |     |

| Figure 4.3. A modified version of SDR receiver based on tuneable notch BP ADC6                                                                                              |     |

| Figure 4.4. (a) Input signal at frequency $f_{RF}$ to an ideal S/H operating at $f_S$ (b) Output of the S/H                                                                 |     |

| showing the replicas of the original and image signal6                                                                                                                      | 8   |

| Figure 4.5. (a) Input of BP- $\Sigma\Delta M$ ADC with a centre frequency of 4/5 $f_S$ (b) Output spectrum of                                                               |     |

| BP-ΣΔM ADC with quantisation noise shaping at $f_s/5$ [111]6                                                                                                                |     |

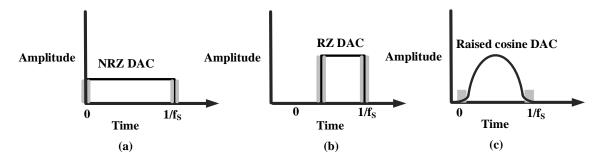

| Figure 4.6. Frequency response of NRZ, RZ and raised-cosine DACs7                                                                                                           | 1   |

| Figure 4.7. Graphical illustration of a sine-shaped DAC (Raised cosine DAC)7                                                                                                | 1   |

| Figure 4.8. Illustration of timing jitter on 3 types of DACs (a) NRZ DAC (b) RZ DAC and (c)                                                                                 |     |

| Raised cosine DAC                                                                                                                                                           | 1   |

| Figure 4.9. A 4 <sup>th</sup> -order CT BP-ΣΔM ADC7                                                                                                                         | 4   |

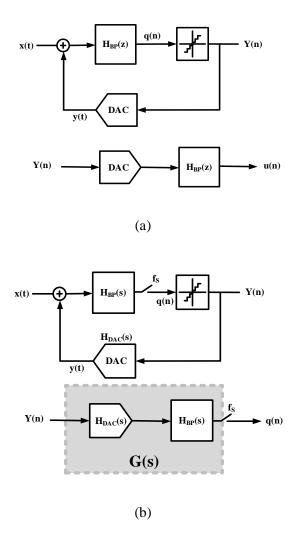

| Figure 4.10. Loop filter in $\Sigma\Delta M$ for (a) DT implementation (b) CT implementation                                                                                | 8   |

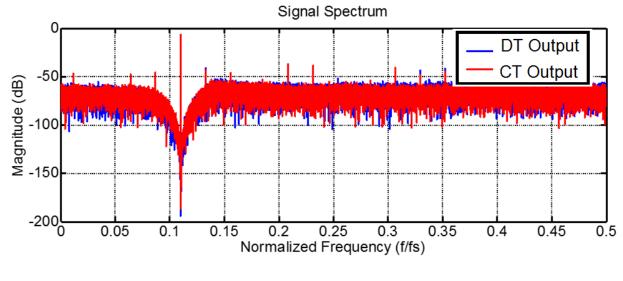

| Figure 4.11. CT-to-DT transformation at three different notch frequencies (a) $0.12f_S$ (b) $0.2f_S$ (c)                                                                    | )   |

| $0.25f_{S}$ 8                                                                                                                                                               |     |

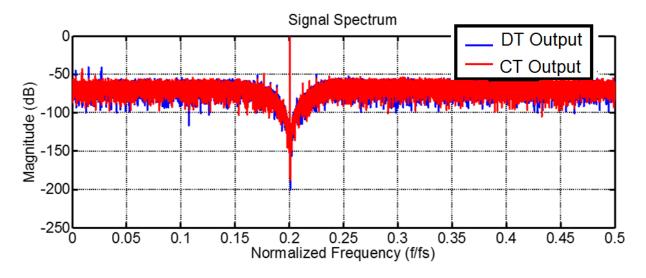

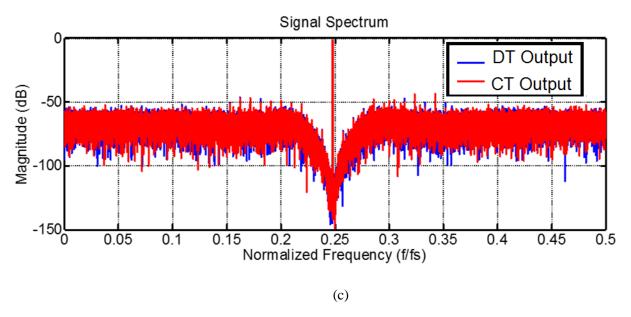

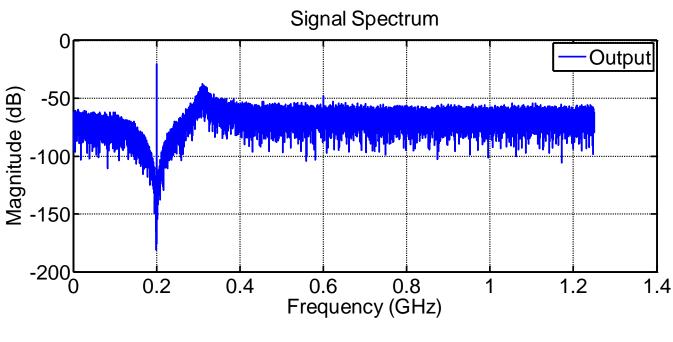

| Figure 4.12. Modulator output spectra for the different cases of $f_{RF}$ and $f_{S}$ (a) $f_{RF}$ = 0.44 GHz, $f_{S}$                                                      | =   |

| 2 GHz (normal mode) (b) $f_{RF} = 2.14$ GHz, $f_S = 1$ GHz (sub-sampling mode) and (c) $f_{RF} = 1$                                                                         |     |

| $5.2 \text{ GHz}, \text{ f}_{S} = 2.5 \text{ GHz} \text{ (sub-sampling mode)}.$                                                                                             |     |

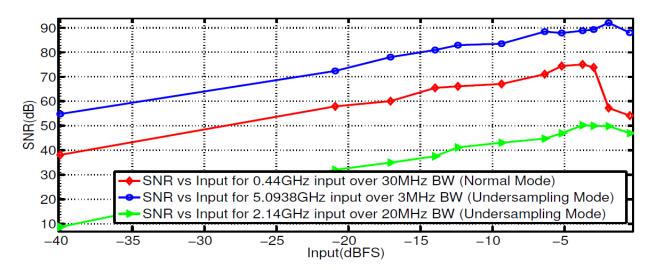

| Figure 4.13. SNR vs. input for different cases of $f_{RF}$ and $f_{S}$ ( $f_{RF}$ = 0.44GHz, $f_{S}$ = 2GHz (normal                                                         |     |

| mode), $f_{RF} = 2.14$ GHz, $f_S = 1$ GHz (sub-sampling mode) and $f_{RF} = 5.2$ GHz, $f_S = 2.5$ GHz                                                                       | . – |

| (sub-sampling mode))                                                                                                                                                        | , / |

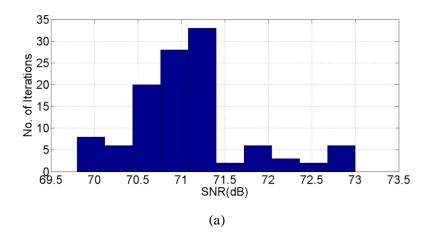

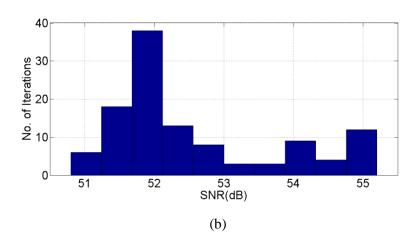

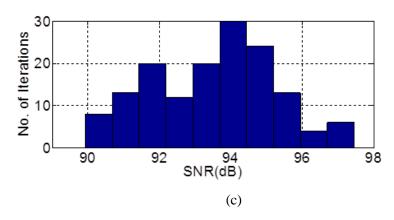

| Figure 4.14. SNR histograms for the different cases of $f_{RF}$ and $f_{S}$ (a) $f_{RF} = 0.44$ GHz, $f_{S} = 2$ GHz                                                        |     |

| (normal mode) (b) $f_{RF} = 2.14 \text{GHz}$ , $f_S = 1 \text{GHz}$ (sub-sampling mode) and (c) $f_{RF} = 5.2 \text{ GHz}$ , $f_{RF} = 2.5 \text{ GHz}$ (sub-sampling mode) |     |

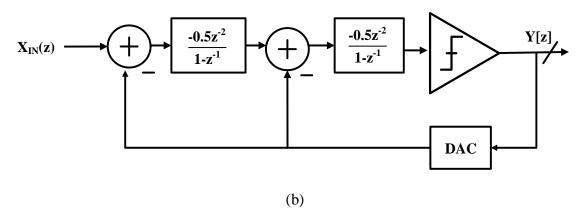

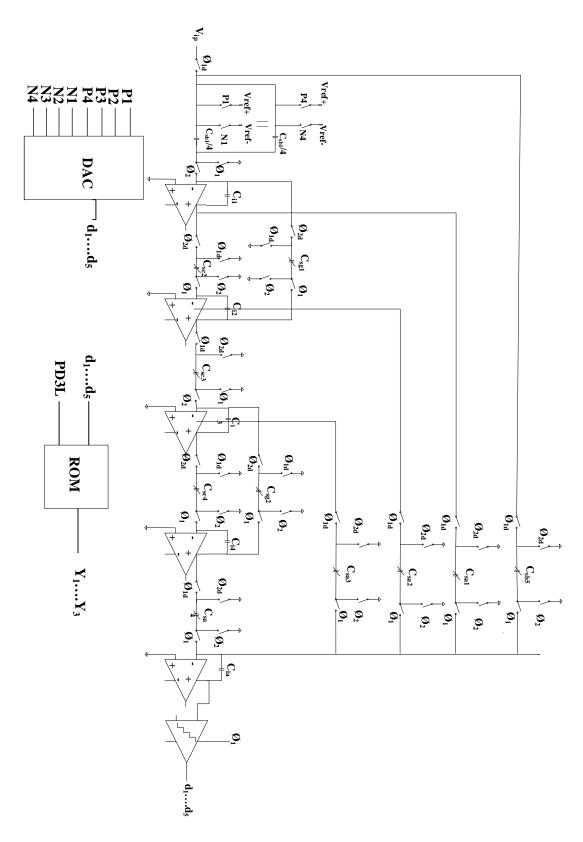

| $f_S = 2.5 \text{ GHz} \text{ (sub-sampling mode)}.$ Figure 5.1. Reconfigurable 4 <sup>th</sup> -order CRFF $\Sigma \Delta M$ architecture.                                 |     |

| Figure 5.1. Reconfigurable 4 -order CRFF 2/2M architecture                                                                                                                  |     |

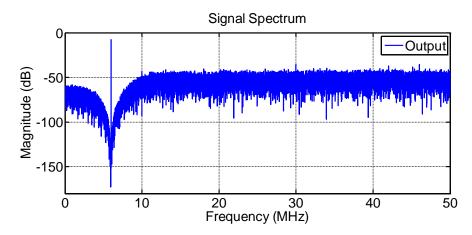

| in the LP-mode ( $f_S = 100 \text{ MHz}$ )9                                                                                                                                 | _   |

| Figure 5.3. Output spectrum plot with $f_N = 3$ MHz for ideal model with the ADC operating in the                                                                           |     |

| BP-mode ( $f_S = 100 \text{ MHz}$ )9                                                                                                                                        |     |

| Figure 5.4. Output spectrum plot with $f_N = 6$ MHz for ideal model with the ADC operating in th                                                                            |     |

| BP-mode ( $f_S = 100 \text{ MHz}$ ).                                                                                                                                        |     |

| Figure 5.5. Output spectrum plot with $f_N = 9$ MHz for ideal model with the ADC operating          | in the |

|-----------------------------------------------------------------------------------------------------|--------|

| BP-mode (f <sub>S</sub> = 100 MHz).                                                                 | 96     |

| Figure 5.6. Output spectrum plot with $f_N = 12$ MHz for ideal model with the ADC operating         | g in   |

| the BP-mode ( $f_S = 100 \text{ MHz}$ )                                                             | 97     |

| Figure 5.7. Output spectrum plot with $f_N = 15$ MHz for ideal model with the ADC operating         | g in   |

| the BP-mode ( $f_S = 100 \text{ MHz}$ )                                                             | 97     |

| Figure 5.8. Output spectrum plot with $f_N = 18$ MHz for ideal model with the ADC operating         | g in   |

| the BP-mode ( $f_S = 100 \text{ MHz}$ )                                                             | 97     |

| Figure 5.9. Output spectrum plot with $f_N = 22$ MHz for ideal model with the ADC operating         | g in   |

| the BP-mode ( $f_S = 100 \text{ MHz}$ )                                                             | 98     |

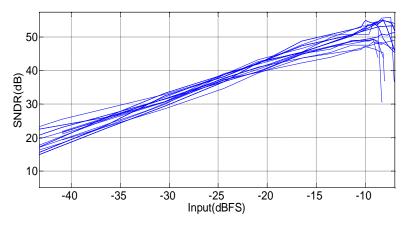

| Figure 5.10. SNDR vs. input amplitude for a bandwidth of 1 MHz and $f_{\rm N}$ from 0 to 44 MHz     | Z      |

| (while employing $f_S$ = 100 MHz for the tuning range $f_N$ = 0-to-22 MHz and $f_S$ = 200 MHz       | Hz     |

| over the tuning range $f_N = 23$ -to-44 MHz).                                                       | 98     |

| Figure 5.11. Conceptual SC schematic of the loop filters and adder in the proposed $\Sigma\Delta M$ | 99     |

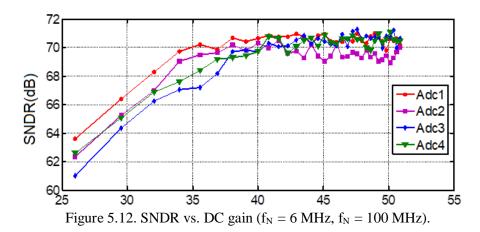

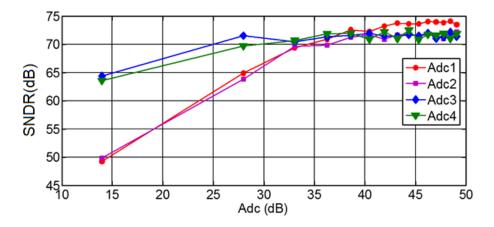

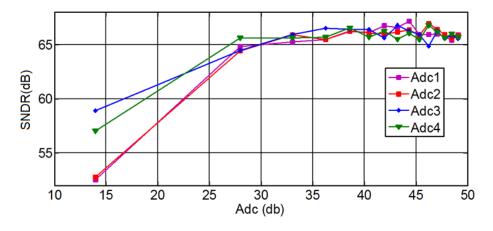

| Figure 5.12. SNDR vs. DC gain ( $f_N = 6$ MHz, $f_N = 100$ MHz)                                     | 105    |

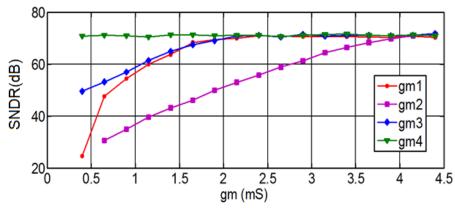

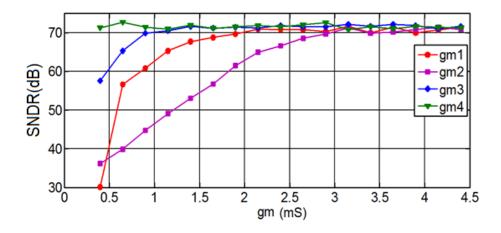

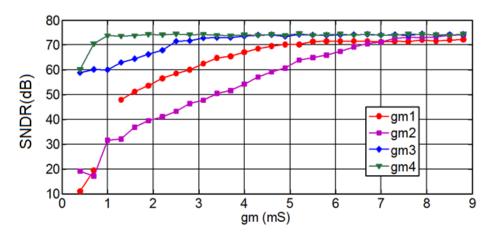

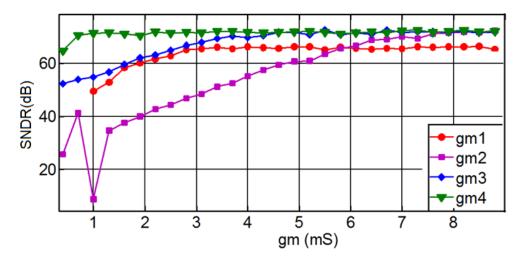

| Figure 5.13. SNDR vs. transconductance ( $f_N = 6$ MHz, $f_N = 100$ MHz)                            | 106    |

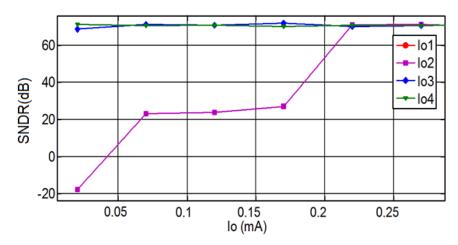

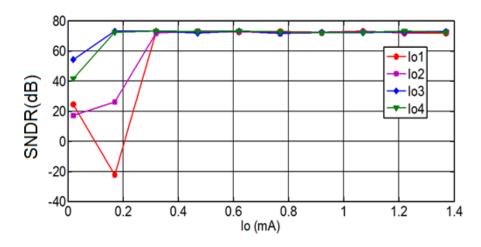

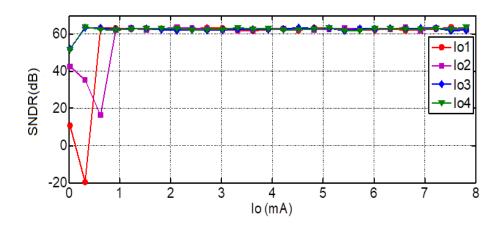

| Figure 5.14. SNDR vs. output current ( $f_N = 6$ MHz, $f_N = 100$ MHz)                              | 106    |

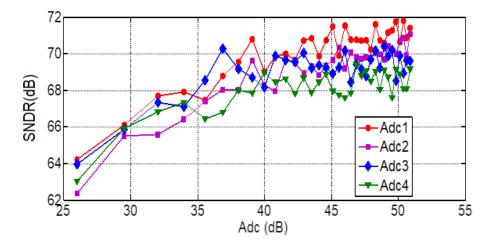

| Figure 5.15. SNDR vs. DC gain ( $f_N = 22$ MHz, $f_N = 100$ MHz)                                    | 106    |

| Figure 5.16. SNDR vs. transconductance ( $f_N = 22$ MHz, $f_N = 100$ MHz)                           | 107    |

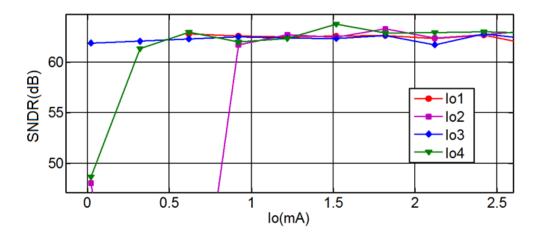

| Figure 5.17. SNDR vs. output current ( $f_N = 22$ MHz, $f_N = 100$ MHz).                            |        |

| Figure 5.18. SNDR vs. DC gain ( $f_N = 30$ MHz, $f_S = 200$ MHz)                                    |        |

| Figure 5.19. SNDR vs. transconductance ( $f_N = 30 \text{ MHz}$ , $f_S = 200 \text{ MHz}$ )         |        |

| Figure 5.20. SNDR vs. output current ( $f_N = 30 \text{ MHz}$ , $f_S = 200 \text{ MHz}$ )           | 109    |

| Figure 5.21. SNDR vs. DC gain ( $f_N = 36 \text{ MHz}$ , $f_S = 200 \text{ MHz}$ )                  | 109    |

| Figure 5.22. SNDR vs. transconductance ( $f_N = 36$ MHz, $f_S = 200$ MHz)                           | 110    |

| Figure 5.23. SNDR vs. output current ( $f_N = 36$ MHz, $f_S = 200$ MHz)                             | 110    |

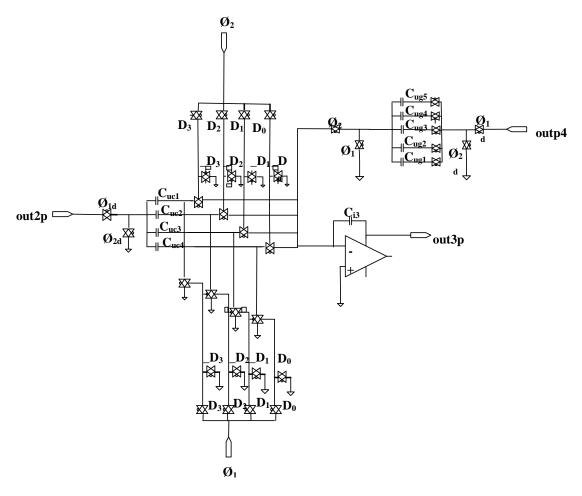

| Figure 5.24. Single-ended version of a $4^{th}$ -order SC $\Sigma\Delta M$ .                        | 113    |

| Figure 5.25. Switched capacitor implementation of the third integrator.                             | 115    |

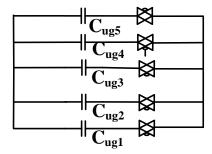

| Figure 5.26. Implementation of variable resonance capacitor ( $C_{sg1}$ and $C_{sg2}$ )             | 115    |

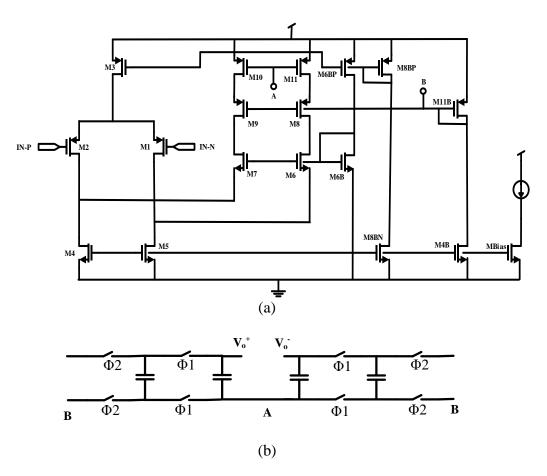

| Figure 5.27. Folded cascode op-amp: (a) Core op-amp (b) SC common-mode feedback net                 | work.  |

|                                                                                                     |        |

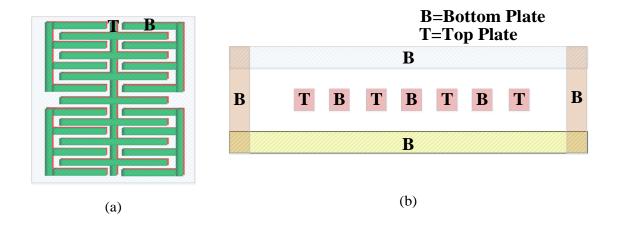

| Figure 5.28. Arrangement of top and bottom plates in MOM capacitors.                                |        |

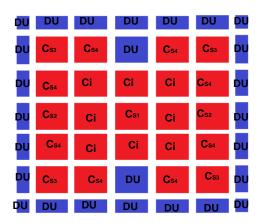

| Figure 5.29. Common centroid arrangement of capacitors in 4 <sup>th</sup> integrator.               |        |

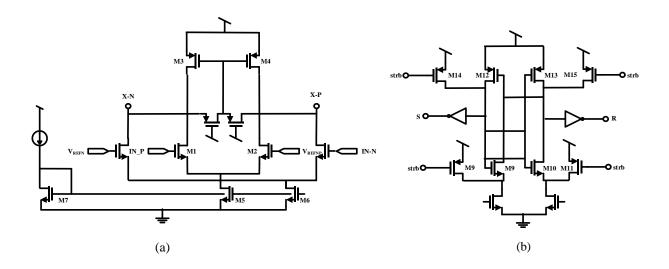

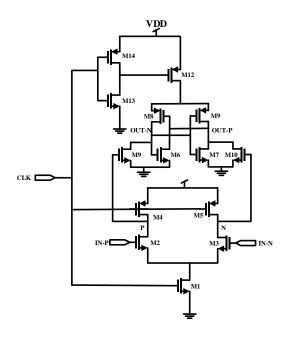

| Figure 5.30.Comparator schematic (a) Pre-amplifying stage (b) Regenerative latch                    |        |

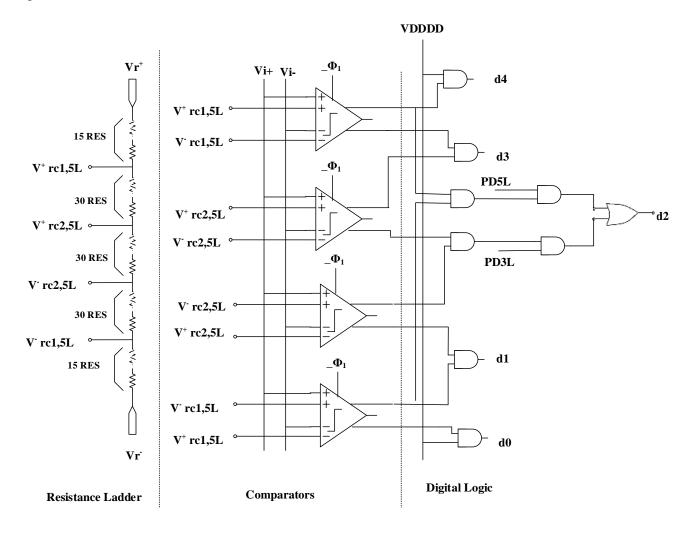

| Figure 5.31. Resistance ladder, quantiser and digital logic.                                        |        |

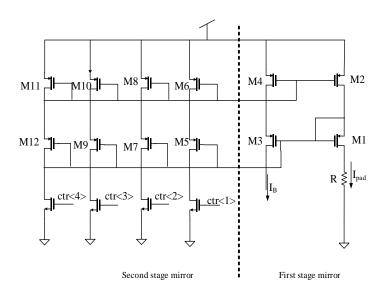

| Figure 5.32. Master biasing circuit.                                                                |        |

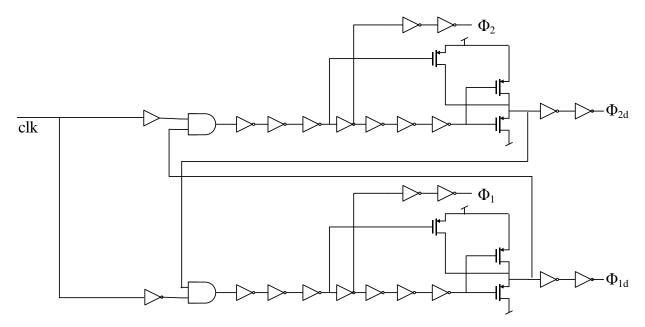

| Figure 5.33. Clock phase generator schematic.                                                       |        |

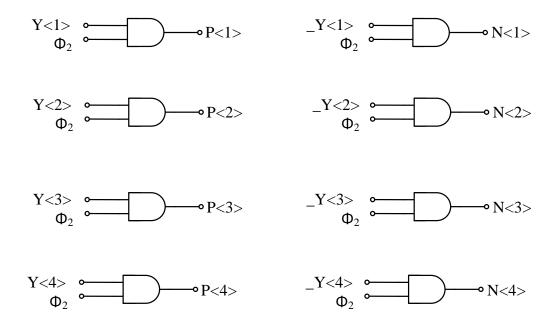

| Figure 5.34. DAC control signals configuration.                                                     |        |

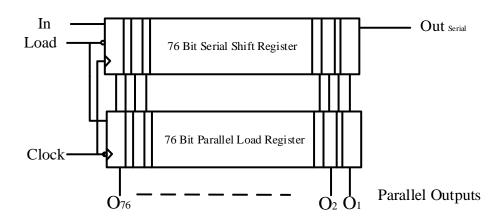

| Figure 5.35. Block diagram of the serial-in parallel-out register                                   |        |

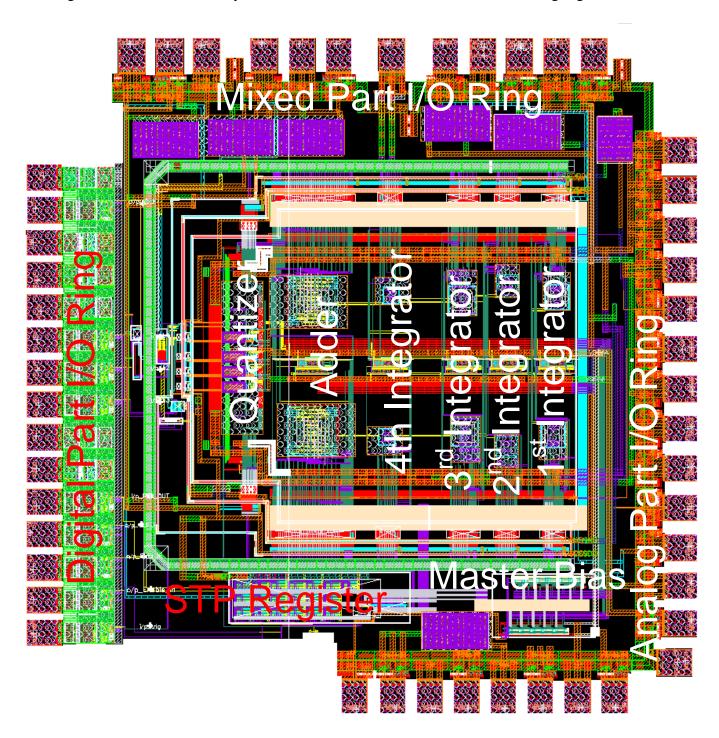

| Figure 5.36. Layout of whole $\Sigma \Delta M$ ADC with different blocks being highlighted          |        |

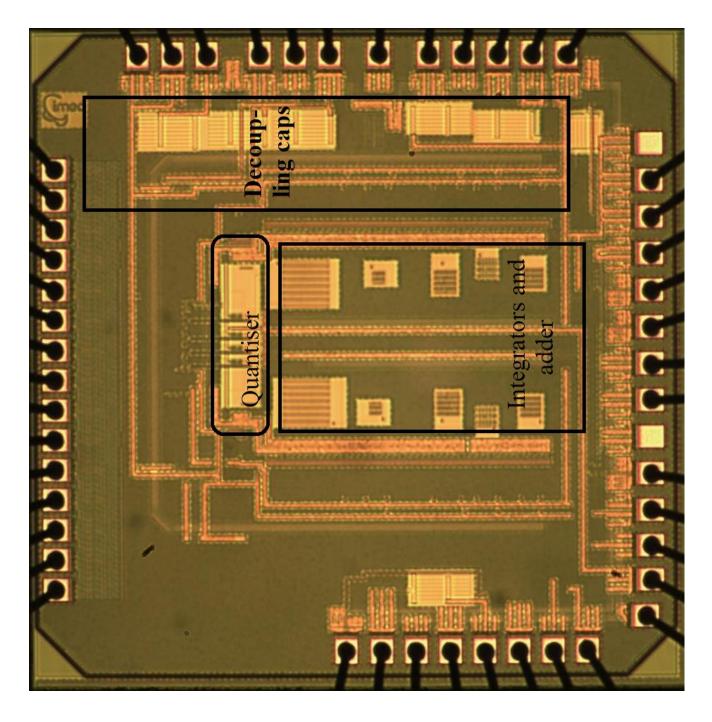

| Figure 5.37. Micrograph of the fabricated ADC.                                                      |        |

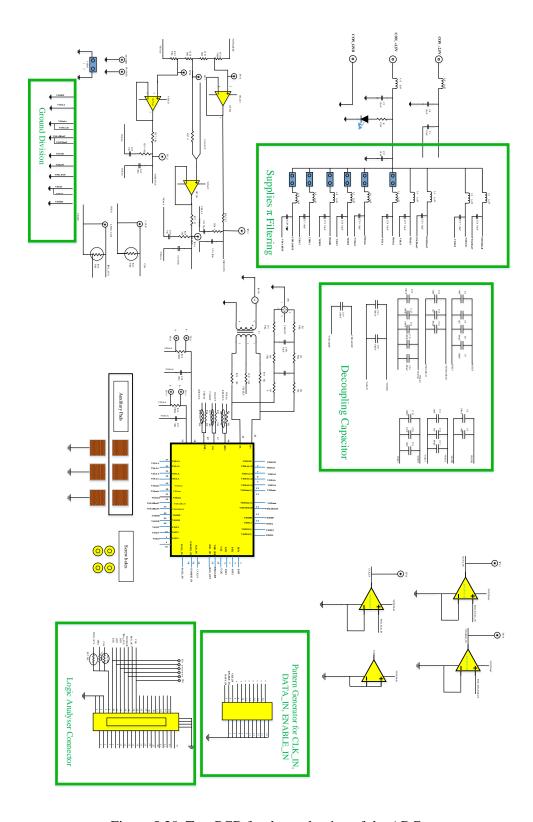

| Figure 5.38. Test PCB for the evaluation of the ADC.                                                |        |

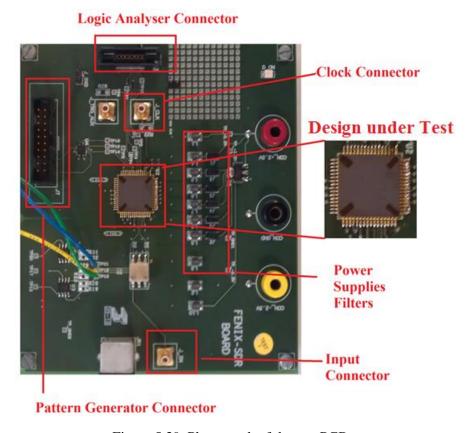

| Figure 5.39. Photograph of the test PCB                                                             | 131    |

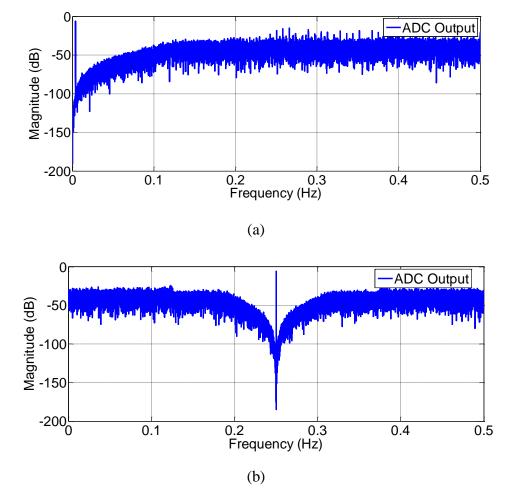

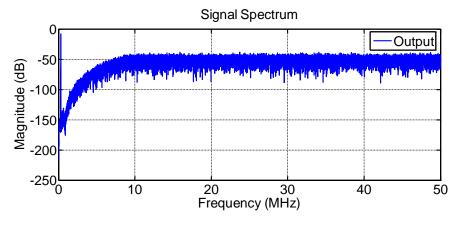

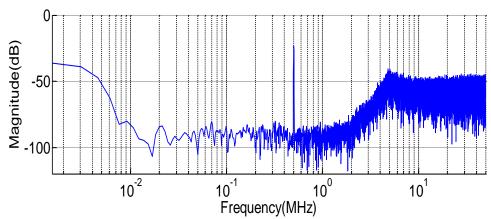

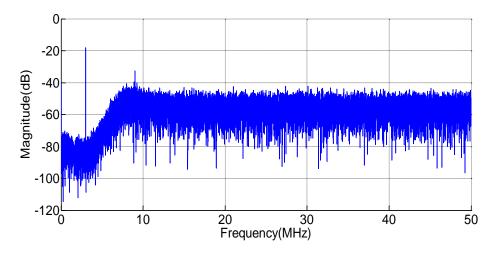

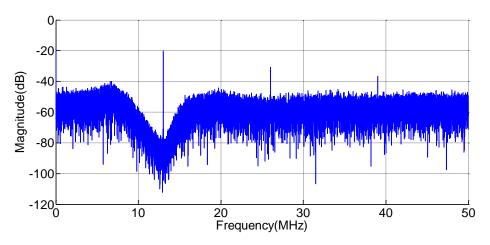

| Figure 5.40. Spectrum plot for LP configuration.                                                                        | .132 |

|-------------------------------------------------------------------------------------------------------------------------|------|

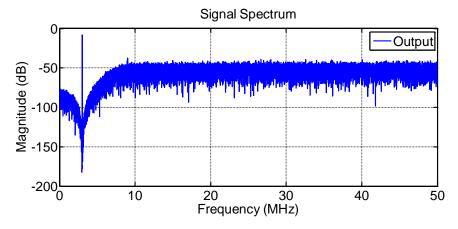

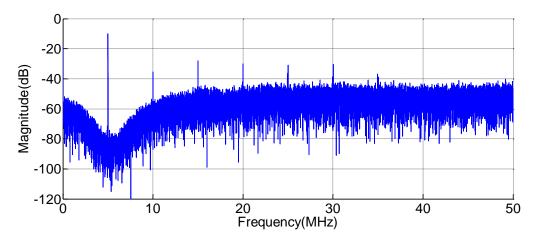

| Figure 5.41. Spectrum plot at $f_N = 3$ MHz.                                                                            | .132 |

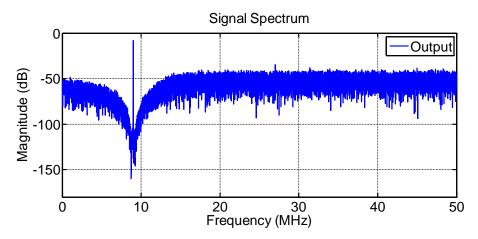

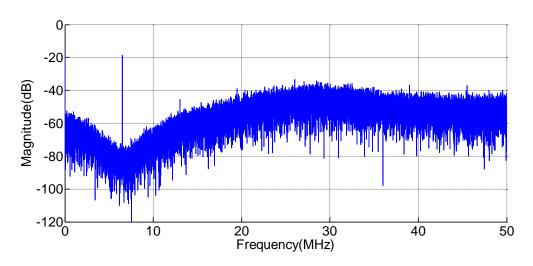

| Figure 5.42. Spectrum plot at $f_N = 5$ MHz.                                                                            | .133 |

| Figure 5.43. Spectrum plot at $f_N = 6$ MHz.                                                                            | .133 |

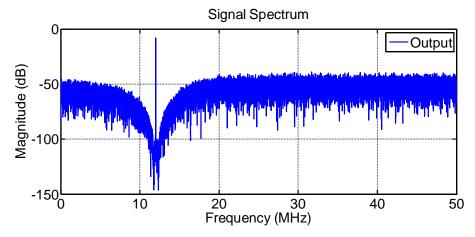

| Figure 5.44. Spectrum plot at $f_N = 9$ MHz.                                                                            | .133 |

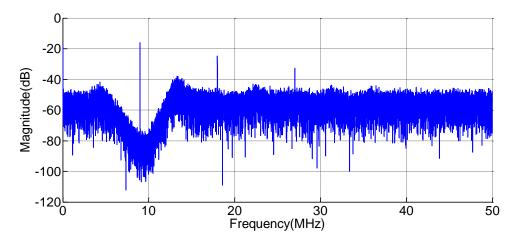

| Figure 5.45. Spectrum plot at $f_N = 13$ MHz                                                                            | .134 |

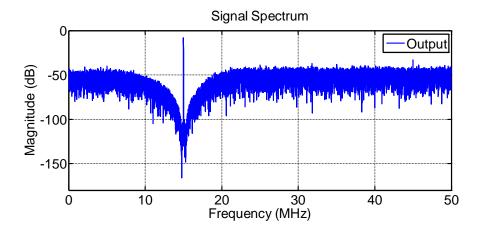

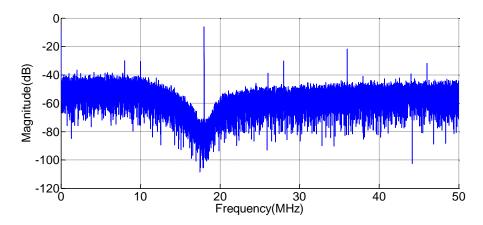

| Figure 5.46. Spectrum plot at $f_N = 18$ MHz                                                                            | .134 |

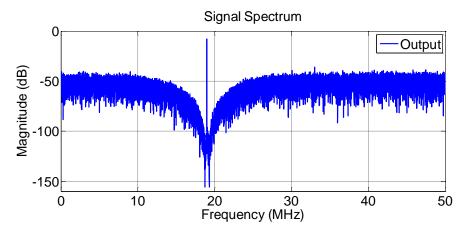

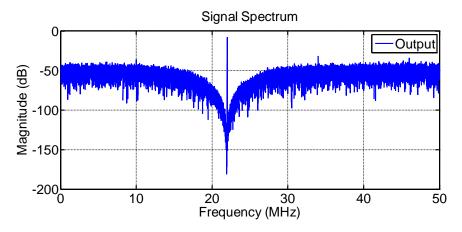

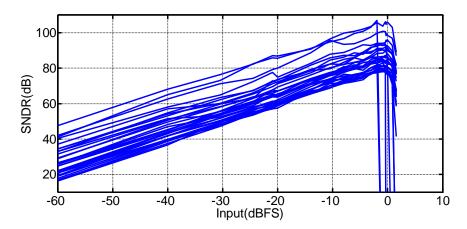

| Figure 5.47.SNDR vs. input for a BW of 1MHz at $f_N = 100$ kHz-to-18 MHz                                                | .134 |

| Figure 6.1. A digital controller of DC/DC converter with ADC.                                                           | .140 |

| Figure 6.2. Basic SAR ADC.                                                                                              |      |

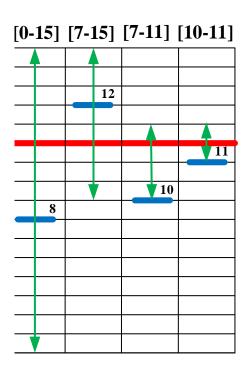

| Figure 6.3. 4-bit binary search algorithm in SAR ADC                                                                    | .144 |

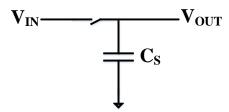

| Figure 6.4. A basic S/H circuit.                                                                                        | .145 |

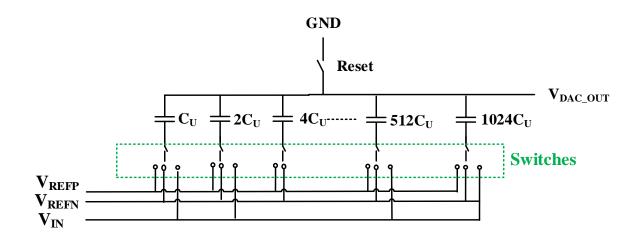

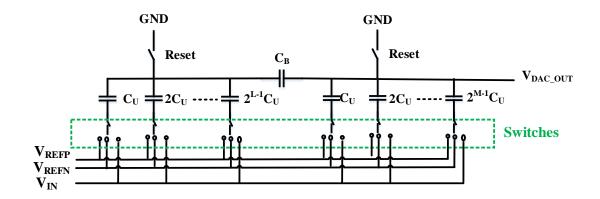

| Figure 6.5. A single-ended schematic of CBW DAC.                                                                        | .148 |

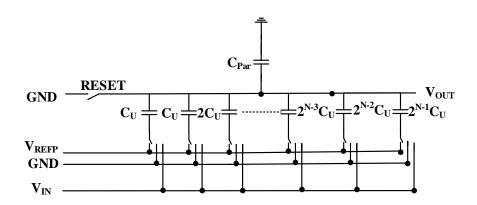

| Figure 6.6. A single-ended schematic of BWA DAC.                                                                        |      |

| Figure 6.7. Parasitic capacitance in CBW DAC.                                                                           | .152 |

| Figure 6.8. Parasitic capacitance in BWA DAC.                                                                           | .153 |

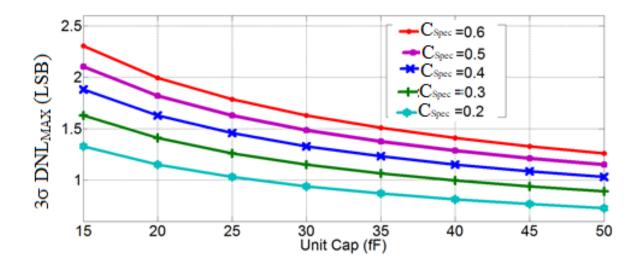

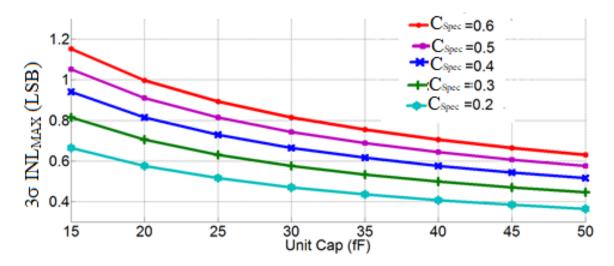

| Figure 6.9. 3σ DNL <sub>MAX</sub> incurred for BWA DAC based SAR ADC over a range of C <sub>U</sub> and C <sub>sp</sub> |      |

|                                                                                                                         |      |

| Figure 6.10. $3\sigma$ INL <sub>MAX</sub> incurred for BWA DAC based SAR ADC over a range of $C_U$ and $C_{st}$         | nec• |

| <i>y</i>                                                                                                                |      |

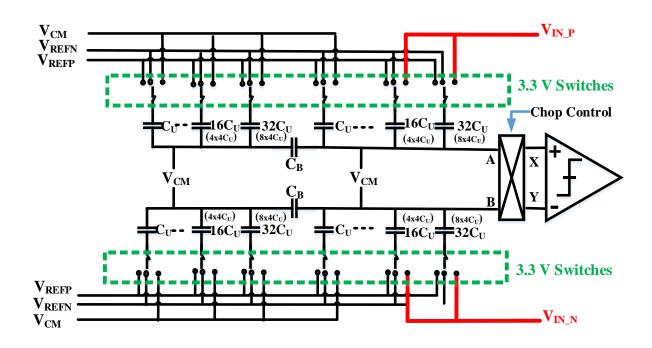

| Figure 6.11. Proposed 6-6 BWA 12-bit SAR ADC architecture with input scaling                                            | .158 |

| Figure 6.12. Sampling of the input voltage.                                                                             |      |

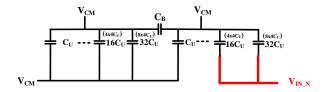

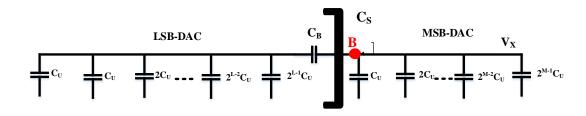

| Figure 6.13. Simplified schematic of SE DAC of the SAR ADC.                                                             |      |

| Figure 6.14. MOM Capacitor (a) Top view (b) Cross-sectional view                                                        |      |

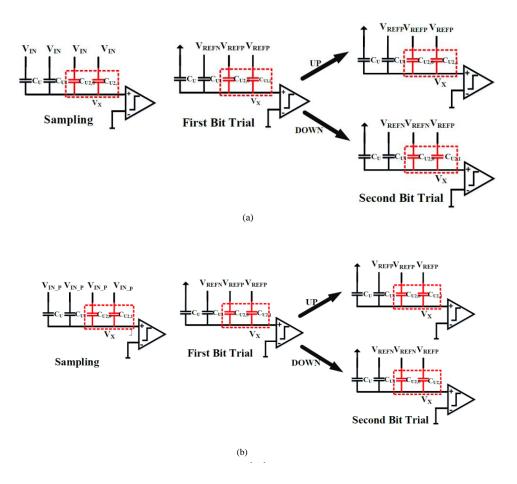

| Figure 6.15. 2-bit SAR ADC operation with (a) Normal DAC (b) Segmentation DAC                                           |      |

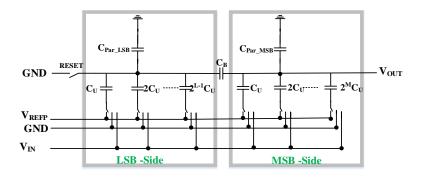

| Figure 6.16. BWA DAC consisting of M and L numbers of bits in the MSB and LSB-DACs                                      |      |

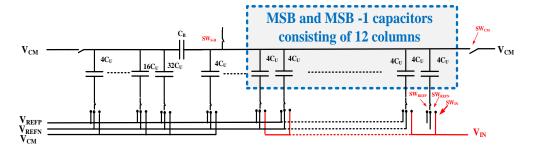

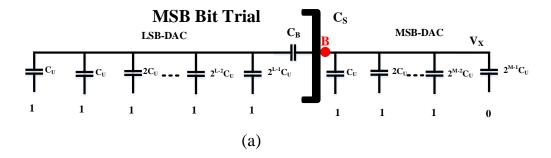

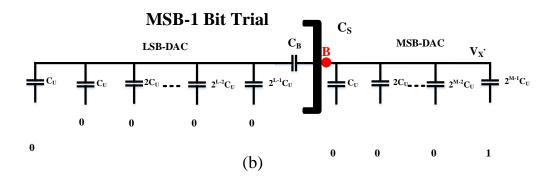

| Figure 6.17. Capacitor states during (a) MSB-bit trial (b) MSB-1 bit trial                                              |      |

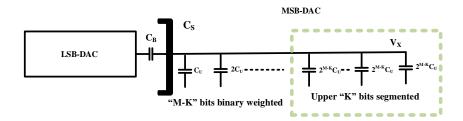

| Figure 6.18. Segmented MSB-DAC where upper K bits in MSB-DAC are segmented                                              |      |

| Figure 6.19. Code transition where maximum number of capacitors in segmentation DAC cha                                 |      |

| their state (a) Before transition (b) After transition.                                                                 | _    |

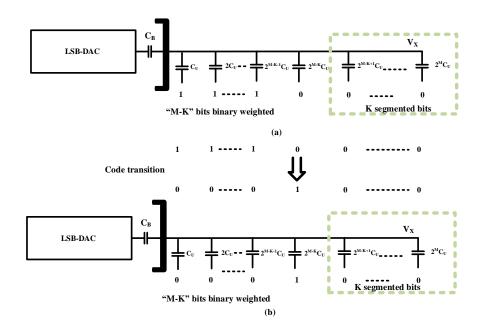

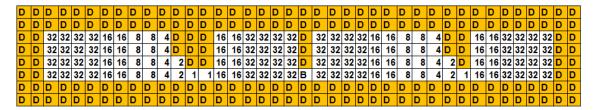

| Figure 6.20. Layout of 12-bit DAC to facilitate the segmentation.                                                       |      |

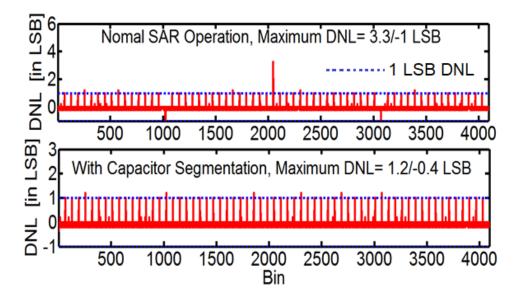

| Figure 6.21. DNL plots of 12 SAR ADC, 0.81% mismatch in MSB and MSB-1 in 6-6 BWA                                        |      |

| based SAR ADC with conventional and segmented DACs.                                                                     | .169 |

| Figure 6.22. Double-tail latch comparator.                                                                              |      |

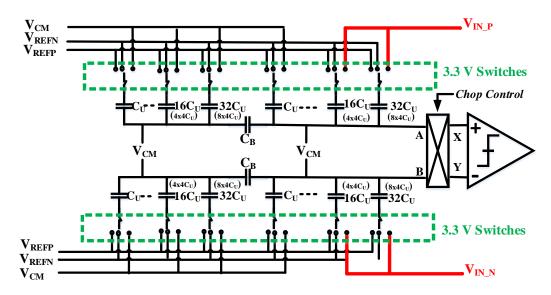

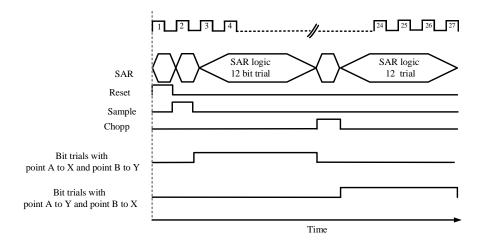

| Figure 6.23. Full schematic of ADC with chopping in front of comparator                                                 |      |

| Figure 6.24. ADC operation sequence in offset-calculation.                                                              |      |

| Figure 6.25. Pseudo-random arrangement of capacitors.                                                                   |      |

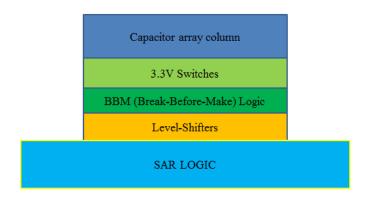

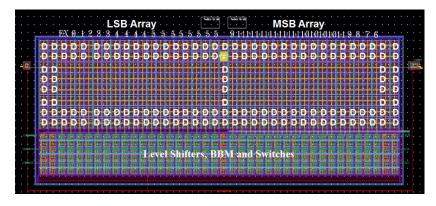

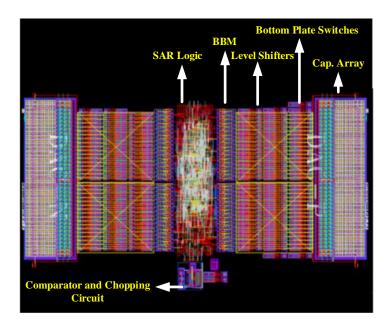

| Figure 6.26. Arrangement of SAR logic, level shifters, BBM and capacitor array                                          |      |

| Figure 6.27. Complete DAC layout with capacitor array, switches, BBM and level shifters                                 |      |

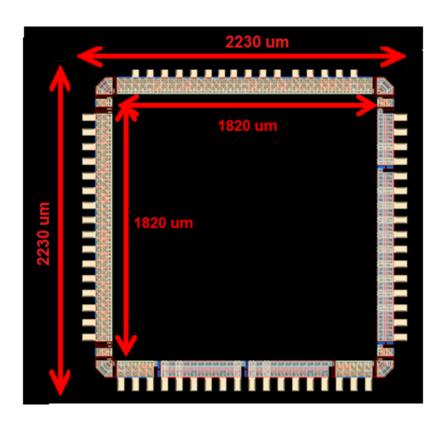

| Figure 6.28. IO ring layout.                                                                                            |      |

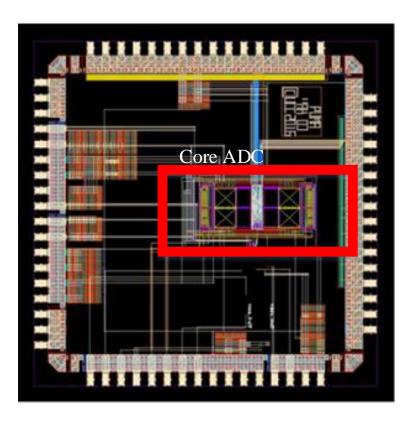

| Figure 6.29. Core ADC and IO ring                                                                                       |      |

| Figure 6.30. Core ADC sub-blocks                                                                                        |      |

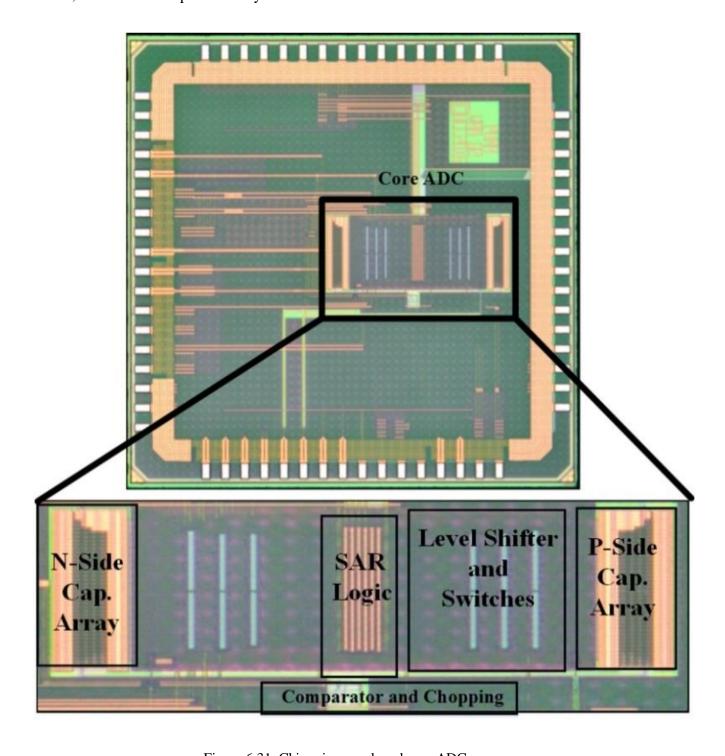

| Figure 6.31. Chip micrograph and core ADC.                                                                              |      |

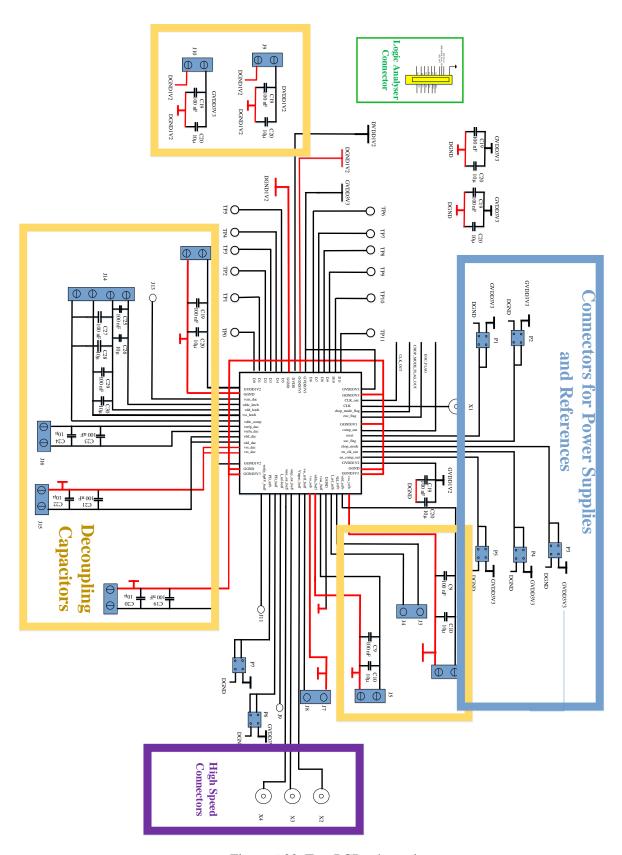

| Figure 6.32. Test PCB schematic                                                           | .179 |

|-------------------------------------------------------------------------------------------|------|

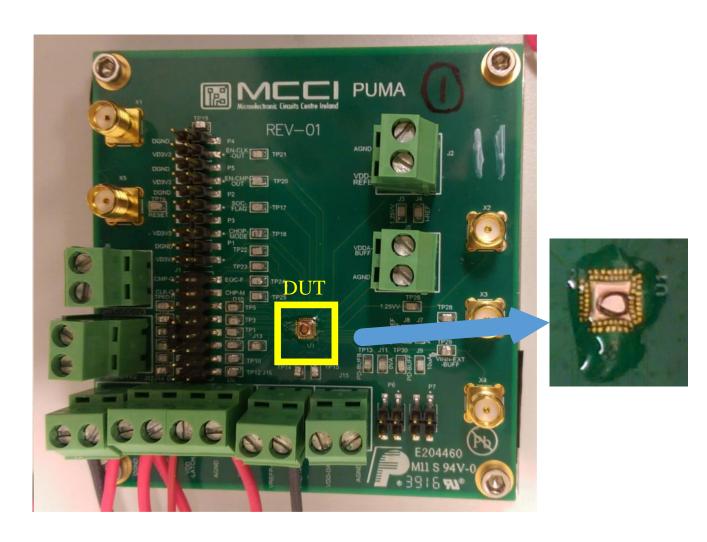

| Figure 6.33. Photograph of the test-PCB with a close up of DUT                            | 180  |

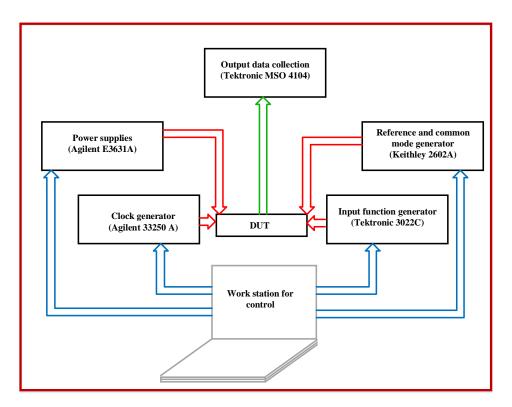

| Figure 6.34. Block diagram of test setup.                                                 | .181 |

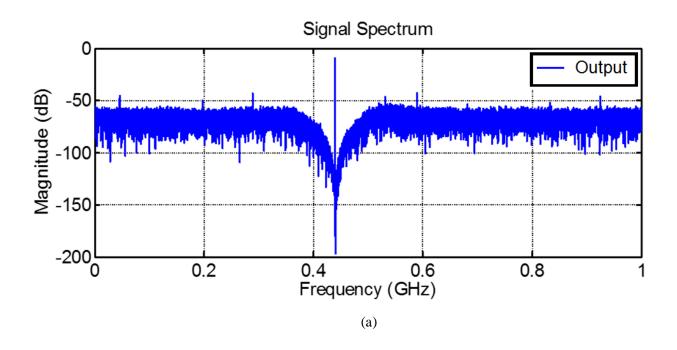

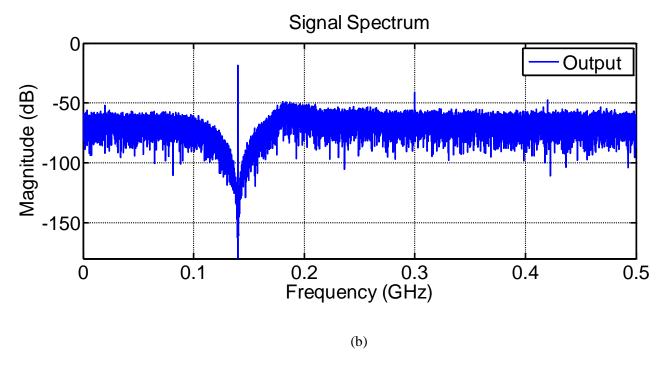

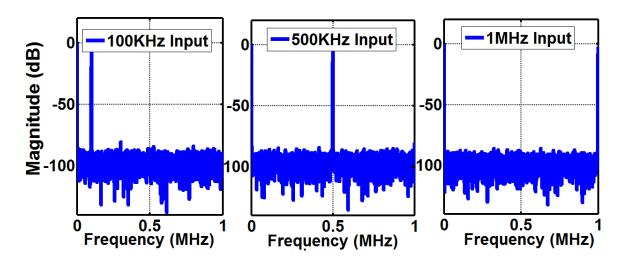

| Figure 6.35. Measured FFT spectrum of 3 different input frequencies, 100 kHz, 500 kHz and | 1    |

| MHz                                                                                       | 182  |

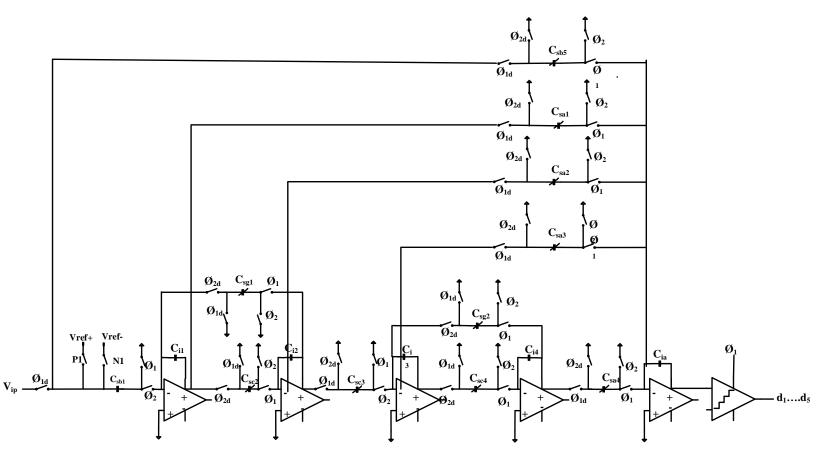

| Figure 6.36. SNDR and SFDR vs. input frequency                                            | .183 |

| Figure 6.37. Measured INL and DNL at 2MS/s                                                | 183  |

# **List of Tables**

| Table 4.1. CT ΣΔM ADC based architectures operating in GHz range                                           | 62   |

|------------------------------------------------------------------------------------------------------------|------|

| Table 4.2. Resolution requirements for different wireless communication standards                          | 66   |

| Table 4.3. $f_S$ selection for BP- $\Sigma\Delta M$ ADC for different wireless communication standards (in |      |

| normal and sub-sampled modes)                                                                              | 73   |

| Table 4.4. Summary of the achievable performance of the modulator in normal and sub-                       |      |

| sampling mode                                                                                              | 88   |

| Table 5.1. Modulator coefficients for $f_N = 3$ MHz                                                        | 94   |

| Table 5.2. Maximum and minimum values of all coefficients along with the number of bits                    |      |

| required for the implementation                                                                            | 95   |

| Table 5.3. f <sub>N</sub> , sampling capacitors of first and second integrator and corresponding IBE       | .102 |

| Table 5.4. Summary of the sampling and integrating capacitor values (pF)                                   | .102 |

| Table 5.5. Binary weighted sampling and resonant capacitors for 4 integrators                              | .102 |

| Table 5.6. Op-amps specifications (f <sub>s</sub> = 100 MHz)                                               | .107 |

| Table 5.7. SNDR for different bandwidths ( $f_s = 100 \text{ MHz}$ )                                       | .108 |

| Table 5.8. Op-amp specifications ( $f_S = 200 \text{ MHz}$ )                                               | .111 |

| Table 5.9. SNDR for different bandwidths ( $f_S = 200 \text{ MHz}$ )                                       | .111 |

| Table 5.10. Implementation of integrator coefficients                                                      | .114 |

| Table 5.11. Transistor sizes of op-amp.                                                                    | .117 |

| Table 5.12. Op-amp performance summary                                                                     | .117 |

| Table 5.13. Transistor sizing of switches of the different integrators and adder                           | .120 |

| Table 5.14. Transistor sizing of current mirror                                                            | .122 |

| Table 5.15. Functionality of control signals.                                                              | .125 |

| Table 5.16. Performance summary of the designed ADC                                                        | .135 |

| Table 5.17. Comparison of the designed ADC with other reported BP or reconfigurable BP $\Sigma$            | ΔM   |

| ADCs                                                                                                       | .137 |

| Table 6.1. Required specifications of the targeted ADC                                                     | .142 |

| Table 6.2. Capacitors mismatch data from different design kits.                                            | .156 |

| Table 6.3. Transistor sizes in double tail latch comparator.                                               | .171 |

| Table 6.4. Simulation results of comparator                                                                | .171 |

| Table 6.5. Measured performance of SAR ADC                                                                 | .184 |

| Table 6.6. Comparison of the measured performance with different state of the art designs                  | .184 |

## **Abbreviations**

A Area

AAF Anti-aliasing-filter

AC Alternating current

ADC Analog-to-digital converter

BBM Break-before-make

BoM Bill of material

BP  $\Sigma \Delta M$  Band-pass sigma delta modulator

BW Bandwidth

BWA Binary weighted with attenuation capacitor

BE Backward-Euler

CBW Conventional binary weighted

CM Common mode

C<sub>Spec</sub> Specific capacitance

CRFF Cascade of resonators with feedforward

CRFB Cascade of resonators with feedback

CMOS Complementary metal-oxide-semiconductor

CT Continuous time

C<sub>U</sub> Unit Capacitor

DAC Digital-to-analog converter

DC Direct current

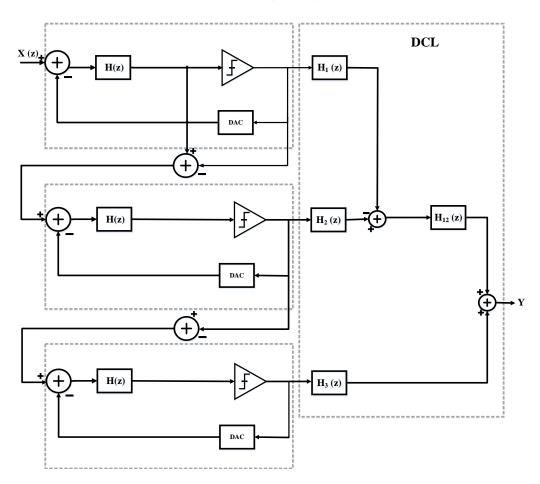

DCL Digital cancellation logic

DEM Dynamic Element Matching

DNL Differential non-linearity

DSP Digital signal processing

DR Dynamic range

DUT Design-under-test

DPWM Digital-pulse-width-modulator

DT Discrete time

DWA Data weighted averaging

ENOB Effective number of bits

E<sub>Q</sub> Quantisation Error

FE Forward-Euler

ILA Individual level averaging

IBE In-band error

ISI Inter-symbol-interference

f<sub>MAX</sub> Maximum frequency

f<sub>N</sub> Notch frequency

f<sub>S</sub> Sampling frequency

FS Full-scale

FoM Figure of merit

GBW Gain-bandwidth

HRZ Half-return-to-zero

HP High-pass

IC Integrated circuit

IF Intermediate frequency

INL Integral non-linearity

ISI Inter-symbol interference

ITRS International technology roadmap for semiconductors

k Boltzmann's constant

K<sub>C</sub> Pelgrom mismatch coefficient

LSB Least significant bit

LP Low-pass

MDAC Multiplying DAC

MSB Most significant bit

NF Noise figure

NRZ Non-return-to-zero

NTF Noise transfer function

OBG Out of band gain

Op-amp Operational amplifier

OSR Oversampling ratio

PAM Pulse amplitude modulation

PCB Printed circuit board

PDF Probability density function

PLL Phase locked loop

PWM Pulse-width-modulator

PSD Power spectral density

PMIC Power management integrated circuits

R<sub>ON</sub> ON-resistance

P<sub>Q</sub> Quantisation noise

Q Quality factor

QPSK Quadrature phase shift keying

RF Radio frequency

RMS Root mean square

ROM Read-only-memory

QoE Quality of experience

RZ Return-to-zero

SAR Successive approximation register

SC Switched capacitor

SI Switched current

SDR Software-defined-radio

$\Sigma\Delta$  Sigma delta

SFDR Spurious free dynamic range

S/H Sample and hold

SNDR Signal to noise and distortion ratio

SQNR Signal to quantisation noise ratio

SNR Signal to noise ratio

SR Set-reset

STF Signal transfer function

T Absolute temperature

TDC Time-to-digital converter

TF Transfer function

THD Total harmonic distortion

TI Time-interleaved

$V_{CM}$  Common mode voltage

$V_{IN}$  Input sampled voltage

VLSI Very large scale integration

$V_{OUT}$  Output voltage

$V_{pp} \hspace{1cm} Peak\text{-to-peak voltage} \\$

$V_{REFN}$  Negative reference voltage

V<sub>REFP</sub> Positive reference voltage

$V_T$  Threshold Voltage

## **Chapter 1: Introduction**

#### 1.1 Background

Integrated circuits (ICs) are an essential component in all electronic systems, especially for multimedia, mobile, automotive, communication, medical and portable applications. Most of the ICs in such electronic systems process and store the information in digital domain. At the same time, in order to communicate with the real world analog signals, analog-to-digital conversion is required, thus making ADCs an indispensable part of these systems.

Recent advancements in CMOS process technology led to it being the technology of choice for the realisation of modern ICs [1]. With the continuous and aggressive scaling of modern CMOS processes, digital circuits have benefitted most [2]. Transistors with lower feature sizes allow either to have more functionality on a die, or a reduction in die size for a given functionality, resulting in lower cost. Due to this, almost all the digital systems are being designed in CMOS technologies. However, this scaling has created various challenges for analog and mixed signal circuit designers. With the technology scaling; voltage headroom, oxide thickness and the intrinsic gain of transistors decreases [3]. Furthermore, the threshold voltage (V<sub>T</sub>) scaling is not in the same order as the supply voltage. These factors not only make analog and mixed signal circuit design especially ADC designs more challenging but also increases the power consumption for a given performance as designs migrate to smaller and smaller geometries. Another limitation associated with lower technology nodes is the gate-leakage mismatch that dominates over conventional mismatch mechanisms [4]. When all these factors are combined, it creates a complex set of constraints on the design of mixed signal IC systems where the analog and digital circuits are integrated on a single silicon die. The primary design

challenge in current integrated system designs is to exploit the benefits of technology scaling for digital circuits while careful design planning around those said limitations posed by scaling on analog circuits. Needless to say, there is a strong interest in the design community on the ADC design in the scaled technologies as demonstrated by the Murmann's ADC survey which tracks the ADC publications [5].

#### 1.2 Motivation

This thesis focuses on the design of ADCs in CMOS technologies for two application areas i.e. wireless communication and power management integrated circuits (PMICs).

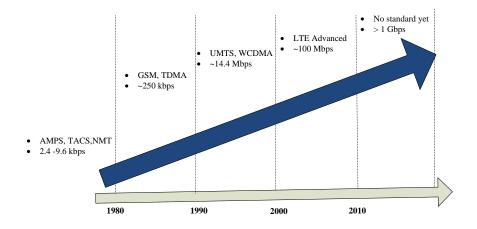

The wireless communication industry has seen unprecedented levels of growth over the past 40 years. Over the years, various wireless communication standards have been introduced. Figure 1.1 shows evolution of different wireless communication standards and the associated data rates over the last 40 years [6]. It is interesting to note that the supported data rates are getting faster with each standard. In addition to this, a modern radio receiver would need to support today's evolving systems such as IoTs, video-on-demand and machine-to-machine communications etc. Due to these factors, there has been a continuous growth in interest towards the design of highly integrated multistandard RF receiver architectures.

Figure 1.1. Evolution of different wireless communication standards [6].

PMIC is another important area of research in the context of IC design. These ICs generate, manage, control and distribute the stable voltages to other circuits and blocks in an electronic system. The continuous increase in the number of transistors in processors and microprocessors has equally benefitted all the computing applications ranging from data centres and servers to handheld and portable devices. However, power consumption and power management for these systems is one of the most important concerns. Typically, the data centres power and cooling expenditure are in the range of 10 to 15% of the total operational cost [7]. With the growing numbers of servers and their associated hardware capacity, energy efficiency is key to cost savings. Moreover, with the continuous increase of processing and memory capacity of different handheld and portable devices, energy efficiency is highly desired for a longer battery life [8]. Enhanced power management for such devices is very important for higher user quality of experience (QoE) [9]. Due to these factors, PMICs have got tremendous interest by the designer community. Furthermore, power management applications are also driving various other sectors such as automotive, healthcare, computing, artificial intelligence, neural networks, internet-of-things (IoTs) etc. As a result, PMICs have become an essential building block of electronic devices in order to optimise energy management, efficiency and sustainability. The global market for PMICs has reached to \$46 billion by 2020 [10]. These factors are driving a renewed interest in the research of power management circuits specifically in the area of increased conversion efficiencies and reducing the associated Bill of Materials (BoM).

The ADCs employed for these two applications pose a wide range of design challenges [11]-[21]. Firstly, in the context of wireless communication, the natural evolution of radio receiver architectures leads to the integration of multiple radio standards into a single receiver. Furthermore, as a result of the advancements in very large scale integration (VLSI) technology

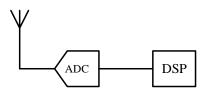

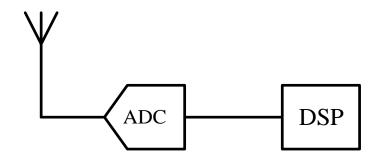

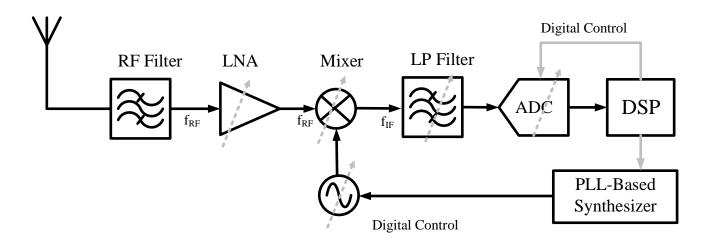

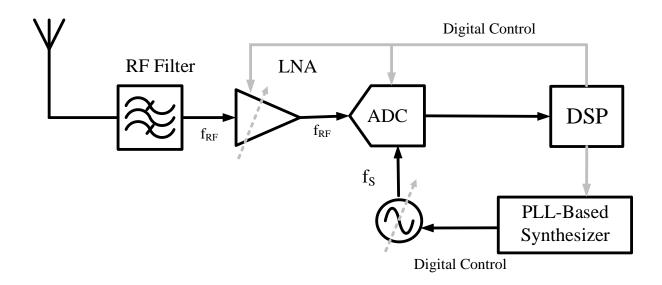

and CAD tools for the digital designs, there has been an enormous increase in the processing capabilities of digital signal processors (DSPs). These two factors have led to the emergence of the term "software-defined-radio" (SDR), first coined by Mitola [11]. A simplified block diagram of such receivers is shown in Figure 1.2. Such radios directly digitize the input RF signals just after the antenna thus transferring the entire signal processing to the digital domain, where software is used on a high performance DSP to perform the entire signal processing function in a flexible way [11]. The realisation of SDR architectures is primarily limited by the extremely power hungry specifications of such high performance ADCs [12]-[18]. Major design challenges include the wide bandwidth (BW), higher dynamic range (DR), high linearity and low power consumption. However, with recent advances in the BP-ΣΔM ADCs design techniques along with continuous scaling of the CMOS technologies, RF digitization is becoming a reality [12]-[19]. Some of these BP- $\Sigma\Delta$ Ms operating in RF frequency employ fixed notch frequency  $f_N$ in the NTF, to shape the quantisation noise away from the band of interest, to convert the input signal located at this frequency [13][14][18]. In order to successfully digitize the entire frequency range of the input RF signal, it needs to be placed within the modulator's passband. Other solutions include the use of reconfigurable BP continuous time (CT)- $\Sigma\Delta$ Ms with a tuneable f<sub>N</sub> [12][15]-[18]. The first part of the thesis is dedicated to the architectural level exploration, modelling, design and implementation of different ADC architectures for the SDR applications. Two different architectures for these applications will be detailed in the first part of the thesis.

Figure 1.2. Ideal SDR based receiver architecture as proposed in [11].

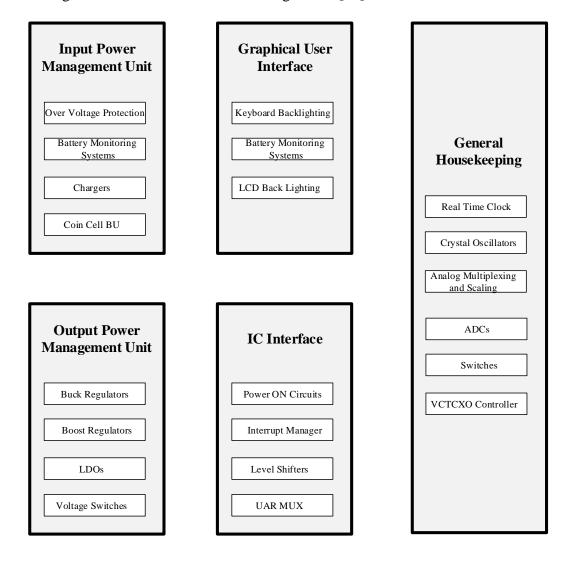

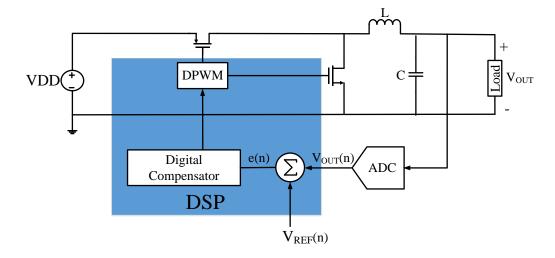

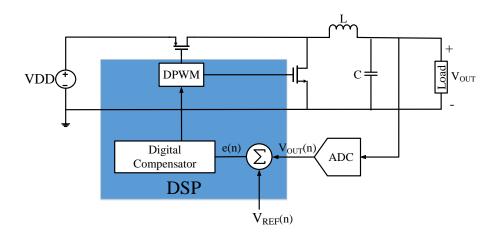

In the context of PMIC design, with the increase in complexity of the current electronic systems, PMICs have become far more complex compared to a simple power supply design. A block-level diagram of a typical PMIC is depicted in Figure 1.3 [19] and the diagram represents the different sub-blocks and their functionalities at an abstract level. The most important sub-block is the output power management unit which largely consists of different DC/DC converters. In recent years, there has been a surge in digitally controlled DC/DC converters. The ADC plays a key role in such digitally controlled DC/DC converters, where it is used to digitize the sensed voltages and currents as illustrated in Figure 1.4 [21].

Figure 1.3. A simplified block level representation of PMIC [20].

Figure 1.4. A digital controller of DC/DC converter with ADC.

Unlike conventional signal processing ADCs, these ADCs require excellent DC specifications e.g. DNL, INL, gain, offset and monotonicity. The second part of the thesis focuses on system level exploration, design and implementation of an ADC suitable for integration in a digitally controlled DC/DC converter solution. A comprehensive study of different ADC architectures suitable for this application, along with its design and implementation will be detailed in the second part of this thesis.

## 1.3 Thesis Organisation

The thesis is organised as follows:

Chapter 2 presents the general background of ADCs. Performance metrics and figure-of-merits (FoM) of ADCs are detailed in this chapter. Two major categories of ADCs, namely Nyquist rate and oversampling converters are also discussed briefly.

Chapter 3 presents a review of the working principles of noise shaping oversampled  $\Sigma\Delta M$  ADCs. Different topologies such as single-loop first and second-order modulators, single loop

higher order modulators, multiple loop or cascaded, as well as single and multibit quantiser implementations are explained in detail.

Chapter 4 presents an architectural level exploration and system level design of  $4^{th}$ -order CT BP- $\Sigma\Delta M$  ADCs for SDR applications. In the context of the SDRs comprising RF-to-digital converters, the concept of sub-sampled  $\Sigma\Delta M$  ADC is explained. A new methodology for the synthesis of CT BP implementation is also presented and discussed. Based on the said methodology, a  $4^{th}$ -order CT BP- $\Sigma\Delta M$  ADC has been modelled and simulated and results are presented.

Chapter 5 focuses on the design and implementation of a tuneable notch (i.e.  $f_N$ )  $4^{th}$ -order SC  $\Sigma\Delta M$  aimed at intermediate frequency (IF) digitization. Starting from the coefficient synthesis, different architectural and circuit level techniques have been detailed in this chapter. Experimental characterization of the designed ADC is explained towards the end of the chapter.

Chapter 6 focuses on the design of the SAR ADC. Two broad categories of SAR ADCs are briefly detailed. Furthermore, SAR ADC sub-blocks i.e. sample-and-hold (S/H), DAC and comparator and their different design considerations are also detailed in this chapter. Following that, the circuit-level implementation of a 12-bit SAR ADC for power management applications is given. Different strategies for input scaling, comparator offset removal and linearity improvement along with experimental characterization are also detailed.

Chapter 7 summarises the main conclusions of the presented work and directions for potential future work.

## **Chapter 2: ADCs Background Study**

## 2.1 Introduction

This chapter introduces the basic concepts of ADCs, including sampling and quantisation. ADC performance metrics are presented and examined. A basic introduction of two major categories of ADCs, namely Nyquist rate ADCs and oversampling ADCs is also given. Finally, two commonly used FoMs of ADCs are briefly explained.

## 2.2 Basic Concepts of ADCs

Analog signals are continuous in time and amplitude. ADC takes these signals and outputs a discrete time (DT) representation using a limited set of amplitude levels, at discrete time intervals. To achieve this, the input signal is both sampled in time domain and amplitude is quantised. This section examines the considerations associated with both steps.

## 2.2.1 Sampling

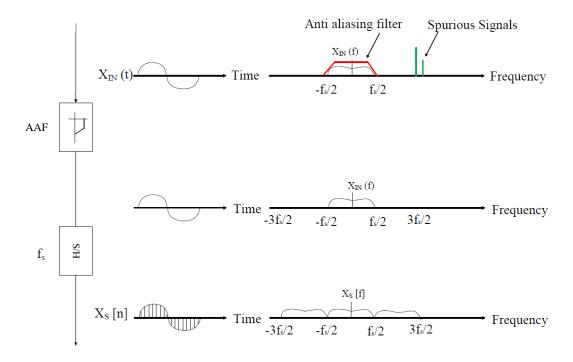

Sampling is the process of converting a CT signal into a DT signal. The minimum sampling frequency  $(f_S)$  required to acquire the information from the signal is twice the signal bandwidth also known as Nyquist frequency [22]. In the frequency domain, sampling produces the aliases of input signal at the multiples of  $f_S$ . As an illustration, Figure 2.1 depicts the signal-spectrum plots of input and output of sample and hold (S/H). Due to aliasing, signals or noise located at frequencies greater than the Nyquist frequency fold into the band of interest when sampled. An example of this problem is illustrated in Figure 2.2, where two signals located at different frequencies i.e.  $f_S/2$  (Figure 2.2. (a)) and  $3f_S/2$  (Figure 2.2. (b)) result in the same discrete time signal when sampled by an S/H as illustrated in Figure 2.2. (c).

Figure 2.1. Input and output of an S/H.

Figure 2.2. Aliasing due to two sinusoids (a) Input sinusoid at a frequency  $f_S/2$  (b) Input sinusoid at a frequency  $3f_S/2$  and (c) Output of the S/H.

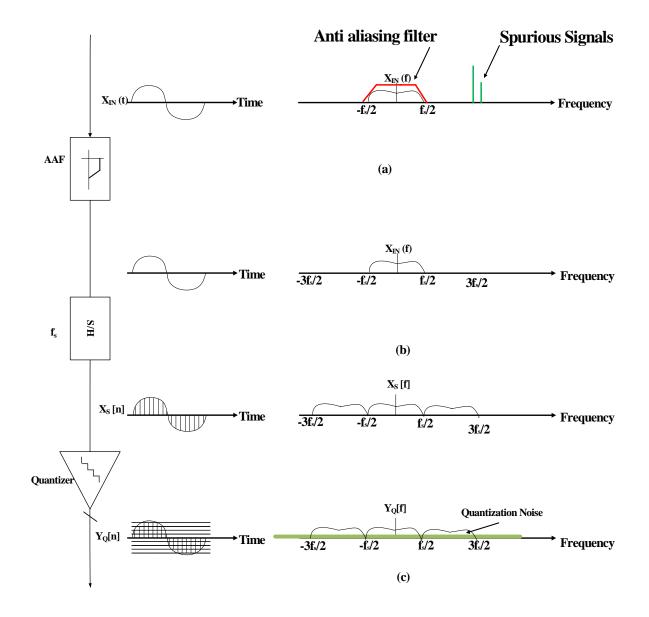

To avoid this, usually anti-aliasing filters (AAF) are employed in front of the S/H circuit to suppress any out of band unwanted signals, from corrupting the baseband. Time and frequency domain plots of an S/H in the presence of a preceding AAF are depicted in Figure 2.3.

#### 2.2.2 Quantisation

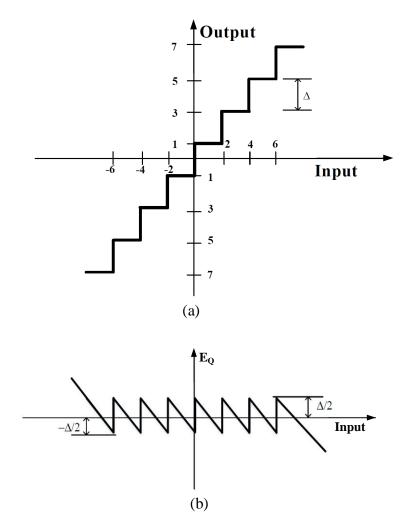

Quantisation is the process of discretising the signal with respect to amplitude. In this process, the signal amplitude is mapped to a limited set of values. The number of these sets of values depends on the resolution of the quantiser (also represented in bits). The difference between two consecutive output levels is called quantisation step and is represented by  $\Delta$ , whereas the difference between the actual input level and the corresponding digital output level is termed as quantisation error (E<sub>Q</sub>). The input-output characteristics of a quantiser along with its associated E<sub>Q</sub> across the allowable range of input values are depicted in Figure 2.4 (a) and (b) respectively, demonstrating that for an input signal located within the valid input range of quantiser, the E<sub>Q</sub> is bounded within [ $-\Delta$ /2,  $\Delta$ /2].

Figure 2.3. Time and corresponding frequency domain plots of an S/H with a preceding AAF.

Figure 2.4. (a) Input-output characteristic of a quantiser (b) The corresponding E<sub>0</sub>.

When the input signal exceeds this range,  $E_Q$  increases monotonically, resulting in what is commonly referred as the overload or saturation of the quantiser (illustrated in Figure 2.4 (a)).

Due to its highly non-linear nature, the analysis of quantisers is not simple [23]. Specifically, in complex systems, like  $\Sigma\Delta M$  having a quantiser in the loop, the dynamics become quite complex and as a result more difficult to analyse. Due to this reason, many designers rely on simple models, like the "uniform white noise or additive model". Using such models, quantiser is replaced by its linearised version, thus making the analysis and design of the system simpler, while keeping a certain degree of accuracy.

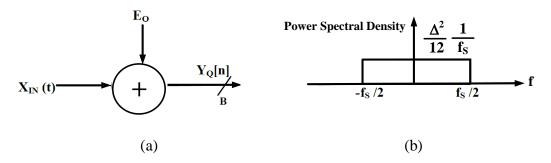

If it is assumed that the input signal changes rapidly from sample to sample by amounts greater than  $\Delta$ , then the  $E_Q$  does not have any correlation from one sample to the next. As a result, it can be considered to have an equal probability of lying anywhere between  $-\Delta/2$  and  $\Delta/2$ , provided that no overloading occurs. Based on this, the quantiser can be modelled as an additive uniform white noise source [23]. A block diagram of this model is illustrated in Figure 2.5 (a). Based on this model, the  $E_Q$  can be approximated by a uniform random number distributed between  $-\Delta/2$  and  $\Delta/2$  [24][25]. In this way, the total quantisation power can be approximated to  $\Delta^2/12$ , with a white power spectrum as shown in Figure 2.5 (b) [26].

#### 2.3 ADC Performance Metrics

ADC specifications can be divided in two broad categories: AC or dynamic specifications and DC or static specifications [27]. This section describes the various performance metrics associated with these categories.

#### 2.3.1 AC Performance

The performance of the ADC in the frequency domain is characterised by AC performance metrics which are extracted from the digital outputs of the ADC by assuming a sinusoid as an input test signal. The imperfections of the ADC sub-blocks introduce noise and distortion into the digitized output.

Figure 2.5. (a) Linear quantiser white noise model and (b) The associated white noise spectral density.

Thereby these metrics indicate the accuracy, noise and distortion of the digitized output. Important AC specifications include signal-to-noise ratio (SNR), signal-to-noise-and-distortion ratio (SNDR), dynamic range (DR) and effective number of bits (ENOB). All these specifications are briefly described in the following while a graphical illustration of these metrics versus input sinusoid amplitude is given in Figure 2.6 [28].

#### 2.3.1.1 Signal to Noise Ratio

SNR is the ratio of the power at the frequency of an input sinusoid to the total in-band-noise power at the output of the ADC (in dBs) for specific input amplitude [1][28]. This parameter is also expressed in  $V_{RMS}$ , or %. SNR accounts for the linear performance of the ADC and therefore in-band-noise associated with harmonics is not included. For an ideal ADC having input sinusoid amplitude of "X" and considering the quantisation noise of  $P_Q$ , the SNR is represented as:

$$SNR = 10\log_{10} \left[ \frac{X^2}{2P_Q} \right]. \tag{2.1}$$

Figure 2.6. AC performance metrics on a typical SNR curve of a  $\Sigma\Delta M$  ADC [28].

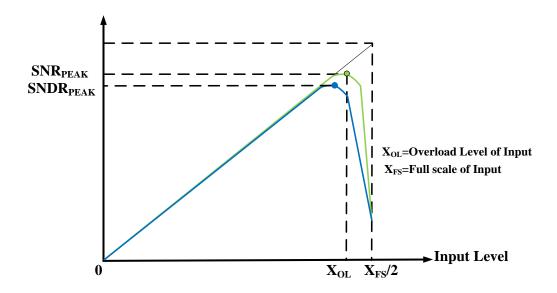

#### 2.3.1.2 Signal to Noise plus Distortion Ratio

SNDR is the ratio of the input signal power and the in band noise power while taking into account the harmonics at the ADC output as well [1]. The magnitude is typically expressed in dBs. Figure 2.6 illustrates a typical SNDR curve of a  $\Sigma\Delta M$ . For the larger input amplitudes, the curve deviates from the SNR due to the distortions. SNDR is usually calculated for  $f_{IN} < BW/3$ , where  $f_{IN}$  is the frequency of input sinusoid and BW is the bandwidth, so that second and third harmonics lie within the band of interest [28].

# 2.3.1.3 Dynamic Range

DR is the ratio of the output power of a sinusoid having maximum amplitude to the output power of the minimum detectable input signal for which SNR=0 dBs [28]. The maximum amplitude of the input signal can be characterised as peak-to-peak, zero-to-peak or root mean square (rms). The minimum detectable signal is the rms noise measured with no applied signal. For a sinusoidal input signal with maximum amplitude at the ADC input  $X_{FS}/2$  having quantisation noise of  $P_O$ , the DR can be represented as:

DR =

$$10\log_{10} \left[ \frac{\left( X_{FS} / 2 \right)^2}{2P_Q} \right]$$

. (2.2)

#### 2.3.1.4 Effective Number of Bits

The DR of an ADC is reduced due to noise, distortion and other non-idealities present. A given input cannot be resolved beyond a certain number of bits of resolution, which is known as effective number of bits (ENOB) [28]. ENOB can be represented as:

ENOB =

$$\frac{\left(DR\big|_{dB} - 1.76\right)}{6.02}$$

. (2.3)

For  $\Sigma\Delta M$  ADCs, instead of a DR in (2.3), SNDR<sub>PEAK</sub> is used [28].

#### 2.3.1.5 Overload Level

In the context of  $\Sigma\Delta M$  ADCs, OL is another important AC performance metric. As illustrated in Figure 2.6, the SNR of the ADC starts dropping for input amplitudes close to half of the full scale of input. In that sense, it is considered as the maximum input amplitude for which the ADC can function correctly.

#### 2.3.2 DC Performance

The DC specifications of the ADC give the performance measures of ADC with steady state analog inputs. These specifications are more important in instrumentation and measurement applications such as temperature, pressure or weight etc. In such applications, ADC input signals are located near DC and possess very low bandwidths. Important DC specifications include DNL, INL, gain error and offset.

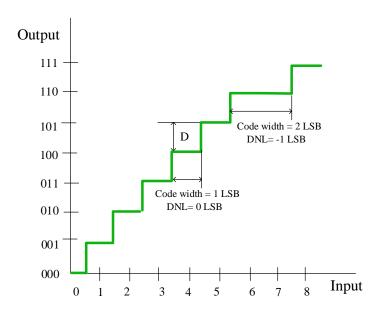

#### 2.3.2.1 Differential Non-Linearity

The output of an ADC is represented in bits, whereby the difference between two consecutive output levels is equal to one least significant bit (LSB). DNL is the deviation of difference of two consecutive output levels from the ideal difference (one LSB) [29]. Due to non-idealities of the ADC, it can be higher than 1 LSB. As an example, Figure 2.7 illustrates the input-output characteristic of a 3-bit ADC having a DNL of 1 LSB. For an N-bit ADC, DNL can be represented as:

$$DNL[i] = \left\lceil \frac{V_{i+1} - V_i}{LSB} \right\rceil - 1$$

(2.4)

Figure 2.7. Input-output characteristic of a 3-bit ADC having 1 LSB DNL.

where "i" represents the output level such that  $0 < i < 2^N$ -1. If the DNL becomes larger than 1 LSB, a missing code can result. If the output code always increases with increasing input ADC is said to be monotonic. For an ADC to be monotonic, DNL should never exceed beyond -1 LSB. A non-monotonicity situation can be catastrophic if ADCs are being employed in feedback control systems.

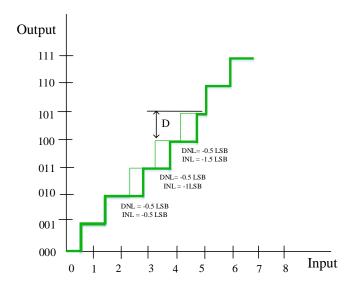

# 2.3.2.2 Integral Non-Linearity

The INL of the ADC at a specific input is the cumulative sum of the DNL till that point [29]. It can be represented as:

$$INL[i] = \sum_{m=1}^{m=i-1} DNL[m]. \tag{2.5}$$

Where "i" represents the output level such that  $0 < i < 2^{N}$ -1. As an example, Figure 2.8 illustrates the INL of a 3-bit ADC at different points.

Figure 2.8. Input-output characteristic of a 3-bit ADC with INL, shown as cumulative sum of DNL.

Larger INL not only degrades the DC performance of the ADC, but in addition adds noise and distortion in the digitized signal, thus degrading the SNR. Therefore, the total amount of noise at the output of an ADC is the sum of quantisation noise and the noise introduced due to INL and can be represented as [30]:

$$V_{\text{noise}}^{2} = \frac{\Delta^{2}}{12} + \underbrace{\frac{\Delta^{2}}{12} \sum_{i=0}^{2^{N}-1} INL_{i}^{2}}_{INLNoise}.$$

(2.6)

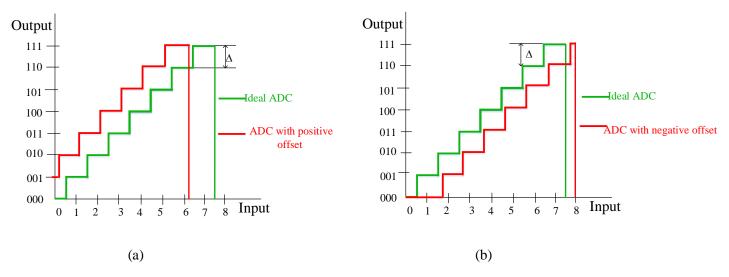

#### 2.3.2.3 Offset

The transfer function (TF) of an ADC is the relationship of the input to the ADC versus the code's output by the ADC. Offset error shifts the TF curve of the ADC linearly, as illustrated in Figure 2.9. The magnitude of offset error is equal to the difference between ideal start points (0.5 LSB) to actual start point [31]. As an example, Figure 2.9 (a) and (b) illustrates the input-output characteristic of a 3-bit ADC having positive and negative offset, respectively.

Figure 2.9. Input-output characteristic of a 3-bit ADC having (a) Positive offset (b) Negative offset.

Offset in an ADC is typically caused due to mismatches of the circuit components (transistors, capacitors, resistors etc.) and can move with ageing. Depending upon the application, different strategies can be adopted to remove the offset errors [32][33].

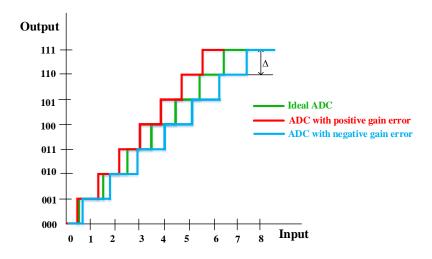

## **2.3.2.4 Gain Error**

Gain error, also known as full scale error is the difference between the full scale output code and the actual value of the input providing full scale at the output [31]. Although important, this error can be removed from the digital output. The gain error of an ADC is characterised after calibrating the ADC readings for the offset.

As an example, Figure 2.10 illustrates the input-output characteristic of a 3-bit ADC having positive and negative gain errors, respectively. Note that the gain error impacts the maximum input signal.

Figure 2.10. Input-output characteristic of a 3-bit ADC with positive and negative gain error.

# 2.4 Nyquist-rate ADCs

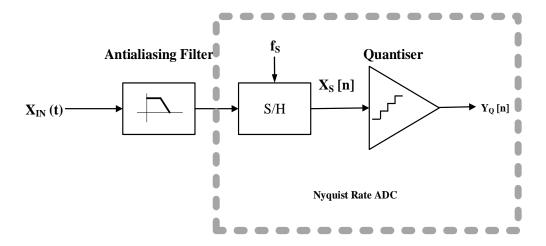

Nyquist-rate ADCs sample at twice the BW of input signals [27]. A block diagram of a Nyquist-rate ADC along with different sub-blocks is shown in Figure 2.11 while Figure 2.12 illustrates the time and frequency plot of the signal at the inputs and outputs of different sub-blocks of the ADC. The input signal X(t), after passing through the AAF, is sampled by the S/H and then passes through the quantiser. Sampling the input signal does not introduce any error in the signal spectrum, provided the Nyquist criteria are fulfilled.

Figure 2.11. Arrangement of blocks in a Nyquist ADC.

Figure 2.12. Time and frequency domain plots of signal at different nodes of Nyquist-rate ADC (a) Input signal (b) Output of AAF (c) Output of S/H (c) Output of quantiser.

The quantiser maps the amplitude values of the sampled signals into a set of discrete values, and introduces quantisation noise, which is equal to the difference between quantised value,  $Y_Q[n]$ , and corresponding input,  $X_S[n]$ . It has been shown in section 2.2.2 that for the case where the quantisation levels are separated by  $\Delta$ , the  $E_Q$  can be approximated by a uniform random number distributed between  $\pm \Delta/2$ , that can be modelled as white noise spread over the frequency range of 0-to-f<sub>S</sub> [23] [24].

The noise introduced by the quantiser is dependent upon the resolution (or quantisation step i.e.  $\Delta$ ) of the quantiser and is given by  $\Delta^2/12$  [23]. The quantisation noise,  $P_Q$ , also determines the signal-to-quantisation-noise ratio (SQNR). If the maximum input amplitude applied to an N-bit quantiser is in the non-overload region is  $X_{FS}/2$ , then its corresponding power at the ADC output can be approximated as:

$$P_{OUT} = \frac{(X_{FS}/2)^2}{2} \cong \frac{(2^N \Delta/2)^2}{2} = (2^{2N-3} \Delta^2)$$

(2.8)

Therefore, the SQNR of the ideal ADC or SQNR<sub>MAX</sub> is given by:

$$SQNR_{MAX} = \frac{P_{OUT}}{P_{O}}.$$

(2.9)

Here  $P_Q$  is the quantisation noise and is given by:

$$P_{Q} = \frac{\Delta^2}{12} \tag{2.10}$$

Employing the expression for  $P_{OUT}$  and  $P_{Q}$  from (2.8) and (2.10) in (2.9) gives,

$$SQNR_{MAX|dB} = 6.02N + 1.76$$

(2.11)

## 2.5 Nyquist-rate ADC Architectures

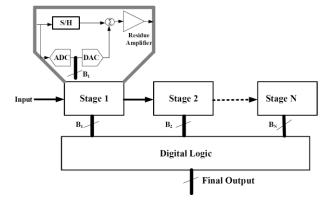

Nyquist ADCs can be realised with various architectures. Each architecture involves different trade-offs among speed, accuracy, power and area. A brief overview of three of the most important architectures namely flash, SAR and pipeline ADCs and their trade-offs are given here.

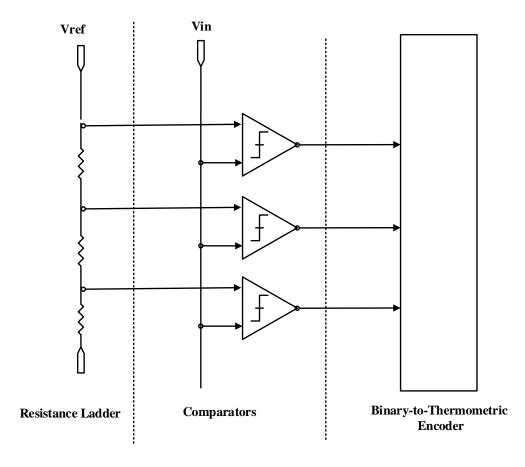

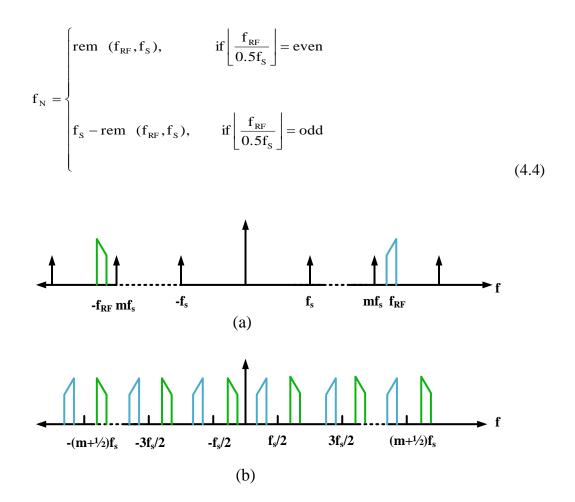

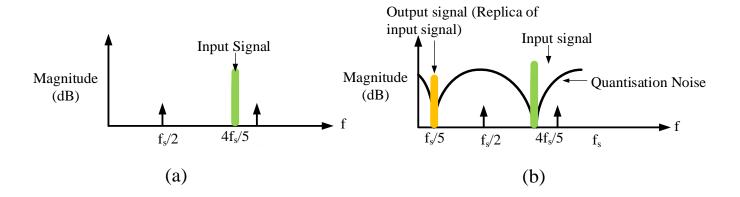

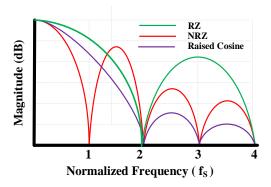

#### **2.5.1** Flash ADC