## A Generalized Predictive Controlled ANDALUCIA TECH T-type Power Inverter with a deterministic dc-link capacitor voltage balancing approach

### A PROJECT REPORT

Submitted by

### **CHARANRAJ MOHAN**

In the partial fulfillment for the award of the degree

of

### **MASTER**

in

**ELECTRONICS, SIGNAL PROCESSING & COMMUNICATION**

### ESCUELA TECNICA SUPERIOR DE INGENIERIA UNIVERSIDAD DE SEVILLA SEVILLE 41092

**JULY 2015**

### **ACKNOWLEDGEMENT**

First and foremost, I sincerely thank our beloved director **Prof. Jaime Dominguez Abascal,** deputy director of studies, **Prof. Francisco Rodriquez Rubio,** Secretary, **Prof. Francisco Javier Gutierrez Ortiz** and head of the electronics engineering department, **Prof. Antonio Jesus Torralba Silgado** of Escuela Superior de Ingenieria, University of Seville at this high time for providing the necessary facilities to complete my project successfully.

I would like to express my sincere thanks to the HERITAGE consortiumteam and its coordinators for providing me an opportunity to do Masters under the HERITAGE-Erasmus Mundus project.

I am grateful to **Prof. Leopoldo Garcia Franquelo,** Department of Electronics Engineering for his anchoring support and guidance in doing this project.

I express my sincere thanks to Associate Prof. Sergio Vazquez, Associate Prof. Jose Ignacio Leon Galvan and Mr. Abraham Marquez from the department of Electronics Engineering for their constant guidance, high patience, constructive criticism and encouragement throughout the project work.

I also thank all the teaching, non- teaching staffs, friends, colleagues and family who had directly and indirectly helped in bringing out the project in a success.

| CHAPTER | TITLE                                           | <b>PAGE</b> |

|---------|-------------------------------------------------|-------------|

| NO.     |                                                 | NO.         |

|         | ABSTRACT                                        | i           |

|         | LIST OF TABLES                                  | ii          |

|         | LIST OF FIGURES                                 | iv          |

|         | LIST OF ABBREVATIONS                            | viii        |

| 1.      | INTRODUCTION                                    | 1           |

| 2.      | MULTILEVEL INVERTERS                            | 3           |

|         | 2.1. INVERTER TOPOLOGIES                        | 4           |

|         | 2.1.1. NEUTRAL POINT CLAMPED MULTILEVEL         | 4           |

|         | INVERTER                                        |             |

|         | 2.1.2. CASCADED H-BRIDGE INVERTER               | 5           |

|         | 2.1.3. FLYING CAPACITOR MULTILEVEL              | 6           |

|         | INVERTERS                                       |             |

|         | 2.2. MODULATION SCHEMES                         | 8           |

|         | 2.3. CONTROL STRATEGIES                         | 9           |

| 3.      | NEUTRAL POINT PILOTED (NPP) POWER INVERTER      | 11          |

| 4.      | SYSTEM DESCRIPTION, MODELING & CONTROL          | 13          |

|         | DESIGN                                          |             |

|         | 4.1. GPC STRATEGY FOR OUTPUT VOLTAGE CONTROL    | 13          |

|         | 4.2. T-TYPE INVERTER SYSTEM WITH INDIVIDUAL     | 19          |

|         | VOLTAGE SOURCES                                 |             |

|         | 4.3. T-TYPE INVERTER SYSTEM USING INDIVIDUAL DC | 22          |

|         | LINK CAPACITORS                                 |             |

|         | 4.3.1. REDUNDANCY DC LINK CAPACITOR             | 22          |

|         | VOLTAGE BALANCING APPROACH                      |             |

|         | 4.3.2. DETERMINISTIC DC LINK CAPACITOR          | 24          |

|         | VOLTAGE BALANCING APPROACH                      |             |

|    | 4.4. COMPARISON OF THE DC LINK CAPACITOR | 36 |

|----|------------------------------------------|----|

|    | VOLTAGE BALANCING APPROACHES             |    |

| 5. | DESIGN OF A NPP POWER INVERTER           | 38 |

| 6. | ADVANTAGES & APPLICATIONS                | 47 |

| 7. | CONCLUSION & FUTURE WORK                 | 48 |

| 8. | REFERENCES                               | 49 |

### **ABSTRACT**

The thesis consists of implementing a Generalized Predictive Control (GPC) strategy for controlling the output voltage of the T-type converter with output LC filter, whose control signals are modulated by a fast three-dimensional Space Vector Modulation (SVM). The GPC strategy used for the T-type converter involves developing a system of dynamic equations from the output LC filter and load, which is transformed to a Controlled Auto-Regressive and Moving-Average (CARIMA) model in order to obtain a sequence of control signals, so that a cost function is optimized and the reference is tracked.

The core of the thesis addresses the main problem of dc-link capacitor balancing. This is done by modeling the converter and deploying a mathematical analysis of the capacitor voltage difference dynamics, by singular perturbation approach. This analysis results in an explicit sinusoidal disturbance. Now, classical control theory is applied by using a Luenberger Observer (LO) in order to estimate the disturbance and encounter it, thereby keeping the dc-link capacitor voltage balanced in the due flow of the modulation and output voltage control. By this method, the output voltage across the filter capacitor is controlled, the dc-link capacitor voltage is balanced and the low-frequency voltage ripples present in the dc-link of the T-type converter are reduced to an acceptable level.

### LIST OF TABLES

| <b>TABLE</b> | DESCRIPTION                                         | PAGE NO |

|--------------|-----------------------------------------------------|---------|

| Table 2.1    | Switching states of a Three level single phase NPC  | 4       |

| Table 2.2    | Switching states of a single phase three level H-   | 5       |

|              | Bridge converter                                    |         |

| Table 2.3    | Switching states of a Five level single phase H-    | 6       |

|              | Bridge Converter                                    |         |

| Table 2.4    | Switching states of a three level single phase FCC  | 7       |

| Table 3.1    | Switching states of a single phase T-type converter | 11      |

| Table 4.1    | System Variables and Parameters                     | 16      |

| Table 4.2    | Model & Simulation Parameters for GPC               | 16      |

| Table 4.3    | GPC recursive polynomial calculation across         | 17      |

|              | horizons                                            |         |

| Table 4.4    | Redundancy control strategy to balance the dc link  | 22      |

|              | capacitor voltages                                  |         |

| Table 4.5    | Model parameters used in the equivalent ideal       | 25      |

|              | switch                                              |         |

| Table 4.6    | Resolving the input currents flowing towards the    | 27      |

|              | switches into quadratic function                    |         |

| Table 4.7    | Space vector sequence & switching times for 3D-     | 32      |

|              | SVM                                                 |         |

| Table 4.8    | Space vector sequence & switching times for 3D-     | 35      |

|              | FFSVM                                               |         |

| Table 5.1    | Switching modes of AT-NPC 3-level IGBT module       | 39      |

|              | (a three level NPP converter leg)                   |         |

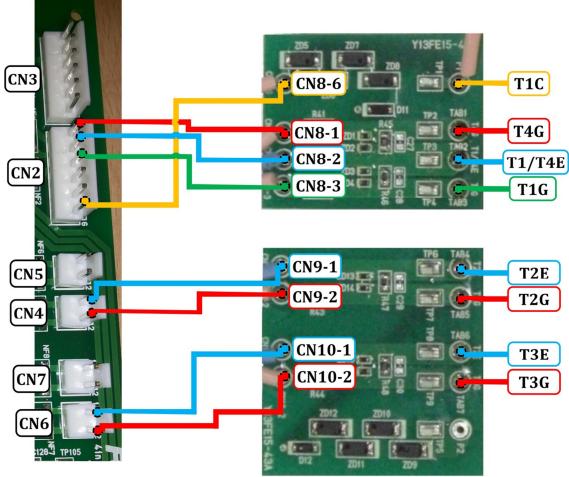

| Table 5.2    | Pin configuration of Input connectors- CN1 &        | 39      |

|              | CN101 for each driver board                         |         |

| Table 5.3    | Pin configuration of Output connectors- CN2, CN3,   | 40      |

|              | CN4, CN5, CN6 & CN7 for each IGBT driver            |         |

|              | board                                               |         |

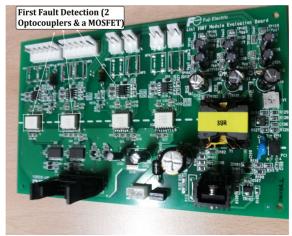

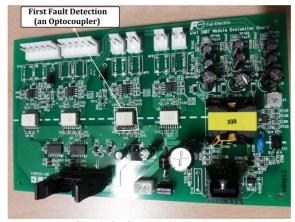

| Table 5.4    | List of Faulty components during FFD                | 41      |

| Table 5.5    | Ratings of output side power supply of optocoupler  | 43      |

| Table 5.6 | Observed values in the faulty optocouplers   | 43 |

|-----------|----------------------------------------------|----|

| Table 5.7 | Summary of faults in driver & its correction | 44 |

### LIST OF FIGURES

| FIGURE     | DESCRIPTION                                                                                                                                  | PAGE NO |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 2.1 | Different multilevel converter topologies                                                                                                    | 3       |

| Figure 2.2 | A single phase NPC                                                                                                                           | 4       |

| Figure 2.3 | Conventional H-bridge (3 level, single phase) converter                                                                                      | 5       |

| Figure 2.4 | Five-level single phase H-bridge converter                                                                                                   | 6       |

| Figure 2.5 | Three-level single phase flying capacitor converter                                                                                          | 7       |

| Figure 2.6 | Various modulation schemes for multilevel converters                                                                                         | 8       |

| Figure 3.1 | Leg schematic of a three-level T-type power inverter: (a) bidirectional switch with conventional IGBT, (b) bidirectional switch with RB-IGBT | 11      |

| Figure 3.2 | Leg schematic of a single phase three level T-type module                                                                                    | 11      |

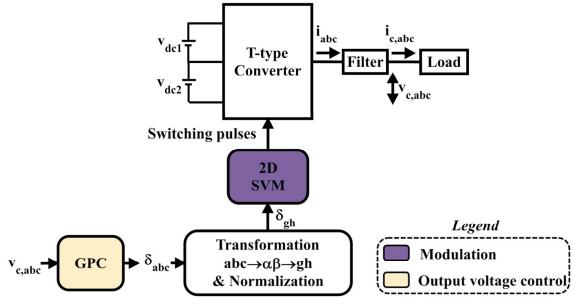

| Figure 4.1 | Scheme of T-type converter connected to load via LC filter                                                                                   | 15      |

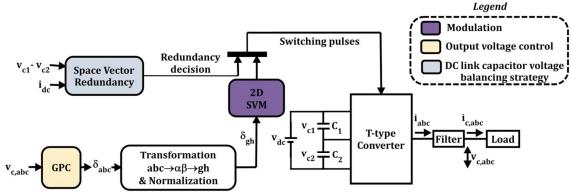

| Figure 4.2 | Block diagram of the T-type inverter system with separate dc voltage source                                                                  | 20      |

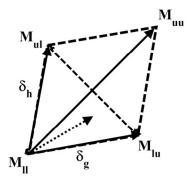

| Figure 4.3 | Parallelogram comprising two equal triangles                                                                                                 | 20      |

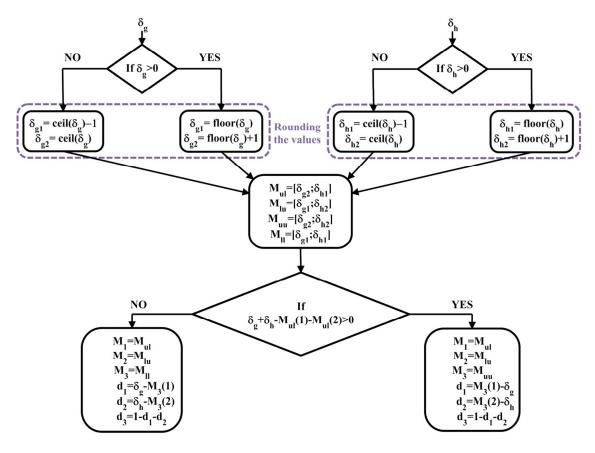

| Figure 4.4 | Two dimensional Space Vector Modulation algorithm                                                                                            | 21      |

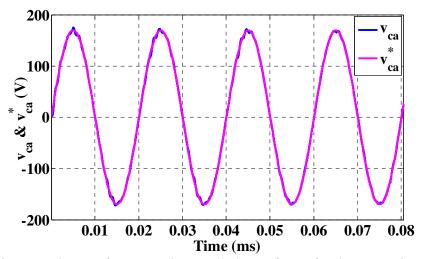

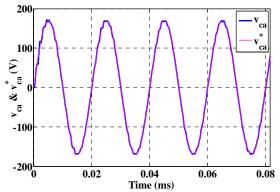

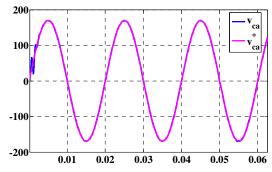

| Figure 4.5 | Output voltage-reference and controlled waveforms for the T-type inverter system with individual dc voltage sources                          | 21      |

| Figure 4.6 | Block diagram of the T-type inverter system with redundancy dc link capacitor voltage balancing approach                                     | 22      |

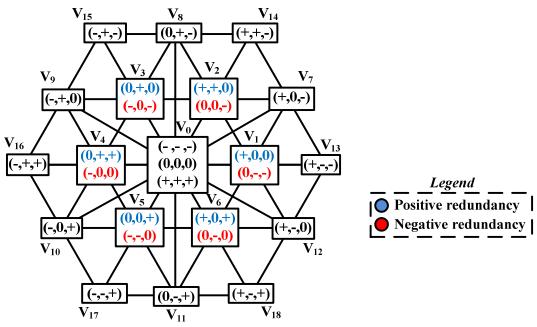

| Figure 4.7 | Switching state vectors of a three level converter                                                                                           | 23      |

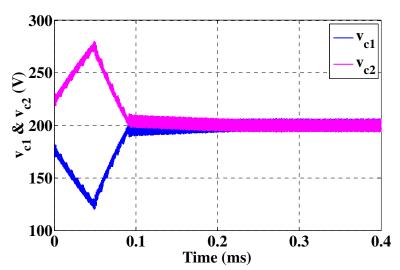

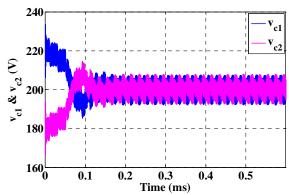

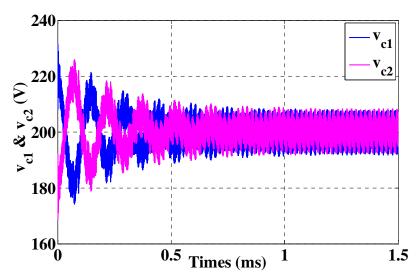

| Figure 4.8 | DC link capacitor voltages $v_{c1}$ & $v_{c2}$ balanced by redundancy approach with initial imbalance condition                              | 23      |

| Figure 4.9  | Output voltage-reference and controlled waveforms for Redundancy approach                                                              | 24 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

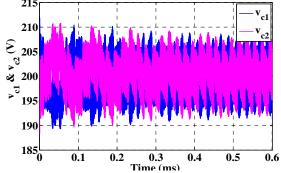

| Figure 4.10 | DC link capacitor voltages $v_{c1}$ & $v_{c2}$ for redundancy approach                                                                 | 24 |

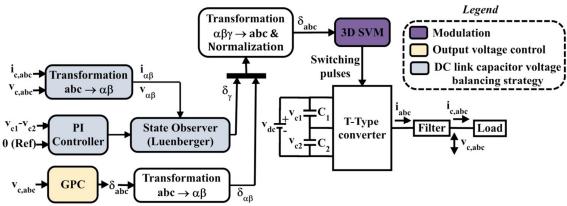

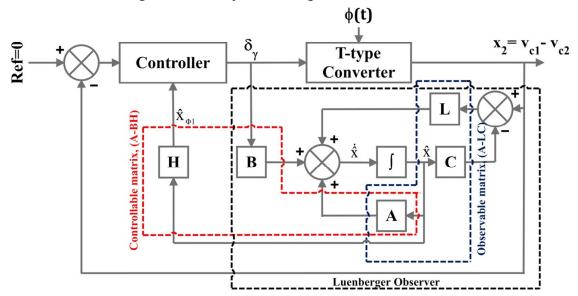

| Figure 4.11 | Block diagram of deterministic capacitor voltage balancing approach using 3D SVM                                                       | 25 |

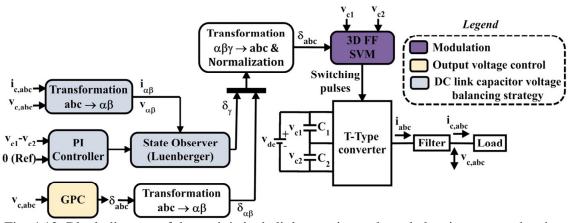

| Figure 4.12 | Block diagram of deterministic capacitor voltage balancing approach using 3D FFSVM                                                     | 25 |

| Figure 4.13 | Equivalent circuit of a 3L T-type converter with ideal switches                                                                        | 26 |

| Figure 4.14 | Deterministic dc link capacitor voltage balancing approach                                                                             | 30 |

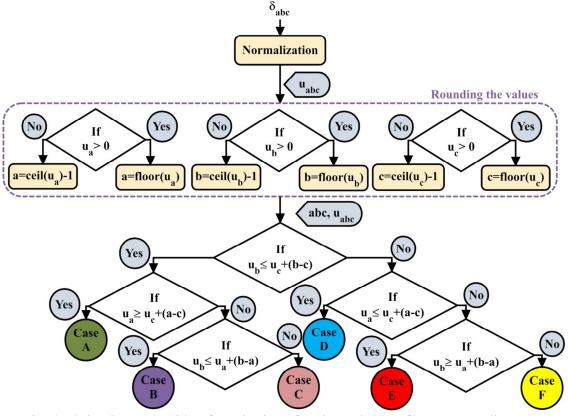

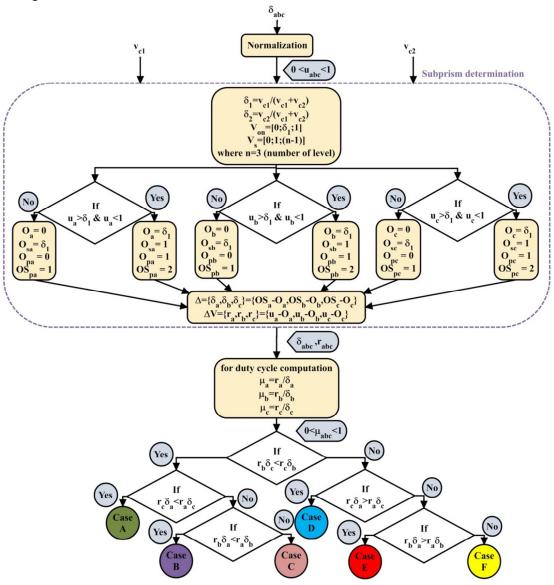

| Figure 4.15 | 3D-SVM algorithm for selection of each tetrahedron for corresponding state vectors                                                     | 32 |

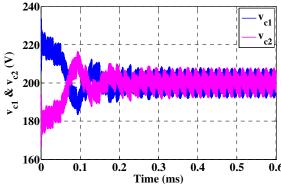

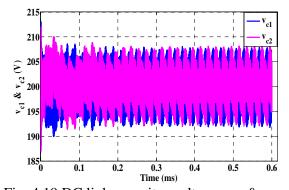

| Figure 4.16 | DC link capacitor voltages vc1 and vc2 balanced by deterministic approach using 3D SVM with initial imbalance condition                | 33 |

| Figure 4.17 | DC link capacitor voltages vc1 and vc2 balanced by deterministic approach using 3D SVM with initial imbalance condition by fine tuning | 33 |

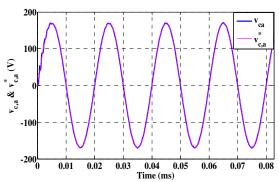

| Figure 4.18 | Output voltage-reference and controlled waveforms for deterministic approach using 3D SVM                                              | 33 |

| Figure 4.19 | DC link capacitor voltages $v_{c1}$ & $v_{c2}$ for deterministic capacitor voltage balancing approach using 3D SVM                     | 33 |

| Figure 4.20 | 3D-feedforward SVM algorithm for selection of each subprism for corresponding state vectors                                            | 34 |

| Figure 4.21 | DC link capacitor voltages vc1 & vc2 balanced by deterministic approach using 3D FFSVM with initial                                    | 35 |

### imbalance condition

| Figure 4.22 | Output voltage-reference and controlled waveforms for deterministic approach using 3D FFSVM                                                                                                                 | 35 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.23 | DC link capacitor voltages $v_{c1}$ & $v_{c2}$ for deterministic capacitor voltage balancing approach using 3D FFSVM                                                                                        | 35 |

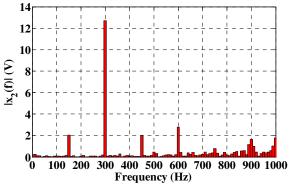

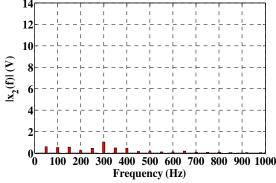

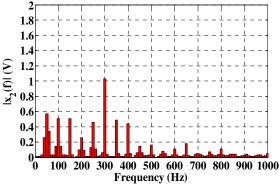

| Figure 4.24 | Single sided amplitude frequency spectrum of $x_2=v_{c1}-v_{c2}$ for redundancy capacitor voltage balancing approach                                                                                        | 36 |

| Figure 4.25 | Single sided amplitude frequency spectrum of $x_2=v_{c1}-v_{c2}$ for deterministic capacitor voltage balancing approach using 3D SVM                                                                        | 36 |

| Figure 4.26 | Single sided amplitude frequency spectrum of $x_2=v_{c1}-v_{c2}$ for deterministic capacitor voltage balancing approach using 3D FFSVM                                                                      | 36 |

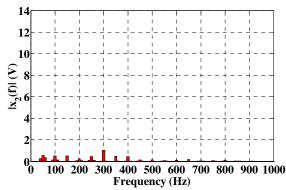

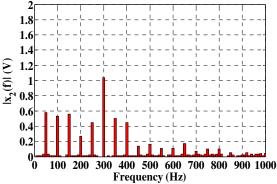

| Figure 4.27 | A zoom preview of single sided amplitude frequency spectrum of $x_2=v_{c1}-v_{c2}$ for deterministic capacitor voltage balancing approach using 3D SVM                                                      | 37 |

| Figure 4.28 | A zoom preview of single sided amplitude frequency spectrum of $x_2=v_{c1}-v_{c2}$ for deterministic capacitor voltage balancing approach using 3D FFSVM                                                    | 37 |

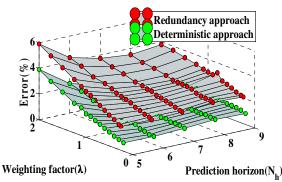

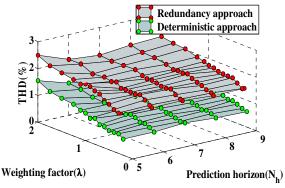

| Figure 4.29 | RMS <sub>error</sub> values between the reference and the measured output voltages for different values of prediction horizons and weighting factors using redundancy and deterministic (3D SVM) approaches | 37 |

| Figure 4.30 | THD values between the reference and the measured output voltages for different values of prediction horizons and weighting factors using redundancy and deterministic (3D SVM) approaches                  | 37 |

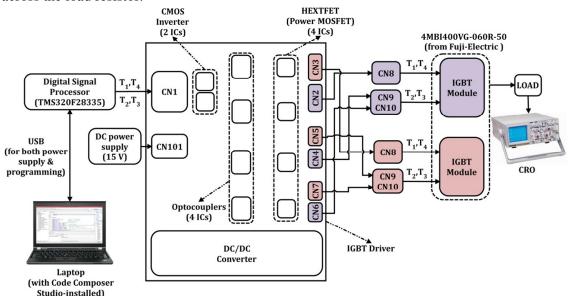

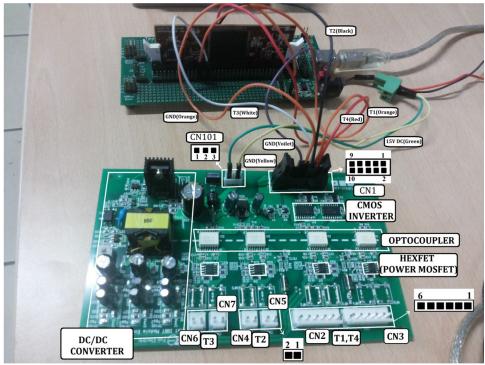

| Figure 5.1  | Block diagram consisting of main components, ICs & connectors for NPP module evaluation              | 38 |

|-------------|------------------------------------------------------------------------------------------------------|----|

| Figure 5.2  | Circuit arrangement showing DSP connected the to the IGBT driver board                               | 39 |

| Figure 5.3  | Connection between the output terminals of the IGBT driver board and the connectors- CN8, CN9 & CN10 | 41 |

| Figure 5.4  | IGBT Drive 1                                                                                         | 41 |

| Figure 5.5  | IGBT Driver 2                                                                                        | 42 |

| Figure 5.6  | IGBT Driver 3                                                                                        | 42 |

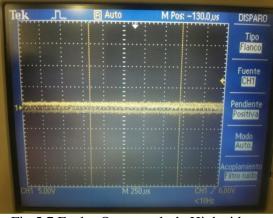

| Figure 5.7  | Faulty Optocoupler's High side voltage output                                                        | 42 |

| Figure 5.8  | Faulty Optocoupler's Low side voltage output                                                         | 42 |

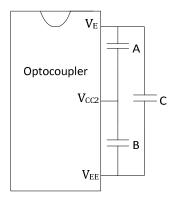

| Figure 5.9  | Optocoupler secondary side power supplies-outline                                                    | 43 |

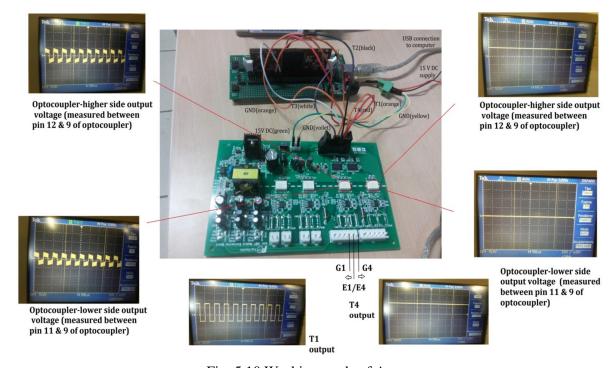

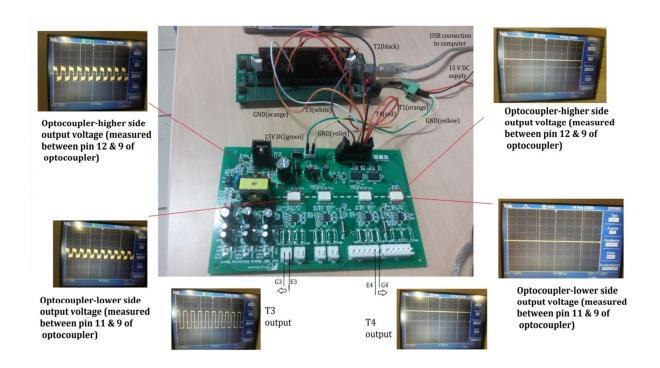

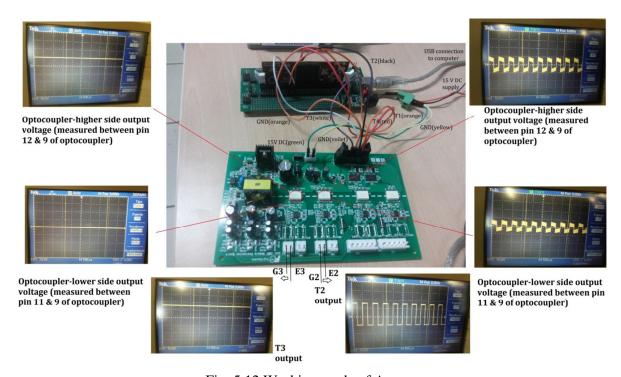

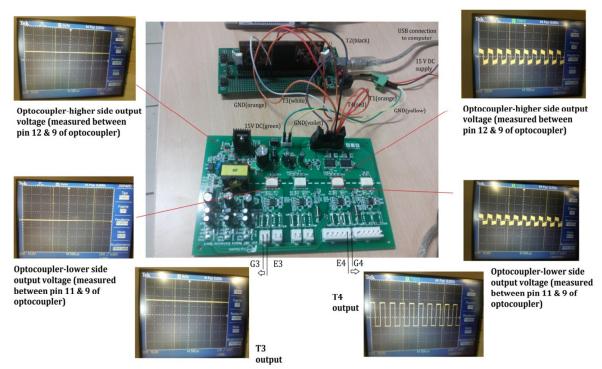

| Figure 5.10 | Working mode of A <sub>1</sub>                                                                       | 44 |

| Figure 5.11 | Working mode of B <sub>1</sub>                                                                       | 45 |

| Figure 5.12 | Working mode of A <sub>2</sub>                                                                       | 45 |

| Figure 5.13 | Working mode of B <sub>2</sub>                                                                       | 46 |

### LIST OF ABBREVATIONS

**AC** – **Alternating Current**

DC – Direct Current

SVM – Space Vector Modulation

2D SVM - Two Dimensional Space Vector Modulation

3D SVM - Three Dimensional Space Vector Modulation

FFSVM - Feed Forward Space Vector Modulation

**PWM** – **P**ulse **W**idth **M**odulation

IGBT – Insulated Gate Bipolar Transistor

RB IGBT - Reverse Blocking Insulated Gate Bipolar Transistor

MOS – Metal Oxide Semiconductor

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

CMOS – Complementary Metal Oxide Semiconductor Field Effect Transistor

SMPS – Switched Mode Power Supplies

LED – Light Emitting Diode

**UPS** – Uninterruptible Power Supplies

NPP – Neutral Point Piloted

NPC – Neutral Point Clamped

MPC – Model Predictive Control

GPC – Generalized Predictive Control

VSI – Voltage Source Inverter

VSC – Voltage Source Converter

**EMC** – Electro-Magnetic Compatibility

**DCC** – **D**iode Clamped Converter

SDCS – Separate DC Source

**CHB** – Cascaded **H-B**ridge

FCC - Flying Capacitor Converter

PS PWM – Phase Shifted Pulse Width Modulation

LS PWM - Level Shifted Pulse Width Modulation

SV PWM – Space Vector Pulse Width Modulation

ANPC – Active Neutral Point Clamped

SHE – Selective Harmonic Elimination

SHM – Selective Harmonic Mitigation

**THD** – **Total Harmonic Distortion**

RMS - Root Mean Square

GA – Genetic Algorithm

**CARIMA** – Controlled Auto-Regressive and Moving-Average

LO – Luenberger Observer

**KCL** – **Kirchhoff's Current Law**

**KVL** – **Kirchhoff's Voltage Law**

PI – Proportional Integral

**DSP** – **D**igital **S**ignal **P**rocessor/**P**rocessing

GPIO – General Purpose Input Output

**EPWM** – Enhanced Pulse Width Modulation

**FFD** – **F**irst **F**ault Detection

PCB - Printed Circuit Board

UVLO – Under Voltage Lock Out

**CRO** – Cathode Ray Oscilloscope

ICs - Integrated Circuits

LPF – Low Pass Filter

### **CHAPTER 1**

### INTRODUCTION

Multilevel converters have become a common solution in applications like integration of renewable energies, electric drives, Uninterruptible Power Supplies (UPS), energy storage systems, etc. [1], [2]. The main reason for using these mature technologies are increased output voltage and reduced harmonic content. Although several multilevel converter topologies exists like Diode Clamped Converter (DCC), Cascaded H-bridge (CHB) converter and Flying Capacitor Converter (FCC), which are mainly used in many high power applications [3], [4], there is a demand of converters which are particularly suitable for low and medium power applications [5].

The Neutral Point Piloted (NPP) [6] converters, also known as T-type power converters are good choice of option, when used in low and medium power Photovoltaic (PV) systems. Other applications of these converters include compact electric drives, small unmanned drones, etc. The T-type power converter has the advantage of using an active bidirectional switch at the dc-link midpoint, thereby making the bridge-leg simpler and with lower number of power devices when compared to conventional Diode Clamped Converters (DCC). Additionally, the efficiency of T-type power converters is excellent for medium switching frequencies from 6 to 20 kHz, which makes it suitable for low power applications.

In our project, the NPP power converter is used as a Voltage Source Inverter (VSI) with output LC filter. The NPP inverter system mainly comprises the semiconductor switches, dc link capacitors, DC sources, filter & load, a modulator and controller. The controllers may be one or many and they mainly serve the purpose of controlling the output voltage and balancing the dc link capacitor voltages.

Model Predictive Control (MPC) is a family of control techniques, which gives fruitful results when applied to power converters [7], [8]. The MPC explicitly uses the system model to predict the output at future time instants, called horizons. A control sequence is calculated at every sampling time in order to minimize an objective function, so that the prediction horizon is displaced towards future. Generalized Predictive Control (GPC) [9] is one of the family members of MPC and it is an indirect control strategy, which tracks the reference in order to control the output voltage, thereby resulting in an effective voltage reference for the modulator.

In order to generate the firing pulses for the semiconductor switches the modulation algorithm is used. The two main modulation techniques are Pulse Width Modulation (PWM) [10] and Space Vector Modulation (SVM). In our project SVM is used. A two dimensional SVM [11] is used when the control strategy is defined in the  $\alpha\beta$  stationary frame; where as either a three dimensional SVM [12] or a three dimensional feedforward SVM [13] is used when the control strategy is defined in the  $\alpha\beta\gamma$  frame.

The dc link capacitor voltage balancing has been a serious challenging problem in multilevel power converters, since its inception. Although many efforts have been made to balance the dc link capacitor voltages [14], [15], researchers are still focusing on optimized solutions, that can eradicate other major issues like ripple reduction, harmonic current minimization and other qualitative parameters of the converter's performance. The sinusoidal disturbances originated from the harmonic currents, incurred during dc link capacitor switching have pulled the researcher's interest [16]. Despite the fascinating adaptive controllers [17], observers and estimators play a vital role in classical control theory, when it comes to deterministic and stochastic control approaches respectively. Once such good option to counter these sinusoidal disturbances, is the use of Luenberger observer [18], which

consequently solves the dc link capacitor voltage balancing problem.

In our project a simple redundancy approach is used when the control strategy is defined in the  $\alpha\beta$  stationary frame; where as a deterministic approach is used when the control strategy is defined in the  $\alpha\beta\gamma$  frame. In the control strategy defined in  $\alpha\beta\gamma$  frame (or three component control), the  $\gamma$ -component is used to balance the dc-link capacitor voltages and to remove the lower order harmonics, occurred during capacitor switching to an acceptable level.

The thesis work primarily addresses the two possible cases in the T-type inverter system, i.e. the case of using separate DC voltage sources and the case of introducing the dc link capacitors. The former case does not need a dc link capacitor voltage balancing strategy and a simple two dimensional SVM scheme is used. The latter one needs a separate control strategy for balancing the dc link capacitors. This case is again discussed into two strategies of balancing the dc link capacitor voltages i.e. the redundancy approach and the deterministic approach. In redundancy approach a simple static relation is considered to solve the dc link capacitor voltage balancing issue, whereas in deterministic approach a Luenberger Observer control scheme is used. In redundancy approach a two dimensional SVM is used, whereas in deterministic approach both three dimensional SVM and three dimensional FFSVM are the possible modulation schemes. It is to be noted that in all the cases a Generalized Predictive Control (GPC) approach is used for tracking output voltage. The GPC calculates the control signals to track the desired output filter capacitor voltages. A comparison of the T-type inverter system's performance is made for the different approaches, in order to understand, investigate and realize the importance of the deterministic approach of capacitor voltage balancing method.

The thesis report mainly comprises eight chapters including the introductory chapter. The 2<sup>nd</sup> chapter gives a basic idea of multilevel inverters, its topologies, various modulation and control schemes. The next chapter throws light on the NPP power inverter, thereby stating its importance. The 4<sup>th</sup> chapter, named 'System description, modeling and control design' is the core work of the thesis, which initially describes the GPC strategy. It also discusses the T-type inverter system in case wise including its modulation-cum-control methodologies. This further includes modeling the inverter system for both GPC design and for deriving the dc link capacitor and inductor dynamics, which are the key concepts in deterministic approach. At the end of this chapter a comparison of the redundancy and the deterministic approaches are discussed. The 5<sup>th</sup> chapter describes the prototype design of the NPP converter and its evaluation. The advantages and applications are discussed in chapter 6. Chapter 7 is inferred with few conclusions and future work. Chapter 8 comprises the references cited.

### **CHAPTER 2**

### **MULTILEVEL INVERTERS**

Industrial applications utilize both high and medium power levels and this is fairly possible only with multilevel converters. So, one can extract many voltage levels from multilevel converters based on his/her application need or interest. The foremost reasons to go for multilevel inverters are to avoid step up transformer during each stage of power conversion and to reduce output harmonics. Such multilevel converters are widely used in integration of renewable energy resources, ships, aviation, traction, Uninterruptible Power Supplies (UPS), High Voltage Direct Current (HVDC) systems, Flexible AC Transmission System (FACTS), variable-frequency drives, electric vehicle drives and air conditioning applications.

### By definition,

'Multilevel inverters are power converters composed by an array of semiconductors and capacitor voltage sources, that when properly controlled, can generate waveform output voltages with adjustable frequency and amplitude'.

Since the inception of multilevel converters [19] during 1975, research and development in multilevel converters have revolutionized much. Firstly, it all began with a simple three level power converter, which later led to development of different topologies and control methods [20]. These revolutions have mainly resulted in possible up-gradations of different topologies, modulation schemes, control methodologies, harmonics reduction possibilities and balancing of dc link capacitor voltages. The basic idea of multilevel converter is to get different output voltage levels by switching the semiconductor switches in an orderly fashion, resulting in a staircase output voltage, which is later inverted by a filter circuit to produce an AC output to be utilized by the load. Turning off a semiconductor switch is called commutation and this commutation is done in an orderly fashion, such that a different voltage levels are achieved at the output. Switching sequences of these semiconductor switches are generated by modulators, which are discussed in detail in section 2.2.

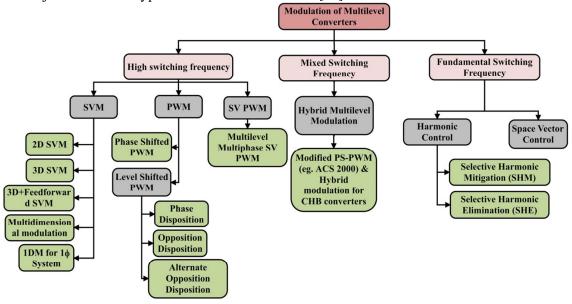

Fig. 2.1. Different multilevel converter topologies

The multilevel power converters have the following advantages:

- ➤ Reduced dv/dt stresses and electromagnetic compatibility (EMC) problems, which improves the staircase waveform quality.

- Smaller Common Mode (CM) voltage

- > Low distortion of input current

- > Operates at both fundamental and high switching frequencies

- ➤ Higher voltage operation (above classic semiconductor limits)

- ➤ Lower voltage distortion (more sinusoidal waveforms)

- Multilevel converters are well suitable for reactive power compensation.

Although multilevel converters are mature technologies, there is always a rising demand in new topologies, modulation schemes and control strategies to counteract one or more drawbacks of conventional one and to go on with a newly proposed converting technology.

### 2.1. INVERTER TOPOLOGIES

Although many topologies and its industrial applications are found in literature [21] [22], the three major multilevel converter types are Neutral Point Clamped (NPC) converter, Cascaded H-Bridge (CHB) converter and Flying Capacitor Converter (FCC). Figure 2.1 shows the classification of multilevel converters [23].

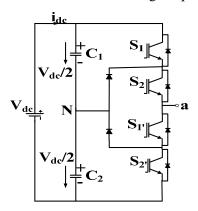

### 2.1.1. NEUTRAL POINT CLAMPED MULTILEVEL INVERTER

The Neutral Point Clamped (NPC) converter was initially proposed by Nabae, Takahashi, and Akagi in 1981 [24], which laid a foundation to the era of voltage source multilevel high power converters. Figure 2.2 shows a single phase NPC for which the switching states are given in Table 2.1. The lower leg switches are the complementary of those of the upper leg switches. The clamping diodes allow the connection of the phase output to the midpoint of the dc link i.e. neutral (N) and this paves a way for three voltage levels. It is to be noted that if 'L' is the number of levels in phase to neutral voltage (V<sub>aN</sub>), then the number of steps in phase to phase voltage (V<sub>ab</sub>) is '2L-1'. The blocking voltage of the power devices is equal to V<sub>dc</sub>/(L-1). NPCs are used for medium and high voltage applications. Integrated Gate Commutated Thyristors (IGCT) or Insulated Gate Bipolar Transistor (IGBT) is commercially used as switching devices. If the converter is for high voltage and high current applications, IGCT is a good choice of option. It is to be noted that IGBT has lower commutation losses and easy drivers, but it has high conduction losses.. Commercial NPCs include ACS 1000, SINAMICS SM120, Altivar 1000, etc. whose maximum power ranges from 10 to 40 MW.

Advantages of multilevel diode-clamped inverters:

- As all of the phases share a common dc bus, the capacitance requirement of the converter gets reduced. Due to this, NPC favors back-to-back regenerative applications.

- ➤ The capacitors can be pre-charged in a group.

- For fundamental switching frequency, the efficiency is high.

Fig. 2.2. A single phase NPC

Table.2.1 Switching states of a three level single phase NPC

| Voltage              | Switching states |       |         |         |

|----------------------|------------------|-------|---------|---------|

| $V_{aN}$             | $S_1$            | $S_2$ | $S_{1}$ | $S_2$ , |

| V <sub>dc</sub> /2   | 1                | 1     | 0       | 0       |

| 0                    | 0                | 1     | 1       | 0       |

| - V <sub>dc</sub> /2 | 0                | 0     | 1       | 1       |

Disadvantages of multilevel diode-clamped inverters:

- Real power flow is difficult for a single inverter because the intermediate dc levels will tend to overcharge or discharge without precise monitoring and control.

- ➤ The inner most devices are switched on for most of the time. To overcome this and maintain a nominal uniformity, the Active Neutral Point Clamped (ANPC) were introduced.

- The total number of clamping diodes required is quadratically related to the number of levels, which can be more complex for units with a high number of levels.

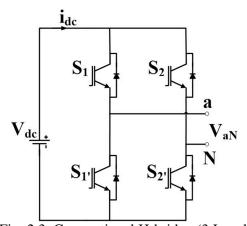

### 2.1.2. CASCADED H-BRIDGE INVERTER

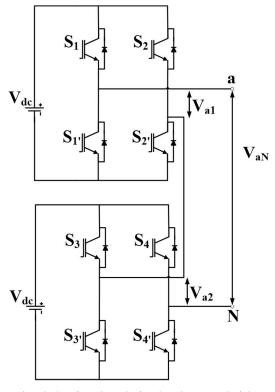

The cascaded H-Bridge converters are first introduced during late 1960s [25], [26], which paved a way to think of using a separate DC source in multilevel converters. As the name 'CHB' defines the use of multiple units of H-bridge power cells, which are connected in series such that the output voltage is the sum of each inverter outputs. Each Separate DC Source (SDCS) is connected to a single-phase full-bridge or H-bridge inverter. A conventional H-bridge cell is shown in the figure 2.3, whose switching states are given in table 2.2. The lower leg switches in each CHB cell are the complementary of the upper leg switches. The H-bridge cells are connected in series to form multilevel cascaded converters. The connection can be symmetrical (using same dc source values) or asymmetrical (using different dc sources). Figure 2.4 shows the leg-scheme of a symmetrical five-level CHB converter, whose switching states are given in the table 2.3.

It is to be noted that, for a 'm' level symmetrical cascaded H-bridge converter the number of dc sources needed is (m-1)/2 & the maximum number of level of line-to-line output voltage is (2m-1). CHB converters are best suitable for large PV-plants, when used with an isolated DC-DC conversion stage [27]. They are ideal for renewable energy integration and traction systems. Commercial CHB converters are available in ABB, Arrow speed & Siemens (Perfect harmony).

Fig. 2.3. Conventional H-bridge (3 Level, single phase) converter

Table.2.2 Switching states of a single phase three level H-Bridge converter

| Voltage,             | Switching states |       |  |  |

|----------------------|------------------|-------|--|--|

| V <sub>aN</sub>      | $S_1$            | $S_2$ |  |  |

| V <sub>dc</sub> /2   | 1                | 0     |  |  |

| 0                    | 0                | 0     |  |  |

| 0                    | 1                | 1     |  |  |

| - V <sub>dc</sub> /2 | 0                | 0     |  |  |

Advantages of cascaded H-bridge inverters:

- ➤ The modular structure or the multiple units of identical H-bridge power cell reduces the manufacturing cost.

- The number of possible output voltage levels is more than twice the number of dc sources

- Less voltage THD and dv/dt when compared to two level converters operating at the same

voltage rating and switching frequency.

➤ H-bridge cells are cascaded to produce high AC voltages, which eliminates the problem of equal voltage sharing for series-connected devices.

Fig. 2.4. Five-level single phase H-bridge converter

| Table.2.3 Switching states of a Five level |

|--------------------------------------------|

| single phase H-Bridge Converter            |

| Voltage,   | Switching states |       |       |                | Individual cell output voltage |                  |  |

|------------|------------------|-------|-------|----------------|--------------------------------|------------------|--|

| $V_{aN}$   | $S_1$            | $S_2$ | $S_3$ | S <sub>4</sub> | $V_{a1}$                       | $V_{a2}$         |  |

| $2V_{dc}$  | 1                | 0     | 1     | 0              | $V_{dc}$                       | $V_{dc}$         |  |

|            | 1                | 0     | 1     | 1              | $V_{dc}$                       | 0                |  |

| $V_{dc}$   |                  | Ů     | 0     | 0              | v dc                           |                  |  |

| ▼ ac       | 1                | 1     | 1     | 0              | 0                              | $V_{dc}$         |  |

|            | 0                | 0     | 1     | U              | O                              | ▼ dc             |  |

|            | 0                | 0     | 0     | 0              |                                |                  |  |

|            | 0                | 0     | 1     | 1              | 0                              | 0                |  |

| 0          | 1                | 1     | 0     | 0              | U                              | U                |  |

| 0          | 1                | 1     | 1     | 1              |                                |                  |  |

|            | 1                | 0     | 0     | 1              | $V_{dc}$                       | $-V_{dc}$        |  |

|            | 0                | 1     | 1     | 0              | -V <sub>dc</sub>               | Vdc              |  |

|            | 0                | 1     | 0     | 0              | -V <sub>da</sub>               | 0                |  |

| V.         |                  | 1     | 1     | 1              |                                | U                |  |

| $-V_{dc}$  | 0                | 0     | 0     | 1              | 0                              | V.               |  |

|            | 1                | 1     | U     | 1              | U                              | $-V_{dc}$        |  |

| $-2V_{dc}$ | 0                | 1     | 0     | 1              | -V <sub>dc</sub>               | -V <sub>dc</sub> |  |

Disadvantage of cascaded H-bridge inverters:

A large number of separate dc sources are required for CHB, which are usually obtained from a multi-phase diode rectifier by employing an expensive phase shifting transformer.

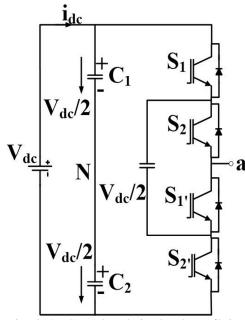

### 2.1.3. FLYING CAPACITOR MULTILEVEL INVERTER

The flying capacitors were first introduced by Meynard and Foch in 1992 [28]. As the name suggests, a capacitor is connected between the upper and the lower leg or between the two cells. In other words, the free-wheeling diodes in NPC are replaced by a capacitor. Figure 2.5 shows a three level single phase FC, which has two cells. Additional cells can be added to increase the number of output levels, but the nominal power of the converter remains the same. It is to be noted that for 'm' voltage level, flying capacitor needs 2(m-1) semiconductor switches, (m-1) DC bus capacitors and (m-1)(m-2)/2 number of balancing capacitors per phase. Table 2.4 shows the switching states of a three-level single phase FC. The phase redundancy switching state-zero voltage is used to control the floating capacitor voltage. A well-known commercial flying capacitor converter is Alstom VDM 6000. ABB's ACS 2000 is an example of hybrid FCC, which is a combination of a 3L-ANPC and a FCC.

Advantages of flying capacitor inverters:

- ➤ Unlike other inverters, switching combination redundancies even in inner voltage levels makes balancing the voltage levels of the capacitors easier and flexible with more switching combinations.

- Real and reactive power flow can be controlled making a possible voltage source converter candidate for high voltage dc transmission [29], [30].

- ➤ Large number of capacitors enables the inverter to ride through capabilities during power rage.

Fig. 2.5. Three-level single phase flying capacitor converter

Table.2.4 Switching states of a three level single phase FCC

| Voltage,            | Switching states |       |

|---------------------|------------------|-------|

| $V_{aN}$            | $S_1$            | $S_2$ |

| V <sub>dc</sub> /2  | 1                | 1     |

| 0                   | 1                | 0     |

| 0                   | 0                | 1     |

| -V <sub>dc</sub> /2 | 0                | 0     |

Disadvantages of flying capacitor inverters:

- ➤ Control is complicated to regulate the voltage levels for all of the capacitors. Also, precharging all of the capacitors to the same voltage level and startup are complex.

- > Inverter control will be very complicated and the switching frequency and switching losses will be high for real power transmission.

- ➤ The large numbers of capacitors are both more expensive and bulky than clamping diodes in multilevel diode-clamped converters. Packaging is also more difficult in inverters with a high number of levels.

Apart from the above topologies, there are Modular Multilevel Converter (MMC) [31], Cascaded Matrix Converter (CMC) [32], [33] and Neutral Point Piloted (NPP) converter [34]. There also exists symmetrical topologies like n-level Cascaded Cell Multilevel Converter (CCMC) [35], [36], which do not have a common dc link; instead they are made of stages, connected in series, which comprises two basic cells in parallel connection. These basic cells share a common DC source or capacitor. Asymmetric topologies also prevail, like Hybrid Multilevel Converter (HMC) [37] where different stages are connected in series, that has different values of DC voltages and Cascade Asymmetric Multilevel Converter (CAMC) [38], which is a combination of ANPC and FC.

In the project work, the NPP or T-type inverter is used & the emphasis lies on it, which is discussed in chapter 3 in detail.

### 2.2. MODULATION SCHEMES

The major modulation schemes are Pulse Width Modulation (PWM), Space Vector Modulation (SVM) & harmonic control. Focus on new and hybrid modulation schemes rely on encountering other issues like using less number of switches, optimizing output voltage control, solving the dc link capacitor voltage balancing problem, reducing or eliminating the harmonic contents, increasing robustness & fault tolerance capability, etc. Figure 2.6 shows the major modulation types in multilevel converters [39].

Fig. 2.6. Various modulation schemes for multilevel converters

Pulse Width Modulation (PWM): The basic idea in PWM is to compare a reference signal with a carrier signal in order to obtain a constant frequency PWM signal, which is used as firing pulses for the semiconductor switches. Numerous developments in optimizing the PWM technique have been done since its inception [10]. In Bipolar PWM (Two level voltage case), a simple triangular carrier signal is compared with a sine reference and those overlapping with the upper and lower carrier signals are given as switching pulses to the lower and upper switches respectively. In Unipolar PWM (used for single phase, three level voltage converter) a triangular carrier signal is compared with two reference sine waves of 180° shifted from each other. The switching pulses obtained from the positive sine wave overlapping are applied to one leg and the switching pulses obtained from the negative sine wave overlapping are applied to the other leg. In Phase shifted PWM (used for FCC or CHB converter) n-1 triangular carrier signals are used with optimal displacement 180°/m (where 'n' is the number of voltage levels and 'm' is the number of cells) are overlapped using a reference sine wave and the switching pulses are given to the converters. The number of carrier signals depends on the number of cells used. For example: In a three level FCC two carrier signals are used whereas in a four level FCC three carrier signals are used. In Level shift PWM the carrier signals are arranged in a vertical shift. For a m-level inverter, (m-1) carrier signals are needed. The below control logics are used in the level shifted PWM used for a three level converter:

- If the reference is above the carriers the upper switches are turn on.

- If the reference is between both carriers the output is connected to the neutral point.

- ➤ If the reference is under both carriers the lower switches are turned on.

In phase disposition, the carrier signals are aligned in a similar fashion, whereas in opposition disposition, the lower carrier signals are 180° phase shifted from the upper signals, whereas

in alternate opposition disposition, the carrier signals are 180° phase shifted from each other.

Space Vector Modulation (SVM): The basic idea of SVM is to switch the semiconductor switches, by locating a reference signal on the Space Vector (SV) of appropriate level and finding the nearest switching vectors and their corresponding switching times. In a 2D SVM [11], the three phase reference is transformed to g-h coordinate system and the closest three vector are found and switched, whereas in a 3D SVM [12], a normalized phase voltage references are located in a three-dimensional space and the closed four vectors are switched. The feedforward 3D SVM [13] takes into account the actual dc-link capacitor voltage imbalance and uses a modulation scheme similar to 3D with slight changes. The 1DM for single phase multilevel converters uses the 1-D control region to identify the possible switching states and their duty cycles [40]. The multidimensional modulation technique is a generalized modulation scheme for cascaded multilevel converters, which determines the switching states on a multidimensional control region [41]. Here, the DC voltage control strategy is used on a 2D control region. One can consider the real values of dc-link capacitor voltages and extend the feedforward mD-PWM scheme for cascaded converters. (where m is the number of cells). In SVPWM technique, the reference voltage vector is resolved by timeaveraging with the nearest active switching vectors. In Multilevel multiphase SVPWM [42], the concept of permutation matrix is introduced, which determines the switching time of the switches.

Hybrid multilevel modulation: Modified carrier-based PWM are used in Active NPCs, where n-1 triangular carriers are used which are phase-shifted by 90°(where n is the number of voltage level). Such modulation schemes are advantageous to balance the dc link capacitor voltages inherently in medium voltage power inverters. In 5L-ANPC a fundamental switching is used for ANPC cell and a phase-shifted PWM is used for the flying-capacitor cell [43].

Space vector control for multilevel converters: The basic idea of space vector control is when using multilevel inverters with high number of levels (which results in high space vector density) there is no need of modulation. Space vector control approximates the reference vector by the closest space vector generated by the inverter. The approximation is compensated by outer loop controllers and the inverter works with low switching frequency.

Harmonic control: In Selective Harmonic Elimination (SHE) [44] the 'n' lower-order odd, nontriplen (non-multiple of 3) harmonics are eliminated by solving a set of m= n+1 equations for fundamental amplitude and 'm' angles. The Selective Harmonic Mitigation (SHM) [45] is based on SHMPWM, that generates switching three-level PWM patterns to meet grid codes with high quality from harmonic perspective, thereby avoiding the elimination of some specific harmonics. Later an optimized SHM [46] is identified by, which are applied to high power converters with low switching frequency. In both the cases the objective functions are optimized by algorithms like Genetic Algorithm (GA), simulated annealing, etc.

The modulation schemes used in the project are 2D SVM, 3D SVM and 3D FFSVM, which are explained in detail in the chapter 4.

### 2.3. CONTROL STRATEGIES

The control strategies comprise concepts like direct power control [47], [48], [49], Model Predictive Control (MPC) [50], [51], hysteresis/non-hysteresis control of current [52], using conventional controllers like PI [53], fuzzy PID [54], neural network & fuzzy logic methods

[55] etc. and other advanced control techniques. Most new works rely and emphasize on strategies like harmonics reduction, dc link capacitor voltage balancing, less computation effort, new efficient control methods, that can solve one or more other issues and increased system performance. For this, one has to undergo a modeling approach to the converter system which is discussed in detail in chapter 4. All these modeling strategies need a prior knowledge of fundamental Clarke [56] & Park [57] transformation. Both the transformations are basically used to simplify the analysis of three phase circuits. The Clarke's transformation is used in the project, which facilitates the inclusion of the third control component i.e. the gamma  $(\gamma)$  or zero (0) component. This  $\gamma$  component is used to solve the dc link capacitor issue in the deterministic approach, which is discussed in detail in chapter 4.

### **CHAPTER 3**

### NEUTRAL POINT PILOTED (NPP) POWER INVERTER

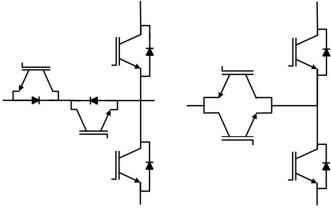

The Neutral Point Piloted converter [58], [59] or the T-type converter is an extension of the conventional two-level Voltage Source Converter (VSC) with an active bidirectional switch to the dc-link midpoint, which blocks only half of the dc link voltage. Figure 3.1 (a) shows the leg schematic of a three-level T-type power converter, whose bidirectional switches are conventional IGBTs. Hence, it can be implemented with devices having a lower voltage rating. Due to this feature, the converter shows very low switching losses, acceptable conduction losses and lower number of semiconductor devices, when compared to conventional topologies like NPC and FCC. Although the T-type converters were introduced during 1985 [60], owing to demand in rise of compact and efficient low power converters, various developments are made in these T-type converters to be more reliable and fault tolerant [61], [62].

Later these conventional AC switches were replaced by Reverse blocking IGBT (RB-IGBT) [63] which has low switching losses and better reverse blocking capability. When seen from fabrication perspective, the module with RB-IGBT has only one pn-junction and this reduces the reverse recovery. Figure 3.1(b) shows the leg schematic of a three-level T-type power converter, whose bidirectional switches are RB-IGBT.

Fig. 3.1. Leg schematic of a three-level T-type power inverter : (a) bidirectional switch with conventional IGBT, (b) bidirectional switch with RB-IGBT

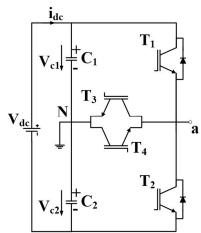

Table 3.1. Switching states of a single phase T-type converter

| Voltage,            | Switching states |       |       |       |

|---------------------|------------------|-------|-------|-------|

| $V_{aN}$            | $T_1$            | $T_2$ | $T_3$ | $T_4$ |

| V <sub>dc</sub> /2  | 1                | 0     | 0     | 0     |

| 0                   | 0                | 0     | 1     | 1     |

| -V <sub>dc</sub> /2 | 0                | 1     | 0     | 0     |

Fig. 3.2. Leg schematic of a single phase three level T-type converter

Figure 3.2 shows the circuit of a single phase T-type inverter. Table 3.1 shows the switching states of the T-type converter. Additionally, these T-type inverters are promising power conversion topologies for medium switching frequencies from 6-20 kHz. There T-type inverters are used in applications of low or medium power like small PV-systems and standalone applications [58], [59].

### **CHAPTER 4**

### SYSTEM DESCRIPTION, MODELING & CONTROL DESIGN

This chapter is the core work of thesis, that discusses on various aspects of how the output voltage is controlled and the capacitor voltage balance is achieved. The chapter is divided into three sub-chapters, which discusses initially about the Generalized Predictive Control (GPC) of output voltage control. Then, the topic on application of the GPC on the T-type inverter with individual voltage sources is discussed. The next part of the chapter explains how the dc link capacitor voltage balancing problem is solved by two approaches i.e. redundancy and deterministic approach. At last a comparison on system performance is done on these two approaches.

### 4.1. GPC STRATEGY FOR OUTPUT VOLTAGE CONTROL

The output voltage control is the primary objective, which is implemented by the Model Predictive Control (MPC) approach [64]. The MPC calculates the control signals to track the desired output capacitor AC voltages. These control signals are the  $\delta_{\alpha\beta}$  component, which are the effective multiple of the reference voltage for the modulators.

MPC is a family of control techniques that has been successfully applied to power converter applications [65], [66]. The MPC strategy is based on explicitly using a model of the power inverter system to predict the process output at future time instants (called horizons). A control sequence is calculated in order to minimize an objective function and receding strategy is used, so that at each sampling instant the prediction horizon is displaced towards the future [67].

The GPC strategy, proposed by Clarke et al. is a well know control strategy in MPC family [9]. GPC favors many advantages like robustness and reasonable number of design variables intrusion, when applied to power converters.

GPC is based on predicting the output by using a Controlled Auto-Regressive and Moving-Average (CARIMA) model:

$$A(z^{-1})y(t) = B(z^{-1})z^{-d}u(t-1) + C(z^{-1})\frac{e(t)}{\Delta}$$

(1) where  $y(t)$  is the output of the system,  $u(t)$  is the control sequence,  $d$  is the dead time or delay

of the system, e(t) is the zero mean white noise and  $\Delta = (1-z^{-1})$ . A, B and C are the polynomials in backward shift operator  $z^{-1}$ , which are obtained from the system transfer function.

When applying the GPC strategy to the T-type inverter system, the dead time, d is equal to 0 and for simplicity, the noise polynomial  $C(z^{-1})$  is considered to be equal to 1. The CARIMA model for the inverter system becomes,

$$A(z^{-1})y(t) = B(z^{-1})u(t-1) + C(z^{-1})\frac{v(t)}{\Delta}$$

where y(t) is the output voltage & v(t) is an additive white Gaussian noise. (2)

The optimal prediction is done by solving the Diophantine equation, whose solution is obtained by recursive algorithm. This algorithm uses the transfer function model of the system. The Diophantine equation is given by,

$$C(z^{-1}) = E_j(z^{-1})\tilde{A}(z^{-1}) + z^{-j}F_j(z^{-1})$$

(3)

where  $E_j$  and  $F_j$  are the polynomial obtained by dividing 1 by  $\tilde{A}(z^{-1})$  until the remainer can be factorized as  $z^{-j}F_j(z^{-1})$ , j is the value of prediction horizon and  $\tilde{A}(z^{-1}) = \Delta A(z^{-1})$ .

Applying the Diophantine equation to the T-type inverter system, the noise polynomial,  $C(z^{-1})$ is taken as 1 (as considered before),

$$1 = E_i(z^{-1})\tilde{A}(z^{-1}) + z^{-j}F_i(z^{-1})$$

(4)

A control sequence is applied that minimizes a multistage cost function, which is of the form,

$$J(N_1, N_2, N_u) = \sum_{j=N_1}^{N_2} \delta(j) [\hat{y}(t+j|t) - w(t+j)]^2 + \sum_{j=1}^{N_u} \lambda(j) [\Delta u(t+j-1)]^2$$

(5) where  $N_I$  is the minimum costing horizon,  $N_2$  or  $N_h$  is the maximum costing horizon,  $N_u$  is the control horizon,  $w(t+j)$  is the future reference trajectory,  $\delta(j)$  and  $\lambda(j)$  are the weighting sequences &  $\hat{y}(t+j|t)$  is an optimum j step ahead prediction of the system output on data up

When the cost function is applied to the T-type inverter system, it get minimized to,

$$J = \sum_{j=1}^{N_h} [\hat{y}(t+j|t) - w(t+j)]^2 + \sum_{j=1}^{1} \lambda(j) [\Delta u(t+j-1)]^2$$

where control horizon,  $N_u$ =1 and the initial cost horizon,  $N_l$ =1. (6)

When (2) is multiplied by  $\Delta E_i(z^{-1})z^j$ ,

to time t.

$$\tilde{A}(z^{-1})E_j(z^{-1})y(t+j) = E_j(z^{-1})B(z^{-1})\Delta u(t+j-1) + E_j(z^{-1})v(t+j)$$

Substituting (4) in (7),

$$y(t+j) = F_i(z^{-1})y(t) + E_i(z^{-1})B(z^{-1})\Delta u(t+j-1) + E_i(z^{-1})v(t+j)$$

(8)

where the polynomial  $E_i(z^{-1})$  is of degree (j-1), the noise components are all in the future, so the optimal prediction is given by,

$$y(t+j|t) = F_j(z^{-1})y(t) + G_j(z^{-1})\Delta u(t+j-1)$$

(9)

where j>1 and  $G_i(z^{-1}) = E_i(z^{-1})B(z^{-1})$ .

The aim of the GPC is to compute the future control sequence u(t), u(t+1),... in such a way that the future voltage output, y(t+j) coincides with the reference trajectory w(t+j). Let us consider a definite prediction horizon (say for instance j = 1,2,...,N) during which, a sequence of future control signals is calculated at each sampling instant until the output is close to the reference.

When (9) is considered for a set of j ahead optimal predictions and expressed in terms that depend only on past values and others which are dependent on the future control signals as

$$y = Gu + f \tag{10}$$

The cost function J obtained by substituting (10) in (6),

$$J = (Gu + f - w)^{T} (Gu + f - w) + \lambda u^{T} u$$

(11)

where, G matrix describes the system dynamics, f is the free response of the system, w is the reference sequence or future set-point and u is the future control input with the following vectors,

The minimal cost function, J can be obtained by making its gradient equal to zero.

$$\frac{\partial \mathbf{J}}{\partial \mathbf{u}} = 0 \tag{12}$$

where u is the increment of control signal applied at each sampling instant, which leads to,

$$u = (G^{T}G + \lambda I)^{-1}G^{T}(w - f)$$

(13)

The control signal that is actually sent as input to the system is the first element of vector u, which is given by

$$\Delta \mathbf{u}(\mathbf{t}) = \mathbf{K}(\mathbf{w} - \mathbf{f}) \tag{14}$$

where K is the vector of first row of matrix  $(G^TG+\lambda I)^{-1}G^T$

The steps are repeated at each sampling instant. There will be no change in the control signal, if there exists no future prediction errors, i.e., if (w-f) = 0. It is to be noted that, all these computational steps (up to finding the K vector) are done explicitly during initiation of simulation [68].

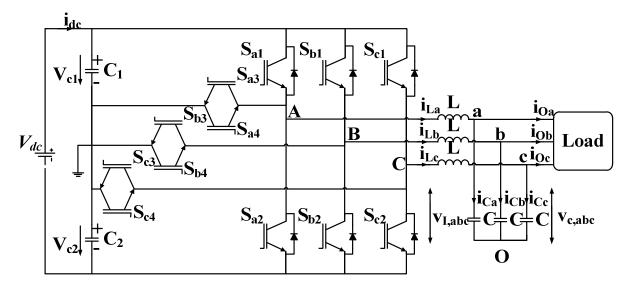

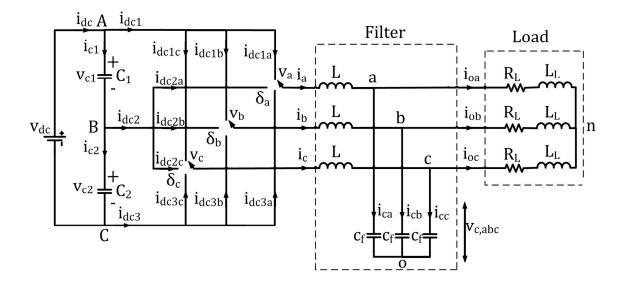

Fig. 4.1. Scheme of T-type converter connected to load via LC filter

The figure 4.1 shows the scheme of the T-type converter connected to a RL load via a LC filter [69], whose descriptions are given in table 4.1. Table 4.2 consists of the model and simulated parameters. It is to be noted that the load resistance,  $R_1$  used in actual simulation is 15  $\Omega$ , whereas the  $R_1$  used in model is 60  $\Omega$ . This is a model mismatch and the GPC is later notified for tackling this situation well, thereby predicting the output voltage across the filter capacitor.

The dynamic equations of the output filter inductor currents and the output filter capacitor voltages are as follows,

$$i_{L,abc} = C \frac{dv_{C,abc}}{dt} + i_{O,abc}$$

(15)

$$V_{I,abc} = L \frac{di_{L,abc}}{dt} + V_{C,abc}$$

(16)

Table 4.1 System Variables and Parameters

| Variable                                                    | Description                            |  |

|-------------------------------------------------------------|----------------------------------------|--|

| $V_{C,abc} = \left\{ v_{aO} \ v_{bO} \ v_{cO} \right\}^{T}$ | Output filter capacitor voltage vector |  |

| $i_{L,abc} = \left\{ i_{La} \ i_{Lb} \ i_{Lc} \right\}^{T}$ | Output filter inductor current vector  |  |

| $V_{I,abc} = \left\{ v_{AO} \ v_{BO} \ v_{CO} \right\}^{T}$ | T-type output voltage vector           |  |

| $i_{O,abc} = \left\{i_{Oa} i_{Ob} i_{Oc}\right\}^{T}$       | Output load current vector             |  |

| $S_{abc} = \left\{ S_a S_b S_c \right\}^T$                  | Switching vector                       |  |

| $S_{p \mid p=\{a, b, c\}} = \{-1, 0, 1\}$                   | Switching functions                    |  |

| L                                                           | Output filter inductance               |  |

| С                                                           | Output filter capacitance              |  |

| $V_{dc}$                                                    | dc-link voltage                        |  |

| $i_{ m dc}$                                                 | dc-link current                        |  |

| $C_1, C_2$                                                  | dc-link capacitance                    |  |

Table 4.2 Model & Simulation Parameters for GPC

| Parameter                                       | Value      |

|-------------------------------------------------|------------|

| Output filter inductance, L                     | 2mH        |

| Output filter capacitance, C                    | 50μF       |

| Switching frequency, f <sub>sw</sub>            | 10kHz      |

| Output load resistance (model), R <sub>1</sub>  | $60\Omega$ |

| Output load resistance (actual), R <sub>1</sub> | 15Ω        |

| $ m V_{dc}$                                     | 400V       |

| Output voltage reference, V <sub>RMS</sub>      | 120V       |

| Weighting factor, λ                             | 0.95 (say) |

| Control horizon, N <sub>u</sub>                 | 1          |

| Prediction horizon, N                           | 6 (say)    |

### GPC formulation (for example)

Transfer function of the inverter system considering the output filter and load is given by,

$$H(s) = \frac{Y(s)}{U(s)} = \frac{1}{LCs^2 + \frac{L}{R_l}s + 1} = \frac{1}{(2 \times 10^{-3} \times 50 \times 10^{-6})s^2 + (\frac{2 \times 10^{-3}}{60})s + 1} = \frac{1}{10^{-7}s^2 + 3.333 \times 10^{-5}s + 1}$$

Discretizing the system or taking Z-transform,

$$H(z^{-1}) = \frac{B(z)}{A(z)} = \frac{0.04904 z + 0.0485}{z^{2} - 1.8697 z + 0.9672}$$

$$H(z^{-1}) = \frac{B(z^{-1})}{A(z^{-1})} = 1/z(\frac{0.04904 + 0.0485z^{-1}}{1 - 1.8697z^{-1} + 0.9672z^{-2}})$$

where,

$$A(z^{-1}) = 1 - 1.8697z^{-1} + 0.9672z^{-2}$$

$B(z^{-1}) = 0.0490 + 0.0485z^{-1}$

$$C(z^{-1}) = 1$$

(noise polynomial)

$$\widetilde{A}(z^{-1}) = \Delta A(z^{-1}) = (1 - z^{-1})A(z^{-1}) = (1 - z^{-1})(1 - 1.8697z^{-1} + 0.9672z^{-2}) = 1 - 2.8697z^{-1} + 2.8369z^{-2} - 0.9672z^{-3}$$

The polynomials of the Diophantine equations are determined using the below recursive calculation steps.

Table 4.3 GPC recursive polynomial calculation across horizons

# Prediction Horizon 1 $E_1 = 1$ $F_1 = z(1 - E_1\tilde{A}) = z[1 - (1 - 2.8697z^{-1} + 2.8369z^{-2} - 0.9672z^{-3})]$ $= 2.8697 - 2.8369z^{-1} + 0.9672z^{-2}$ $G_1 = B(z^{-1})E_1 = (0.0490 + 0.0485z^{-1}) \times 1 = 0.0490 + 0.0485z^{-1}$ Prediction Horizon 2 $E_2 = E_1 + (F_1, 0)z^{-1} = 1 + 2.8697z^{-1}$ $F_2 = z^2(1 - E_2\tilde{A}) = z^2[1 - (1 + 2.8697z^{-1}) \times (1 - 2.8697z^{-1} + 2.8369z^{-2} - 0.9672z^{-3})]$ $= 5.3982 - 7.1738z^{-1} + 2.7756z^{-2}$ $G_2 = B(z^{-1})E_2 = (0.0490 + 0.0485z^{-1}) \times (1 + 2.8697z^{-1}) = 0.0490 + 0.1892z^{-1} + 0.1392z^{-2}$ Prediction Horizon 3 $E_3 = E_2 + (F_2, 0)z^{-2} = 1 + 2.8697z^{-1} + 5.3982z^{-2}$ $F_3 = z^3(1 - E_3\tilde{A})$ $= z^3[1 - (1 + 2.8697z^{-1} + 5.3982z^{-2}) \times (1 - 2.8697z^{-1} + 2.8369z^{-2} - 0.9672z^{-3})]$

$$= z^{3}[1 - (1 + 2.8697z^{-1} + 5.3982z^{-2}) \times (1 - 2.8697z^{-1} + 2.8369z^{-2} - 0.9672z^{-3})$$

$$= 8.3173 - 12.5385z^{-1} + 5.2212z^{-2}$$

$$G_{3} = B(z^{-1})E_{3} = (0.0490 + 0.0485z^{-1}) \times (1 + 2.8697z^{-1} + 5.3982z^{-2})$$

$$= 0.0490 + 0.1892z^{-1} + 0.4039z^{-2} + 0.2618z^{-3}$$

### Prediction Horizon 4

$$\begin{split} E_4 &= E_3 + (F_3,0)z^{-3} = 1 + 2.8697z^{-1} + 5.3982z^{-2} + 8.3173z^{-3} \\ F_4 &= z^4 \big(1 - E_4 \tilde{A}\big) \\ &= z^4 \big[1 - \big(2.8697z^{-1} + 5.3982z^{-2} + 8.3173z^{-3}\big) \times \big(1 - 2.8697z^{-1} + 2.8369z^{-2} - 0.9672z^{-3}\big)\big] \\ &= 11.3294 - 18.3740z^{-1} + 8.0446z^{-2} \\ G_4 &= B\big(z^{-1}\big)E_4 = \big(0.0490 + 0.0485z^{-1}\big) \times \big(2.8697z^{-1} + 5.3982z^{-2} + 8.3173z^{-3}\big) \\ &= 0.0490 + 0.1892z^{-1} + 0.4039z^{-2} + 0.6697z^{-3} + 0.4034z^{-4} \end{split}$$

### Prediction Horizon 5

$$E_5 = E_4 + (F_4, 0)z^{-4} = 1 + 2.8697z^{-1} + 5.3982z^{-2} + 8.3173z^{-3} + 11.3294z^{-4}$$

$$F_5 = z^5(1 - E_5\tilde{A})$$

$$= z^5[1 - (1 + 2.8697z^{-1} + 5.3982z^{-2} + 8.3173z^{-3} + 11.3294z^{-4}) \times (1 - 2.8697z^{-1} + 2.8369z^{-2} - 0.9672z^{-3})]$$

$$= 14.1378 - 24.0958z^{-1} + 10.9580z^{-2}$$

$$G_5 = B(z^{-1})E_5 = (0.0490 + 0.0485z^{-1}) \times (1 + 2.8697z^{-1} + 5.3982z^{-2} + 8.3173z^{-3} + 11.3294z^{-4})$$

$$= 0.0490 + 0.1892z^{-1} + 0.4039z^{-2} + 0.6697z^{-3} + 0.9589z^{-4} + 0.5494z^{-5}$$

### Prediction Horizon 6

$$\begin{split} E_6 &= E_5 + (F_5,0)z^{-5} = 1 + 2.8697z^{-1} + 5.3982z^{-2} + 8.3173z^{-3} + 11.3294z^{-4} + 14.1378z^{-5} \\ F_6 &= z^6 (1 - E_6 \tilde{A}) \\ &= z^6 [1 - (1 + 2.8697z^{-1} + 5.3982z^{-2} + 8.3173z^{-3} + 11.3294z^{-4} + 14.1378z^{-5}) \times (1 - 2.8697z^{-1} + 2.8369z^{-2} - 0.9672z^{-3})] \\ &= 16.4752 - 29.1496z^{-1} + 13.6743z^{-2} \\ G_6 &= B(z^{-1})E_6 \\ &= (0.0490 + 0.0485z^{-1}) \times (1 + 2.8697z^{-1} + 5.3982z^{-2} + 8.3173z^{-3} + 11.3294z^{-4} + 14.1378z^{-5}) \\ &= 0.0490 + 0.1892z^{-1} + 0.4039z^{-2} + 0.6697z^{-3} + 0.9589z^{-4} + 1.2427z^{-5} + 0.6856z^{-6} \end{split}$$

The predicted output calculated for values from j=1 to j=6 and is given by,

$$y = Gu + F(z^{-1})y(t) + G'(z^{-1})\Delta u(t-1)$$

with

$$G = \begin{pmatrix} 0.0490 & 0 & 0 & 0 & 0 & 0 \\ 0.1892 & 0.0490 & 0 & 0 & 0 & 0 \\ 0.4039 & 0.1892 & 0.0490 & 0 & 0 & 0 \\ 0.6697 & 0.4039 & 0.1892 & 0.0490 & 0 & 0 \\ 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 & 0 \\ 1.2427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \end{pmatrix}; F = \begin{pmatrix} 2.8697 & -2.8369 & 0.9672 \\ 5.3982 & -7.1738 & 2.7756 \\ 8.3173 & -12.5385 & 5.2212 \\ 11.3294 & -18.3740 & 8.0446 \\ 14.1378 & -24.0958 & 10.9580 \\ 16.4752 & -29.1496 & 13.6743 \end{pmatrix};$$

$$G' = \begin{pmatrix} 0.0485 \\ 0.1392 \\ 0.2618 \\ 0.4034 \\ 0.5494 \\ 0.6856 \end{pmatrix}$$

where G' is the matrix of coefficients of the right-most backward shift operator of  $G_j$ , where j takes the value 1 to  $N_h$  or  $N_2$  (prediction horizon).

$$K = \text{first row of } (G^T G + \lambda I)^{-1} G^T$$

= first row of

$$\left( \begin{pmatrix} 0.0490 & 0 & 0 & 0 & 0 & 0 \\ 0.1892 & 0.0490 & 0 & 0 & 0 & 0 \\ 0.4039 & 0.1892 & 0.0490 & 0 & 0 & 0 \\ 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 & 0 \\ 1.2427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \end{pmatrix}^{T} \begin{pmatrix} 0.0490 & 0 & 0 & 0 & 0 & 0 \\ 0.1892 & 0.0490 & 0 & 0 & 0 & 0 \\ 0.4039 & 0.1892 & 0.0490 & 0 & 0 & 0 \\ 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 & 0 \\ 1.2427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \end{pmatrix}^{T} \begin{pmatrix} 0.0490 & 0 & 0 & 0 & 0 \\ 0.1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 1 \end{pmatrix}^{T} \begin{pmatrix} 0.0490 & 0 & 0 & 0 & 0 \\ 0.1892 & 0.0490 & 0 & 0 & 0 \\ 0.04039 & 0.1892 & 0.0490 & 0 & 0 \\ 0.0589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \end{pmatrix}^{T} \begin{pmatrix} 0.0490 & 0 & 0 & 0 & 0 \\ 0.1892 & 0.0490 & 0 & 0 & 0 \\ 0.04039 & 0.1892 & 0.0490 & 0 & 0 \\ 0.0589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0.9589 & 0.6697 & 0.4039 & 0.1892 & 0.0490 \\ 0.12427 & 0$$

$$= \text{first row of} \begin{pmatrix} 0.0256 & 0.0817 & 0.1349 & 0.1654 & 0.1646 & 0.1317 \\ -0.0172 & -0.0274 & 0.0001 & 0.0485 & 0.1061 & 0.1646 \\ -0.0099 & -0.0467 & -0.0688 & -0.0334 & 0.0485 & 0.1654 \\ -0.0048 & -0.0230 & -0.0609 & -0.0688 & 0.0001 & 0.1349 \\ -0.0017 & -0.0084 & -0.0230 & -0.0467 & -0.0274 & 0.0817 \\ -0.0003 & -0.0017 & -0.0048 & -0.0099 & -0.0172 & 0.0256 \\ \end{pmatrix}$$

$K = (0.0256 \ 0.0817 \ 0.1349 \ 0.1654 \ 0.1646 \ 0.1317)$

Expression for control law is given by,

$$\Delta u(t) = K(w - f)$$

$\begin{pmatrix} w(t+1) \\ w(t+2) \\ w(t+3) \\ w(t+3) \\ w(t+5) \\ w(t+6) \end{pmatrix} = \begin{pmatrix} 0.0485\Delta u(t-1) + 2.855y(t) - 2.8369y(t-1) + 0.9672y(t-2) \\ 0.1392\Delta u(t-1) + 5.3982y(t) - 7.1738y(t-1) + 2.7756y(t-2) \\ 0.2618\Delta u(t-1) + 8.3173y(t) - 12.5385y(t-1) + 5.2212y(t-2) \\ 0.4034\Delta u(t-1) + 11.3294y(t) - 18.3740y(t-1) + 8.0446y(t-2) \\ 0.5494\Delta u(t-1) + 14.1378y(t) - 24.0958y(t-1) + 10.9580y(t-2) \\ 0.6856\Delta u(t-1) + 16.4752y(t) - 29.1496y(t-1) + 13.6743y(t-2) \end{pmatrix}$

=

$\begin{pmatrix} 0.0256 \, w(t+1) - 0.0012416 \, \Delta u(t-1) - 0.073088 \, y(t) + 0.07262464 \, y(t-1) - 0.02476032 \, y(t-2) + \\ 0.0817 \, w(t+2) - 0.01137264 \, \Delta u(t-1) - 0.44103294 \, y(t) + 0.58609946 \, y(t-1) - 0.22676652 \, y(t-2) + \\ 0.1349 \, w(t+3) - 0.03531682 \, \Delta u(t-1) - 1.12200377 \, y(t) + 1.69144365 \, y(t-1) - 0.70433988 \, y(t-2) + \\ 0.1654 \, w(t+4) - 0.06672236 \, \Delta u(t-1) - 1.87388276 \, y(t) + 3.0390596 \, y(t-1) - 1.33057684 \, y(t-2) + \\ 0.1646 \, w(t+5) - 0.09043124 \, \Delta u(t-1) - 2.32708188 \, y(t) + 3.96616868 \, y(t-1) - 1.8036868 \, y(t-2) + \\ 0.1317 \, w(t+6) - 0.09029352 \, \Delta u(t-1) - 2.16978384 \, y(t) + 3.83900232 \, y(t-1) - 1.80090531 \, y(t-2) + \\ 0.0256 \, w(t+1) + 0.0817 \, w(t+2) + 0.1349 \, w(t+3) + 0.1654 \, w(t+4) + 0.1646 \, w(t+5) + 0.1317 \, w(t+6) \end{pmatrix}$

Note: A similar calculation is carried out for prediction horizons 5, 7, 8 & 9 with a range of weighting factors  $\lambda$  and the comparison is made to extract the one with best pair of weighting factors and prediction horizon.

The output of GPC yields to the control component  $\delta_{\alpha\beta}$ , which is used as reference for modulation.

### 4.2. T-TYPE INVERTER SYSTEM WITH INDIVIDUAL VOLTAGE SOURCES

In this case separate dc voltage sources of each 200 V is used at the dc link instead of capacitors, so that there is no necessity of using a separate control strategy for balancing the dc link capacitor voltages. Figure 4.2 shows the block diagram of the T-type inverter system, when individual dc voltage sources are used. The control signal  $\delta_{abc}$ , obtained from the GPC-strategy, discussed in the section 4.1 is first transformed to  $\delta_{\alpha\beta}$ , which is then transformed to  $\delta_{gh}$  using the transformations (17) & (18) and normalized to  $\frac{(n-1)}{v_{dc}}$ , where n(=3) is the number of levels of the inverter &  $v_{dc}$  (= $v_{dc1}+v_{dc2}$ =400 V) is the DC source voltage. It is to be noted that as  $\delta_{\gamma}$  is not needed here in the case of T-type inverter system with individual voltage sources. Hence, it is neglected.

$$T_{abc}^{\alpha\beta\gamma} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix}$$

(17)

$$T_{\alpha\beta}^{gh} = \begin{bmatrix} 1 & \frac{-2}{\sqrt{3}} \\ 0 & \frac{2}{\sqrt{3}} \end{bmatrix} \tag{18}$$

(17) is the power variant form of Clarke's transformation, where the gain is  $\sqrt{3}$ . In ordinary Clarke's transformation the gain is 2/3. In order to make the transformation matrix unitary i.e.

the inverse matrix coincides with its transpose and to preserve the active and reactive power one has to consider power invariant form of Clarke's transformation.

Fig. 4.2. Block diagram of the T-type inverter system with separate dc voltage sources

Once the control signal (or reference for modulator),  $\delta_{gh}$  is obtained, it is sent to the modulator to get the firing pulses for the semiconductor switches. The modulation strategy used here is two-dimensional SVM [11]. This involves finding the nearest three coordinates in the two-dimensional space vector coordinate system and switching the corresponding vectors, with their respective duty cycles. It is done by rounding the values and doing a simple comparison in the two dimensional coordinate system. After finding the diagonal vectors of the parallelogram, another simple comparison is done to find if the reference,  $\delta_{gh}$  is in the upper triangle or in the lower triangle, as shown in the figure 4.3. Once all the three coordinates in the g-h coordinate system are obtained, the duty cycles are computed and the switching pulses are generated for the IGBT switches. Figure 4.4 shows the 2D SVM algorithm.

Fig. 4.3. Parallelogram comprising two equal triangles

Fig. 4.4. Two dimensional Space Vector Modulation algorithm

It is to be noted that the two dimensional SVM is very fast and computationally efficient, which can be extended to n-level three phase converters. Figure 4.5 shows the reference and the actual output voltage of GPC control during simulation, which reveals the efficiency in tracking the reference and the performance of GPC to tackle the mismatch of model parameter.

Fig. 4.5 Output voltage-reference and controlled waveforms for the T-type inverter system with individual dc voltage sources

### 4.3. T-TYPE INVERTER SYSTEM USING INDIVIDUAL DC LINK CAPACITORS

In this case the dc sources are replaced by separate dc link capacitors and this needs a separate control strategy for balancing the dc link capacitor voltages. The efficiency of the control strategy relies on system performance parameters like computational effort, harmonic reduction and good tracking of the output voltage. There are two dc link capacitor voltage balancing approaches i.e. the redundancy approach and the deterministic approach, whose performances are simulated and compared.

### 4.3.1. REDUNDANCY DC LINK CAPACITOR VOLTAGE BALANCING APPROACH

In this approach, an extra redundancy block is used, that facilitates a simple static comparison [70], [71], [72] of the dc link capacitor voltages and current as shown in the figure 4.6. According to this comparison result, the redundancy of the inner level switching vectors in a three level converter is used and appropriate switching is done as shown in the table 4.4. Figure 4.7 shows the possible switching states of a three level converter. The inverter has three states per phase and as there are three phases,  $3^3$ =27 different switching states exists. It is to be noted that the redundancy exists in the inner level vectors-  $V_1$ ,  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  &  $V_6$  in a three level space vector. For example- consider the vector  $V_7$  (+, 0, -), which denotes that, phase a is connected to the positive terminal, phase b is connected to the dc link mid-point and phase c is connected to the negative terminal. In zero vector ( $V_0$ ) the magnitude of voltage is 0V. In the internal vectors ( $V_1$  to  $V_6$ ) the magnitude of voltage is  $\frac{v_{dc}}{3}$  V. The middle vectors ( $V_7$  to  $V_{12}$ ) have magnitude of  $\frac{v_{dc}}{\sqrt{3}}$ V, whereas the external vectors ( $V_{13}$  to  $V_{18}$ ) have the magnitude of  $\frac{v_{dc}}{\sqrt{3}}$ V.

Fig. 4.6. Block diagram of the T-type inverter system with redundancy dc link capacitor voltage balancing approach

Table 4.4 Redundancy control strategy to balance the dc link capacitor voltages

| Voltage imbalance     | DC link current | Internal redundancy     |

|-----------------------|-----------------|-------------------------|

| $(v_{c1}-v_{c2}) < 0$ | $i_{dc} < 0$    | Positive redundancy (0) |

|                       | $i_{dc} > 0$    | Negative redundancy (1) |

| $(v_{c1}-v_{c2}) > 0$ | $i_{dc} < 0$    | Negative redundancy (1) |

|                       | $i_{dc} < 0$    | Positive redundancy (0) |

Fig. 4.7. Switching state vectors of a three level converter

It is to be noted that a two-dimensional SVM is used, as discussed in the section 4.2. The GPC strategy used is the same as the one discussed in section 4.1. On performing a series of simulation experiments, it is found that the GPC performs well when prediction horizon,  $N_h=6$  and weighting factor,  $\lambda=0.242$ . This performance of the system is assessed by the Root Mean Square (RMS<sub>error</sub>) and Total Harmonic Distortion (THD) values, which are discussed in section 4.4.

The RMS<sub>error</sub> is given by,

$$RMS_{error}(\%) = \frac{{}_{RMS}(v_{c,abc} - v_{c,abc}^*)}{v_{c,abc}^*|_{RMS}} \times 100~\%$$

where  $v_{c,abc}$  is the actual output voltage

$v_{c,abc}^*$  is the reference output voltage &

$v_{c,abc}^*|RMS$  is the RMS voltage reference =120 V, 50 Hz

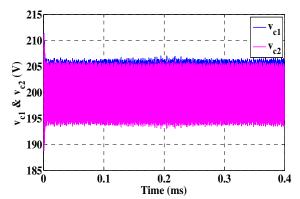

Fig. 4.8 DC link capacitor voltages  $v_{c1}$  &  $v_{c2}$  balanced by redundancy approach with initial imbalance condition

Fig. 4.9 Output voltage-reference and controlled waveforms for Redundancy approach

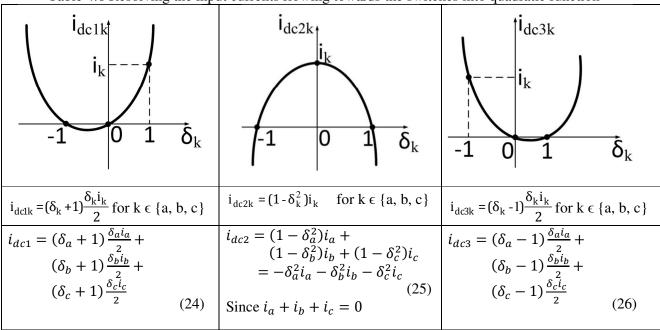

Fig. 4.10 DC link capacitor voltages v<sub>c1</sub> & v<sub>c2</sub> for redundancy approach