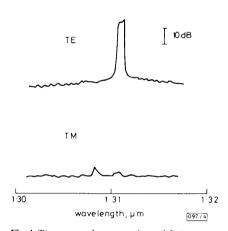

observed in an ordinary asymmetric reflectivity DFB laser without  $\lambda/4$  phaseshift was due to a mode partition between the DFB mode and Fabry-Perot modes caused by insufficient AR coating at one end of the laser. So far TE-TM mode partition as shown in Fig. 3 has not been observed.

In the  $\lambda/4$  shifted DFB laser the threshold gain difference  $\Delta \alpha L$  among TE modes or among TM modes is around 0.7 when optimally designed,<sup>3</sup> i.e.,  $\kappa L$  is 1.25, while the mode selection between TE and TM mode provided by the difference in the coupling coefficient and the mode confinement factor is very small. Theoretical calculation assuming a rectangular shaped corrugation using a model by Streifer et al.4 showed that there was no difference in the coupling coefficient between TE and TM modes for the active layer thickness  $d_a$  of  $0.15 \,\mu\mathrm{m}$ . For a thinner  $d_a$  of  $0.1 \,\mu\mathrm{m}$  there was a slight difference. However, even in this case, the  $\Delta \kappa L$  for optimum  $\kappa L$  of 1.25 was only 0.06, which corresponded to the threshold gain difference  $\Delta \alpha L$  between TE and TM mode of only 0.07. The difference in mode loss owing to the mode confinement factor could not be as large because of the small absorption coefficient of the cladding layers. The mode selection between TE and TM mode in a  $\lambda/4$  shifted DFB laser is much smaller than that in an ordinary asymmetric reflectivity DFB laser in which TE-TM mode selection is provided by the facet reflectivity. Fig. 4 shows the time averaged spectra of a  $\lambda/4$  shifted DFB laser under modulation measured using a polariser. We can identify a small amplitude TM emission. This small amplitude TM emission is evidence of TM mode lasing with a very small probability, of the order of 10<sup>-10</sup>, under modulation due to the gain overshoot.

Fig. 4 Time averaged spectra under modulation

TM spectrum was measured using a Glan-Thompson polariser

We have developed a very-low-threshold-current highefficiency  $\lambda/4$  shifted DFB laser having bandwidth of 11 GHz. However, transmission experiment revealed that there existed a mode partition between TE and TM mode. This mode partition is due to a small threshold gain difference between TE and TM mode. To make full use of the attractive feature of the  $\lambda/4$  shifted DFB laser, i.e., the large threshold gain difference between modes, we must incorporate a strong mode selection mechanism between TE and TM mode. This is especially important for a laser to be used in several Gbit/s systems under a direct modulation scheme.

The authors wish to thank M. Matsuda for his fabrication of the  $\lambda/4$  shifted corrugations, and S. Isozumi, T. Kusunoki, T. Tanahashi, H. Sudo and M. Sugano for their co-operation in this work. They also wish to thank T. Misugi, M. Kobayashi, and T. Sakurai for their encouragement.

H. ISHIKAWA 26th February 1988

K. KAMITE

K. KIHARA

H. SODA

H. IMAI

Fuitsu Laboratories Ltd. 10-1 Morinosato-Wakamiya, Atsugi, Japan References

- ISHIKAWA, H., SODA, H., WAKAO, K., KIHARA, K., KAMITE, K., KOTAKI, Y., MATSUDA, M., SUDO, H., YAMAKOSHI, S., ISOZUMI, S., and IMAI, H.: 'Distributed feedback laser emitting at 1.3 µm for gigabit communication systems', J. Lightwave Technol., 1987, LT-5, pp. 848-855

- KAMITE, K., SUDO, H., YANO, M., ISHIKAWA, H., and IMAI, H.: 'Ultrahigh speed InGaAsP/InP DFB lasers emitting at 1·3 μm wavelength', IEEE J. Quantum Electron., 1987, QE-23, pp. 1054-1058

- SODA, H., KOTAKI, Y., SUDO, H., ISHIKAWA, H., YAMAKOSHI, S., and IMAI, H.: 'Stability in single longitudinal mode operation in GaInAsP/InP phase-adjusted DFB lasers', IEEE J. Quantum Electron., 1987, QE-23, pp. 804-814

- STREIFER, W., SCIFRES, D. R., and BRUNHAM, R. D.: 'TM-mode coupling coefficients in guided-wave distributed feedback lasers', IEEE J. Quantum Electron., 1976, QE-12, pp. 74-78

## SWITCHED-CAPACITOR NEURAL **NETWORKS FOR LINEAR PROGRAMMING**

Indexing terms: Neural networks, Switched-capacitor networks. Linear programming solvers, Circuit theory and design

A circuit for online solving of linear programming problems is presented. The circuit uses switched-capacitor techniques and is thus suitable for monolithic implementation. The connection of the proposed circuit to analogue neural networks is also outlined

Introduction: It has been shown that both linear and nonlinear programming problems can be solved by using analogue circuits with a neural-like structure. 1.2 These circuits exhibit strong potential for those applications where online optimisation is required as is the case in robotics, satellite guidance, etc. Breadboard prototypes have been built using off-the-shelf circuit components. Since the required component-count is very high even for simple examples, it makes sense to explore the possible realisation of these circuits using fully integrated techniques.

Nonlinear programming solvers are particular examples of the broader family of analogue neural networks, which is of increasing interest because it seems to pave the way for analogue artificial intelligence circuits.<sup>1.4</sup> However, the field of analogue neural networks is just emerging and very little has been done on the practical implementation of the different classes of such networks. In a very recent letter, Tsividis and Anastassiou<sup>5</sup> proposed a technique for the VLSI implementation of a type of analogue neural network using a switchedcapacitor neural cell. The proposed technique is adequate for solving optimisation problems that can be formulated in an explicit form, but not readily applicable to linear and nonlinear programming problems. A different strategy is required for this type of analogue neural network, since the equations describing mathematical programming problems are implicit in nature and do not admit to being cast in an explicit form.

In this letter we propose a method for the realisation of linear programming solvers using switched-capacitor techniques. The proposed circuits are members of the general family of analogue neural networks, being more adequate for monolithic implementation than previous linear programming solver proposals.

Problem formulation and proposed circuit structure: The general linear programming problem can be stated as follows.6 Minimise a scalar cost function

$$\Phi(x) = \sum_{i=1}^{n} a_i x_i \tag{1}$$

subject to a set of p constraints,

$$f_{j}(x) = \sum_{i=1}^{n} b_{ji} x_{i} \ge 0 1 \le j \le p (2)$$

where x is the vector of variables for the problem, p and n are integer numbers and a and  $b_j$ , for each j, are vectors of coefficients.

ELECTRONICS LETTERS 14th April 1988 Vol. 24 No. 8

By using the concept of the penalty function<sup>6</sup> and applying a gradient strategy we obtain the following numerical algorithm to solve the above general linear programming problem,

$$x(q+1) = x(q) - \frac{1}{\alpha} \left[ w(f) \nabla \Phi(x) + \sum_{j=1}^{p} \nabla \rho_j(x) \right]$$

(3)

where  $\alpha$  is an arbitrary positive constant, q is an integer number for the iteration count and functions w(f) and  $\rho_j$  are defined as follows,

$$w(f) = \begin{cases} 1 & \text{if } f_j \ge 0 \text{ for every } j \\ 0 & \text{otherwise} \end{cases}$$

(4)

$$\rho_{j}(f_{j}(\mathbf{x})) = \begin{cases} 0 & \text{if } f_{j} \ge 0\\ \beta \mid f_{j} \mid & \text{otherwise} \end{cases} \qquad \text{for } 1 \le j \le p \quad (5)$$

where  $\beta$  is an arbitrary positive constant.

Note that the introduction of the function w(f) means a modification of the traditional way of combining f and  $\Phi$  to define penalty functions.<sup>6</sup> This modification is important to improve the convergence of the algorithm.

Using eqns. 4 and 5 and eqns. 1 and 2 in eqn. 3 we obtain the following relationship for each component of x:

$$x_{i}(q+1) = x_{i}(q) - \frac{1}{\alpha} \left[ w(f)a_{i} - \frac{\beta}{2} \sum_{j=1}^{p} [1 - \operatorname{sgn}(f_{j})]b_{ji} \right]$$

(6)

where sgn(.) is the well-known sign function.

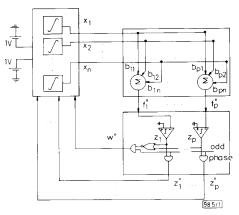

Fig. 1 Block diagram of proposed linear programming solver

Fig. 1 shows the conceptual block diagram for the implementation of the general linear programming problem using switched-capacitor techniques. Note that one integrator is required per program variable. The p constraint functions are obtained via a set of summers whose inputs are the integrator outputs. The nonlinear functions w(f) given in eqn. 4, and  $z_1(f_j) = \frac{1}{2}(1 - \text{sgn }(f_j))$  are respectively obtained from the

outputs of the summers via the block at the bottom of the Figure on the right, henceforth called the constraint block.

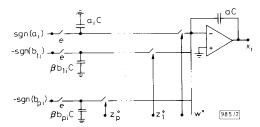

Fig. 2 shows a detail of the *i*th integrator block. A twophase clock signal is used to control the analogue switches. The input switches are directly controlled by one of the phases (the even clock phase) and the switches connected to the op-amp negative input lead are controlled by the outputs of the constraint block. These outputs are defined during the odd clock phase. By elementary analysis involving charge conservation principles it is clear that the circuit in Fig. 2 implements eqn. 6. The summer block appearing in Fig. 1 can be implemented by using techniques reported elsewhere.<sup>7</sup>

Fig. 2 Detail of integrator block

Practical results: The proposed circuit has been computer simulated using DIANA<sup>8</sup> and a detailed macromodel for the op-amps.<sup>9</sup> The simulated programming problems are listed in Table 1, where both the theoretical solution and the one computed by DIANA are shown for every example. Also included in Table 1 is the number of clock periods required for the circuit to reach its final state. In all the cases, the initial state was the origin of the program variable space. As can be seen it is possible to obtain a very approximate solution in relatively few clock periods.

Conclusions: A circuit structure is proposed for implementing linear programming problems using switched-capacitor techniques. This structure is based on a reduced set of basic cells that are interconnected following a dense regular pattern. The resulting circuits exhibit a very high modularity and in this sense can be considered as members of the general family of analogue neural networks. The method is valid for any linear programming problem and is also suitable for monolithic implementation, a significant advantage as compared to previous analogue neural linear programming solvers. 1,2

Acknowledgments: This research has been supported by Spanish CICYT under contract no. ME87-0004.

A. RODRÍGUEZ-VÁZQUEZ

9th February 1988

A. RUEDA

J. L. HUERTAS

R. DOMÍNGUEZ-CASTRO

Departamento de Electricidad y Electrónica Facultad de Fisica Universidad de Sevilla Avda. Reina Mercedes s/n, 41012-Sevilla, Spain

Table 1 THEORETICAL AND SIMULATION RESULTS FOR TWO PROBLEMS

| Theoretical solution           | Simulated<br>solution using<br>DIANA                                | Number of clock periods                                                                                                                                                  |

|--------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $v_1 = -5$ $v_2 = -5$          | $v_1 = -4.99 \pm 0.03$ $v_2 = -5.03 \pm 0.08$                       | 40                                                                                                                                                                       |

| $v_1 = -6$ $v_2 = 0$ $v_3 = 0$ | $v_1 = -5.88 \pm 0.3$ $v_2 = -0.04 \pm 0.11$ $v_3 = -0.01 \pm 0.15$ | 40                                                                                                                                                                       |

|                                | solution $v_1 = -5$ $v_2 = -5$ $v_1 = -6$ $v_2 = 0$                 | Theoretical solution using DIANA $v_1 = -5 & v_1 = -4.99 \pm 0.03 \\ v_2 = -5 & v_2 = -5.03 \pm 0.08$ $v_1 = -6 & v_1 = -5.88 \pm 0.3 \\ v_2 = 0 & v_2 = -0.04 \pm 0.11$ |

ELECTRONICS LETTERS 14th April 1988 Vol. 24 No. 8

## References

- 1 TANK, D. W., and HOPFIELD, J. J.: "Simple "neural" optimization networks: an A/D converter, signal decision circuit, and a linear programming circuit, IEEE Trans., 1986, CAS-33, pp. 533-541

- programming circuit', IEEE Trans., 1986, CAS-33, pp. 533-541

KENNEDY, M. P., and CHUA, L. O.: 'Unifying the Tank and Hopfield linear programming circuit and the canonical nonlinear programming circuit of Chua and Lin', IEEE Trans., 1987, CAS-34, pp. 210-214

- 3 WILSON, G.: 'Quadratic programming analogs', IEEE Trans., 1986, CAS-33, pp. 907-911

- 4 TSIVIDIS, Y.: 'MOS analog IC design—new ideas, trends and obstacles'. Proceedings of the 1986 European Conf. on Solid-State Circuits, 1986, pp. 113–115

- TSIVIDIS, Y., and ANASTASSIOU, D.: 'Switched-capacitor neural networks', Electron. Lett., 1987, 23, pp. 958-959

VANDERPLAATS, G. V.: 'Numerical optimization techniques for

- 6 VANDERPLAATS, G. V.: 'Numerical optimization techniques for engineering design: with applications' (McGraw-Hill, New York, 1984)

- 7 GREGORIAN, R., and TEMES, G. C.: 'Analog MOS integrated circuits for signal processing' (Wiley-Interscience, 1986)

- 8 ARNOUT, G., REYNAERT, PH., CLAESEN, L., and DUMLUGOL, D.: 'DIANA V7E user's guide'. ESAT Laboratory, Katholieke Universiteit Leuven, 1983

- 9 PÉREZ-VERDÚ, B., HUERTAS, J. L., and RODRÍGUEZ-VÁZQUEZ, A.: 'A new nonlinear time-domain op-amp macromodel using threshold functions and digitally-controlled network elements', IEEE J. Solid-State Circuits, 22, to be published

## HIGH-CURRENT PULSE-DOPED GaInAs MESFET

Indexing terms: Semiconductor devices and materials, Field-effect transistors, Gallium compounds

We report the DC and microwave performance of pulse-doped GaInAs power MESFETs. For a  $0.7\,\mu m$  gate-length device, a maximum drain-current density of  $870\,\text{mA/mm}$  and a peak transconductance of  $325\,\text{mS/mm}$  were measured. A maximum stable gain of  $11.7\,\text{dB}$  at  $26\,\text{GHz}$ , and an extrapolated  $f_1$  of  $33\,\text{GHz}$  were obtained. These values are the highest reported for MESFETs having gates as long as  $0.7\,\mu m$ .

Power amplifiers based on GaAs/AlGaAs HEMTs suffer from low drain-saturation current. Recently, multichannel and pseudomorphic HEMTs have been developed to increase current densities, 1-4 but the low thermal conductivity of the GaAs substrate limits the maximum achievable power of these devices. Improved performance can be obtained by using AlInAs/GaInAs heterostructure FETs, which combine high mobility with high sheet-carrier concentration. In addition, the InP substrate offers higher thermal conductivity than GaAs. The microwave performance of AlInAs/GaInAs HEMTs is beginning to surpass that of GaAs/AlGaAs HEMTs.\*5 We recently reported  $n^+$ -pulse-doped GaInAs MESFETs of  $0.7 \mu m$  gate length with excellent maximum stable gains of 14 dB at 26.5 GHz, and a maximum frequency of oscillation of greater than 100 GHz.6 In this letter, we report the fabrication and performance of n+-GaInAs-channel MESFETs with both high current densities and high gains.

The pulse-doped GaInAs MESFET structure was grown by MBE on a semi-insulating InP substrate. The device structure consisted of a 2500 Å AlInAs buffer layer, 100 Å of undoped GaInAs, a 200 Å  $n^+$ -GaInAs layer, 500 Å of undoped AlInAs, and a 100 Å  $n^+$ -GaInAs cap. All the layers were lattice matched to InP. The undoped AlInAs layer reduces the gate leakage current and increases the barrier height. We have grown three structures with varying electron concentration. For the first structure (48N), a Hall mobility of 4100 cm²/Vs with an electron concentration of 4·8 × 10<sup>12</sup> cm² was measured at 300 K. A Hall mobility of 4100 cm²/Vs with an electron concentration of 5·8 × 10<sup>12</sup> cm² was measured for the

second structure (58N). We have measured for the third structure (80N) sheet concentrations as high as  $8\times10^{12}\,\mathrm{cm^{-2}}$  with mobilities of 3500 cm<sup>2</sup>/Vs.

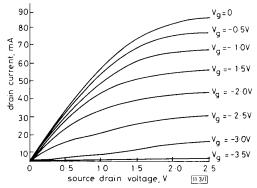

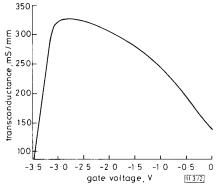

The processing of these MESFETs was similar to that reported previously.6 The MESFETs had a gate length of  $0.7 \,\mu\text{m}$  with a  $4.0 \,\mu\text{m}$  source/drain spacing. The I/V characteristics of 58N-structure MESFET having a 100 µm gate width are shown in Fig. 1. A drain saturation current of 870 mA/mm and complete pinch off at a gate voltage of  $-3.5 \,\mathrm{V}$  is achieved. For the 48N structure MESFET, a drain current of  $680 \,\mathrm{mA/mm}$  with a pinch off voltage of  $-3.0 \,\mathrm{V}$  was measured. For devices on the 80N-structure with a sheet concentration of  $8.0 \times 10^{12} \, \text{cm}^{-2}$ , we measured currents as high as  $1.0 \, \text{A/}$ mm but they could not be pinched-off. Fig. 2 shows the variation of the transconductance with gate voltage for the 58N-structure MESFET. The large bandgap AlInAs confines the carriers in the channel, resulting in the broad peak in the transconductance against gate voltage and improved linearity for high-power FETs. Extrinsic transconductances as high as 325 mS/mm were achieved. For the 48N-structure MESFETs, we achieved transconductances between 250 and 310 mS/mm. A gate/drain breakdown voltage of 3.2 V was measured at a leakage current of  $0.5 \,\mu\text{A}/\mu\text{m}$  of gate width for the 58N structure. Higher breakdown voltages can be obtained with thicker undoped AlInAs layers, but at a sacrifice of transconductance.

Fig. 1 I/V characteristics of a pulse-doped GaInAs MESFET

The microwave performance of these MESFETs for different source/drain voltages and gate voltages was measured over the frequency range  $0.5-26.5\,\mathrm{GHz}$  using an automated Cascade wafer probe and an HP 8510 network analyser. Fig. 3 is a plot of the maximum stable gain (MSG) against frequency computed from the measured S-parameters. An MSG of 11.7dB at  $26.0\,\mathrm{GHz}$  and an extrapolated  $f_{max}$  of over  $100\,\mathrm{GHz}$  was obtained. The current gain was also computed from the measured S-parameters. Extrapolating a  $6\,\mathrm{dB/octave}$  roll-off, a current-gain cutoff frequency ( $f_i$ ) of  $33\,\mathrm{GHz}$  was obtained. The microwave-gain measurements were performed both before and after isolating the gates from the edge of the mesa.\* After gate isolation, we measured an increase in the MSG, which we attributed to a decrease in the gate-leakage current.

Fig. 2 Transconductance against gate voltage for pulse-doped GaInAs MESFET

ELECTRONICS LETTERS 14th April 1988 Vol. 24 No. 8

<sup>\*</sup> FATHIMULLA, A., ABRAHAM, J., and LOUGHRAN, T.: 'High performance InGaAs/InAlAs HEMTs and MESFETs'. Submitted for publication (IEEE Electron. Device Letts.)