# Modeling OpAmp-Induced Harmonic Distortion for Switched-Capacitor $\Sigma\Delta$ Modulator Design

F. Medeiro, B. Pérez-Verdú, A. Rodríguez-Vázquez and J.L. Huertas Dept. de Diseño de Circuitos Analógicos. Centro Nacional de Microelectrónica. Edificio CICA, Avda. Reina Mercedes s/n, 41012-Sevilla (Spain).

#### **ABSTRACT**

This communication reports a new modeling of opampinduced harmonic distortion in SC  $\Sigma\Delta$  modulators, which is aimed to *optimum* design of this kind of circuit for high-performance applications. We analyze incomplete transfer of charge in a SC integrator and use power expansion and nonlinear fitting to obtain *analytical* models to represent harmonic distortion as function of the opamp finite gain-bandwidth (GB), slew-rate (SR) and nonlinear DC gain. Calculated models apply for all modulator architectures where harmonic distortion is dominated by the first integrator in the chain [1,2]. We show that results provided by the new analytical models fit well to that obtained by simulation in time domain and have accuracy levels much larger than that provided by previously reported modeling approaches.

### INTRODUCTION

Switched-Capacitor (SC) integrators are basic building blocks for robust monolithic implementation of analog and mixed-mode signal processing and data conversion circuits. In particular, they are widely used to design high-resolution  $\Sigma\Delta$  modulators for voice applications [3]. Also, recent developments extend the useful frequency range of SC  $\Sigma\Delta$  modulators up to video frequencies [4], thus opening new application fields for forthcoming potential products. Nevertheless, it is amply recognized that increasing either resolution or operation speed of SC  $\Sigma\Delta$  modulators still remains a difficult design problem, whose solution requires thorough modeling of nonidealities that degrade dynamic range and the concourse of advanced optimization strategies [3, 5].

One of the major causes of performance degradation in SC  $\Sigma\Delta$  modulators is due to incomplete transfer of charge in the SC integrators, a non-ideal effect which is dominated by three major opamp parasitics: (a) finite and nonlinear DC gain, (b) finite gain-bandwidth product (GB), and, (c) slew-rate (SR). This incomplete transfer of charge, which produces gain error and distortion at the integrator output, has been previously analyzed by different authors; for SC filters [6, 7], and for SC  $\Sigma\Delta$  modulators [8, 9, 10]. In particular [7] carries out a thorough analysis by assuming that feedback is linear and that the integrator input is a sinusoidal input. Unfortunately, his analy-

sis does not apply to SC  $\Sigma\Delta$  modulators, where feedback is highly nonlinear and, consequently, the integrator input can not be considered sinusoidal. Other solution, adopted in [8], is using overspecified analog cells, resulting in large area occupation and power consumption, and underexploiting circuit performance potentialities. A recent paper by Dias et al. [9] assumes that error due to incomplete transfer of charge can be considered a white noise contribution which, after integration in the signal band, enables to obtain analytical expressions to evaluate the influence of GB and finite slew-rate. As we demonstrate in this paper this again produces overconservative estimations and, hence, precludes full exploitation of the modulator capabilities.

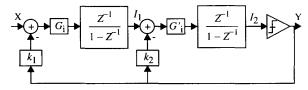

Our paper aims to analyze the influence of opamp dynamics (slew-rate and GB) and nonlinear DC gain on the behavior of a SC integrator; and to capture the analysis issues into analytical models suitable to be used for optimum high-level synthesis of  $\Sigma\Delta$  modulators following the approach previously reported by the authors at [5]. Our analysis focuses on the 2nd-order modulator, shown in Fig.1, and applies to all modulator architectures where distortion is dominated by the first integrator in the chain. This defines a class which includes all multistage architectures whose first stage is second-order [1] -- very important for high-speed applications [2, 4]. In particular we will consider the case where feedback coefficients  $k_1$  and  $k_2$  in Fig.1 are arbitrary, constrained only by the equation  $k_2 = 2G_ik_1$ .

Figure 1. Second-order  $\Sigma\Delta$  modulator.

#### SLEW-RATE DISTORSION

To cope with the nonlinear feedback that appears in  $\Sigma\Delta$  modulators, we will assume herein that the integrator input signal consists of the sinusoidal input signal plus a square-wave component that represents the feedback signal. Slew-rate will

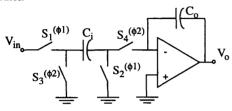

appear or not depending upon the instantaneous amplitude of this feedback signal. The approach developed here assumes the effect of the slew-rate in a SC integrator may be interpreted as a nonlinear gain. Let us consider the integrator shown in Fig. 2; during the *nth* integration interval  $(\phi_2 \text{ in } on)$  the evolution of the output node is,

$$v_o(t) = v_o(nT - T) + \frac{C_i}{C_o} V_S(1 - e^{-t/\tau}) \; ; \; nT - T < t < nT$$

(1)

where  $V_S = v_{in} (nT - T/2)$  and  $\tau$  is the time constant of the integrator.

Figure 2. Classical SC integrator.

The slope of this curve reaches its maximum value when t = 0, which results,

$$\frac{d}{dt}v_o(t)\Big|_{max} = \frac{C_i}{C_o} \frac{V_s}{\tau} \tag{2}$$

Let us separately consider two cases [9]:

- 1. The SR of the opamp is higher than the value specified in (2): there is not limitation of the SR and the evolution of  $v_0$  fits equation (1).

- 2. The SR is less than (2): in this case the first part of the temporal evolution of vo is linear with slope SR. The version of corresponding to this latter case is:

$$v_o(t) = v_o(nT - T) + G_i V_s + (SRt_0 - G_i V_s) e^{-(t - t_0)/\tau}$$

(3)

where  $G_i = C_i/C_0$  and  $SRt_0$  is the value reached by  $v_0$  at the time instant where the limitation of SR ends. On the other hand, the slope of the curve in (3) for  $t = t_0$  should be SR; consequently,

$$t_0 = G_i V_c / SR - \tau \tag{4}$$

with which, (3) becomes,

$$v_{o}(nT) = v_{o}(nT - T) + G_{i}V_{s} - sgn(V_{s})SR\tau e^{-\left(\frac{T}{2\tau} - \frac{G_{i}|V_{s}|}{SR\tau} + 1\right)}$$

(5)

where sgn(.) denotes the sign function, whose value equals unity for positive arguments and -1 otherwise; this sign function, together with the absolute value of  $V_s$  in the exponent, is included to contemplate both the rise and fall slopes. Note that in both cases, (1) and (5), can be described as an integrator with error terms for its gain. These can be calculated using the following expression:

$$g_{i}(V_{s}) = \begin{cases} G_{i}(1 - \beta e); & |V_{s}| \leq V_{L} \\ G_{i}(1 - \beta e^{|V_{s}|/V_{L}}); & |V_{s}| > V_{L} \end{cases}$$

(6)

where.

$$\beta = e^{-(T/(2\tau)+1)}; \quad V_L = SR\tau/G_i$$

(7)

In the first of the cases presented in (6), the effect of the integrator time constant translates to a gain error, which will cause increased noise in the signal's band [9]. However, this effect is commonly dominated by the appearance of harmonic distortion due to gain dependence of the integrator on its input, as shown in the second case of (6). In the following the approach developed to determine the amplitude of these harmonics is explained.

It can be shown that for a  $\Sigma\Delta$  modulator like that in Fig.1, whose first integrator presents the following nonlinear gain:

$$g_i(\nu) = G_i \sum_n \alpha_n \nu^{n-1}$$

$\alpha_n \ll \alpha_{n-1}$ ;  $n = 1, 2, 3...$  (8)

the amplitude of the *n-th* harmonic at the output is:

$$A_{H,n} = \alpha_n A^n / (2^{n-1}k_1); \quad n = 1, 2, 3, ...$$

(9)

where A is the amplitude of the sinewave input signal of the modulator. In our case, and since the symmetry of (6) annuls the coefficients  $\alpha_2$  y  $\alpha_4$ , we will assume that the integrator gain can be expressed as:

$$g_i(v) = G_i \cdot (\alpha_1 + \alpha_3 v^2 + \alpha_5 v^4)$$

(10)

For a real amplifier, the SR may be different in the rise and fall, however this dissymmetry will always be small in a typical design. Thus, the even harmonics in (9) are negligible respect to the odd ones. In this point, the problem of estimating harmonic distortion consists of searching for the curve with the form shown in (10) which best fits (6) for a specific interval. Considering for a  $\Sigma\Delta$  modulator like that presented in Fig.1, the signal at the input of the first integrator is distributed in the interval  $(k_1V_{ref}-A, k_1V_{ref}+A)$ , one solution is to apply the least square method to this range. With this method, the calculation of the coefficients in (10) becomes the solution of the following system of linear equations:

$$\sum_{j=1,3,5} \alpha_j \left( V_{R,h}^{j+2l} - V_{R,l}^{j+2l} \right) / (j+2l) = B_l \; ; \; l = 0, 1, 2 \quad (11)$$

where  $V_{R,h}$  and  $V_{R,l}$  represent the upper and lower limits of the interval, respectively, and

$$B_{l} = \int_{V_{R,h}}^{V_{R,h}} g_{i}(v) v^{2l} dv = \int_{V_{R,l}}^{V_{L}} G_{i}(1 - \beta e) v^{2l} dv +$$

$$+ \int_{V_{L}}^{V_{R,h}} G_{i} \left[ 1 - \beta exp\left(\frac{v}{V_{L}}\right) \right] v^{2l} dv$$

(12)

where it is assumed that  $V_{R,l} < V_L < V_{R,h}$  (note that the validity of the calculation is restricted to the case where  $V_{R,h} > V_L$ ; since, otherwise, the settling will be linear for any output swing and there will be no distortion). For the worst case,

where  $A = k_1 V_{ref}$  and thus  $V_{R,l} = 0$ , the values of  $\alpha_3$  and  $\alpha_5$  are:

$$\begin{split} &\alpha_{3} \cong -105\beta \left[ \frac{9}{8} \left( 11e - 30\zeta \right) \frac{V_{L}^{5}}{V_{R,h}^{7}} + \frac{135}{4} \zeta \frac{V_{L}^{4}}{V_{R,h}^{6}} - \frac{1}{8} \left( 7e + 114\zeta \right) \frac{V_{L}^{3}}{V_{R,h}^{5}} + 3\zeta \frac{V_{L}^{2}}{V_{R,h}^{4}} - \frac{1}{4} \zeta \frac{V_{L}}{V_{R,h}^{3}} \right] \\ &\alpha_{5} \cong 315\beta \left[ \frac{7}{16} \left( 11e - 30\zeta \right) \frac{V_{L}^{5}}{V_{R,h}^{9}} + \frac{105}{8} \zeta \frac{V_{L}^{4}}{V_{R,h}^{8}} - \frac{5}{16} \left( e + 18\zeta \right) \frac{V_{L}^{3}}{V_{R,h}^{7}} + \frac{5}{4} \zeta \frac{V_{L}^{2}}{V_{R,h}^{6}} - \frac{1}{8} \zeta \frac{V_{L}}{V_{R,h}^{5}} \right] \end{split}$$

where  $\zeta = exp(V_{R,h}/V_L)$ ;  $V_{R,h} \ge V_L$ . Applying (9), (10) and (13), the amplitudes of the third and fifth harmonics of the modulator output are defined as:

$$A_3 = |\alpha_3|A^3/(4k_1); A_5 = |\alpha_5|A^5/(16k_1)$$

(14)

## DISTORTION DUE TO THE NONLINEAR GAIN OF THE OPERATIONAL AMPLIFIER

Once again, let us consider the integrator in Fig.2 and assume that the gain of the operational amplifier depends on its output, in such a way that:

$$A_{V} = A_{0} (1 + \beta_{1} \nu_{o} + \beta_{2} \nu_{o}^{2})$$

(15)

In this way, the differential equation describing integrator operation is:

$$v_{o,n} = \frac{A_V G_i v_{i,n-1}}{A_V + 1 + G_i (1 + k_1)} + \frac{(A_V + 1) v_{o,n-1}}{A_V + 1 + G_i (1 + k_1)}$$

(16)

where  $v_i$  and  $v_o$  represent the integrator input and output, respectively. Considering that  $A_0$  tends to infinity and  $\beta_1$  and  $\beta_2$  tends to zero, (16) can be defined as:

$$v_{o,n} = v_{o,n-1} + G_i \left( v_i - \frac{v_i + v_{o,n}}{A_0} + \beta_1 v_{o,n} \frac{v_i + v_{o,n}}{A_0} + \beta_2 v_{o,n}^2 \frac{v_i + v_{o,n}}{A_0} \right)$$

(17)

According to this, analysis of an SC integrator with non linear gain of the operational amplifier, like that in (15), can be made considering an ideal integrator whose input is equal to the expression in parenthesis in (17). Thus, we may estimate the distortion as equal to the input of the integrator, analyzing the harmonics of the said expression. For this, we will follow the technique given in [6], briefly repeated here. Let us suppose that the input and output of the integrator can be estimated through their first harmonics; that is:

$$v_i \cong V_i \sin(\omega n T_s)$$

$v_o \cong V_o \cos(\omega n T_s)$  (18)

where  $\omega$  is the input frequency and  $T_{\rm S}$  the sample period. Substituting these expression in (17) and performing a Fourier series expansion of the term in parenthesis, the amplitudes of the second and third harmonics referred to in the first integrator are:

$$A_{2} = |\beta_{1}| (1 + k_{1}) V_{o} \sqrt{V_{i}^{2} + V_{o}^{2}} / (4A_{0})$$

$$A_{3} = |\beta_{2}| (1 + k_{1}) V_{o}^{2} \sqrt{V_{i}^{2} + V_{o}^{2}} / (8A_{0})$$

(19)

From here, and taking into equations describing the ideal oper-

ation of the second-order modulator, and that in  $\Sigma\Delta$  modulators  $\omega T_s << 1$ , consequently that  $V_i \cong 2\omega T_s A \ll V_o = A (k_2/k_1)$ , we obtain the following expressions for the amplitude of the second and third harmonics referred to at the modulator output,

$$A_2 = \frac{|\beta_1| (1+k_1)}{4A_0} \frac{k_2^2}{k_1^3} A^2 \qquad A_3 = \frac{|\beta_2| (1+k_1)}{8A_0} \frac{k_2^3}{k_1^4} A^3 \quad (20)$$

#### ILLUSTRATIVE RESULTS

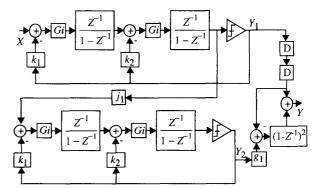

The 4th-order two-stage modulator shown in Fig.3 is used in order to evaluate the proposed models. For this, behavioral simulations using the parameters given in Table 1 have been made. Also,  $j_1$  equals unity;  $G_i = G_i$  and  $g_1$  has been made to  $1/(G_i G_i)$  for maximum cancelation of quantization noise.

Figure 3. Fourth-order cascaded  $\Sigma\Delta$  modulator.

| Sampling freq. | 5.12 Mhz | Slew-rate | 25 V/μs |

|----------------|----------|-----------|---------|

| Input freq.    | 5 Khz    | DC gain   | 60 dB   |

| Ref. voltages  | ±1.0 V   | $\beta_2$ | 2.5%    |

Table 1: Parameters used in the simulations.

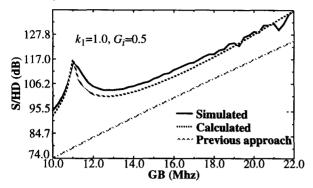

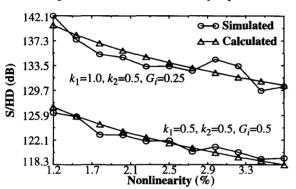

In particular, Fig.4 shows the signal-to-distortion ratio (S/HD) as a function of GB, for  $SR=25V/\mu s$ , and includes the simulated curve, the one obtained by using the proposed model, and the one which results applying the model in [9]. As it can be seen the model fits well the simulated results, even in those areas where the S/HD curve is nonmonotonic. Fig.5 illustrates results provided by the model of nonlinear gain. In particular, the curves show S/HD as a function of  $\beta_1$  in (20), for  $\beta_2=2.5\%$ , and two different sets of values for the modulator parameters  $k_1$ ,  $k_2$  and  $G_i$ . As for Fig.4 there is a good fitting to the simu-

lated results (please note the granularity of the scale in the vertical axis).

Figure 4. S/HD as a function of opamp GB.

Figure 5. S/HD as a function of the gain nonlinearity.

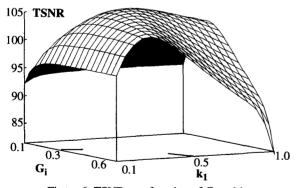

Fig.6 is intended to illustrate the use of the proposed models, together with other noise contributions [5], for systematic exploration of the design spaces for multi-stage  $\Sigma\Delta$  modulator architectures, in order to find optimum values of parameters  $k_1$ ,  $k_2$  and Gi. It represents the signal-to-(noise + distortion) ratio (TSNR) peak as a function of the  $G_i$  and  $k_1$  (see Fig.3) for a given set of building block specifications.

Figure 6. TSNR as a function of  $G_i$  and  $k_1$ .

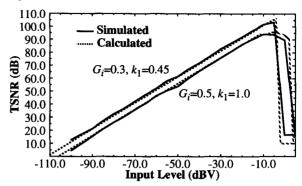

This curve has its maximum value at  $G_i = 0.3$  and  $k_1 = 0.45$ , which are the optimum values for the given block specification set. For that couple of values, both calculated and simulated

TSNR are plotted versus the modulator input amplitude in Fig.7.

Figure 7. TSNR vs. input amplitude.

Also, the corresponding curves for the classical choice  $G_i$ =0.5 and  $k_1$ =1.0 are shown. Note that the optimized curve reaches a maximum value of 10dB over the classical one which implies a resolution improvement of 1.7bits.

#### REFERENCES

- [1] H. Baher and E. Afifi, "Novel Fourth-Order Sigma-Delta Convertor", *Electonics Letters*, 28, 15, July 1992.

- [2] G.M. Yin, F. Stubbe and W. Sansen, "A 16-b 320-Khz CMOS A/D Converter Using Two-Stage Third-Order ΣΔ Noise Shaping", *IEEE JSSC*, 28, pp. 640-647, June 1993.

- [3] J.C. Candy and G.C. Temes, Oversampling Delta-Sigma Data Converters: Theory, Design and Simulation, IEEE Press, New York 1992.

- [4] G.M. Yin and W. Sansen, "A High-Frequency and High-Resolution Fourth-Order ΣΔ A/D Converter en BICMOS Technology", Procc. ESSCIRC'93, pp. 1-4, Sep. 1993.

- [5] F. Medeiro et al., "A Tool for Automated Design of Sigma-Delta Modulators using Statistical Optimization". *Procc ISCAS'93*, pp. 1373-1376, May 1993.

- [6] K. Lee and R.G. Meyer, "Low Distortion Switched-Capacitor Filter Design Techniques", *IEEE Journal of Solid-State Circuits*, SC-20, pp. 1103-1113, Dec. 1985.

- [7] W. Sansen et al., "Transient Analysis of Charge Transfer in SC-Filters-Gain Error and Distortion", *IEEE JSSC*, SC-22, pp. 268-276, April 1987.

- [8] B. E. Boser and B. A. Wooley, "The Design of Sigma-Delta Modulation Analog-to-Digital Converters", *IEEE JSSC*, 23. pp. 1298-1308, Dec. 1988.

- [9] V. M. F. Dias, "A Design Environment for Switched-Capacitor Noise-Shaping A/D Converters", Ph. D. Dissertation, Universita' Degli Studi di Pavia, 1991.

- [10] F. Op'T Eynde, "High-Performance Analog Interfaces for Digital Signal Processors", Ph. D. Dissertation, Katholieke Universiteit Leuven, 1991.