# A $\Sigma\Delta$ modulator for a programmable-gain, low-power, high-linearity automotive sensor interface

José M. de la Rosa\*, Fernando Medeiro, Belén Pérez-Verdú, Rocío del Río and Angel Rodríguez-Vázquez

## Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC) Edificio CICA-CNM, Avda Reina Mercedes s/n, 41012-Sevilla, SPAIN

## ABSTRACT

This paper describes the design and electrical implementation of a  $0.35\mu$ m CMOS 17-bit@40kS/s Sigma-Delta Modulator ( $\Sigma\Delta M$ ) forming part of a sensor interface for automotive applications. First of all, the paper discusses the most important limiting factors and design considerations applicable to a high-resolution  $\Sigma\Delta M$  for sensor interfaces. After an exhaustive comparison among multiple  $\Sigma\Delta M$  architectures in terms of resolution, speed and power dissipation, a third-order (2-1) cascade  $\Sigma\Delta M$  is chosen. For a better fitting to the characteristics of different sensor outputs, the  $\Sigma\Delta M$  here includes a programmable set of gains (0.5, 1, 2, and 4). The gain programmability is implemented by a reconfigurable capacitor array of unitary capacitors. In order to relax the amplifier dynamics requirements for the different modulator gains, switchable capacitor arrays are used for all the capacitors in the first integrator. The design of the modulator building blocks is based upon a top-down CAD methodology which combines simulation and statistical optimization at different levels of the modulator hierarchy. Behavioural simulations considering transistor-level circuit parasitics shows a Dynamic Range (DR) over 105dB for all cases of the modulator gain.

Keywords: Analog-to-digital converters, sigma-delta modulators, automotive sensor interfaces.

## **1. INTRODUCTION**

Since the introduction in the late 1970s of microprocessor-based automotive engine-control modules that regulated gas emissions, there has been an ever increasing penetration of electronic control systems in the automotive industry. In these systems, sensors play a critical role, covering a wide range of data capturing functions in multiple parts of the vehicle, such as the engine, powertrain and braking<sup>1</sup>. In recent years, the number of applications is increasingly growing with the combined use of sensors and Integrated Circuits (ICs) using the so-called MicroElectroMechanical (MEM) technologies<sup>2</sup>. These technologies have made possible a new generation of "smart" sensors that combine digital signal processing and communication with the environment on a single chip or within the same package. In the case of automotive components, MEM sensors must operate under very adverse environmental conditions with extreme temperatures ([ $-40^{\circ}C$ , 175°C]), mechanical shocks (50 – 500g on the vehicle), electromagnetic interferences, etc<sup>1-3</sup>.

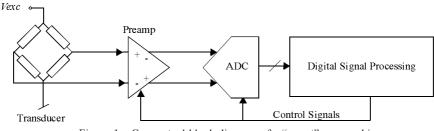

Therefore, the measuring circuit driving the sensor, normally formed by a low-noise preamplifier and an <u>A</u>nalog-to-<u>D</u>igital <u>C</u>onverter (ADC) (see Fig.1), must be very accurate and robust in order to handle the typically weak sensor output signals (ranging from  $\mu$ Vs to hundreds of mVs) in the hostile conditions mentioned above<sup>4-7</sup>. This is aggravated in most

Figure 1. Conceptual block diagram of a "smart" sensor chip

\* jrosa@imse.cnm.es; phone +34955056666; fax +34955056686; www.imse.cnm.es

VLSI Circuits and Systems, José Fco. López, Juan A. Montiel-Nelson, Dimitris Pavlidis, Editors, Proceedings of SPIE Vol. 5117 (2003) © 2003 SPIE · 0277-786X/03/\$15.00 applications as a consequence of the offset voltage due to the excitation voltage supplying most transducers. In practice, that offset voltage is subject to temperature and manufacturing process variations, thus causing a shift in the signal range provided by the sensor. Hence, the measuring circuit must accommodate the complete range of possible offsets and real signals. The same problem arises in multi-purpose sensors. In such devices, a programmable gain preamplifier is used to boost the sensor signal to a workable level where the ADC digitizes it and the rest of processing is carried out in the digital domain<sup>6</sup>.

In this scenario, the use of ADCs based on Sigma-Delta Modulators ( $\Sigma\Delta Ms$ ) is convenient for several reasons. On the one hand, the noise-shaping performed by  $\Sigma\Delta Ms$  allows to achieve high resolution (typically 16-17bits) in the band of interest (10-20kHz), with less power consumption than full Nyquist ADCs<sup>8-9</sup>. On the other hand, the action of feedback renders  $\Sigma\Delta Ms$  very linear, and high-linearity is a must for automotive applications. Besides, in some of these applications the principle of the sensing devices fits in with the topology of the  $\Sigma\Delta Ms$  with respect to circuit imperfections make them suitable to include programmable gain without significant performance degradation<sup>7</sup>. This feature allows to accommodate the complete range of possible offsets and information signals in a sensor interface with relaxed specifications for the preamplifier circuitry.

This paper describes the design and implementation of a third-order cascade (2-1)  $\Sigma\Delta M$  with programmable gain in a 0.35µm CMOS technology – the type of technology commonly employed for automotive applications (deep submicron is mostly employed for telecom). According to precise simulations which take into account transistor-level performance and technological parasities, the  $\Sigma\Delta M$  here is capable of handling signals up to 20-kHz bandwidth with 17-bit resolution for all cases of modulator gain (0.5, 1, 2 and 4), considering a temperature range of [-40°C,175°C] with a worst-case power consumption of 25mW. To achieve these features, a top-down CAD methodology has been followed which combines simulation and statistical optimization at different levels of the modulator hierarchy<sup>9</sup>.

The paper is organized as follows. Section 2 briefly reviews the fundamentals, architectures and major circuit limitations of  $\Sigma\Delta$ Ms, paying special attention to the most critical limiting factors in sensor interface applications. Section 3 applies the design considerations derived from Section 2 to choose the most appropriate architecture to be implemented in the programmable gain sensor interface in terms of resolution, speed and power dissipation. Section 4 describes the design of the building blocks at the transistor-level to achieving the required specifications. Finally, Section 5 shows several behavioural simulation results including electrical performance of building blocks and technological parasitics.

#### 2. FUNDAMENTALS AND CIRCUIT LIMITATIONS OF $\Sigma \Delta Ms$

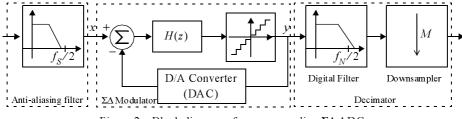

Fig.2 shows the conceptual block diagram of a  $\Sigma\Delta$  ADC which includes three basic components: an anti-aliasing filtering, a  $\Sigma\Delta M$ , and a digital decimator<sup>8-9</sup>. The signal is oversampled and quantized in the modulator. This block also filters the quantization error, by shaping its <u>Power Spectral Density</u> (PSD) in such a way that most of its power lies outside of the signal band, where the error is eliminated by digital filtering. The modulator output – coded into a reduced number of bits – is passed through the decimator, where, after filtering all the components out of the signal band, data are decimated to reduce the sampling frequency,  $f_S$ , down to the Nyquist frequency,  $f_N$ . The result is the signal coded in a large number of bits and clocked at  $f_N$ .

Among the converter blocks, the modulator is the hardest to design, since oversampling simplifies the anti-aliasing filter requirements and the decimator is a pure digital block whose design can be highly structured and automated<sup>8</sup>. As shown in Fig.2, the modulator output, y, is substrated from its input, x, which has been sampled at a rate much larger than  $f_N$ . The result is filtered by H(z), and passed through a quantizer, which usually has a reduced number of levels. If the gain of H(z) is high in the band of interest, and low outside of it, the quantization error is attenuated within the band due to the feedback loop.

Figure 2. Block diagram of an oversampling  $\Sigma\Delta$  ADC

Proc. of SPIE Vol. 5117 287

Assuming that the quantization error can be modelled as an additive, white noise source, e, the Z-transform of y is given by:

$$Y(z) = S_{TF}(z)X(z) + N_{TF}(z)E(z)$$

(1)

where X(z) and E(z) are the Z-transform of the input signal and quantization noise, respectively;  $S_{TF}(z)$  and  $N_{TF}(z)$  are the respective transfer functions of the input signal and quantization noise, given by

$$S_{TF}(z) = \frac{H(z)}{1 + H(z)} \qquad N_{TF}(z) = \frac{1}{1 + H(z)}$$

(2)

In case of *lowp ass* signals like that handled by sensors interfaces, the modulator loop filter, H(z), is properly chosen to obtain the following transfer functions

$$S_{TF}(z) = z^{-L}$$

$N_{TF}(z) = (1 - z^{-1})^{L}$  (3)

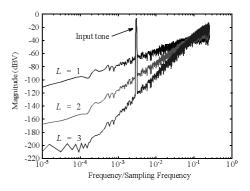

thus implementing the noise shaping concept illustrated in Fig.3 for different values of the modulator order, L. In this figure, the input signal is a sinewave of amplitude  $X = X_{FS}/4$ , with  $X_{FS}$  being the full-scale range of the quantizer.

The *in-band* quantization noise power can be calculated by integrating the output noise PSD within the signal band,  $B_w$ , giving:

$$P_{Q} = \int_{0}^{B_{w}} 2S_{Q} |N_{TF}(f)|^{2} df \cong \frac{\pi^{2L} \Delta^{2}}{12(2L+1)M^{(2L+1)}}$$

(4)

where  $S_Q = \Delta^2/(12f_S)$  is the PSD of the quantization noise,  $\Delta$  is the quantization step, and  $M \equiv f_S/(2B_w)$  is the *oversampling ratio*. From (4), and assuming that the modulator input is a sinewave of amplitude X, the <u>Signal-to-Noise Ratio</u> (SNR) at the output results in:

Figure 3. Noise shaping concept in  $\Sigma\Delta Ms$ .

$$SNR = \frac{X^2}{2P_Q} = \frac{6(2L+1)M^{(2L+1)}}{\pi^{2L}\Delta^2}X^2$$

(5)

The modulator Dynamic Range (DR) is obtained by making  $X = X_{FS}/2$  in the above expression. For an N-bit quantizer,  $\Delta = X_{FS}/(2^N - 1)$ , and hence

$$DR = \frac{3(2^{N}-1)^{2}(2L+1)M^{2L+1}}{2\pi^{2L}}$$

(6)

#### **2.1 Main** $\Sigma \Delta M$ architectures

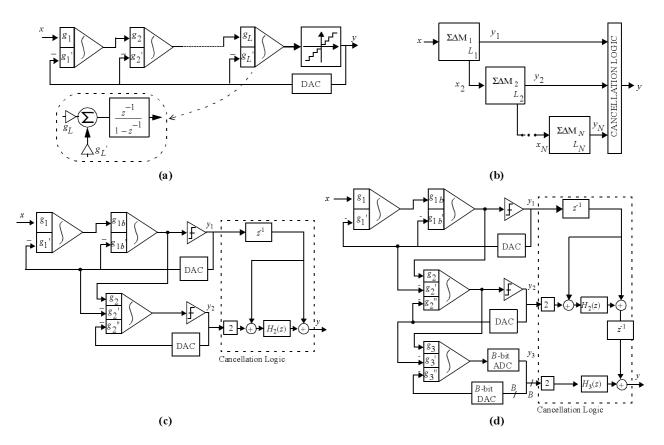

The simplest way of implementing an *Lth*-order  $\Sigma \Delta M$  consists of including *L* Forward-Euler (FE) integrators before the quantizer as illustrated in Fig.4(a), usually referred to as *Lth*-order single-loop  $\Sigma \Delta M$ . An important limitation of these architectures is their tendency to instability for L > 2. An alternative to single-loop  $\Sigma \Delta M$ s are the cascade architectures (also named multi-stage or MASH) whose generic block diagram is shown in Fig.4(b). Their functioning is based on the cascade connection of low-order modulators ( $L \le 2$ ), whose stability is guaranteed by design. The quantization noise generated in one stage is then re-modulated by the next one, and later cancelled in the digital domain. As a result, one obtains the modulator input plus the quantization noise of the last stage, attenuated by a shaping function of order equal to the number of integrators in the cascade.

Usually, the first stage of cascade  $\Sigma\Delta Ms$  is a second-order single-loop and the remaining stages are first-order modulators. For that reason, these architectures are often referred to as  $2 \cdot 1^{L-2} \Sigma\Delta Ms$ . As an illustration Fig.4 shows two cascade modulators using the mentioned stage distribution. Fig.4(c) is a 2-1 cascade modulator, which as demonstrated later, is a good candidate to be included in the sensor interface. Fig.4(d) is a  $2 \cdot 1^2$  with *multi-bit* (mb) quantization only in the

Figure 4. Main  $\Sigma\Delta M$  architectures. (a) *Lth*-order single-loop. (b) *Lth*-order cascade. (c)-(d) Practical realizations.

last stage  $(2-1^2 \text{ mb})$ . In such a way, the DAC non-linearity error is attenuated by a shaping function and filtered out by the digital decimator. The values of the integrator weights are the following<sup>12</sup>:

$$g_{1a} = g_{1a}' = 0.25; g_{1b} = 1, g_{1b}' = 0.5; g_k = 1, g_k' = 0.5, g_k'' = 0.5$$

$k = 2, ..., L-1$  (7)

and the digital blocks are  $H_k(z) = (1 - z^{-1})^k$ , k = 2...L - 1.

#### 2.2 Circuit limitations and design considerations

In the discussion above,  $\Sigma\Delta Ms$  have been considered ideal except for the inherent quantization error. However, in practical implementations, the in-band error power of whatever  $\Sigma\Delta M$  can be expressed as the summation of the contributions due to several circuit error mechanisms<sup>9</sup>,

$$P_{\text{in-band}} \cong P_Q + P_{cn} + P_{nl} + P_{st} \tag{8}$$

where right-hand side terms stand for quantization error, circuit noise, non-linearity error, and defective settling error powers, respectively. Although depending on the modulator type the basic  $P_Q$  (see eq. (4)) can be altered by circuit imperfections, the most important impact of such circuit imperfections is to be found in the remaining contributions in (8). For modest performance, the circuit requirements to render  $P_{cn} + P_{nl} + P_{st} \ll P_Q$  are not demanding. However, this is not the case for really challenging specifications, like those required in sensor interfaces, where the achievement of high resolution forces designers to work on the edge of feasibility. In these designs, the quantization error usually plays a secondary role.

For obvious reasons, out of the circuit imperfections above, dynamic limitations are not an issue in low-frequency sensor applications. On the contrary, circuit noise contribute 90% of the in-band error power in a typical design, thus deserving especial attention in this section.

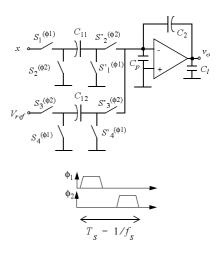

Consider the two-branch SC FE integrator in Fig.5, that assumes that the signal sampling capacitor,  $C_{11}$ , can be different from the feedback sampling capacitor,  $C_{12}$ , in order to create a modulator input-output gain  $\xi = C_{11}/C_{12}$ . In this circuit the noise contributors are the OTA (thermal + flicker noise) and the switch on-resistance (thermal noise). Also, potential noise coming from the reference voltage  $(V_{ref})$  generation block must be accounted for, which overall will be a mixture of white and flicker noise. Whereas flicker noise can be very efficiently removed from the signal band by applying chopper techniques<sup>5-6</sup>, for example, the low-frequency white noise PSD is boosted by the well-know aliasing mechanism: due to dynamic requirements, the equivalent noise bandwidths for these contributions are well in excess of half the sampling frequency, thus causing aliasing of their PSD. A careful analysis shows that the input-equivalent white noise PSD per fully-differential branch can be approximated (at low frequencies) by,

Figure 5 Two-branch SC integrator.

$$S_{in, C_{11}}(f) \cong \frac{4kT}{C_{11}f_S} + \frac{4kT(1+n_t)}{3C_{eq}, f_S}; \qquad S_{in, C_{12}}(f) \cong \frac{4kT}{C_{12}f_S} + \frac{4kT(1+n_t)}{3C_{eq}, f_S} + \frac{kT}{C_{12}f_S} \cdot \frac{R_{eq, ref}}{2R_{on}}$$

(9)

where k is the Boltzman constant, T is the absolute temperature and  $R_{on}$  is the switch-on resistance. The first term corresponds to the contribution of all the switches in each branch, the second one is for the OTA contribution, where

$$C_{eq,i} = C_p + C_{12}(1+\xi) + C_l \left[ 1 + \frac{C_p + C_{12}(1+\xi)}{C_2} \right]$$

(10)

is the OTA equivalent load during the integration phase ( $\phi_2$  high). In estimating the white noise PSD of the OTA, the contributions of MOS devices other than the input ones are compiled in the factor  $n_t$ , which equals the summation of the respective transconductance ratios. The third term in  $S_{in, C_{12}}$  represents the noise coming from the DAC reference voltages,  $V_{ref}$ , with  $R_{ea, ref}$  being its equivalent noise resistance.

By neglecting contributions other than the first integrator's, the  $\Sigma\Delta M$  output white noise power is obtained.

$$P_{wn} \approx \frac{4kT}{MC_{12}} (1+\xi) + \frac{4kT(1+n_t)}{3MC_{eq,i}} (1+\xi)^2 + \frac{kT}{MC_{12}} \frac{R_{eq,ref}}{2R_{on}\xi^2}$$

(11)

In obtaining (11), the OTA noise contributions in (9) have been considered fully correlated because it is the same circuitry and its noise is sampled at the same instant. From this point, some recommendations can be made for the design of a high-resolution  $\Sigma\Delta M$ :

- For given M and  $\xi$ , choose the feedback sampling capacitor,  $C_{12}$ , large enough to make the first term in (11) smaller than the maximum allowed in-band error power.

- The previous recommendation assumes that second and third contributions in (11) are less important, which requires that both the OTA and switch dynamic performances are not oversized.

Another fact clearly visible in (11) is that the output white noise power depends on the  $\Sigma\Delta M$  gain,  $\xi$ . The first two terms increase with  $\xi$ , while the third one decreases. The overall trend for  $P_{wn}$  is to increase with  $\xi$ . Also, as (10) shows, the OTA equivalent load increases with  $\xi$ , thus requiring more demanding dynamics and, hence, dissipating more power. The immediate conclusion is that the  $\Sigma\Delta M$  gain should be as close as possible to unity. In fact, if  $\xi = 1$  the second branch in Fig.5 is not necessary thus reducing even more  $P_{wn}$  and, consequently,  $C_{eq,i}$ . This choice, commonly found in literature<sup>6</sup>, puts the ball back into the preamplifier's court, rendering its design more complicate and the overall programmability less flexible.

#### **3. ARCHITECTURE SELECTION AND HIGH-LEVEL SIZING**

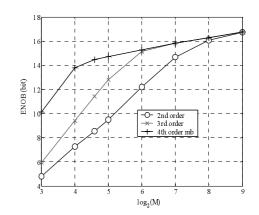

Comparing eqs. (4) and (11), it can be seen that, for each  $\Sigma\Delta M$  architecture, there will be a value of M for which  $P_Q \cong P_{wn}$ . In order to illustrate this, Fig.6 shows the effective resolution measured from three  $\Sigma\Delta Ms$  (4th-order 3bit, 3rd-order 1bit, and 2nd-order 1bit, all of them with the same front-end integrator) as a function of M. Differences among curves are justified by the different modulator orders and the fact that one of them is multi-bit. However, note that in each curve there is a change in the slope which coincides with the point beyond which the in-band error power is dominated by the first integrator white noise, and quantization error is not an issue any more. This is the reason why the three curves converge for sufficiently high M. Once in this region, doubling M generates a mere 3dB decrease in error power (i.e., 0.5-bit increase in effective resolution). In Fig.6, the only way to shift up the white-noise-limited

region is to increase the value of the sampling capacitors. Our expe-

Figure 6. Effective resolution vs. oversampling ratio.

rience and other design evidences in the open literature show that efficient  $\Sigma\Delta Ms$  are those located slightly inside this region: that is, with some equilibrium between  $P_Q$  and circuit-derived error power. Intuitively, this is due to the following rationale: (a) if for the oversampling ratio selected,  $P_Q$  clearly dominates the in-band error power (design located at the high-slope region of the curves in Fig.6), the building block specifications are bound to be oversized; (b) otherwise, (for design located deep in the low-slope regions), probably L or B (or both) could have been reduced without significant impact on resolution.

Contrary to high-frequency applications (e.g., communications), in sensor applications we can take maximum advantage of the maneuverability of M, making use of a highly-oversampled  $\Sigma\Delta M$  to fulfil the high-resolution requirements. This will push our design to the right in Fig.6, so that high-order and/or multi-bit architectures seem to be impractical. However, note that, if for a certain low-frequency application, the resolution does not have to be that high, thus requiring less oversampling, it will be sensible to try high-order and/or multi-bit solutions, as the equilibrium point between quantization error and circuit error moves to the left in Fig.6.

In order to quantitatively evaluate these qualitative considerations, an approximate (iterative) procedure can be implemented making use of the equations in the previous section to estimate the implementation cost of different architectures. For the sake of brevity, we will only sketch the main steps:

- For given values of  $L, M, N, V_{ref}$  and  $\xi$ , calculate  $P_Q$  and select  $C_{12}$  so that  $P_Q + P_{wn}$  is smaller than the maximum allowed in-band error power.

- Estimate C<sub>eq,i</sub> from (10). Then, a linear settling model with settling constant C<sub>eq,i</sub>/g<sub>m</sub> can be used to estimate the OTA transconductance required, since it takes a number ln(2<sup>ENOB</sup>) of time constants to settle within <u>Effective</u> <u>N</u>umber <u>Of Bits</u> (ENOB) resolution.

- Relate the OTA  $g_m$  with the OTA power dissipation, for which the candidate OTA topology must be known a priori. A suitable selection is extremely linked to the fabrication process: supply voltage, minimal device length, etc. Sensible choices are a folded-cascode OTA up to 3-V supply, and a two-stage amplifier below 2.5V.

- Once the first integrator power dissipation is estimated, that of the remaining integrators (in practice with less demanding specifications) can be estimated as a fraction of it. The overall static power of the modulator is then obtained by adding up all the contributions.

Of course, fine-tuning of this procedure is required for more realistic estimations, including the impact of other nonideal effects (such as finite and non-linear OTA DC-gain, slew-rate, errors in the multi-bit quantizers, etc.), power dissipation in other blocks, as well as the dynamic power dissipation<sup>12</sup>. In addition, the power dissipation and silicon area of the required decimation filter must be included in the trade-off towards architecture selection.

#### 3.1 Modulator architecture

The design considerations described above have been applied to design a 17-bit effective resolution, 40-kS/s ΣΔM

Proc. of SPIE Vol. 5117 291

for an automotive sensor interface requiring Signal-to-(Noise + Distortion) Ratio (SNDR) > 100dB within a temperature range of ([-40°C, 175°C]). The intended technology is a 3.3-V 0.35µm CMOS, with M-i-M capacitors available. In order to obtain the best  $\Sigma\Delta M$  that fulfils these specifications, the architecture selection procedure sketched above has been used and a large number of architectures have been compared using the following Figure-Of-Merit (FOM),

$$FOM = \frac{Power}{2^{\text{ENOB}} \times DOR} \times 10^{12}$$

(12)

which measures the energy needed per conversion in  $pJ^{13}$ .

Table 1 shows the outcome of the comparison for  $\Sigma\Delta Ms$  with 1-bit quantization, showing the best cases (sorted in terms of FOM) for each case of the modulator gain. In addition to the FOM, the modulator order (L), the oversampling ratio (M), and the power consumption are also included in Table 1. Note that the third-order 2-1 cascade architecture obtains the best result except for the case of  $\xi = 4$ . In this case the best FOM is obtained by a 2nd-order single-loop  $\Sigma\Delta M$  with M = 512, the third-order being the second one in the ranking. However, the 2-1 architecture has been preferred to the 2nd-order architecture because the latter requires M = 512, i.e. a 20.4 MHz sampling frequency, – discarded for several practical reasons, among the others: a less relaxed design of building blocks and switching noise coming from the digital part<sup>14</sup>.

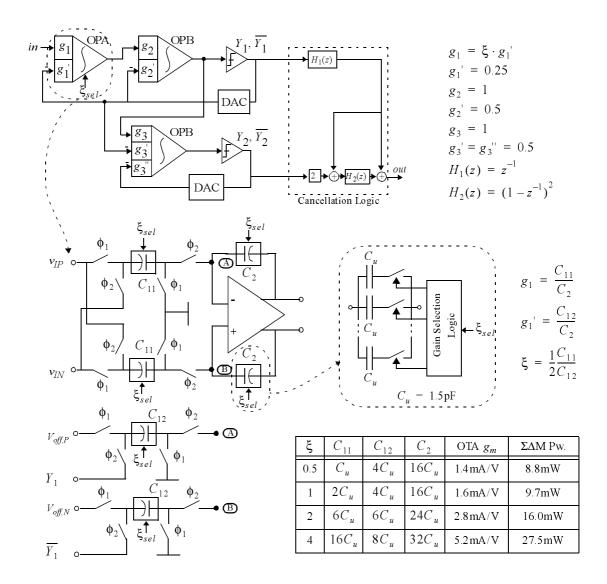

Fig. 7 shows the block diagram of the selected architecture together with the values for the analog coefficients. Note that the first integrator contains two differential input branches: one of them is for the sensor signal, in which double sampling is used to achieve an extra signal gain of 2, without increasing circuit noise<sup>15</sup>. The second branch receives the DAC outputs. Making use of the spare connection of the second branch, an external DC signal ( $V_{off}$ ) can be applied during  $\phi_1$  to center the sensor signal in the modulator full-scale range. This solution renders unnecessary a third branch for offset compensation with the subsequent thermal noise saving.

The programmable gain ( $\xi = 0.5, 1, 2$  and 4) has been mapped onto switchable capacitor arrays, each of them formed by a variable number of unitary capacitors. Such numbers and the unitary value (also shown in Fig.7) are selected for minimum power dissipation, bearing in mind the circuit noise limitation and the high temperature required for this sensor interface, (175°C). In order to keep the amplifier dynamic requirements as relaxed as possible, we propose to switch the number of unitary capacitors forming all the capacitances involved (not only the ones forming the sampling capacitors). The rationale behind this proposal is the following:

- For low gain cases the capacitor sampling the signal  $(C_{11})$  must be small compared to the  $V_{ref}$  and offset compensation sampling capacitor  $(C_{12})$ . According to (11), the input-referred thermal noise power appears multiplied by  $(1+C_{12}/C_{11})$ , which means that it will be amplified with respect the unity gain case.

- For large gains the situation is the opposite. Now thermal noise power is reduced with respect to the unity gain case, which allows us to decrease the capacitance values. This strategy also relaxes the minimum required amplifier dynamics because its equivalent load capacitance will be also decreased. Furthermore, by manipulating the tail current of the first OTA, the estimated power dissipation of the complete  $\Sigma\Delta M$  (tabulated in Fig.7) adjusts to the specific application.

| $\Sigma\Delta M$ Gain, $\xi$ | Order $(L)^{a}$ | Oversampling Ratio $(M)$ | Pow. Cons. (mW) | FOM (pJ/conversion) |

|------------------------------|-----------------|--------------------------|-----------------|---------------------|

|                              | 3               | 128                      | 6.77            | 1.291               |

| 0.5                          | 3               | 256                      | 8.12            | 1.548               |

|                              | 4               | 128                      | 8.27            | 1.578               |

|                              | 3               | 128                      | 8.48            | 1.618               |

| 1                            | 3               | 256                      | 9.77            | 1.863               |

|                              | 4               | 128                      | 10.32           | 1.969               |

|                              | 3               | 128                      | 12.69           | 2.422               |

| 2                            | 3               | 256                      | 13.85           | 2.641               |

|                              | 2               | 512                      | 13.88           | 2.647               |

| 4                            | 2               | 512                      | 23.24           | 4.432               |

|                              | 3               | 128                      | 24.21           | 4.618               |

|                              | 3               | 256                      | 25.02           | 4.772               |

|  | Table 1: | Outcome | of the | ΣΔΜ | architecture | selection |

|--|----------|---------|--------|-----|--------------|-----------|

|--|----------|---------|--------|-----|--------------|-----------|

a. All  $\Sigma\Delta$ Ms in this table are cascade architectures except for L = 2.

Figure 7 Modulator architecture with switchable gain.

• In order to simultaneously handle the modulator gain  $(2C_{11}/C_{12})$  and the first integrator feedback weight  $(C_{12}/C_{23})$  always equal to 0.25), the value of all capacitances must be changed by re-arranging the number of unitary capacitors forming them.

#### 3.2 High-level sizing

The  $\Sigma\Delta M$  in Fig.7 has been high-level sized, i.e, the modulator specifications have been mapped onto building-block specifications using statistical optimization for design parameter selection, and compiled equations (capturing non-ideal building block behaviour) for evaluation. This process is fine-tuned by behavioural simulation using ASIDES, an advanced behavioural simulator of SC  $\Sigma\Delta Ms$ . At this step, non-idealities are covered more accurately than in the case of using compiled equations. Also, worst cases for speed (the largest capacitor values) and for thermal noise (the highest temperature and the lowest capacitor values) are contemplated.

The results of this sizing process are summarized in Table 2, in which OPA denotes the opamp used at the first integrator in the chain and OPB refers to the opamps used at the second- and third- integrator in the modulator chain (see Fig.7). The data in Table 2 define the specifications of the building blocks, which are the starting point for electrical sizing.

|             | SPECS: 17bit@40kS/s                | @2V <sub>p</sub>  | 2-1 Arch. | Unit            |

|-------------|------------------------------------|-------------------|-----------|-----------------|

| MODULATOR   | Oversampling ratio                 |                   | 128       |                 |

|             | Sampling frequency                 |                   | 5.12      | MHz             |

|             | Reference voltages                 |                   | $\pm 2.0$ | V               |

|             | Estimated Power Consumption        | Gains 0.5+1+2+4   | 27.5      | mW              |

|             |                                    | Gains 0.5+1+2     | 16        | mW              |

|             |                                    | Gains 0.5+1       | 9.7       | mW              |

|             |                                    | Gain 1+2          | 16        | mW              |

| INTEGRATORS | Integration capacitor              | Gain 0.5          | 24        | pF              |

|             |                                    | Gain 1            | 24        | pF              |

|             |                                    | Gain 2            | 36        | pF              |

|             |                                    | Gain 4            | 48        | pF              |

|             | Unitary capacitor                  |                   | 1.5       | pF              |

|             | Sigma (assumed from tech.)         |                   | 0.1       | %               |

|             | Capacitor non-linearity (assumed t | from tech.)       | 25        | $ppm/V^2$       |

|             | Bottom parasitic capacitor (assume | ed from tech.)    | 5         | %               |

|             | Switch ON-resistance               |                   | <650      | Ω               |

| OPAMPS      | DC-gain                            | OPA               | 68        | dB              |

|             |                                    | OPB               | 63        | dB              |

|             | DC-gain non-linearity              |                   | 15%       | V <sup>-2</sup> |

|             | GBW                                | OPA (44.2pF load) | 17        | MHz             |

|             |                                    | OPB (8.9pF load)  | 15        | MHz             |

|             | Slew-rate                          | OPA (44.2pF load) | 17        | V/µs            |

|             |                                    | OPB (8.9pF load)  | 28        | V/µs            |

|             | Output swing                       |                   | ±2.5      | V               |

| COMPARATORS | Hysteresis (max.)                  |                   | 30        | mV              |

| Table 2: R | Results of high-level | sizing for the 2-1 $\Sigma\Delta M$ | with programmable gain |

|------------|-----------------------|-------------------------------------|------------------------|

|            |                       |                                     |                        |

## 4. DESIGN OF BUILDING BLOCKS

The modulator building blocks, namely, amplifiers, comparators and switches have been conveniently selected and sized according to the requirements given in Table 2. Design considerations on each of these blocks as well as their electrical performance using HSPICE are detailed in this section.

#### 4.1 Amplifiers

The key features for the design of the amplifiers are their open-loop DC-gain, dynamic requirements and output swing, where the last one becomes especially critical in a low voltage implementation. Nevertheless, the set of integrator weight used for the  $\Sigma\Delta M$  in Fig.7 allow us to relax the output swing requirements to be slightly larger than the reference voltages -2V in this case –, which is feasible when operating with 3.3-V supply in differential mode.

Note from Table 2 that the requirements for the OPA are more aggressive than those for the OPB since the contribution of the latter to the total in-band error power is attenuated by increasing powers of the oversampling ratio. This recommends, in order to avoid oversizing and optimize the power consumption, to obtain two different designs: one for the OPA and other one for the OPB.

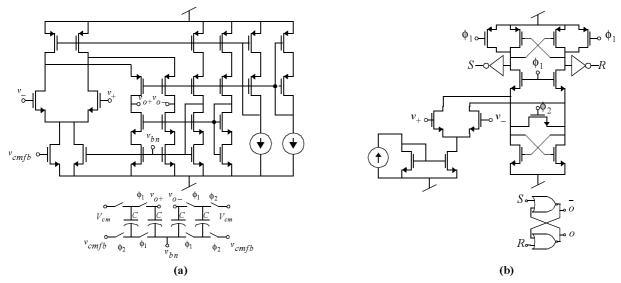

For this purpose, the transistor-level sizing tool FRIDGE<sup>9</sup> was used to explore the potential of several OTA fully-differential topologies. The search criteria were the achievement of the specifications for OPA and OPB with minimum power dissipation and reduced circuit complexity. After this exploration, a single-ended folded-cascode architecture, shown in Fig.8(a), was selected for both amplifiers. Note that an N-type input pair has been considered because a twinwell technology is used, and hence, the body effect can be removed in NMOS. The <u>Common-Mode Feed-Back</u> (CMFB) net has been implemented using a SC circuit, which provides fast and linear operation with small power dissipation.

Table 3 summarizes the electrical performance of both amplifiers in terms of target values imposed during the optimization procedure in FRIDGE to the main parameters affecting the modulator specifications. The corresponding values of these parameters, obtained by electrical simulations using HSPICE, are shown for typical conditions (typical process parameters, nominal supply voltage and room temperature). Finally, Table 3 shows also the worst-case value obtained for each of the parameters in a technology corner analysis.

Figure 8. Building block schematics. (a) Folded-cascode amplifier with SC CMFB net. (b) Comparator.

#### 4.2 Comparators

In order to fulfil the requirements for the 1-bit quantizer (comparator) given in Table 2, a regenerative latch including a preamplifying stage was selected – shown in Fig.8(b). The role played by the preamplifier is to improve the resolution of the comparator, which can be severely degraded in practice due to dissymmetries between the latch parameters.

MonteCarlo simulations and corner analysis have been done for characterizing the comparator performance after its full sizing. Table 4 summarizes the comparator features, showing the worst-cases for hysteresis and resolution time, together with the power dissipation.

|                        | OPA (45pFload) |            | OPB(9pF load) |            |

|------------------------|----------------|------------|---------------|------------|

| Model                  | Typical        | Worst-Case | Typical       | Worst-Case |

| DC-gain (dB)           | 74.0           | 71.09      | 68.3          | 68.3       |

| GB (MHz)               | 22.6           | 15.8       | 34.4          | 23.8       |

| PM (°)                 | 86.4           | 85.5       | 83.5          | 81.4       |

| Slew-Rate (V/µs)       | 22.1           | 21.1       | 38.1          | 35.7       |

| Output Swing (V)       | $\pm 2.75$     | ±2.5       | $\pm 2.75$    | ±2.5       |

| Transc. (mA/V)         | 6.3            | 4.5        | 1.95          | 1.35       |

| Power consumption (mW) | 7.1            | 7.2        | 2.3           | 2.4        |

Table 3: Electrical performance of the opamps (HSPICE)

| Parameter                   | Typical | Worst-case |

|-----------------------------|---------|------------|

| Offset (mV)                 | 0.75    | 9.92       |

| Hysteresis (mV)             | 0.03    | 0.12       |

| Resol time, $T_{RLH}$ (ns)  | 4.1     | 8.6        |

| Resol. time, $T_{RHL}$ (ns) | 3.9     | 6. 15      |

| Power Consumption (mW)      | C       | ) 43       |

Proc. of SPIE Vol. 5117 295

#### 4.3 Switches

The value of the finite switch on-resistance,  $R_{on}$ , is mainly constricted by dynamic considerations. Incomplete settling originated by transmission gates is traditionally reduced by making  $R_{on}Cf_S \ll 1$ , with C being the sampling capacitor. In our design, it has been evaluated that  $R_{on} < 650 \Omega$  can be tolerated with no degradation of the modulator performance. This range can be obtained (considering technology corners) using CMOS switches with aspect ratios of 6.5/0.35 for the NMOS and 23.5/0.35 for the PMOS, operating with the nominal 3.3-V supply.

However, in low-voltage technologies, given that the threshold voltage of the MOS transistors is not scaled down in the same amount as the supply voltage, the voltage range in which  $R_{on}$  keeps a nearly constant value decreases. The sampling process with such an on-resistance causes dynamic distortion – the more evident the larger the sampling capacitor.

In sensor interfaces, high-linearity is a must. Therefore, the non-linear sampling effect in the first integrator has to be carefully taken into account, especially in the case of  $\xi = 4$ , in which C = 24 pF. In this case the CMOS switch size given above causes harmonic distortion which can severally degrade the sensor interface performance. To avoid this, the switches used in the first integrator have been sized in order to obtain an *SNDR* over 17bits. This is achieved by increasing the aspect ratio of the CMOS switches in the front-end integrator to 29.1/0.35 and 105.9/0.35 for the NMOS and the PMOS transistors, respectively.

## 5. SIMULATION RESULTS

The modulator in Fig.7 has been simulated using ASIDES. Simulations were done considering the highest temperature in the sensor interface (175°C), which corresponds to the worst-case for thermal noise. Besides, the worst-case electrical performance of building blocks described in Section 4 were used and realistic models for the M-i-M capacitors available in the intended technology were included in the simulation, considering both mismatch and non-linearity effects.

Other important effect included in the simulations is the DC-gain non-linearity, which must be carefully taken into account in (low-voltage) high-linear  $\Sigma\Delta Ms$  like those used in sensor interfaces. In a typical design, the open-loop DC-gain of the amplifier varies with the DC output voltage, reaching its maximum for centred voltage (around the operating point) and decreasing as the output approaches one of the rails. In order to obtain accurate estimations for the impact of this effect, we have resorted to a look-up table procedure from opamp DC curves obtained by electrical simulation, whose data were included in ASIDES through a fast-convergence iterative procedure.

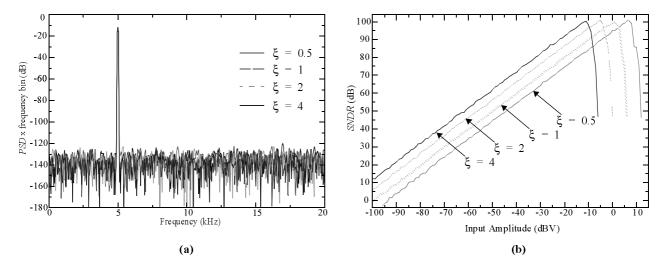

Fig.9(a) shows the output spectra for all cases of the modulator gain,  $\xi$ , corresponding to an input tone of frequency 5kHz and an amplitude at the *SNR*-peak. Fig.9(b) shows a set of *SNDR*-vs-amplitude curves for the different values of  $\xi$ . In all cases, the *SNR*-peak, which moves to left as  $\xi$  increases, is higher than 100dB. The *DR* is always over 105dB, corresponding to 17-bit resolution.

Figure 9. Simulation results. (a) Output spectra for all cases of the modulator gain. (a) SNDR-vs-amplitude

#### 6. CONCLUSIONS

The design of a  $0.35\mu$ m CMOS programmable-gain  $\Sigma\Delta M$  forming part of an automotive sensor interface has been described. Main design considerations have been discussed and applied to choose the most appropriate modulator architecture in terms of resolution, speed and power dissipation. As a result a 2-1 cascade architecture has been selected and their building blocks were designed based upon a top-down CAD methodology which combines simulation and statistical optimization at different levels of the modulator hierarchy. Behavioural simulations considering main circuit errors and technology corners show an effective resolution equal to 17 bits in a 20-kHz signal bandwidth for all cases of the modulator gain.

## ACKNOWLEDGMENTS

This work has been supported by the EU ESPRIT IST Project 2001-34283/TAMES-2 and the Spanish CICYT Project TIC2001-0929/ADAVERE.

## REFERENCES

- 1. W. J. Fleming, "Overview of Automotive Sensors", IEEE Sensors Journal, pp. 296-308, Dec. 2001.

- D. S. Eddy and D. R. Sparks, "Application of MEMs Technology in Automotive Sensors and Actuators", Proc. of the IEEE, pp. 1747-1755, Aug. 1998.

- 3. G. van der Horn, J. L. Huijsing, Integrated Smart Sensors, Kluwer Academic Publishers, 1998.

- 4. J.E. Johnston, "A 24-bit Delta-Sigma ADC with an Ultra-Low Noise Chopper-Stabilized Programmable Gain Instrumentation Amplifier", *Proc. of Advances A/D and D/A Conversion Techniques and their Applications*, pp. 27-28, 1999.

- 5. P. Malcovati and F. Maloberti, "An Integrated Microsystem for 3-D Magnetic Field Measurements", *IEEE Trans. on Instrumentation and Measurement*, pp. 341-345, April 2000.

- 6. C.B. Wang, "A 20-bit 25-kHz Delta-Sigma A/D Converter Utilizing a Frequency-Shaped Chopper Stabilization Scheme", *IEEE J. of Solid-State Circuits*, pp. 566-569, March 2001.

- F. Murabayashi, M. Matsumoto, K. Hanzawa, T. Yamauchi, K. Sakurai, H. Yamada, S. Shimada and A. Miyazaki, "A Programmable Sensor Signal Conditioning LSI", Proc. of the Second IEEE Asia Pacific Conference on ASICs, pp. 107-110, 2000.

- 8. S.R. Norsworthy, R. Schreier and G. Temes, *Delta-Sigma Data Converters Theory, Design and Simulation*, IEEE Press, 1997.

- 9. F. Medeiro, B. Pérez-Verdú and A. Rodríguez-Vázquez, *Top-down Design of High-Performance Sigma-Delta Modulators*, Kluwer Academic Publishers, 1999.

- K.A.A. Makinwa and J.H. Huijsing, "A Smart CMOS Wind Sensor", Proc. IEEE ISSCC, digest of Technical Papers, pp. 432-479, 2002.

- 11. H. Kulah, N. Yazdi, and K. Najafi, "A CMOS Switched-Capacitor Interface Circuit for an Integrated Accelerometer", *Proc. IEEE Midwest Symp. on Circuits and Systems*, pp. 244-247, August 2002.

- 12. F. Medeiro, R. del Río, J.M. de la Rosa, B. Pérez-Verdú and A. Rodríguez-Vázquez: "High-Order Cascade Multi-bit ΣΔ Modulators", Chapter 9 in the book A. Rodríguez-Vázquez, F. Medeiro and E. Janssens (Editors): "CMOS Telecom Data Converters". Kluwer Academic Publishers, to appear.

- F. Goodenough: "Analog Technologies of all Varieties Dominate ISSCC," *Electronic Design*, vol. 44, pp. 96-111, February 1996.

- 14. M. van Heijningen, et al.: "Substrate noise generation in complex digital systems: efficient modeling and simulation methodology and experimental verification," *IEEE Journal of Solid-State Circuits*, Vol. 37, pp. 1065-1072, August 2002.

- 15. C. C. Enz and G. C. Temes, "Circuit Techniques for Reducing the Effects of Op-Amp Imperfections: Autozeroing, Correlated Double Sampling, and Chopper Stabilization", *Proc. of the IEEE*, Vol. 84, pp. 1584-1614, Nov. 1996.