# Enhanced Sensitivity of CMOS Image Sensors by Stacked Diodes

Juan Antonio Leñero-Bardallo, Manuel Delgado-Restituto, Senior Member, IEEE, Ricardo Carmona-Galán, Senior Member, IEEE, and Ángel Rodríguez-Vázquez, Fellow, IEEE

Abstract—We have investigated and compared the performance of photodiodes built with stacked p/n junctions operating in parallel versus conventional ones made with single p/n junctions. We propose a method to characterize and compare photodiodes sensitivity. For this purpose, a dedicated chip in the standard AMS 180-nm HV technology has been fabricated. Four different sensor structures were implemented and compared. Experimental results are provided. Measurements show sensitivity enhancement ranging from 55% to 70% within the 500-1100 nm spectral region. The larger increment is happening in the near infrared band (up to 62%). Such results make stacked photodiodes suitable candidates for the implementation of photosensors in vision chips designed for standard CMOS technologies.

*Index Terms*—Stacked photodiodes; spectral sensitivity; photodiode characterization; event-based vision sensors; NIR.

## I. INTRODUCTION

**S** TANDARD CMOS technologies offer different alternatives for the implementation of embedded photodiodes, among which the n-well/p<sup>-</sup> substrate junction is considered a good choice owing to sensitivity, SNR and area considerations [1]–[4]. However, as a difference to specialized CIS (CMOS Image Sensor) technologies [5], where detailed characterization data for photo-sensors and pixels macro-cells are available to IC designers, in standard CMOS photodiode characterization is usually a required stage for the design of smart imagers and/or vision system-on-chips using standard CMOS.

Although CIS technologies feature better photo-sensors than standard ones, the rationale for using the latter include lower production cost and larger flexibility for the incorporation of complex logic circuitry. Hence, they may be a good choice for applications where emphasis is on vision tasks,

Manuscript received May 23, 2016; accepted September 14, 2016. Date of publication September 20, 2016; date of current version November 4, 2016. This work was supported in part by the Spanish Ministry of Economy and Competitiveness under Grant TEC2012-33634 and Grant TEC2015-66878-C3-1-R, Co-Funded by ERDF-FEDER, in part by Junta de Andaluca CEICE under Grant TIC 2012-2338 (SMARTCIS-3D), and in part by ONR under Grant N000141410355 (HCELLVIS). The associate editor coordinating the review of this paper and approving it for publication was Dr. Shoushun Chen. J. A. Leñero-Bardallo is with the University of Cádiz, Cádiz 11519, Spain (e-mail: juanantonio.lenero@uca.es).

M. Delgado-Restituto, R. Carmona-Galán, and Á Rodríguez-Vázquez are with the Institute of Microelectronics of Seville (IMSE-CNM), CSIC-Universidad de Sevilla, Seville 41092, Spain (e-mail: mandel@imsecnm.csic.es; rcarmona@imse-cnm.csic.es; angel@imse-cnm.csic.es).

Digital Object Identifier 10.1109/JSEN.2016.2611759

i.e. on extracting information from the sensor data, instead of image reproduction [6]–[9]. Since largest possible photode-tectors sensitivity is required for these vision sensors we may take advantage of the deep n-wells and/or p-wells available in modern technologies to build stacked photodiodes.

As compared to non-stacked conventional structures, stacked ones have the potential for increased sensitivity and spectral selectivity. This latter feature refers to detection of photons of different frequencies by using junctions placed at different depths within the semiconductor, exploiting the fact that absorption depths depend on photon wavelengths [10], [11]. By placing p/n junctions at different depths, the overall spectral response to white light is more balanced than using a single p/n junction. Each stacked photodiode will have a sensitivity peak at a different wavelength. Hence, the resultant spectral sensitivity will be flatter. Furthermore, the overall photocurrent will be higher because several photodiodes will operate in parallel. Since the stacked photodiodes share the same deep n-well, the area consumption is similar to the area required to fabricate a single diode.

The use of stacked photodiodes for vision sensors has been explored by different authors [6]–[8], [12]. The transient response of these different stacked photodiodes have been analyzed for communications applications; for instance, [13], [14]. Image sensors with stacked diodes are also commercialized by Foveon [11]. Regarding non-stacked spectral discrimination of CMOS-compatible photodiodes, photodetectors properties have been reported elsewhere [1]–[3]. However, to the best of our knowledge, there are not results published yet on the comparison of different CMOS-compatible stacked photodiodes options. Besides, while most papers describe stacked junctions operating individually as to preserve color information, there are no systematic data regarding parallel operation aimed to sensitivity enhancement.

This paper is aimed to compare the performance of four different CMOS-compatible photodiodes. Two of them are built by stacking different diodes involving deep n-well and deep p-well layers. The other two are classic photodiodes available in standard CMOS technologies, i.e. diodes either made with n-well/substrate junction or with a  $n+/p^-$  substrate junction. The paper also describes a method and an associated, easy to implement embedded circuitry to compare photodiodes' efficiency by a rather simple, indirect measurement procedure. Experimental results comparing all of them

1558-1748 © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

are provided. Details of the experiments and the experimental setup necessary to run the experiments are described.

The article is organized as follows: Section II describes the different p/n junctions available in the AMS 180nm HV technology and how they have been interconnected to create four different kinds of photodiodes. The circuitry used to determine its sensitivity is shown too. In Section III, the experimental setup is described. Moreover, experimental results are presented. Finally, Section IV discusses the experimental results and the photodiodes design trade-offs.

#### **II. CIRCUIT DESCRIPTION**

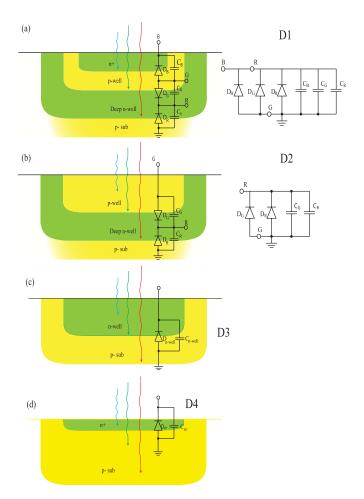

Our target is to compare the *sensitivity* —pixel performance in Volts per unit area and time per incident light power per unit area in  $(V.cm^{-2}.sec^{-1}/W.cm^{-2})$ , of the four different structures shown in Fig. 1. Colored arrows have been added to illustrate the absorption depth of different colors [10]. The first two photodiodes are created combining different p/n junctions with a deep n-well. The two others are conventional photodiodes available in standard CMOS technologies, i.e. a n-well/p<sup>-</sup> substrate junction and a n<sup>+</sup>/substrate junction.

Let us first consider Fig. 1.a (left) where three p/n junctions are stacked. Since absorption depth is lower for smaller frequencies, junctions at the bottom are expected to be more sensitive to wavelengths in the near infrared band, close to the red color. The top ones will be more sensitive to shorter wavelengths [10]. If we connect the diodes to operate in parallel as shown at the right of Fig. 1.a (D1), we obtain a twofold benefit:

- First the resultant spectral response will be more homogeneous than using an unique diode, i.e. the sensitivity curve of the resultant photodiode will be flatter.

- Second, the sensitivity to white light will be higher, because three photodiodes will be operating in parallel at different wavelengths.

These are interesting features for the design of vision sensors devised to operate in the whole visible spectrum.

Fig. 1.b depicts a second stacked photodiode (D2) that employs also deep n-well layer, but where the  $n^+$  diffusion on top has been removed to create two stacked photodiodes. This configuration is expected to have higher sensitivity operating with longer wavelengths than the one of Fig. 1.a. The layout design is simpler than the previous one and the minimum pitch that can be achieved is lower.

Fig. 1.c displays a photodiode created with a n-well/p<sup>-</sup> substrate junction (D3). This is usually the preferred choice when implementing image sensors operating in the visible band. This photodiode can be built in any standard CMOS technology and features good spectral sensitivity [1]–[4].

Fig. 1.d displays the last photodiode implemented for this study (D4). It is created with the junction of a  $n^+$  diffusion and a  $p^-$  substrate diffusion. Although this choice traditionally offers poor sensitivity, it can be interesting for applications that require good sensitivity in the blue.

As photodiodes spectral sensitivities must be characterized prior to using them with a non CIS technology. However, measuring photocurrents of photodiodes with a small pitch is

Fig. 1. (a) Triple-junction stacked photodiodes, interconnection between them, and circuit model. (b) Double-junction stacked photodiodes, interconnection between them, and circuit model. (c) N-well/p<sup>-</sup> substrate junction photodiode. (d) n<sup>+</sup>/ p<sup>-</sup> substrate junction photodiode.

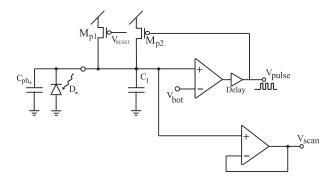

Fig. 2. Integrate-and-fire circuitry. Each photodiode (D<sub>\*</sub>) is connected to an independent I&F circuit that pulses with a frequency that is proportional to illumination. An analog buffer is connected to integration capacitance node to monitor the transient voltage at this point. Transistor sizes are (W/L,  $\mu$ m/ $\mu$ m):  $M_{p1} = 0.5/0.7$ ,  $M_{p2} = 10/1$ .  $C_1 = 40$  fF.

challenging [15], and dedicated equipment must be used. Also since pads leakage affects the measurements, removing pads protections is necessary for precise measurements. Another obstacle comes from the fact that small variations of output resistances produce measurement mismatch.

We propose an alternative approach that employs simple circuitry that can easily coexist with a pixel array in the same chip. It has low area requirements and only require three pads to gauge the photodiodes sensitivities. Each set of photodiodes is connected to an integrate-and-fire (I&F) circuit [16] as is depicted in Fig. 2. This circuit is an astable oscillator that switches between two states at the pace defined by the input photocurrent. Initially, the reset signal is activated to set the voltage at  $C_1$  too  $V_{DD}$ . Once the reset is released, the voltage at  $C_1$  decreases with a step proportional to the photocurrent. Whenever the voltage intersects  $V_{bol_i}$ , the OTA switches to the initial state and a new cycle starts. The digital buffer located after the opamp is needed to increase switching speed and to stabilize the operation. The oscillation period is given by this equation:

$$T = \frac{C \cdot (V_{DD} - V_{bot})}{I_{ph} + I_{dark} - I_{leakage}} + T_d + T_{reset}$$

(1)

Where  $I_{dark}$  is the photodiodes' dark current.  $T_d$  is the digital buffer delay, and  $T_{reset}$  is the time needed to reset the integration capacitance,  $C = C_{ph} + C_1$ . According to Muller and Kamins [17],  $I_{dark}$  can be expressed as:

$$I_{dark} = \frac{A_j \cdot q \cdot n_i \cdot W}{2 \cdot \tau_0} \tag{2}$$

It depends on the effective lifetime of minority carriers,  $\tau_0$ , that has a strong dependence with temperature; the width of the depletion region, W; the doping,  $n_i$ ; and the effective area of influence of the incident light,  $A_j$ . None of these parameters is disclosed by the foundry.  $I_{leakage}$  is the transistors leakage introduced by transistors  $M_{p1}$  and  $M_{p2}$  in Fig. 2. It can be estimated with the BSIM model equation:

$$I_{leakage} = I_0 \cdot e^{\frac{V_{gs} - V_{lh}}{nU_T}} \cdot \left(1 - e^{-\frac{V_{ds}}{U_T}}\right),\tag{3}$$

with

$$I_0 = \frac{W\mu_o C_{ox} U_T^2 e^{1.8}}{L}$$

Photodiodes dimensions were  $16\mu m \times 13\mu m$ . We connected two of them in parallel. According to the transistors models provided by the technology,  $I_{leakage} \approx 65 \mathrm{pA}$ .  $I_{dark}$  depends on temperature, the reverse bias voltage, and the photodiode type. For instance, according to the diode model provided for the n-well/p<sup>-</sup> sub diode, with a reverse bias voltage equal to  $V_{DD} = 5V$ , and under low illumination conditions with white light (0.8lux),  $I_{dark} = 20 \text{pA}$ ,  $I_{ph} = 50$  pA. Hence, the circuit of Fig. 2 elicits oscillations because  $I_{ph} - I_{dark} > I_{leakage}$ . Under average indoor illumination conditions, the chip illuminance is usually much higher than 0.8lux. Thus, it can be neglected the impact of the dark current, i. e.  $I_{ph} \gg I_{leakage} - I_{dark}$ . For the rest of photodiodes, we do not have models. However, for the illumination values selected to measure the sensitivity in the paper, we observed a linear relationship between the chip illuminance and the output frequency. Therefore, it can be assumed that  $I_{ph} - I_{dark} > I_{leakage}$  too.

$T_d \approx 20$ ns and  $T_{reset} \approx 1.3$ ns is the amount of time required to reset the integration capacitance,  $C = C_1 + C_{ph}$ . When the oscillation period is under average illumination conditions, its value is in the order of milliseconds, and can  $T_d$  and  $T_{reset}$

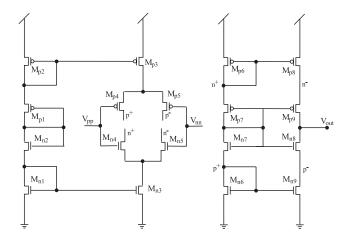

Fig. 3. Schematics of the OTAs. Transistor sizes are (W/L,  $\mu$ m/ $\mu$ m):  $M_{p1} = M_{n2} = 5/1$ ,  $M_{n1} = M_{p2} = 7.5/1$ ,  $M_{n3} = M_{p3} = 5/1$ ,  $M_{n4} = M_{n5} = M_{p4} = M_{p5} = 5/2$ ,  $M_{p6} = M_{p7} = M_{p8} = M_{p9} = 2.5/1$ ,  $M_{n6} = M_{n7} = M_{n8} = M_{n9} = 3/1$ .  $V_{DD} = 5$ V. Its power consumption is approximately 90 $\mu$ A.

can be neglected. Therefore, Equation 1 can be simplified as follows:

$$T \approx \frac{\left(C_1 + C_{ph}\right) \cdot \left(V_{DD} - V_{bot}\right)}{I_{ph}} = \frac{\left(C_1 + C_{ph}\right) \cdot \Delta V}{I_{ph}} \quad (4)$$

According to Equation 4, the frequency of the output pulses is proportional to the input photocurrent. The sensitivity of each photodiode is given by:

$$S = \frac{V_{DD} - V_{bot}}{T \cdot P_0} \propto \frac{V_{DD} - V_{bot}}{T} = \frac{\Delta V}{T} = \frac{I_{ph}}{C_1 + C_{ph}} \quad (5)$$

Where  $P_0$  is the incident optical power. All the photodiodes receive the same power. Since  $\Delta V$  is always a constant, the sensitivity will be proportional to the oscillation frequency. Note, that the oscillation frequency depends on the ratio  $I_{ph}/C_{ph}$  of each photodiode, for a given incident power. In our implementation, we made  $C_1 = 40$  fF, that is a value large enough to have a good matching between different capacitances. Thus, measuring the oscillation frequencies and the incident light power, it is possible to gauge the photodiodes sensitivities. Note that, according to Equation 5, it is not necessary to measure the incident optical power if our target is only to determine what photodiode is more sensitive to light.

Fig. 3 shows the implementation of the OTAs in Fig. 2. Their design is an adapted version of the original architecture proposed by Lu [18]. It has wide dynamic range operation and can drive large output loads. It does not require any extra pad for biasing. Our target was to minimize the number of pads, avoiding extra chip pins for biasing. One OTA was configured as a simple comparator. The other one, that is connected to an output analog pad, functions as an analog buffer to scan the output voltages at the integration capacitances. For a fair comparison of the photodiodes spiking frequencies,  $\Delta V = V_{DD} - V_{bot}$  in Equation 4, must be exactly the same for four the different I&F circuits. The comparators are expected to have DC offset variations in the order of mV. To be sure that there is no variation of  $\Delta V$  between the

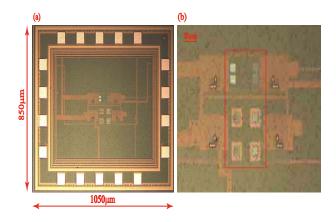

Fig. 4. Chip microphotograph. Chip dimensions are  $1050\mu m \times 850\mu m$ . Photodiodes dimensions were  $16\mu m \times 13\mu m$ . Four pairs of photodiodes were implemented. (a) Entire chip. (b) Detail of the four pairs of photodiodes.

I&F circuits,  $\Delta V$  can be measured with the source follower output ( $V_{scan_i}$  in Fig. 2) and tuned accordingly adjusting  $V_{bot_i}$ . We implemented four integrate-and-fire circuits in total, corresponding to each photodiode type in Fig. 1.

#### **III. EXPERIMENTAL RESULTS**

#### A. Experimental Setup and Circuit Operation

Fig. 4.a shows a microphotograph of the chip. Its dimensions are  $1050\mu m \times 850\mu m$ . All the photodiodes have exactly the same sizes in order to compare them. Since we expected low sensitivity at certain wavelengths, specially for the n<sup>+</sup>/ p<sup>-</sup> substrate junction photodiode (D4) within the NIR band, we implemented photodiodes with large pitches to be able to operate with our experimental setup and take measurements in the visible band. Their sizes are  $16\mu m \times 13\mu m$ . We have implemented two diodes of each type (see Fig. 4.b). They are connected in parallel to one I&F circuit like the one depicted in Fig. 2. Each integrate-and-fire circuit implementation occupies  $90\mu m \times 60\mu m$  and requires only two pads for its implementation ( $V_{scan_i}$ , and  $V_{bot_i}$  signals). The reset signal  $V_{RESET}$  can be shared by all the I&F circuits.

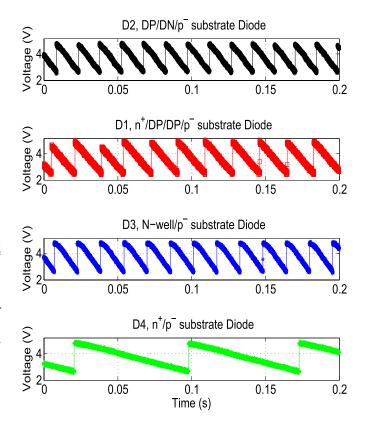

Fig. 5 displays the typical transient voltages at the comparator's input of the I&F circuit depicted in Fig. 2 when the photodiodes are exposed to indoor illumination of approximately 400lux generated with a white light source. The analog buffer depicted in Fig. 3 was connected to  $C_1$  to scan the transient voltage variations. Small variations of the comparators' thresholds are expected due to mismatch. Typically there are a few millivolts offset between different comparators. To ensure before gauging the diodes' sensitivity, that  $\Delta V_i$  was the same for the four integrate-and-fire circuits, the voltages values of  $V_{bot_i}$  were tuned accordingly for each comparator.

During the experiments, all the photodiodes were exposed to the same light intensity at constant temperature. Measurements were repeated several times and averaged. Fig. 6 shows the experimental setup. A white light Oriel/Newport 66884 tungsten lamp was employed as controlled light source. Its light beam is split into two light beams with the same power inside an integrating sphere. The first one is directed to

Fig. 5. Typical integrate-and-fire transient voltages at capacitor  $C_1$  in the oscillator depicted in Fig. 2. Photodiodes were exposed to indoor illumination. Output frequencies are proportional to their photocurrents.  $\Delta V_i$  can be adjusted independently for each oscillator.

Fig. 6. Experimental setup to characterize the photodiodes. An Oriel/ Newport 66884 source was used as a white light source for the experiments. An integrating sphere was placed to split the light beam into two independents beams. One of them was sent to a light power meter. The other one was sent to the sensor through a diffuser to assure that all the photodiodes receive the same amount of power. In between the light source and the integrating sphere, we placed two filter holders to place color and neutral density filters. Main components have been highlighted.

a Newport 1930-C light power meter to measure the power of the incident light. The second one is directed to the chip through a diffuser to assure that all the pixels receive exactly the same light intensity. Hence, it is always possible to monitor the power of the incident light on chip. There are two filter  $10^{4}$

10<sup>3</sup>

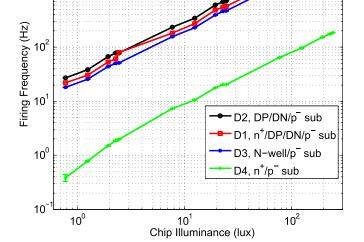

Fig. 7. Spiking frequencies versus illumination values. Photodiodes were illuminated with a white Lambertian source.

holders in the path in between the light source and the integrating sphere. Its purpose is to place discrete filters to either attenuate or filter the incident light when necessary, depending on the experiment. The setup is robust to possible variations of the filters transmission coefficients, and the lamp power irradiance variations at different wavelengths.

## B. Comparison of Diodes' Sensitivity to White Light

To compare the diodes' sensitivity to white light, we exposed the chip to the white Lambertian source Oriel/Newport 66884. Neutral density filters were employed to attenuate the light intensity emitted by the light source. Measurements were repeated for different illumination values at constant temperature. The output spiking frequency of each photodiode for each illumination value has been plotted in Fig. 7. Error bars indicate the standard deviation between measurements. For all the diodes, there is a linear dependence between illumination and the firing frequency and the illumination values. Hence, we can assume that  $I_{ph} - I_{dark} > I_{leakage}$ . According to Equation 5, the ratio between two diodes firing frequencies is proportional to the ratio between photodiodes' sensitivities, i.e.:

$$\frac{f_1}{f_2} = \frac{S1}{S2} = \frac{I_{ph_1}}{I_{ph_2}} \cdot \frac{C_1 + C_{ph_1}}{C_1 + C_{ph_2}} \tag{6}$$

After analyzing the results, the double diode (D2) made with deep p-well/deep n-well and a deep n-well/p<sup>-</sup> substrate happens to be the more efficient one. In second place, it comes the triple-junction photodiode, D1 (n<sup>+</sup>/deep p-well, p-well/deep n-well and a deep n-well/p<sup>-</sup> substrate junctions). The conventional diode with a n-well/p- substrate (D3) junction offers good performance in the whole visible spectrum, but it has less sensitivity than the ones built with stacked photodiodes

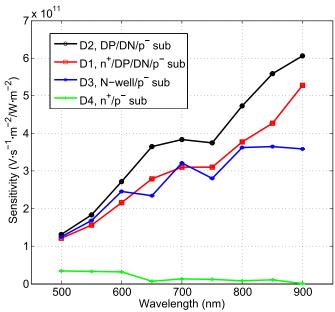

Fig. 8. Photodiodes spectral sensitivity. Discrete optical filters were introduced to obtain each measurement. The DP/DN/p<sup>-</sup> substrate photodiode (D2) has a the highest sensitivity at 900nm.

operating in parallel. The  $n^+/p^-$  substrate diode (D4) is the one with less sensitivity, as it was expected.

If we compute the ratios between the firing frequencies, with the data of Fig. 7, we obtain:  $S_2/S_1 = 1.25$ ,  $S_2/S_3 = 1.55$ , and  $S_2/S_4 = 35$ . We can state that the new photodiodes made with a deep n-well offer more sensitivity than the classic ones. Hence, technologies that offer a deep n-well layer could benefit of it. We could expect more sensitivity for the triple junction photodiode (D1). However its performance is slightly worse than the one of the double-junction diode. The reasons can be that the top extra diode presents in the triple-junction diode offers poor responsivity and adds an extra junction capacitance. Metal lines, and vias involved in its layout design also limit the performance.

## C. Spectral Sensitivity

In order to determine the spectral diode sensitivity, we exposed them to colored light. To do so, we placed color discrete filters in the lens holders in between the white light source and the photodiodes as it is shown in Fig. 6. Filters have narrow band spectra of approximately 20nm centered at certain wavelengths. Incident power on chip was measured for each filter to determine the spectral sensitivity of each photodiode according Equation 5. Note that to take this measurements, it is necessary to measure the incident power because all the filters do not have the same transmission coefficients, and the light source spectrum is not totally flat.

Fig. 8 displays the the sensitivity of each photodiode to each wavelength. As we were expecting, the  $n^+/p^-$  substrate diode (D4) has better performance for shorter wavelengths. Its sensitivity is lower than the other photodiodes for all the wavelength values. The double- and triple-junction

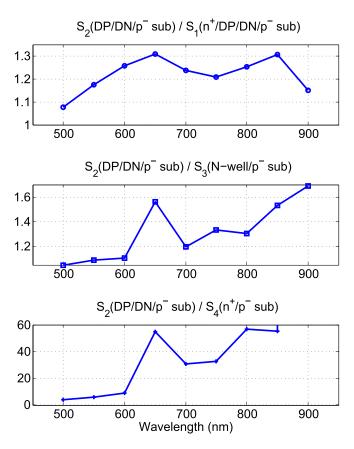

Fig. 9. Ratio between photodiodes' sensitivities. We have compared the photodiode with higher sensitivity (D2,  $DP/DN/p^-$  substrate) over the other three photodiodes depicted in Fig. 1 (D1, D3, and D4).

photodiodes (D2 and D1) have more sensitivity within the NIR band than others. The reason is that the buried photodiodes are more sensitive to longer wavelengths [10], [11]. Longer wavelength photons are less energetic. Hence, they have higher probability of traveling deeper into the cristal before generating electron-hole pairs. Such electrons can be caught easier if the p/n junctions are placed closer to the regions where they are generated. Thus, by having different diodes whose depletion regions are at different depths, the probability of detecting photons at different wavelengths of the visible and the NIR spectrum is higher. The double-junction photodiode (D2) is the one with higher sensitivity for all the wavelengths values. However, its shows similar performance than the triple-junction diode (D1) for shorter wavelengths because its top  $n^+$ /deep p-well diode contributes more to the resultant photocurrent, increasing the photodiode's sensitivity. The sensitivity values that we measured single junction diodes are similar to the ones reported by other authors. For instance, for the n-well/p<sup>-</sup> sub diode (D3), the sensitivity values are alike to the reported by Katic et al. [3], using a standard non-CIS technology. For the stacked photodiodes proposed in the paper, we did not find equivalent results published so far.

Fig. 9 shows the ratios between the photodiodes sensitivities for each wavelength. We have compared the sensitivity of the most efficient diode, D2 (DP/DN/p<sup>-</sup> sub) over the sensitivity of the other three photodiodes (D1, D3, and D4). It can be

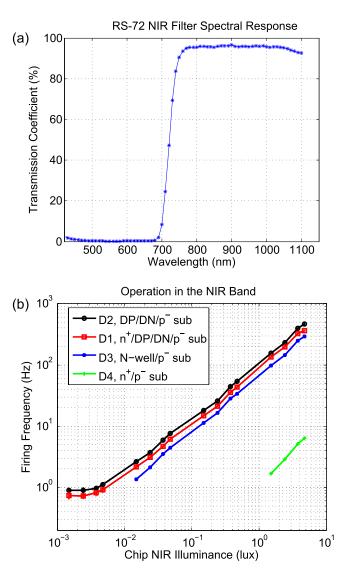

Fig. 10. (a) RS-72 NIR filter measured spectral response. (b) Spiking frequencies versus illumination values. Diodes were illuminated with NIR light between [750,1100]nm.

noticed that it is the most efficient for all the wavelengths. If we compare its performance to the classic n-well/p<sup>-</sup> substrate photodiode sensitivity (S3), we observe that the double-stacked photodiode (D1) has is specially more efficient within the NIR band. For instance, we measured over 70% more sensitivity at 900nm.

## D. Performance in the NIR Band

Since we observed a clear benefit of using stacked photodiodes operating within the NIR band, we have compared the diodes sensitivity within this spectral region. To do so, we employed a R72 filter from Edmund Optics. It is a bandpass filter with a cut on wavelength around 750nm. Its spectral response was measured and it is shown in Fig. 10.a. Within the interval [750, 1100]nm, it has flat response. Radiation below 700nm is rejected. We gauged the diodes spiking frequencies for different NIR light intensity values. The ratio between the diodes sensitivities is constant as long as  $I_{ph}+I_{dark} > I_{leakage}$ .

## E. Stacked Diodes Design Trade-Offs

The implementation of stacked diodes in standard fabrication processes has some trade-offs that should be taken into account. According to our expertise implementing them in different standard fabrication technologies, we can remark that:

- Stacked photodiodes require a deep n-well layer for their implementation. Usually, the minumum distances between a deep n-well and a n-well are higher than between two conventional n-wells.

- Layout design is a bit more complicated. i.e. there are more layers and design rules involved in the photodiode composition.

- Some technologies do not provide models of for the buried photodiodes.

- The minimum pitch required to place an deep n-well is usually higher than for a conventional n-well.

Particularly, using staked photodiodes, it was challenging to achieve in a pixel design a diode pitch below  $10\mu$ m in the 180nm technology chosen to conduct this research work. Nowadays almost all modern standard fabrication technologies offer deep n-well implementations. Although the possibility of allocating a deep n-well on a chip design was not initially conceived to create stacked photodiodes, we believe that foundries will exploit this potential soon, by relaxing the design rules involving deep n-well design. Thus, the minimum pitch to implement stacked photodiodes could be reduced.

#### IV. DISCUSSION

According to the results of Fig. 7, Fig. 8, and Fig. 10, it can be stated that it is advantageous to use stacked photodiodes to implement photonic devices in order to increase their sensitivity to light. The benefit of using them is specially remarkable working in the NIR band.

Comparing the implemented photodiodes depicted in Fig. 1, the double-junction photodiode (D2) is the one that offers better performance. Adding an extra diode made with a n+/deep p-well junction does not improve sensitivity. The are several reasons: this extra diode has very low quantum efficiency in the visible spectrum, due to the low area of its depletion region; it adds extra complexity to the layout (metal lines and vias), and it has an extra junction capacitance. Classic photodiodes with simple p/n junctions (D3 and D4) offers less sensitivity. Nevertheless, they can still be interesting (or the only choice) in sensors that require pixels with fine pitch with more relaxed layout design rules.

The results of this paper suggest that the classic choice of a n-well/ $p^-$  substrate diode (D3) is less competitive, in terms of sensitivity, than the proposed stacked photodiodes. The sensitivity to white light can be increased by 55% using

a double-stacked photodiode over a conventional diode made with a n-well/p<sup>-</sup> substrate junction. Furthermore, in the NIR band the sensitivity increment is higher. We measured an overall sensitivity increment of 62% operating the NIR band with peaks of 70% at 900nm. These features should be taken into account to maximize the photodiodes' sensitivity when designing chip prototypes in a standard fabrication technology. The circuitry described to characterize the photodiodes is simple and does not require a lot of area: only three pins are necessary to compute the photodiodes' sensitivity without using dedicated equipment to gauge photocurrents.

#### ACKNOWLEDGMENTS

The authors are really grateful to Miguel A. Lagos-Florido for the PCB design.

#### REFERENCES

- [1] A. Moini, Vision Chips. Norwell, MA, USA: Kluwer, 2000.

- [2] G. Köklü, R. Etienne-Cummings, Y. Leblebici, G. De Micheli, and S. Carrara, "Characterization of standard CMOS compatible photodiodes and pixels for lab-on-chip devices," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2013, pp. 1075–1078.

- [3] N. Katic, A. Schmid, and Y. Leblebici, "CMOS-integrated photodetectors for neuromorphic and smart imaging applications: A low-cost design and measurement method," in *Proc. IEEE SENSORS*, Nov. 2014, pp. 1579–1582.

- [4] S. Vargas-Sierra, "Proposal of architecture and circuits for dynamic range enhancement of vision systems on chip designed in deep submicron technologies," Ph.D. dissertation, Dept. Electron. Electromag., Univ. Seville, Seville, Spain, 2012.

- [5] TowerJazz Semiconductor Foundry. (Feb. 2016). [Online]. Available: http://www.towerjazz.com

- [6] R. Berner and T. Delbruck, "Event-based pixel sensitive to changes of color and brightness," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 7, pp. 1581–1590, Jul. 2011.

- [7] J. A. Leñero-Bardallo, D. H. Bryn, and P. Häfliger, "Bio-inspired asynchronous pixel event tricolor vision sensor," *IEEE Trans. Biomed. Circuits Syst.*, vol. 8, no. 3, pp. 345–357, Jun. 2014.

- [8] Ł. Farian, J. A. Leñero-Bardallo, and P. Häfliger, "A bio-inspired AER temporal tri-color differentiator pixel array," *IEEE Trans. Biomed. Circuits Syst.*, vol. 9, no. 5, pp. 686–698, Oct. 2015.

- [9] J. Fernández-Berni, R. Carmona-Galán, and Á. Rodríguez-Vázquez, "FLIP-Q: A QCIF resolution focal-plane array for low-power image processing," in *Low-Power Smart Imagers for Vision-Enabled Sensor Networks*. New York, NY, USA: Springer, 2012, pp. 67–109.

- [10] S. M. Sze, Semiconductor Devices Physics and Technology. Hoboken, NJ, USA: Wiley, 2006.

- [11] Foveon Inc. (Feb. 2016). [Online]. Available: http://www.foveon.com

- [12] J. A. Leñero-Bardallo, D. H. Bryn, and P. Häfliger, "Flame monitoring with an AER color vision sensor," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2013, pp. 2404–2407.

- [13] S. Schidl, A. Polzer, J. Dong, K. Schneider-Hornstein, and H. Zimmermann, "Investigation of transient photocurrent response of triple pn junction structure," *Electron. Lett.*, vol. 49, no. 4, pp. 284–285, Feb. 2013.

- [14] S. Schidl and H. Zimmermann, "AC response of 0.35 μm CMOS triplejunction photodetector," *Electron. Lett.*, vol. 50, no. 23, pp. 1728–1729, Nov. 2014.

- [15] EMVA Standard. (Feb. 2016). [Online]. Available: http://www.emva.org/ standards-technology/emva-1288/

- [16] E. Culurciello, R. Etienne-Cummings, and K. A. Boahen, "A biomorphic digital image sensor," *IEEE J. Solid-State Circuits*, vol. 38, no. 2, pp. 281–294, Feb. 2003.

- [17] R. S. Muller and T. I. Kamins, *Device Electronics for Integrated Circuits*. Hoboken, NJ, USA: Wiley, 1986.

- [18] C.-W. Lu, "High-speed driving scheme and compact high-speed lowpower rail-to-rail class-B buffer amplifier for LCD applications," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1938–1947, Nov. 2004.

Juan Antonio Leñero-Bardallo received the M.Sc. degree in telecommunications engineering and the Ph.D. degree in microelectronics from the Universidad de Sevilla, Seville, Spain, in 2005 and 2010, respectively.

He served in several academic institutions and the semiconductor industry. In 2010, he was a Post-Doctoral Associate at Yale University, New Haven, CT, USA, From 2010 to 2013, he was a Post-Doctoral Associate at the University of Oslo. From 2013 to 2016, he was a Post-Doctoral Asso-

ciate at the Universidad de Sevilla, Spain. From March 2016 to August 2016, he was a Senior Engineer at Chronocam Inc.

Since September 2016, he is an Assistant Teacher at the University of Cádiz, Spain, where he teaches and conducts research.

Dr. Leñero-Bardallo's main research interests include address event representation vision systems, frame-based vision sensors, smart sensors, wireless vision sensor networks, signal processing, and very large scale integration emulators of biological systems. He has been a member of the IEEE Sensory Systems Committee since 2012.

Ricardo Carmona-Galán (M'98-SM'16) received the degree in electronic physics and the Ph.D. degree in microelectronics from the Universidad de Sevilla, Spain. He was a Research Assistant with the EECS Department, University of California at Berkeley. He was an Assistant Professor at the School of Engineering, Universidad de Sevilla. Since 2005, he has been a Tenured Scientist with the Institute of Microelectronics of Seville. He held a post-doctoral position with the University of Notre Dame, IN, where he was involved in interfaces for CMOS

compatible nanostructures for multispectral light sensing. He has collaborated with start-up companies, such as Anafocus, Seville, and Eutecus, Berkeley. He has designed several vision chips implementing different focal plane operators for early vision processing. He is currently the Co-Inventor of several patents. He has co-authored over 120 journal and conference papers and a book Low-Power Vision Sensors for vision-enabled sensor networks. His current research interests lie in the design of low-power smart image sensors, single-photon detection and ToF estimation, 3-D integrated circuits for autonomous vision systems, and VLSI implementation of concurrent sensor/processor arrays for real time image processing and vision. He is a member of the IEEE Circuits and Systems and Solid-State Circuits Societies. He has received the Best Paper Award of the IEEE-CASS Technical Committee on Sensory Systems at ISCAS 2015, together with Dr. Vornicu and Prof. Rodríguez-Vázquez. He has been an Associate Editor of the IEEE TCAS-I. He is currently an Associate Editor of the Journal on Real-Time Image Processing (Springer). He received a Certificate of Teaching Excellence from the Universidad de Sevilla.

Delgado-Restituto (M'96-SM'12) Manuel received the M.S. degree in physics and the Ph.D. degree (Hons.) in physics electronics from the Universidad de Sevilla, Spain, in 1988 and 1996, respectively. Since the Doctorate, he has been working with the Institute of Microelectronics of Seville/CNM-CSIC (IMSE-CNM/CSIC). In September 1999, he obtained a permanent position as "Científico Titular del CSIC" (CSIC Tenured Scientist, equivalent to Assistant Professor) and in June 2009, he upgraded to "Investigador Científico CSIC" (CSIC Research Scientist, equivalent to Associate Professor).

Currently, he heads a research group at IMSE-CNM/CSIC on low-power medical microelectronics and works in the design of silicon microsystems to understanding biological neural systems, the development of neural prostheses and brain-machine interfaces, the implementation of wireless body area network transceivers and the realization of RFID transponders with biomedical sensing capabilities (2005).

Dr. Delgado-Restituto has co-authored the books Device-Level Modeling and Synthesis of High-Performance Pipeline ADCs (Springer, 2011) and Ultralow Power Transceiver for Wireless Body Area Networks (Springer, 2013), more than 20 chapters in contributed books, including original tutorials on chaotic integrated circuits, design of data converters, and chips for bioengineering and neuroscience, and 150 articles in peer-review specialized publications.

Dr. Delgado-Restituto is a member of the IEEE CAS Biomedical Circuits and Systems Technical Committee. He has served as the Technical Program Chair in different international IEEE conferences, including ECCTD 2007, ESSCIRC 2010, and ICECS 2012. He served as an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II from 2006 to 2007 and the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I from 2008 to 2011. He also served as the Deputy Editor-in-Chief of the IEEE JOURNAL ON EMERGING AND SELECTED TOPICS IN CIRCUITS AND SYSTEMS from 2011 to 2013 and an Editor-in-Chief of the IEEE JOURNAL ON EMERGING AND SELECTED TOPICS IN CIRCUITS AND SYSTEMS from 2014 to 2015. He is currently the Vice President of Publications of the IEEE CAS in 2016.

Ángel Rodríguez-Vázquez (F'99) received the undergraduate and Ph.D. degrees in physicselectronics with several national and international awards, including an IEEE Award. After different research stays with the University of California-Berkeley and Texas A&M University, he became a Full Professor of Electronics with the University of Sevilla in 1995. He co-founded the Institute of Microelectronics of Sevilla, under the umbrella of the Spanish Council Research (CSIC) and the University of Sevilla and started a research group

on Analog and Mixed-Signal Circuits for Sensors and Communications. In 2001, he was the main promotor and co-founder of the start-up company AnaFocus Ltd., and served as the CEO, on leave from the University, until 2009, when the company reached maturity as a worldwide provider of smart CMOS imagers and vision systems-on-chip.

His research is on the design of analog and mixed-signal front-ends for sensing and communication, including smart imagers, vision chips, and low-power sensory-processing microsystems. He has authored 11 books, 36 additional book chapters, and some 150 journal articles in peer-review specialized publications. He has presented invited plenary lectures at different international conferences and has received a number of awards for his research (the IEEE Guillemin-Cauer Best Paper Award, two Wiley's IJCTA Best Paper Awards, two IEEE ECCTD Best Paper Award, one SPIE-IST Electronic Imaging Best Paper Award, one IEEE ISCAS Best Paper Award, one IEEE ISCAS Best Demo-Paper Award, and one IEEE ICECS Best Demo-Paper Award). He was an elected Fellow of the IEEE for his contributions to the design of chaos-based communication chips and neurofuzzy chips. His research work received some 6939 citations; he has an h-index of 42 and an i10-index of 142.

He has always been looking for the balance between long-term research and innovative industrial developments. AnaFocus Ltd. was founded on the basis of his patents on vision chips and he participated in the foundation of the Hungarian start-up company AnaLogic Ltd. He has eight patents filed, three of which have been licensed to companies. He has served as Editor, Associate Editor, and Guest Editor for different IEEE and non-IEEE journals. He is on the committee of several international journals and conferences, and has chaired several international IEEE and SPIE conferences. He served as VP Region 8 of the IEEE Circuits and Systems Society from 2009 to 2012 and as Chair of the IEEE CASS Fellow Evaluation Committee in 2010 and from 2012 to 2015.