### Trabajo de Fin de Máster "Máster Universitario en Microelectónica: Diseño y Aplicaciones de Sistemas Micro/Nanométricos"

### Optimización del flujo de simulación de defectos y fallos en circuitos analógicos y de señal mixta

Estudiante: Valentín Gutiérrez Gil Tutor: Gildas Leger Septiembre 2018

### Optimization of the defect and fault simulation flow in analog and mixed signal circuits

Student: Valentin Gutierrez Gil Advisor: Gildas Leger

Trabajo Fin de Máster: Máster Universitario en Microelectónica: Diseño y Aplicaciones de Sistemas

September 2018

### Acknowledgements

I would like to express my deepest appreciation to all those who provided me the possibility to complete this work. A special gratitude I give to my advisor, Dr. Gildas Leger, whose contribution in stimulating suggestions and encouragement, helped me to coordinate my project especially in writing this report.

Furthermore, I would like to with much appreciation to the members of the n-PATETIC project, namely, Adoración Rueda, Antonio López, Antonio Ginés, Eduardo Peralías and my advisor for giving me not only the opportunity but for teaching me everything I'm proud of.

Finally, an special thank to my family, whether blood or friendship, for enduring this whole journey with me.

### Contents

| 1        | Intr                                                             | Introduction 1                                                                                                                                               |   |  |  |  |

|----------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|

|          | 1.1 The goal: Test validation                                    |                                                                                                                                                              |   |  |  |  |

|          | <ul><li>1.2 The issue: Reducing the computational cost</li></ul> |                                                                                                                                                              |   |  |  |  |

|          |                                                                  |                                                                                                                                                              |   |  |  |  |

|          | 1.4 State-of-the-Art                                             |                                                                                                                                                              |   |  |  |  |

|          |                                                                  | 1.4.1 Defect extraction                                                                                                                                      | 5 |  |  |  |

|          |                                                                  | 1.4.2 Defect modeling $\ldots \ldots \ldots$ | 7 |  |  |  |

|          |                                                                  | 1.4.3 Defect simulation                                                                                                                                      | 3 |  |  |  |

| <b>2</b> | The proposed Framework 13                                        |                                                                                                                                                              |   |  |  |  |

|          | 2.1                                                              | A complete picture of test quality                                                                                                                           | 3 |  |  |  |

|          |                                                                  | 2.1.1 Modified Defect Coverage                                                                                                                               | 1 |  |  |  |

|          |                                                                  | 2.1.2 Modified Fault Escape                                                                                                                                  | 1 |  |  |  |

|          |                                                                  | 2.1.3 Severity $\ldots$ 15                                                                                                                                   | 5 |  |  |  |

|          | 2.2                                                              | Sequential defect simulation with early stopping 16                                                                                                          | 3 |  |  |  |

| 3        | Statistical evaluation of test metrics                           |                                                                                                                                                              |   |  |  |  |

|          | 3.1                                                              | Likelihood random sampling                                                                                                                                   | 3 |  |  |  |

|          | 3.2                                                              | Estimate of confidence intervals                                                                                                                             | 5 |  |  |  |

|          |                                                                  | 3.2.1 Checking confidence intervals                                                                                                                          | 7 |  |  |  |

| 4        | Description of the developed tools 31                            |                                                                                                                                                              |   |  |  |  |

|          | 4.1                                                              | Defect models                                                                                                                                                | 1 |  |  |  |

|          |                                                                  | 4.1.1 Convergence error with Open-Gate defect                                                                                                                | 3 |  |  |  |

|          | 4.2                                                              | Injection                                                                                                                                                    | 5 |  |  |  |

|          | 4.3                                                              | Simulation                                                                                                                                                   |   |  |  |  |

|          | 4.4                                                              | Collateral developments and applications                                                                                                                     | ) |  |  |  |

|          |                                                                  | 4.4.1 Monte-Carlo analysis                                                                                                                                   | ) |  |  |  |

|          |                                                                  | 4.4.2 Single Event                                                                                                                                           | ) |  |  |  |

| <b>5</b> | Cases of study                            |        |                                  |    |  |  |

|----------|-------------------------------------------|--------|----------------------------------|----|--|--|

|          | 5.1 First case of study: Resistive buffer |        |                                  |    |  |  |

|          |                                           | 5.1.1  | Circuit description              | 43 |  |  |

|          |                                           | 5.1.2  | Test description                 | 45 |  |  |

|          |                                           | 5.1.3  | Results discussion               | 47 |  |  |

|          | 5.2                                       | Second | d case of study: Source follower | 51 |  |  |

|          |                                           | 5.2.1  | Circuit description              | 52 |  |  |

|          |                                           | 5.2.2  | Test description                 | 53 |  |  |

|          |                                           | 5.2.3  | Results discussion               | 54 |  |  |

|          |                                           |        |                                  |    |  |  |

| 6        | 6 Conclusions                             |        |                                  |    |  |  |

### Chapter 1

### Introduction

### 1.1 The goal: Test validation

Historically, the golden standard for analog, Mixed-signal and RF circuit (AMS-RF) test has been functional testing. Indeed, an AMS-RF circuit is defined by its datasheet: a number of performance metrics associated with standard measurement procedures are guaranteed to be within a given range. For instance, the static Integral Non-Linearity of and Analog-to-Digital Converter can be specified to be below 1.4 Least Significant Bits and there that metric can be measured in several ways like histogram testing or servo-loop, as defined in the IEEE 1241 standard [1]. With such a definition, it seems perfectly logical to consider functional testing as a reference: since the datasheet is what is sold to the customer, performing the measurements that are associated to the specified performance parameters should, by definition, guarantee the detection of any faulty behavior.

While this is still true, there are two trends that challenge the suitability of functional test. The first and oldest one is cost: AMS-RF circuits are more and more complex and embedded in larger systems. As a result, it may be difficult to reach the primary input and output of the circuits. In addition, the number of specifications increases and some of them can involve lengthy measurements (the direct measurement of the Error Vector Magnitude in transceivers is a good example). The test time is thus on the rise and so the test cost. By the way, the test cost of a modern System-on-Chip can be dominated by the analog section in spite of the clear superiority of digital circuits in terms of area.

The second and more recent trend questions the quality of functional test itself. Indeed, functional test is performed at time zero but there may be defects or deficiencies that cause a minimum performance degradation at time zero, still within the specifications, but may evolve in time with circuit aging, or simply be stimulated by real-world usage. In safety- or mission-critical applications (like automotive, health-care, space, ...), defects are perceived as a threat even if they do not impact performance in the production line. In the automotive industry, some cases of field issues could be traced to manufacturing defects that were not actually detected by functional test.

As a response to these two trends, there exist a demand for test alternatives to functional test. Some of the proposed solutions respond essentially to the cost issue like reduced (non-exhaustive) functional test, indirect test [2–4] and its recent machine-learning update, Built-In Self-Test (BIST) approaches, etc. And other solutions rather try to mimic what happened in the digital world –where functional test quickly became prohibitive due to the ever increasing number of states to be tested. These solutions aim at detecting defect and their primary goal is not to measure the specifications but rather to guarantee that the circuit exactly corresponds to what was designed. These solutions are gathered under the term of Defect-Oriented Testing, even if they are mostly ad-hoc to a particular topology or at least circuit family.

Independently of the cause, the shift from exhaustive functional testing is a paradigm change from the point of view of validation: If exhaustive functional test is impossible, too costly or simply not considered as perfect anymore, then the test strategy has to be validated before its implementation in the production line. If it involves some design modifications (DfT or BIST) the quality must be assessed at early phases of the design. Unless some mathematical proof of test quality could obtained through formal methods, that validation necessarily involves defect simulation [5,6].

## 1.2 The issue: Reducing the computational cost

In the case of an exhaustive functional test, part of its validation is implicitly done in the design phase. Indeed, the performance measurements are simulated under both process and mismatch variations and the obtained metrics are verified to remain within their specified validity ranges. By definition, an exhaustive functional test would detect any deviation out of the specifications. However, if the target is to assess the defect coverage (which in the case of exhaustive functional case is the proportion of defects that do affect performance), defect simulation has to be done.

If a Defect-Oriented Test or any alternative to exhaustive functional test has to be evaluated, then it should be validated with respect to process and mismatch variations to verify that it does not produce yield losses (i.e. false positive) or test escapes (i.e. false negatives) under normal process conditions. And obviously, a defect simulation would also have to be performed to assess the defect coverage of the proposed test. So as we can see, defect simulation seems unavoidable.

The number of possible defects sites obviously increases with the number of nodes and transistors. Defect simulation can be very challenging from a computational viewpoint, particularly if the tests to be evaluated involve long transient simulation times. If we center our attention only on the possible CMOS transistor defects the relation is straightforward. An approximation for 3 terminal models considers 3 different shorts (Gate-Source, Gate-Drain and Source-Drain) and 3 opens (Source, Gate and Drain). There are thus 6 different defects per transistor and ICs with analog transistor counts in the range of 5000 (a medium complexity) would thus lead to 30000 potential defects. Performing an exhaustive simulation of these candidates in not affordable in practice.

Solutions are thus required to evaluate (validate or discard) test strategies as fast as possible.

### **1.3** Clarification on vocabulary

With respect to the terminology, there are two terms that need to be clearly defined: Defect and Fault. In the test bibliography, these two terms are sometimes used indistinctly and this could lead to important conceptual errors in the rest of this manuscript.

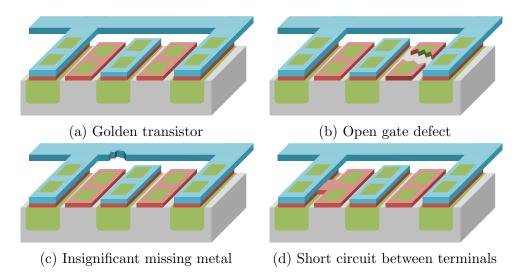

Using [7] as reference, we can define a Defect as a lack or excess of material in any mask used during the fabrication process of an IC. In Fig. 1.1 we have illustrated some examples of defects. Starting from a non defective transistor (fig. 1.1a) we can add or remove material of any layer. For example, in Fig. 1.1b we removed some poly from the gate, generating an open on one of the fingers gate. On the other hand, Fig. 1.1c shows a lack of metal in the horizontal net that, a priori, would not produce any malfunction. Finally, Fig. 1.1d represents a short-circuit between one finger gate and the transistor drain/source. It is crucial to understand that Defects are only manifested in the physical layer of the IC. This is usually a well-accepted definition.

With respect to faults, there are two interpretations that are most of the time not explicitly stated in the bibliography.

The most generic definition would be that a fault is any defect that has an electrical impact of some sort on the behavior of the circuit. In other words, the fault-free and the defective circuits are not electrically equivalent.

Figure 1.1: Examples of possible defects on a two-finger transistor

Such a definition of a fault is most usual in the papers that deal with defect modeling and simulation, which by the way is most of the time called fault-modeling and fault-simulation. Indeed, defects as defined above do not possess intrinsic electrical characteristics and evaluating their impact on a given circuit thus requires a process of electrical modeling. For instance, a short-circuit can be modeled by the inclusion of a extra resistor with a given (parametrized) short resistance. However, such a definition entails a major drawback: the level of detail of defect modeling is always ad-hoc. For instance, the missing material in Fig. 1.1c could be considered irrelevant (and the defect would thus be discarded) or eventually modeled as a slight increase in the resistance of the metal line.

In most papers that deal with alternative test proposals, a fault is usually defined as a defect that cause the test to fail. This looks like a clear definition but it is indeed relative to the test under consideration. Since functional test is still the golden standard in the industry (despite the above-mentioned issue) the best definition of a fault is thus with respect to the functional test of the circuit. In what follows, we will thus call a fault any defect which brings the circuit out of one or more of its specifications.

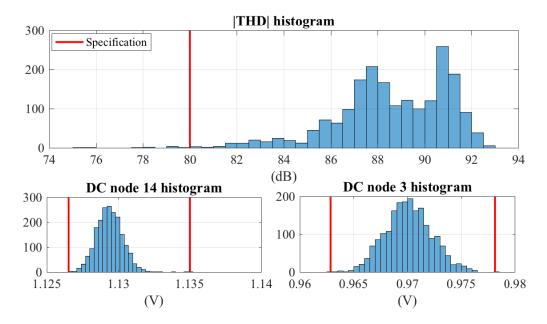

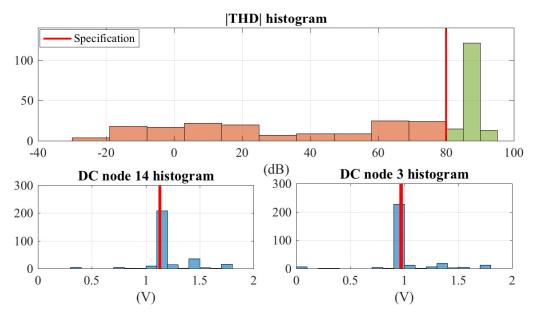

For example, as we will see later, if we have a buffer with a 80dB specification for the Total Harmonic Distortion, any chip that obtains a lower value will be considered faulty. If the design has been properly centered (we thus exclude parametric yield losses), this faulty behavior is necessarily produced by a defect inside the circuit. However, not all defects have to produce a fault. In order to clarify concepts, we will consider the Defects showed in Fig. 1.1. At first sight, we could affirm that 1.1c will not produce a fault itself, since there is not a complete open in that terminal. But if we consider the electromigration effect on that net we can not ensure that the circuit will work properly as long as a non defective one. This defect, that right now can not be considered a fault, could become one in the future.

Defect in 1.1b can be expected to affect performance, but not necessarily cause a fault since it only affects one of the fingers. The electrical effects could be treated as a parametric variation and, maybe, the result of the test would comply the specification. As before, this does not mean that the service life of the circuit is the same.

Finally, 1.1d is a short-circuit between the gate and the source or drain. This is clearly bad, since all the finger gates are usually connected together. This defect will most probably affect the behavior and cause a fault. From now on, we will maintain this nomenclature, even though the references do not mention it in the same way.

### 1.4 State-of-the-Art

It is not till the 80s that industry focused on DoT for AMS-RF circuits. Even though many research groups where working on the field, the biggest changes were made back then. During these years the main issues to be resolved ranged from the definition of the models to the simulation process.

#### 1.4.1 Defect extraction

One of the solutions proposed for defects extraction was the Inductive Fault Analysis (IFA) process. The first mention of this where in [7]. The IFA procedure involves, basically, three major steps. First defects are generated base on statistical data obtained from the fabrication process. Second, the defect behavior is analyzed and the a circuit level model is produced. Finally, defects are classified in types and ranked according to their likelihood of occurrence.

Different groups [2,6,7] have quoted that considering all defects as equally probable is a poor approximation of reality that may induce a bias in the estimate of test quality metrics. For that reason it is needed to take into account the relative likelihood of the different defects RL, that is to say, the relative probability of occurrence of each defect. Intrinsically to this definition it is the fact that the sum of the RL of each defect is 1 (eq. 1.1), being Nthe total number of possible defects in the circuit.

$$\sum_{i}^{N} RL_i = 1 \tag{1.1}$$

This parameter is quite difficult to calculate. It is impossible to reach a realistic set of values until the layout of the circuit is defined, and normally the layout is done at the end of the design process. Defect insertion should ideally be done at layout level either following the flow of IFA [7,8] which randomly inserts disks of missing or extra material according to the dust particle distribution statistics provided by the fab, or resorting to the proxy that consists in observing that the probability of occurrence of a short between two nodes is proportional to the parasitic capacitor between these two nodes while the probability of an open is proportional to the parasitic resistor. On an extracted netlist, the list of parasitics provides a list of potential defect sites together with their relative likelihood.

Unfortunately, test strategies must more often than not be evaluated before the layout is available (particularly if DfT methods are not considered as an afterthought). As a result, many defect simulation campaigns are carried out at schematic level. In such cases, the 6-resistor model is often considered [2,9].

Another way to approach defect-extraction is based on the Monte-Carlo method [10]. In this method, random defects are sprinkled over the layout first. Their number varies from a few thousand to several millions. These defects can be divided into a number of groups and the amount of defects fitting into one group determines the chance a certain type of occurrence. After performing transistor-level simulations the parametric defect model is verifiable. As a result of the algorithm the parametric fault model is a large set of functional circuit instances that range from nominal to marginally functional. Therefore, the algorithm outputs the necessary data to estimate fault coverage and yield coverage metrics of a test suite.

Another approach which leads to the same results is based on the critical area principle [11]. This method determines the probability of a certain defect to occur deterministically. The critical area is defined as the layout area that is susceptible to defects. If the central point of a particle lies in this area, the defect will cause a fault in the circuit.

As a summary, IFA uses the layout as a defect probability extractor. With it, we obtain the total number of possible defect candidates (and their associated likelihoods). The simulator afterwards decides what to simulate depending on it. Once the simulation is done, the evaluation of the test starts.

#### 1.4.2 Defect modeling

At this point, we keep having a nomenclature problem. In the digital field the difference between fault and defect can be kept the same but they use fault models instead of the defects ones. That is, they develop fault models of a defective gate and check the performance of the whole circuit. One example of this is the stack-at fault. This defect affects the state of logic signals, either internal or external, in a logic circuit. It transforms the correct value on the defective signal line to a constant logic value, either a logic 0 or a logic 1, referred to as stuck-at-0 (SA0) or stuck-at-1 (SA1), respectively [12]. If we consider this fault we only have to put a net, or part of a net, with a fixed value. Here, the difference is clear, the fault refers to the bad performance of the affected gate and the defect could be anything that produce that fault, a short with power or ground, for example.

Defects have very complex physical characteristics and may be significantly technology-dependent [13]. The description of the physical properties encloses the relationship between process-induced defects and its effect, which allows the definition of the models. Bubbles, falling particles, flakes or irregular dips belong all to the same group are some of the well known spot defects.

In the analog field we can not set this differentiation with our definition. In [14] is given a very good sum up of the types of spot defects we can consider for an IC. These are classified in 11 groups and they involve the mistakes in any mask used during the fabrication process [7]. As mentioned in [15], most of the spot defects produced in a IC can be modeled as open or shorts. We will insert different open or shorts in the circuit but, a priori, we do not know the behavior of that defect. That is why we refer to Defect models instead of Fault models.

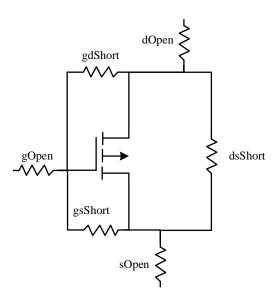

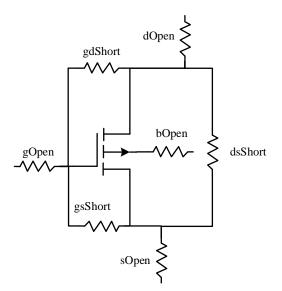

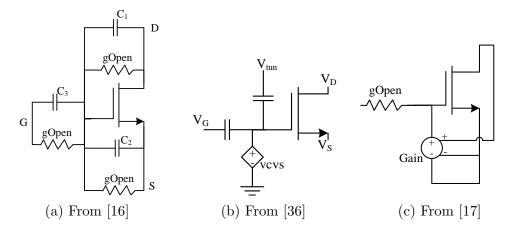

At the IFA process, shorts and opens are inserted in the layout and then the netlist is extracted in order to simulate but as mention before, this is not always possible, so that there are equivalent models attending to the transistors. The most extended defect model is the 6-resistor one. It consist of a possible open in each transistor pin and a short-circuit between each of them. Fig. 1.2 exemplifies that model. On the non-defective transistor each transistor has an ideal value of infinity and zero depending on if the resistor model is a short or an open, respectively. These models are good as a first approximation but there may be convergence problems between SPICE and the gate open model [9,16,17]. However, this point will be dealt with later in Chapter 4.

Figure 1.2: 6 transistor fault model

#### 1.4.3 Defect simulation

Nowadays, there is only two commercial fault simulator for analog and mixed signal circuits: Tessent<sup>®</sup> DefectSim [18], from Mentor<sup>®</sup>.

Tessent<sup>®</sup> DefectSim datasheet gives a brief explanation of the program capabilities. It is able to simulate any combination of Spectre, SPICE, and HDL models, analog/digital circuitry, pre/post-layout sub-circuit netlists. The defect injection can be made from its library of shorts, opens and parametric variabilities or from a custom model defined by the user. At the end of the simulation, the program also outputs an estimated metric of the parametric yield and defect coverage of the test. Automotive industry is one the of most demanding non-defective circuits so it is not a surprise that the program generate the metrics for the ISO-26262 too.

There is another software tool called DOTSS (Defect-Oriented Test Simulation System) from  $NXP^{\textcircled{R}}$  which van be used to perform the simulations [10, 19, 20] but technical details cannot by found in the open litterature. The most interesting part is how it fills the Design Database. It extracts the possible defects from the layout and adapt the effect to the transistor ports to generate a netlist with the fault. Unfortunately, this tool is sold with the fabrication kit.

On the academic side, by contrast, there have been significantly more contributions. It has already been said that the number of possible defects make unmanageable an exhaustive simulation. That is why some of the first efforts center the attention in simulation time reduction. One example of this can be found in [21]. They directly use the IFA flow extracting the defects from the layout by the critical area process. Every defect is weighted using the RL in order to obtain the most significance ones. The list is reduced to the group of most likely defects.

Another method is to simplify the number of nodes. It is trivial to think if the circuit is simpler the simulation will run faster. That is what is done in [22]. They convert non-linear analog circuits into Boolean models, faster to simulate. This method was used in [23] during the simulation process. They only simulated SPICE level model if the block affected by the defect, letting the rest of the circuit as an ideal behavior.

Very close to the previous approximation is in [24] but here they go to a lower level of abstraction. They use a special model of stuck-at fault that affects not the signal path, but the transistors' logic gate. That is the stuckopen and stuck-short. This model substitute the transistor by a unique resistor between the drain and source pin, letting the gate floating. Obviously, this simulation must be done at SPICE level netlist to be able to consider resistors but they only substitute the SPICE model in the defective transistor. The rest of the circuit is in HDL language. Doing this a mixed-signal simulation must be performed and, basing on their results, is remarkably faster than the complete SPICE netlist simulation.

In [25], during the defect extraction process, the authors generate connection schemes between the different sub-circuits that compose the circuit. By doing this, they can isolate independent sections of the chip that does not interact between each other, allowing a reliable divide and conquer approach.

The direct approach to increase simulation speed when we have a big amount of them is to run them in parallel. This method, even though it could be reducibly obvious, can not always be applied. In [26] reached this task with a specific tool called CONCERT2, that can perform DC and transient fault simulations. The simulation speedup is achieved by sharing the intermediate results among the corresponding defective and fault-free circuits.

In another branch of research there are jobs that benefit from the fact that defects which cause significant deviations from the fault-free response are easier to detect than the others, so that simulation accuracy can be lowered. By risking having to repeat the simulation of the defects that do not have a significant effect on the circuit at the higher accurscy, they can reduce the total simulation time for those who do not. In [27] this approach is done with the DC simulation time. By only doing one-step Newton-Raphson iteration to calculate the operating point they not only reduce simulation time but speed up exact fault simulation based on simulation continuation.

A previous work implemented this same idea but trying to accelerate transient simulations. In [28] the speed up the transient analysis by relaxing and tighten the time step dynamically. In order to achieve that, the first perform a DC analysis of all the faults and classify in groups with expected equivalent behavioral. From echa group they simulate the most likely defects in parallel step by step and sharing data between each process to save unnecessary iterations.

Coming back with the first idea of reducing the number of defects to simulate appears the Sensitivity Analysis. With the adjoint network method, for example, the output sensitivities can be computed with respect to the complete defect list at the same time. Indeed, the adjoint network method allows to compute the sensitivity of one output parameter with respect to all component variations (including non-existing components) in only two simulations, one for the original network and one for the corresponding adjoint network [9,29]. This, however, is limited to Linear Time Invariant circuits.

In [30] is presented a technique that enables the derivation of the constraint of an internal functional block with respect to the DC specification. Basing on it, they have implemented a defect simulator that reduces the computational effort by both, removing undetectable defects from the simulation list and performing the defect simulation only in the blocks affected.

In the past few years, the way to consider the problem has changed [6]. Since we can acknowledge that an accurate and faithful defect simulation is computationally too intensive, what is the best way to spend the limited computational resources? As mentioned in [21], a solution is to reduce the number of defects by limiting the evaluation to the most likely ones.

However this may not be representative of the real circuit. Very likely defects (associated to large transistors and/or global nets) may behave differently from unlikely defects (associated to small transistors and or local nets) with respect to test. And despite a significant likelihood difference between individual defects, the population-wise probability of occurrence may not be so different. Indeed, there may be very few though highly-probable defects and many small and unlikely defects.

With this consideration in mind, it was proposed in [15] to use likelihoodweighted defect sampling to obtain a statistically unbiased estimate of defectcoverage. This approach was further refined in [2], proposing a simpler selection algorithm and include the possibility of continuously parametrized defects (i.e. opens and shorts with a given resistance probability density function).

Since exhaustive defect simulation is intractable, the defect coverage obtained by proper defect population sampling is a statistical estimate and as such should be associated to a confidence interval.

In the next chapter, we will explain in more detail the path followed in this work: We will argue that evaluating only the defect coverage is insufficient,

#### 1.4. STATE-OF-THE-ART

since not all defects have to lead to a failure. In order to obtain a more global vision of the test, this fact must be taken into account, as well as the importance that these failures would have in the event of not being detected. Consequently, we will provide a simulation framework to discard or validate a test strategy and optimize the required computational resources.

### Chapter 2

### The proposed Framework

### 2.1 A complete picture of test quality

Since we are in Zero Defects era [19] the exhaustive fault analysis, perfect by definition, has derived to more complex solutions. The imperfections in the process of Defect-Oriented Test has questioned its quality and an evaluation of it is needed. Generally, this problem has been solved by reporting Defect Coverage but this metric presents some problems.

Defect Coverage is defined as the amount of detected defects divided by the total number of considered defects, Eq. 2.1. Using this definition as the only option to evaluate a Defect-Oriented Test only can lead to conclusive results if the value is close to 1 or 0, allowing the validation or exclusion of the test.

$$DC = \frac{Detected \quad defects}{Simulated \quad defects}$$

(2.1)

$$FE = \frac{Undetected \quad faults}{Simulated \quad faults}$$

(2.2)

For intermediate values of the metric it is necessary more information in order to fully assess the test quality. That is why the fault analysis is included in our test. The classical expression of this metric has practically the same definition as de Defect Coverage. Fault Coverage is the ratio between the detected faults and the total amount faults. The complementary metric, Fault Escape, is defined as one minus the Fault Coverage. It is the amount of undetected faults divided by the total of faults, Eq. 2.2.

These two metrics give a more complete vision of the test quality, but there are cases where these metrics can still exclude some valuable info. That is the case when we have with equal Defect Coverage and Fault Escape. Here, the decision between two test should be done taking into account the importance of the defects that have passed the test. Indeed, a circuit that fails to meet the specification only marginally is undoubtedly better than one with a catastrophic failure. In order to solve this problem we have provided a new FoM that pretends to solve this problem.

#### 2.1.1 Modified Defect Coverage

The classical expression of the Defect Coverage is in Eq. (2.1). This expression does not consider the Relative Likelihood of happening of each defect. An extended proposal is that of [15]. It consists of substituting the numerator and denominator by the sum of the RL weights of each defect, Eq. (2.3).

$$DC^* = \frac{\sum_i^N D_i \cdot RL_i}{\sum_i^N RL_i} \tag{2.3}$$

Where  $D_i$  switches its value between 1 and 0 if the defect *i* is detected or not, RL is the array with all the weights and N the total number of considered defects. This metric has resulted to be useful for the non-exhaustive defect simulation, as it will be studied in chapter 4.

#### 2.1.2 Modified Fault Escape

It has already been discussed that perform an exhaustive fault test is not affordable due to the amount of possible defects in an IC. In addition, fault simulations are presumably much longer to simulate than a defect simulation. For the sake of brevity, we call fault simulation the simulation of a defect to assess its impact on performance. It is thus using a functional test setup. Conversely, we call defect simulation the simulation of the defect in the Defect-Oriented Test setup. In order to lower computational burden, we propose to simulate the performance of only those defects that have not been detected by the test. Indeed, we do not really care if the detected defects produce a fault or not since a defect is always a threat and should be discarded so no interesting information is lost.

But the classical metrics cannot be computed since the denominator would be a biased approximation. To clarify this problem we only have to observe two tests. One of them lets go of a failure and the other a fault and a defect. In the first case we would have a Fault Escape of 100% and in the second a 50%. Essentially, both test are equally bad with regard to fault escape but the metrics are different. For that reason we proposed to reference the metric not to the total number of simulated escaped defects but to the total number of defects, as with the Defect Coverage.

$$FE* = \frac{Undetected \quad faults}{Simulated \quad defects} \tag{2.4}$$

The basic approximation is in Eq. (2.4). It has the same form as the original Defect Coverage, but now the numerator only have the undetected faults. As before, this metric can be reshaped for adding the RL, Eq. (2.5).

$$FE^* = \frac{\sum_i^N F_i \cdot RL_i}{\sum_i^N RL_i} \tag{2.5}$$

Here  $F_i$  is set to 1 if the defect has passed the test and it is a fault, it has a null value in any other case, if it has not passed the test or it is not a fault.

### 2.1.3 Severity

Severity is a metric that pretends to summarize how far are the undetected faults from the specification. The problematic with this metric is that it has to be referenced to the test, and not to the faults, since the exhaustive simulation has not been performed, Eq. (2.6).

$$Severity = \frac{\sqrt{\sum_{i}^{N} F_{i} \cdot RL_{i} \left(FV_{i} - Spec\right)^{2}}}{\sum_{i}^{N} RL_{i}}$$

(2.6)

FV is an array with the performance value measured and Spec the specification value. The expression is justifiable if we understand the objective of it.

- With  $(FV_i Spec)$  we measure the distance to the specification.

- $F_i$  is the same array as before. It values 1 if it correspond to a escaped fault and 0 in any other case.

- The sum of the squares,  $\sum_{i}^{Ne} (...)^2$ , ensure that every fault will increase the metric.

- The root allows to resize the value to units of the specification.

• By dividing by the total of defect likelihood,  $\sum_{i}^{N} RL_{i}$ , we normalize the value for comparison with other tests.

However, this metric is quite unintuitive so it only can be used for test comparison, not for absolute results of how good is the test. We're working on another version of it.

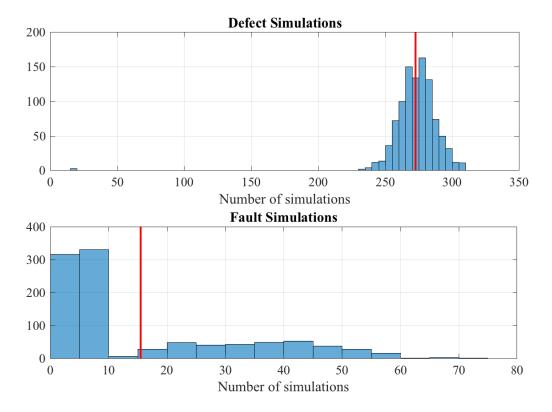

# 2.2 Sequential defect simulation with early stopping

The approach to carry out the simulation using these metrics is a sequential simulation of defects. The idea is setting Defect Coverage and the Fault Escape target and perform simulations till it is possible to ensure that the test reaches or not these values. At first sight this could derive in an exhaustive test, so some considerations must be taken into account.

For the defect selection we will use the "Likelihood-sampling adaptive defect simulation" [2]. This method consists of a random defect selection with the Relative Likelihood as weight. Every time a defect is selected refreshes an array that contain the number of occurrences of each one. On this way, the same defect can be selected more than one time, but the simulation is done only once. Once the simulation is finished, that array is normalized and it contains the likelihood of each defect that has produced the simulation.

Metrics, in turn, are calculated after every simulation. The first problem of not doing an exhaustive test is that metrics confidence is in question. This makes that every metric must be calculated and showed with a level of uncertainty. The process of metrics calculation from subpopulations, what is called estimation, has been widely explored in other research fields and the Confidence Interval calculus is widely extended.

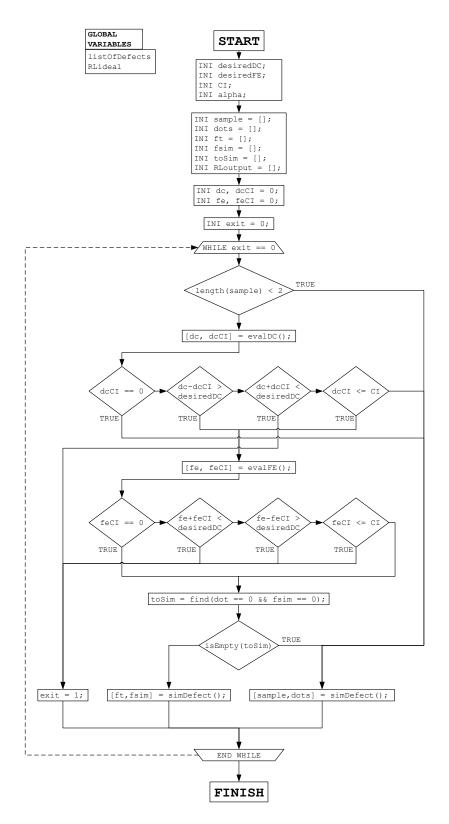

Fig. 2.1 reflects the flow diagram developed. In order to explain it we are going to assume that we have already obtained a list of defects that are saved in the listOfDefects variable. Every defect listed in that array will have an ideal Relative Likelihood associated in the corresponding position of the RLideal variable. These two variables are considered global for allowing any function to access them. Apart from that, the rest of variables initialization has been separated in four different blocks to clarify the meaning of them.

- First block corresponds to the user input variables:

- desiredDC and desiredFE correspond with the desired Defect Coverage and Fault Escape, respectively.

Figure 2.1: Sequential simulation flow diagram.

- CI is the absolute value of the Confidence Interval width. It is used to stop the simulation in the case the early stopping can not be done.

- alpha determine the reliability of the calculated results.

- Second block corresponds to the simulation loop variables. In the arrays are declared the simulation history.

- sample contains the defect index of the selected defects. For every defect simulation, a defect is selected following the likelihoodsampling. If the selected defect index is not in the array it is pushed at the end, if not, this arrays is not updated. So that, the length of the array will correspond with the total number of different defects simulated.

- dots saves the results of the Defect-Oriented Test simulated. For every defect on sample saves a 1 if the defect has been detected and a 0 otherwise. Every time a defect is pushed in sample a 0 is pushed in this array at the same position. On this way, the detection info saved in dots(i) correspond with both the i-th defect simulated and the sample(i) index of the list of defects.

- ft the equivalent to the previous one but for the fault simulation. Maintaining the reference, we push a 0 at the end with every new defect selected. In the case the fault simulation of the sample(i) defect is performed, the ft(i) is updated to 1 if the defect sample(i) is a fault.

- fsim contains the list of performed fault simulations. Like ft, a 0 is pushed with every new defect selected but this array update the fsim(i) value if the fault simulation of the sample(i) is performed, independently of the result. It will be useful to select the non-simulated escapes from the sample, as we will see soon. With this definition, the sum of all the elements of this array will be the number of defects used for the Fault Escape calculation.

- RLoutput contains the number of times a defect has been selected. Intuitively, a 1 is pushed at the end with every new defect and every time the sample(i)-th defect is selected, it increments the i-th position by one.

- The third initialization contains the test evaluation itself. The estimated Defect Coverage and Fault Escape, dc and fe, with its respective Confidence Interval, dcCI and feCI. The last block only contains a variable to stop the loop.

Once the variables are correctly initialized the simulation loop starts and maintain looping until the variable **exit** is not null. For clarity, some variables have been omitted from the functions call but the will appear in the explanation of each of them.

After loop initialization, two different defects are simulated, if this is not done there are none statistics to calculate. simDefect() function, Code 2.1, first perform the likelihood-sampling for defect selection from the listOfDefects variable with the RLideal as weight. The next step is to find out if the defect selected has been already simulated or not. If it has been simulated we update RLoutput. If not, we update all the arrays. The performDOTSimulation() function performs the injection of the defect in the circuit netlist and simulate the Defect-Oriented Test that is being evaluated. The output of the function will be a 1 if the defect is detected and 0 if not and dots is updated accordingly.

```

1 function [sample, dots, RLoutput, ft, fsim] = simDefect(sample, dots,

RLoutput, ft, fsim)

2

3 defect = randsample(1:length(listOfDefects), 1, true, RLideal);

```

```

defect = randsample(1:length(listOfDefects),1,true,RLideal);

3

4

if ismember(defect, sample)

5

RLoutput(find(sample == defect)) =

6

RLoutput(find(sample == defect)) + 1;

7

else

8

\operatorname{sample}(\operatorname{end}+1) = \operatorname{defect};

9

RLoutput (end+1) = 1;

10

dots(end+1) = performDOTSimulation(defect);

11

ft(end+1) = 0;

12

fsim(end+1) = 0;

13

end

14

15

end

16

```

Code 2.1: simDefect() function  $Matlab^{\textcircled{R}}$  code

After two simulations the first estimator can be calculated. The Defect Coverage estimation and its Confidence Interval are obtained from the function evalDC(), Code 2.2. In the code exposed only the estimator calculation has been included. The acquisition of the alpha level of accuracy of the metric will be explained in next section. We will only clarify that the Confidence Interval estimates the error in the measurement done due to the calculation from a subpopulation. From it, we obtain a upper and lower limit. The result returned from the Clcalc() function is the distance to the center of that interval. In this way, we can ensure that the metric is its value plus-minus the CI value with an alpha-level of confidence.

```

1 function [dc,dcCI] = evalDC(dots,RLoutput,alpha)

2

3 RL = RLoutput/sum(RLoutput);

4 dc = sum(dots.*RL)/sum(RL);

5 dcCI = CIcalc(alpha,dots,RL);

7

8 end

```

#### Code 2.2: evalDC() function $Matlab^{\mathbb{R}}$ code

The Confidence Interval will be useful for the early stopping. That is the objective of the four ifs statements in cascade. The first check if the Confidence Interval is valid or not. This could happen if the sample does not have enough diversity. As we will see, this is quite usual for the first few iterations. The second checks if the lower limit is higher than the desired value. If this is the case, we can ensure the test will be accepted so we can start to simulate escapes. Third block checks if the test can be rejected, that is, is the upper limit of the Confidence Interval is lower than the desired value. The last one will stop simulating defects in the case the Confidence Interval is narrow enough.

```

function [fe, feCI] = evalFE(ft, ftsim, dots, RLoutput, alpha)

1

2

RL = RLoutput / sum (RLoutput);

3

simF = find(fsim == 1);

4

\mathbf{5}

fe = sum(ft(simF).*not(dots(simF)).*RL(simF))/sum(RL);

6

7

feCI = Clcalc (ft, ftsim, dots, RLoutput, alpha);

8

9

end

10

```

### Code 2.3: evalFE() function $Matlab^{\mathbb{R}}$ code

If the decision taken is to perform a fault simulation, Fault Escape is estimated first (evalFE(), Code 2.3). With this, we follow the same comparison as before, but with some different exits. The first one is the same, if cannot trust the Confidence Interval we ask for another fault simulation. Otherwise, we check the values. With this three conditionals we finish the loop whether or not we accept the test or if the Confidence Interval is narrow enough.

simFault() function, Code 2.4, performs the fault simulation. It reads the samples in the same order they have been selected until an undetected defect that has not been simulated yet is found. In this way, the same simulation method used for defect selection is virtually repeated for the fault simulation and the metric calculations remains the same.

20

```

function [ft,fsim] = simFault(sample,dots,RLoutput,ft,fsim)

1

\mathbf{2}

noSim = find(fsim == 0);

3

4

for i = 1: length(noSim)

\mathbf{5}

if dots(noSim(1)) = 1

6

fsim(noSim(i)) = 1;

7

else

8

ft = performFTSimulation(sample(noSim(i)));

9

fsim(noSim(i)) = 1;

10

break;

11

end

12

end

13

14

end

15

```

Code 2.4: simFault() function  $Matlab^{(R)}$  code

The fault simulations have an especial consideration, they are only performed if there are escapes that has not been simulated yet. So that, we first look for among the escapes, that is dots==0, the defects that have not been simulated, fsim==0. If the array is empty we perform a defect simulation first to have another try. This loop is done this way do to the fact that we could accept a test that meets Defect Coverage objective but the number of samples is insufficient to ensure that the Fault Escape is low enough.

The gains in computation time comes from two fronts:

- The early stopping criterion, which allows validating or discarding the test as soon as the metrics estimates are confident enough.

- The fact that we simulate for performance only the escapes of the test instead of all the defects. Considering that performance test setups usually require much more longer simulation time than defect oriented ones, this can account for important savings.

### Chapter 3

# Statistical evaluation of test metrics

### 3.1 Likelihood random sampling

In order to solve the problem of the quantity of possible defects to simulate statistical test is performed. Statistics is the science of collecting, organizing, and interpreting experimental data to draw conclusions about unknown populations observed through experiment [5]. This approach can be directly applied test evaluation for reducing simulation effort.

By following the IFA process we obtain the already mentioned Relative Likelihood. As mentioned before, this metric give us information about how likely is a defect to happen relative to the rest. It is rational to think that the mentioned metrics in chapter 2 will be more affected by the defects with high RL than any other, so this defects may be the most important to simulate.

In [2] this fact is discussed. They present the discussion between using Likelihood random sampling or simulating the most likely defects. In essence, the second group argue that since spot defects are not part of any stochastic process, the inference of any defect property can not be done taking into account another defect. Talking about defect coverage, the fact that one defect is detected gives absolutely no clue if another one will be detected or not.

On the other hand, pro-Likelihood Random Sampling group claims that in a complex mixed-signal circuit there can be a majority of defects with low likelihood and fewer defects with large likelihood. The global probability of occurrence of these two populations may be similar. If there could be a reason for which the test coverage may be dependent on likelihood, simulating only the most likely defects would induce a bias. Such a bias is what they obtain in one of the scenarios they use to demonstrate the point. By introducing a strong imbalance in the fault coverage dependent on the likelihood of defect, the simulation of most likely defects produces a very important bias, what it is not surprising since the test was designed to produce that bias. What appears to be more interesting is that the confidence interval of likelihood sampling is almost equal to the confidence interval of the most likely simulation. This means that, even in the hypothesis of independence between likelihood and coverage, there is no significant penalty in terms of computational effort to perform likelihood random sampling instead of simulating only the most significant.

Likelihood random sampling was firstly proposed in [15] but it was refined in [2]. The process of defect selection and simulation can be sum up in the next items.

- Once the Relative Likelihood has been extracted from the circuit netlist, defects are selected randomly using it, what means that a high probable defect will be more likely selected, even more than one time.

- There is substitution in sampling, what is, the same defect can be selected more than one time.

- During the selection, an array, that we have called Output Relative Likelihood, is filled with a start value of 1 for every selected defect.

- If a defect is selected again, it increments its value by one in the Output Relative Likelihood, but it is not simulated again.

- The number of defects in the sample it is not defined by the total number of simulations but for the number of deferent defects selected.

It can be demonstrated that the Output RL array will be the same as the original RL is the number of simulations tends to infinity, but this is not necessary. The Output RL can be used to calculate the defects even though it has not the same values. The effect of the overrated defects is compensated by the overrated value of the less significant ones.

$$dc^* = \frac{\sum_i^n d_i \cdot RLo_i}{\sum_i^n RLo_i} \tag{3.1}$$

$$fe^* = \frac{\sum_i^n f_i \cdot RLo_i}{\sum_i^n RLo_i}$$

(3.2)

Equations (3.1) and (3.2) shows the estimators of the Defect Coverage and Fault Escape with the obtained output Relative Likelihood, *RLo*. The arrays  $d_i$  and  $f_i$  are the same as the originals but with the subpopulations, that is why the sum finish at *n* instead of *N*. With this process a faster convergence of the metrics is reached, what implies a direct reduction on simulation costs, but something more is necessary. By estimating the measurement value with a subpopulation of the defects a Confidence Interval of that result must be given, and this is what we talk in next section.

### **3.2** Estimate of confidence intervals

In general, a ratio is the division of two magnitudes. In the statistical bibliography, specifically in [31], the ratio is defined as the proportional relationship between two means within the same population. What is the same, if we have a population N and two subpopulations of N called Y and X we define the ratio R as

$$R = \frac{Y}{\overline{X}} = \frac{\overline{Y}}{\overline{\overline{X}}}$$

(3.3)

A trivial estimator of this ratio can be the showed in equation (3.4). From now on, we will use uppercase letters when we are talking about a magnitude referring to the whole population and lowercase letters when we are talking about an estimate. On this way, the mean  $\bar{y}$  is the mean of the same magnitude as  $\bar{Y}$  but measured in the subpopulation *n* instead of *N*.

$$r = \frac{y}{x} = \frac{\bar{y}}{\bar{x}} \tag{3.4}$$

The statistical problem comes from determining how much we can rely on the estimation. For that, we first need to determine the sampling method. A widely extended sampling method is the Simple Random Sampling. It consist in the randomly selection of sampling discarding the already selected. On this way, we can determine the Mean Square Error as equation (3.5).

$$MSE(R) = \sigma_{R,1}^{2} = \frac{1 - FPC}{n \cdot \overline{X}^{2}} \frac{\sum_{i}^{N} (Y_{i} - R \cdot X_{i})^{2}}{N - 1}$$

(3.5)

With FPC = n/N, called the Finite Population Correction Ratio. But the problem of evaluating the Confidence Interval (CI) of the ratios comes since, a priori, we do not know the rue value of the population parameters. For that reason, the calculus should be treated carefully. For example, since our metrics can only reach values between 0 and 1 they can be treated as a binomial distribution. In this specific case, the confidence interval can be as easy as (3.6), [32].

$$CI_{binomial} = z_{\alpha/2} \cdot s_{R,binomial} + \frac{1}{2 \cdot n} \tag{3.6}$$

$$s_{R,binomial}^2 = (1 - FPC) \frac{r(1 - r)}{n - 1}$$

(3.7)

The term s is the estimator of  $\sigma$ . Only on this case, the ratio variance can be reduced to (3.7). The term  $\frac{1}{2 \cdot n}$  is the correction for continuity. The problem of this approximation is that it is unreliable for the limits values 0 or 1. So that, it is needed a CI that contemplates that problem, even though generates a bigger interval.

The solution part of considering as correlated numerator and denominator. On this way, the calculus of the confidence interval is reduced to calculate the variances and covariances of both terms and determine the ratio CI with them. For that, it is recommended to obtain the ratio variance from the means variance. This can be done from (3.5), as showed in [31], resulting in equation (3.8)

$$\sigma_{R,2}^2 = \frac{1 - FPC}{n \cdot \overline{X}} \left( \sigma_{\overline{Y}}^2 + R^2 \cdot \sigma_{\overline{X}}^2 - 2 \cdot R \cdot \sigma_{\overline{YX}} \right)$$

(3.8)

$\sigma_{R,2}^2$  is the variance of the ratio in expression of the variances of its terms.  $\sigma_{\overline{Y}}^2$  and  $\sigma_{\overline{X}}^2$ , and the covariance between them,  $\sigma_{\overline{YX}}$ . But this values are unreachable with an exhaustive test, so that an estimator of the variance is used. This results in calculate the variances as follows:

$$s_{\overline{y}}^{2} = \frac{\sum_{i}^{N} (y_{i} - \overline{y})^{2}}{n - 1}$$

(3.9)

$$s_{\overline{x}}^{2} = \frac{\sum_{i}^{N} (x_{i} - \overline{x})^{2}}{n - 1}$$

(3.10)

$$s_{\overline{yx}}^2 = \frac{\sum_i^N \left(y_i - \overline{y}\right) \left(x_i - \overline{x}\right)}{n - 1} \tag{3.11}$$

$$s_r^2 = \frac{1 - FPC}{n \cdot \overline{x}} \left( s_{\overline{y}}^2 + r^2 \cdot s_{\overline{x}}^2 - 2 \cdot r \cdot s_{\overline{yx}} \right)$$

(3.12)

#### 3.2. ESTIMATE OF CONFIDENCE INTERVALS

It is important to differentiate that our intention is not to estimate E(Y|X) but E(Y)/E(X). In fact, if X and Y are normally distributed, the first quantity does not even exist [33]. A widely extended CI calculation is by the Fieller's theorem [34,35], that obtains the limits of the range expressed in (3.13).

$$(\alpha_L, \alpha_U) = \frac{1}{1-g} \left[ r - \frac{g \cdot c_{\overline{yx}}}{s_{\overline{x}}^2} \mp \frac{t_{d,\alpha} \cdot s_r}{\overline{X}} \sqrt{\Gamma} \right]$$

(3.13)

$$\Gamma = s_{\overline{y}}^2 - 2 \cdot r \cdot c_{\overline{yx}} + r^2 \cdot s_{\overline{x}}^2 - g\left(s_{\overline{y}}^2 - \frac{c_{\overline{yx}}^2}{s_{\overline{x}}^2}\right)$$

(3.14)

$$g = \frac{t_{d,\alpha}^2 \cdot s_{\overline{y}}^2}{\overline{X}^2} \tag{3.15}$$

The term  $t_{d,\alpha}$  refers to the  $\alpha$ -level deviate from the Student's t-distribution based on d degrees of freedom, with d = n - 1. The use of the Student's t-distribution approximation instead of the Normal distribution is due to the possibility of not having enough samples. Anyways, the difference from 50 samples or more is insignificant.

In order to use this expression, it is necessary that both means of the ratio follow a bivariate normal distribution. The second condition is that  $\Gamma$ , eq. (3.14), need to be positive so as not to obtain an imaginary value. In addition to that, the parameter g allows to determine the meaning of the range. When g is very close to 1, the confidence interval is infinite and if it is greater than 1, the overall divisor outside the square brackets is negative and the confidence interval is exclusive.

Even though Fieller's theorem is the most extended method we will see it does not work correctly with values close to 0, and the problem of continuity is not solved with it. In order to decide which equation use to perform the analysis we have prepared a virtual environment.

#### **3.2.1** Checking confidence intervals

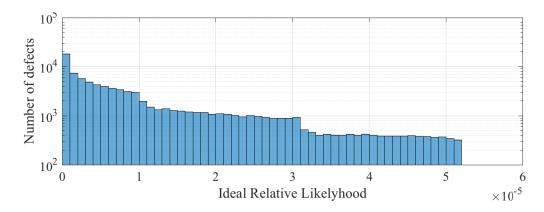

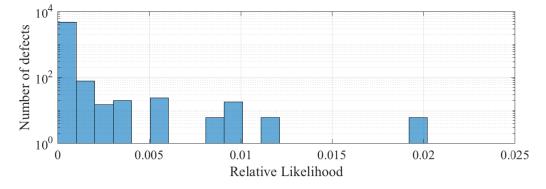

We will perform the analysis of a circuit with 9000 transistors. Each of them with 10 different possible defects. That makes a total of 90000 different simulations. The RL is randomly assigned making more weighted some of them. The histogram of the array through the form showed in Fig. 3.1.

From the full population, we will set a Defect Coverage by randomly selecting defects till the desired value is reached. This definition will work as the exhaustive simulation results. Our aim with this experiment is to obtain the real CI of the Defect Coverage. In order to accomplish this task we will

Figure 3.1: Virtual example, RL histogram

Figure 3.2: CI narrowing with the number of samples,  $dc \approx 0.5$

Figure 3.3: CI narrowing with the number of samples,  $dc\approx 0.1$

perform a virtual sampling 100 times for different amounts of defects. Once this is done, we will have a histogram of the obtained Defect Coverage for each number of defects and we will be capable of setting a empirical Confidence Interval, the measurement error. The theoretical Confidence Interval should follow this results or, at least, not narrowing too fast.

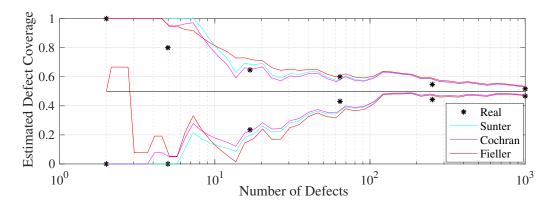

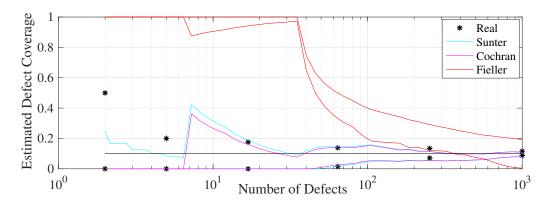

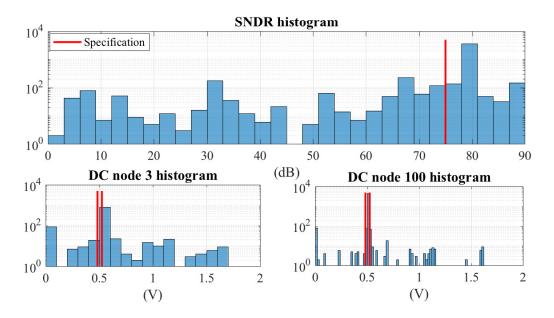

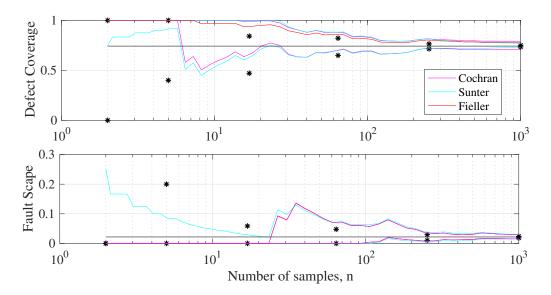

Fig. 3.2 and 3.3 shows the results for a Defect Coverage of 0.5 and 0.1, respectively. The Sunter CI is calculated as Eq. (3.6). Cochran is calculated using the same equation but calculating the typical deviation as a ratio, Eq. (3.8). Finally, the Fieller range is calculated with Eq. (3.13).

In general, Confidence Interval are not reliable for low number of samples, at least 7 are necessary. Besides, all three seem a good approximation when Defect Coverage has an intermediate value since the real value is always inside the theoretical. Regardless, the Fieller's Theorem does not give good results with values close to zero, as expected, so this option is discarded. The difference between Sunter and Cochran depends on the continuity summand. In our case, we are going to use Cochran because the bad behavior with low number of samples is easy to detect, it only requires to compare equality between the two extremes.

### Chapter 4

# Description of the developed tools

#### 4.1 Defect models

It may not be clear the name of fault models when what we want to perform is a defect simulation. This name comes from the digital world where fault models refer to the effect that any defect could have in the circuit, for example, the stuck at 0 or stuck at 1 faults. If we consider this fault we only have to put a net, or part of a net, with a fixed value. Here the fault refers to the bad performance of a gate and the defect could be anything that produce that badfunction, a short with power or ground, for example. So in reality the stuck at 0 and stuck at 1 faults can be seen as a functional fault at gate level.

In the analog field this difference is not as clear. In [14] is given a very good sum up of the types of spot defects we can consider for an IC. These are classified in 11 groups and they involve the mistakes in any mask used during the fabrication process [7]. As mentioned in [15], most of the spot defects produced in a IC can be modeled as open or shorts. Here is the point, we will insert different open or shorts in the circuit, but the defect can be dust, bubbles or any mistake produced during the fabrication.

It is widely accepted modeling spot defects as resistances. This model is close enough in the case of shorts but with opens appears some problems. A big resistor is settled in the place of the open in order to guarantee los currents but the simulator convergence is not limited. In addition, for the transient analysis it could be interesting to add a capacitor in parallel with the resistance. This approach could be applied for the electrical modeling, independently of where it happens.

For an post-layout approximation the resistors would have to substitute

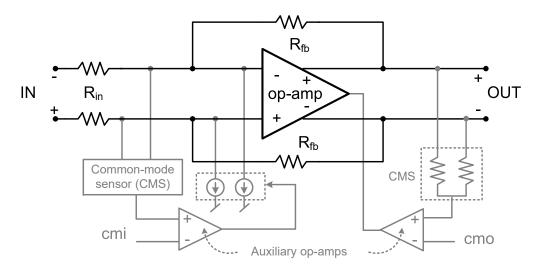

Figure 4.1: 6+1 transistor fault model

the suitable parasite. If it is an open on a net only needs to increase the parasitic resistor value. On the other hand, if it a short between two needs, the parasitic capacitor has to be replaced by a low valued resistor. However, when the injection is done directly on the nominal schematic the defects are usually injected in devices. So that, models are slightly different.

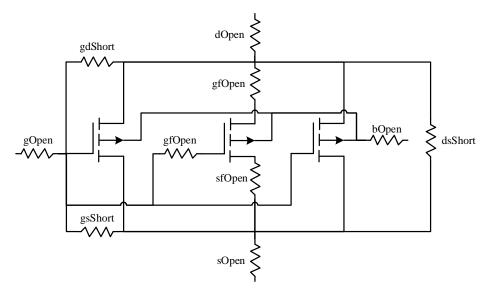

Fig. 4.1 shows the classical 6 resistor fault model. Starting from a nominal case in which the Open resistors have a ideal value of zero whereas the Shorts are set to infinity. In the case a short between any terminal is chosen to simulate the resistor is set to a determined *Rshort* value, that can be fixed or variable depending on the simulation. In the case of the opens we follow the same pattern, but with an *Ropen* parameter. In order to increase accuracy, we have added the baseOpen defect, that could happen in the case the transistor has its own well.

In addition to that, we have considered three more open for the case an only finger fails of the entire transistor. This is a typical example of defect that may affect or not the performance, since it could be considered as a parametric variation of the transistor, and not a complete failure.

The calculation of the Relative Likelihood in this case is done from the device parameters itself. To sum up, the biggest the transistor the most likely to be defective since there are more are where the dust particle can fall. But it is not accurate treating opens as likely as shorts. In fact, opens are more likely than shorts. In our case we will consider five times more. For the fingers open, since only affects to one part of the transistor we have change

Figure 4.2: 6+1 transistor fault model with one-finger open option

the factor by three. Finally, baseOpen defect is the least likely to happen, so its value is divided by half. In the end, the Relative Likelihood array will be the area of the transistor the belong multiplied by the mentioned factors. In order to make the values relative to the rest, the vector is normalized with the sum of all elements.

#### 4.1.1 Convergence error with Open-Gate defect

The problem of modeling the open-gate defect by a large resistor is that the DC analysis converges at the same point with or without input resistance. For that reason some modifications of the model should be done.

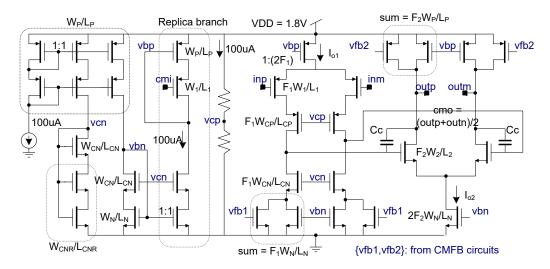

There are several example of Floating Gate Transistor (FGT) models [16,17,36] but due to how the DC analysis with Spectre works, some of them are not implementable. Any model for which the gate voltage depends on resistor ratios will generate wrong results.

For example, in [16], Fig. 4.3a, voltage is induced by two so-called leakage resistors between the gate and both drain and source. Another resistor, with the same value, is located at the gate. Every resistor has a capacitor in parallel which value is the total parasitic capacitance between the nodes they are located. The ones connected with the drain and source are calculated by the transistor parameters and the other considers scaling effect caused by the charge sharing in the polysilicon.

This could work if we had enough information for determining the resistor values. The gate resistor can be set at the *Ropen* value, but the other two

Figure 4.3: FGT model examples

not, since is reasonable to think that these values depends on the transistor itself.

Looking at [36], the gate voltage is decided by a model of the tunneling and injection current, injected with voltage-controlled current sources. The initial value, for the DC analysis, is settled by a voltage-controlled voltage source with a high output resistance, as high as possible. The sources have a gain dependent on the transistor parasitic capacitors. The calculated voltage is settled by a buffer at the gate of the transistor in Fig. 4.3b.

Recently, [17] has shown that an open-gate transistor can be modeled in DC by a transistor having the same electrical properties but operating but in the sub-threshold region. That sub-threshold region is forced by a voltage-controlled voltage source which gain depends on, again, parasitic capacitors. In that paper, the ratio between  $V_{GS}$  and  $V_{DS}$  is inside the margin showed in Eq. (4.1). Even though this premise is debatable, we will use this model as reference for the DC analysis.

$$\frac{C_{gdo}}{WLC_{ox}} \le \frac{V_{GS}}{V_{DS}} \le \frac{3C_{gdo}}{2WLC_{ox}} \tag{4.1}$$

On the other hand, for the transient analysis the model should be different. The gate voltage in the transient analysis is set by the parasitic capacitors in its leakage current and, reading the BSIM3v3 documentation [37], the parasitic capacitors are more than modeled for the transient analysis. So that, we will consider as correct modeling the gate open by a large resistor for transient defect simulations. This model should be conservative in the sense that it will account for dynamic effects, the gate voltage is actually low-pass filtered, but will not disrupt the operating point.

#### 4.2 Injection

The process of injecting defects starts from the netlist obtained from Cadence Virtuoso<sup>®</sup>. But to understand why and how it is needed to explain the netlist itself.

```

simulator lang=spectre

1

global 0

2

parameters ...

3

4

include "..."

\mathbf{5}

6

// COMMENT

7

subckt NAME LIST_OF_TERMINALS

8

paramters ...

9

INSTANCES

10

ends NAME

11

12

NETLIST_TOP_LEVEL

13

14

SIM_CONFIGURATION

15

```

At the beginning of the document we need to add the language used in the document. For Spectre<sup>®</sup> is a must. It only gives the possibility of putting comments (// ...) before of it. The rest of the structure it is more a good practice to avoid mistakes than a mandatory structure.

The label *global* determine the global nets. In the case there are not global nets declared it appears a 0, that will be used as voltage reference during the simulation. Second line correspond to the *parameters*. This can be written any time you want to initialize a new variable and can contain more than parameter in the same line. The only condition is that before using a variable it must be previously declared with this label. It is important to point out that every variable declared in the document will be considered as global, what is to say, a modification of the parameter will affect all the netlist, even if the edition is done after the use of the variable.

Next part are the *include* "..." sentence. This command only add the content of the file between commas to the netlist. It does not matter the format of the document, even no format works, because it will read it as a text file. The only condition is that the text file has a Spectre<sup>®</sup> code structure, that is, starting with *simulator lang=spectre* and having no syntax errors. However, there are some conventions in the text file format for as an habit of order.

• Files that finish with ".mdl" correspond to models, transistors, technology capacitors, resistors or inductances, etc... Some layout extractors,

Figure 4.4: Flattening process

for example, use this format to add the parasites.

- Files finishing in ".inc" normally contain parameters. Model variables, Monte-Carlo variables, etc...

- ".lib" files correspond to the libraries. Here sections are defined. Starting from the nominal, and finishing with corners and Monte-Carlo.

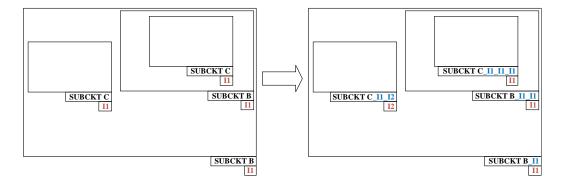

After the models we have the subcircuits declaration. This is the part where we need to work more. By default, subcircuits are only declared one time, independently of the number of times it has been called. An edition of one parameter inside the subcircuit will affect to all its calls. That is why we need to flatten the netlist before working with it.

The netlist top level is where the testbench is defined. In there, the upper level of the circuit is called and the necessary environment to test the circuit is set. The only modification that is expected to be done here is editing the name of the upper subcircuit.

Finally, it is the simulation configuration. Tolerances, analysis, saved voltages, saved currents and temperature is set among these lines. We will see later that we can use the same analysis that is declared here using SpectreMDL<sup>®</sup> in order to ensure the same result we obtained with ADE L.

The basic process of flattening is showed in Fig. 4.4. With an input netlist, the program starts by reading all the declared sub-circuits at the beginning of the document. Afterwards, it reads recursively the document to save the dependencies of that sub-circuits and extract a tree with every sub-circuit instance. The name of the sub-circuit is edited depending on how deep is the sub-circuit instanced. For example, if the call is made at the first level it will only have its own name with the instance string immediately afterwards. If it is a second, third and so on level, the complete list of instances need to reach

#### 4.3. SIMULATION

the sub-circuit is written at the end of the name. On this way, we achieve a netlist with non-repeated instances.

That is the only way to guarantee that there will not be double sub-circuit declaration. Of course, it is more efficient to only flatten the specific sub-circuit we are going to edit, but we have made tests and for Spectre<sup>®</sup> it is transparent or, at least, the simulation time is much more higher. The good point of doing this way is that the measurements done for the input netlist are perfectly compatible with the output, since the measurements depends on the ID and net name inside the sub-circuit, not on its name.

At the end of that process, the netlist is read again in order to obtain the necessary parameters to elaborate a list of Relative Likelihood. In order to calculate the area of the transistor we need the width, height and multiplicity of it but, for the sake of versatility, this requires a more complex process. First of all, the global parameters are read. It is common that the sizes are between this list. Then, we start by reading sub-circuits in order, tanking into account that more parameters would be declared locally. Once a potentially defective device is reached, the three model parameters are extracted and the parameters declared on them are substituted by the real value. At this point, the code is capable of substituting any dependency of parameters, so we have not had to set any requirements to the designer.

Once the netlist is flattened, we are sure that the defect we inject in the netlist will only appear at the block we want to, and not any other. On this part only rest to decide how the defect is gonna be inserted.

On our case, we have edited the transistor models in such a way it only requires add one entry parameter to the transistor call in the netlist. All the transistors models have been replaced by our custom models, keeping functionality with Cadence Virtuoso<sup>®</sup> simulation environment. By default, the models does not have the defect parameter in the netlist, so that Spectre<sup>®</sup> will use its default value, which correspond with the nominal behavior. Once a defect is selected, we follow the root of the defective device until we reach it. The defect injection only requires to add the defective parameter at the end of the call line.

#### 4.3 Simulation

Simulation part has been prepared to be performed in Matlab<sup>®</sup>. A set of functions have been written in order to perform all the IFA process. The functions are hybrid codified between Matlab<sup>®</sup> code and PERL<sup>®</sup>. The use of the last one has resulted to be really useful because of the regular expressions. With it use, text edition, the netlist, becomes much more easy to perform.

During the flattening the data for the RL calculation is extracted, that is, width, length, multiplicity and number of fingers. Furthermore, some extra information is prepared to be read, as the complete route from the top to the transistor, the name of the original sub-circuit where it was placed and the list of possible defects for each transistor.

Relative Likelihood can be calculated after the flattening, using Matlab<sup>(B)</sup>, depending on the case. A first approximation is the mentioned in the first section. We calculate the area and multiply it by a constant depending on the defect, that is, 5 for opens, 3 for finger opens, 0.5 for the base open and 1 for shorts. This will make a more realistic approach to Relative Likelihood once the array is normalized by the sum of all the values.

Defect selection is done attending the the obtained Relative Likelihood. The highest it is the most probable to be selected, and the defect is not discarded once it is selected in order to accomplish the Likelihood-sampling explained before. In addition, the code is capable of discriminating in the defect selection by sub-circuit. That is, we can simulate the same defect in different test-benches or even in different circuits. Once the defect is selected, the injection and simulation process has been reduced to fill the entry data of a function. That function perform the simulation using SpectreMDL<sup>®</sup>. The software use Spectre in background to simulate netlist.

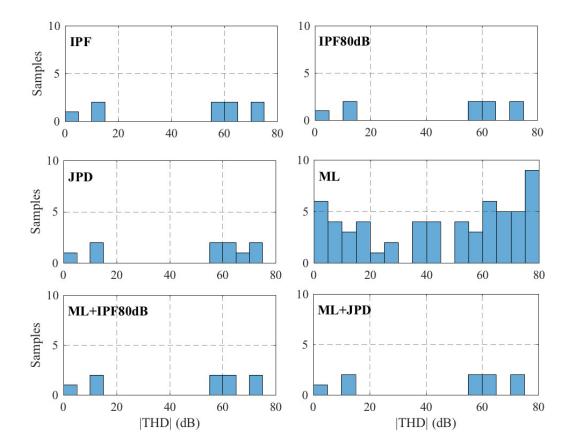

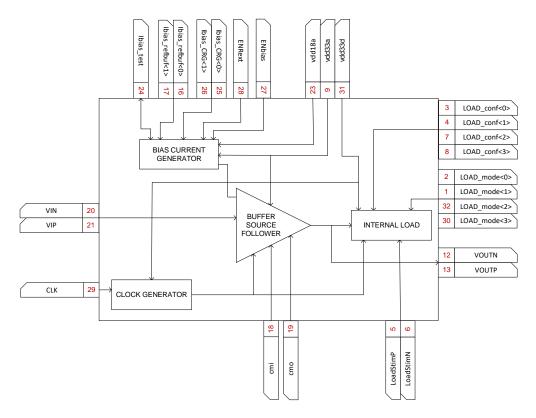

This software, apart from needing a valid initialization of Cadence in the same environment, requires an extra file that defines the models. The structure of this files is defined in the documentation [38] so that we will only mention some functions.