# A Spatial Contrast Retina With On-Chip Calibration for Neuromorphic Spike-Based AER Vision Systems

Jesús Costas-Santos, Teresa Serrano-Gotarredona, Rafael Serrano-Gotarredona, and Bernabé Linares-Barranco

Abstract—We present a  $32 \times 32$  pixels contrast retina microchip that provides its output as an address event representation (AER) stream. Spatial contrast is computed as the ratio between pixel photocurrent and a local average between neighboring pixels obtained with a diffuser network. This current-based computation produces an important amount of mismatch between neighboring pixels, because the currents can be as low as a few pico-amperes. Consequently, a compact calibration circuitry has been included to trimm each pixel. Measurements show a reduction in mismatch standard deviation from 57% to 6.6% (indoor light). The paper describes the design of the pixel with its spatial contrast computation and calibration sections. About one third of pixel area is used for a 5-bit calibration circuit. Area of pixel is  $58~\mu\mathrm{m} \times 56~\mu\mathrm{m}$ , while its current consumption is about 20 nA at 1-kHz event rate. Extensive experimental results are provided for a prototype fabricated in a standard 0.35- $\mu$ m CMOS process.

Index Terms—Address-event representation (AER), analog circuits, artifical retina, calibration, contrast computation, current-mode circuits, imagers, low-power circuits and systems, mismatch, neuromorphic circuits, sensory systems, trimming, vision systems, weak inversion circuits.

# I. Introduction

RADITIONAL CMOS imagers operate under a frame-based philosophy. That is, the image information (intensity, contrast,...) of each pixel is sequentially scanned out with a constant periodicity. After a complete period, the whole image has been read. For consumer video systems, the whole image is usually scanned out in a 20–30-ms period. This restriction becomes a problem when image resolution increases, as the time allocated to read each pixel decreases. The problem of this scanning approach is that the communication bandwidth is equally allocated for each pixel regardless of its relevance.

Manuscript received June 14, 2006; revised October 17, 2006, and January 8, 2007. This work was supported by Spanish Research Grants TIC2003-08164-C03-01 (SAMANTA), TEC2006-11730-C03-01 (SAMANTA-II), and EU grant IST-2001-34124 (CAVIAR). JCS was supported by the I3P program of the Spanish Research Council. RSG was supported by a national grant from the Spanish Ministry of Education and Science. This paper was recommended by Associate Editor A. van Schaik.

- J. Costas-Santos is with the Instituto de Microelectrónica de Sevilla (IMSE), National Microelectronics Center (CNM), Spanish Research Council (CSIC) of Spain, 41012 Sevilla, Spain, and also with Spanish Ministry of Education and Science, Sevilla, Spain.

- T. Serrano-Gotarredona and B. Linares-Baranco are with the Instituto de Microelectrónica de Sevilla (IMSE), National Microelectronics Center (CNM), Spanish Research Council (CSIC) of Spain, 41012 Sevilla, Spain (e-mail: bernabe@imse.cnm.es).

- R. Serrano-Gotarredona is with the Instituto de Microelectrónica de Sevilla (IMSE), National Microelectronics Center (CNM), Spanish Research Council (CSIC) of Spain, 41012 Sevilla, Spain , and also with NXP (Philipps Semiconductors), Graz A-1801, Austria.

Digital Object Identifier 10.1109/TCSI.2007.900179

Thus, communication bandwidth (and power) is wasted on nonrelevant or little relevant pixels.

The retina presented in this paper follows an address-eventrepresentation (AER) communication strategy. AER was first introduced in [1]-[5] as a communication strategy for neuromorphic chips, where a large population of neurons inside a chip have to transmit their state to another population of neurons located in another chip. A common output digital bus is multiplexed and shared by all the chip neurons. Each neuron is coded with a particular address. When a particular neuron accesses the output bus, it identifies itself in the bus by writing its address on the bus. There are many ways to code information (like intensity, contrast, motion, or any feature) into a sequence of spiking events [6]. The most widely used so far, specially for hardware systems, is the so-called *rate-coding* scheme. In this scheme the density of spikes per unit time produced by a pixel is proportional to the information to be transmitted (intensity, contrast, . . .). The spatial contrast retina described in this paper uses this rate coding principle to transform the continuous time spatial contrast information computed at each pixel into a sequence of spikes. Consequently, the activation level (contrast) of each neuron is coded as the time interval between two consecutive appearances of that neuron address on the output AER bus. This way, a relevant pixel uses more communication bandwidth than a less relevant one.

In traditional integration-based CMOS imagers, a photo generated current is integrated on a capacitor during a fixed integration time. After that time, the capacitor voltage is read out and the pixel capacitor is reset to its initial value. In rate-coded AER-based imagers, the current representing the image information (intensity, contrast, etc.) is integrated on a capacitor not during a fixed time but until a certain voltage reference is reached (variable integration time). Thus, the image information is coded as the time needed to charge the capacitor up to the threshold voltage level. When the threshold voltage is reached, an output address event or "spike" is sent out for that pixel, and the pixel capacitor is reset to its initial value. That way, the image information is not coded using the pixel voltage read (as for traditional imagers) but using the time between consecutive spikes of each particular pixel.

This AER approach has the advantage that the output bandwidth is assigned to each pixel according to its demand of information transmission. That way, nonactive pixels do not demand transmission bandwidth, thus, saving bandwidth and power. Furthermore, after a change of scene, the more active pixels will spike first, so that the more relevant information is transmitted first. It has been demonstrated that for this scheme, object recognition is possible when only a small portion of

events have been transmitted, both for a software system [7] and a hardware one [8], [9].

Since its introduction in 1991 [1]-[5] AER has been used by a wide community of neuromorphic hardware engineers. Unarbitrated event read-out has been used [10], [11], and more elaborate and efficient arbitrated versions have also been proposed, based on winner-takes-all [12], or the use of arbiter trees [13], which have evolved to row parallel [14] and burst-mode word-serial [15]-[17] read-out schemes. AER has been used fundamentally in image sensors, for simple light intensity to frequency transformations [18], time-to-first-spike codings [8], [9], [19], [20], foveated sensors [21], [22], and more elaborate transient detectors [23]-[25] and motion sensing and computation systems [26]-[30]. But AER has also been used for auditory systems [3], [31]-[33], competition and winner-takes-all networks [34]–[36], and even for systems distributed over wireless networks [37]. A very interesting and emerging AER research line is its exploitation for complex processing of sensory information, in a way similar to biological brain cortex [38]–[48].

Concentrating on spatial contrast computation AER retinae, there have been several prototypes published in the literature. The original concept proposed by Mahowald and Mead [49] was based on a diffuser grid for computing a local average with respect which compute spatial contrast. Boahen and Andreou developed further this concept using more elaborate biological models [50], using two coupled diffuser grids. At CSEM [8], [9] a very interesting work has been reported recently on spatial contrast (vector) computation retinae (among other functionalities). However, spatial contrast computation is based on nearest neighbor pixels only. It is not a fully AER device, but rather a mixture between event and frame based vision sensor. There is a frame time, but within each frame, pixel information is sent out as ordered event representation. Recently, Zaghloul and Boahen have reported an AER retina which performs spatial and temporal filtering that adapts to illumination and spatiotemporal contrast [51], [52].

The main problem limiting the performance of CMOS spatial contrast retinae is the time-independent fixed pattern noise (FPN) or mismatch due to random variations of the electrical parameters of CMOS transistors. In traditional CMOS imagers (where there is no contrast computation), this FPN is mainly due to random variations in the threshold voltages of the read out transistors that cause random variations in the output voltage read [53]. Some compensation mechanisms have been proposed in the literature for the correction of the output voltage [53]–[56]. AER-based spatial contrast retinae share this FPN problem, and is the main cause limiting its performance [9], [52]. In this paper, we propose a calibration mechanism, adapted from earlier work [46], [57], to compensate for these random variations.

Some retinae have been reported in the literature which have succeeded in providing low mismatch performance, without using trimming/calibration. For example, Ruedi [8] minimizes mismatch by comparing large voltage integrations of uncopied photocurrents between nearest neighbor pixels. Culurciello's retina [18] operates similarly, although it codes directly light intensity. In the case of Lichtsteiner [24], [25] mismatch is

cleverly minimized by accurately amplifying changes to a large voltage before quantizing. However, in all these three examples, where mismatch is reduced by a smart design, none of the retinae computes spatial contrast over a larger-than-one-pixel neighborhood. Surprisingly, such retinae were one of the first ones to be conceived and reported [63], but seem to present an inherent difficulty for reduced mismatch. In the present paper we provide a viable solution.

The visual information transmitted in the implementation presented here is the local spatial contrast. This contrast contains the most relevant information for object recognition, because the relevant information of an object is in the difference of luminance between its different regions and surroundings. It is known that a spatial contrast extraction operation is done in the human retina. This optimizes information transmission through the optic nerve between the retina and the visual cortex area [58], [59]. This contrast can be safely coded with a dynamic range of 4-5 bits (around 20-25 levels), while image intensity is usually transmitted with 8 bits (256 levels) [53]–[55] in present day image and video consumer electronics. Consequently, for artificial vision systems, it is much more efficient to transmit directly spatial contrast information rather than intensity. This is what the brain does [59] and many artificial vision algorithms [60].

The paper is structured as follows. The contrast extraction operation is explained in Section II. The implemented calibration mechanism is contained in Section III. Experimental results are provided in Section IV. Section V describes an experimental setup to reduce AER activity while maintaining the contrast information. Finally, Section VI concludes the paper.

## II. SPATIAL CONTRAST EXTRACTION

Let us call  $I_{\rm photo}(x,y)$  the local photocurrent sensed by the detector at position (x,y), which is proportional to the absolute light intensity incident at that spot at any time. Let us call  $I_{\rm avg}(x,y)$  the representation of the local average of the photocurrent over a certain region centered at position (x,y). We will define a measurement of the local image contrast as [58]

$$I_{\text{cont}}(x,y) = I_{\text{ref}} \frac{I_{\text{avg}}(x,y)}{I_{\text{photo}}(x,y)}$$

(1)

where  $I_{\rm ref}$  is a global reference current level common for all the retina pixels. The contrast is defined as the ratio between the background average intensity and the local intensity value. The inverse of this relation is used by physiologists to fit responses of the retina cones [59]. In other more mathematical models for image processing, contrast is expressed using subtractions. For example, Michelson contrast is defined as

$$I_{\text{cont}}(x,y) = I_{\text{ref}} \frac{I_{\text{photo}}(x,y) - I_{\text{avg}}(x,y)}{I_{\text{photo}}(x,y) + I_{\text{avg}}(x,y)}$$

(2)

$^{1}\mathrm{The}$  inverse can also be defined, equivalently. For example, consider a step in light  $I_{\mathrm{left}} \to I_{\mathrm{right}}$ . If we define the average as the geometric mean  $I_{\mathrm{avg}} = \sqrt{I_{\mathrm{left}}I_{\mathrm{right}}}$ , then (1) or its inverse would provide symmetric contrast outputs. However, in our circuit implementation  $I_{\mathrm{avg}}$  approximates more an arithmetic average. Consequently, (1) and its inverse will not be perfectly symmetric, although the behavior is similar. We chose to use (1) because this way the output tends to be larger.

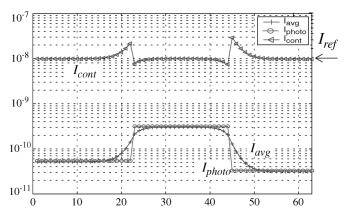

Fig. 1. Electrical circuit simulation of contrast computation in a region with two contrast edges: a step in light intensity of a factor 5 and another step of factor 10. Vertical axis represents current (circles are photocurrents, crosses are computed local average currents, triangles are output contrast currents which vary around global bias  $I_{\rm ref}$ ). Horizontal axis represents pixel position.

or Weber contrast as

$$I_{\text{cont}}(x,y) = I_{\text{ref}} \frac{I_{\text{photo}}(x,y) - I_{\text{avg}}(x,y)}{I_{\text{avg}}(x,y)}.$$

(3)

For these models, zero contrast results in zero output current, and the output current includes a sign depending on whether  $I_{\rm photo}$  is larger or smaller than the local average  $I_{\rm avg}$ . In the retina described in this paper and others reported previously in the literature [58], the contrast follows the computation of (1) or its inverse. This will simplify our calibration circuitry, as will be explained later in Section III. Under these circumstances, the output contrast current will have a dc level equal to  $I_{\rm ref}$  for zero contrast, and it will be always positive. At the end of the paper, in Section V, we will show an AER-based post-processing setup to provide a signed contrast output that corresponds better to the definition in (3).

For the contrast definition of (1), consider first a region of uniform illumination. Since all the neighborhood pixels are evenly illuminated, the average illumination equals the local illumination value,  $I_{\text{avg}}(x,y) = I_{\text{photo}}(x,y)$ . Thus, all the pixels in that region exhibit the same contrast measurement  $I_{\text{cont}}(x,y) =$  $I_{

m ref}$ . Now consider a region where a contrast exists. The local current average  $I_{\text{avg}}(x,y)$  near the contrast edge will differ from the locally sensed current  $I_{\text{photo}}(x,y)$ . Thus, the output of the contrast measurement  $I_{\text{cont}}(x,y)$  will depart form the reference level  $I_{\text{ref}}$ . Output  $I_{\text{cont}}(x,y)$  will be higher than  $I_{\text{ref}}$  at one side of the edge, whereas  $I_{cont}(x,y)$  will be lower than  $I_{ref}$  at the other side of the edge. Fig. 1 shows circuit simulation results of the contrast computation in a one dimensional region of 64 pixels where two contrast edges exist. The trace marked with circles plots the distribution of photoreceptor input currents. The smoother curve marked with plus signs is the computed local average. The upper curve marked with triangles is the computed contrast according to (1). The output of the flat illuminated regions is a constant current  $I_{ref}$ , whereas the output current departs from that level in the neighborhood of the contrast edges.

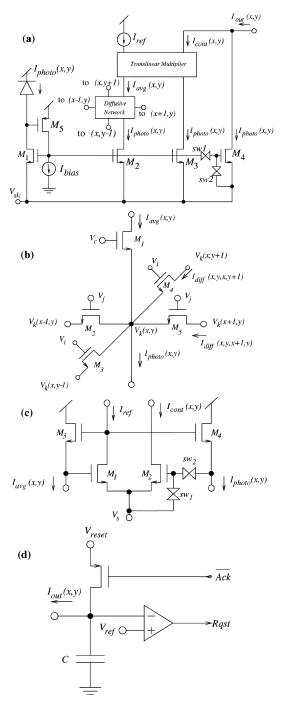

Fig. 2(a) depicts the schematic of the pixel circuitry doing the contrast computation. The photodiode is a p<sup>+</sup>diffusion n-well diode with its well connected to the positive supply. The

Fig. 2. (a) Schematic of the pixel circuitry for contrast computation. (b) Schematic of the diffuser network. (c) Schematic of the translinear circuit. (d) Simplified schematic of pixel output.

photocurrent  $I_{\rm photo}$  is replicated 3 times through an nMOS-type sub-pico-ampere current mirror formed by transistors  $M_1-M_5$  [61], [62]. This current mirror is able to reliably replicate input currents below the pico-ampere range. Three (mismatched) replicas of current  $I_{\rm photo}$  are delivered through the three output transistors  $M_2-M_4$ .

The third output branch (the  $M_4$  branch) is disabled during the normal computation of the contrast. During the normal contrast operation mode of the retina, switch sw1 is open and switch sw2 is closed, so that no current flows through transistor  $M_4$ . The retina can also be operated in a mode where no contrast

extraction is performed. In that mode, sw1 is closed and sw2 is open, so that a replica of the photocurrent  $I_{\rm photo}$  is delivered through transistor  $M_4$ . As we will see below, in that noncontrast extraction mode the output of the translinear multiplier block (see Fig. 2) is cut off, so that the output of the pixel  $I_{\rm out}$  is only the copy of the photocurrent delivered by  $M_4$ .

The replica of  $I_{\rm photo}$  delivered by transistor  $M_2$  flows into a diffuser network whose schematic is shown in Fig. 2(b) [63]–[67]. The transistors in the diffuser network operate in the subthreshold region. Each diffuser cell receives an input current  $I_{\rm photo}(x,y)$  and produces as output a current  $I_{\rm avg}(x,y)$ . The operation of the diffuser network has been described in terms of "pseudo-conductances" [65]. The current diffused through each "pseudo-conductance" transistor  $[M_2-M_5]$  in Fig. 2(b)] verifies a nonlinear exponential relation in the node voltages, but a linear relation between the currents (as long as devices operate in subthreshold). As a consequence, the linear range of operation of the diffuser network extends to several orders of magnitude in the current domain. The diffuser network implements the discrete approximation of the following current diffusion equation in an exact manner [67]:

$$\begin{split} I_{\rm photo}(x,y) &= I_{\rm avg}(x,y) - \lambda_x \frac{\partial^2}{\partial x^2} I_{\rm avg}(x,y) \\ &- \lambda_y \frac{\partial^2}{\partial y^2} I_{\rm avg}(x,y). \end{split} \tag{4}$$

Parameter  $\lambda_x$  is a tunable "horizontal diffusion length" given by  $\lambda_x = \exp((\kappa(V_j-V_c))/U_T)$ , which can be tuned through voltage difference  $V_j-V_c$ . Parameter  $\lambda_y = \exp((\kappa(V_i-V_c))/U_T)$  is a tunable "vertical diffusion length" which can be controlled independently through voltage difference  $V_i-V_c$ .

For a step type input image  $(I_{\text{photo}}(x,y) = I_{\text{left}} \text{ for } x < 0,$  and  $I_{\text{photo}}(x,y) = I_{\text{right}} \text{ for } x > 0)$  the solution of (4) yields

$$x > 0: \quad I_{\text{avg}}(x, y) = I_{\text{right}} - \frac{I_{\text{right}} - I_{\text{left}}}{2} e^{-\frac{x}{\sqrt{\lambda}}}$$

$$x < 0: \quad I_{\text{avg}}(x, y) = I_{\text{left}} + \frac{I_{\text{right}} - I_{\text{left}}}{2} e^{\frac{x}{\sqrt{\lambda}}}. \tag{5}$$

Parameter  $\lambda$  defines the diffusion length. Large values of  $\lambda$   $(V_{i/j} \gg V_c)$  imply diffusion length is large, and the local average will be computed for a large neighborhood. For small values of  $\lambda$   $(V_{i/j} \ll V_c)$ , diffusion length is small, and the local average will be computed for a small neighborhood.

Instead of computing the solution to the continuous time equation approximation of (4), one can compute directly the discrete solution to the finite difference equation, using the Z-transform. The solution would be given by

$$x > 0: \quad I_{\text{avg}}(x, y) = I_{\text{right}} - \frac{I_{\text{right}} - I_{\text{left}}}{2} \frac{1}{a^x}$$

$$x < 0: \quad I_{\text{avg}}(x, y) = I_{\text{left}} + \frac{I_{\text{right}} - I_{\text{left}}}{2} a^x$$

(6)

where  $a=1+1/(2\lambda)+\lambda^{-1}\sqrt{\lambda+1/4}$ , which is always greater than "1" because  $\lambda>0$ . For large values of  $\lambda$  ( $V_{i/j}\gg V_c$ ), a will be slightly larger than "1" but close to "1," which according to (6) will produce long diffusion lengths. For small values of

$\lambda$   $(V_{i/j} \ll V_c)$ , a will be much greater than "1," which results in small diffusion lengths. According to our circuit simulations, the diffuser circuit of Fig. 2(b) can provide a spatial range of over 30 pixels. However, in practice, we found this range limited to about 10 pixels. Discrepancies between (5) and (6) are noticeable only for x < 2 and short diffusion lengths (less or equal than 2 pixels). Consequently, in practice, the continuous and discrete solutions are equivalent.

As depicted in Fig. 2(a), the average current  $I_{\text{avg}}(x,y)$  is fed to a translinear circuit. Fig. 2(c) shows the schematics of the translinear circuit. The translinear circuit also receives a copy of the locally photo generated current  $I_{\rm photo}(x,y)$  and delivers an output current  $I_{\text{cont}}(x,y)$ . Transistors  $M_1 - M_4$  in Fig. 2(c) form the translinear loop, so that their currents verify the relation defined by (1) for contrast computation [66]. As explained previously, switches sw1 and sw2 in Fig. 2(c) have been added to allow the pixel to have two operation modes. During the contrast extraction mode switches sw2 [in Fig. 2(a) and (c)] are closed and switches sw1 [in Fig. 2(a) and (c)] are open, so that the output of the pixel is the  $I_{cont}(x,y)$  current delivered by the translinear multiplier. During the photodiode mode switches sw1 [in Fig. 2(a) and (c)] are closed and switches sw2 [in Fig. 2(a) and (c)] are open,<sup>2</sup> so that the output of the pixel is directly a copy of the locally photo generated current  $I_{\text{photo}}(x,y)$ .

In order to be able to stack the translinear circuit of Fig. 2(c), the diffuser network of Fig. 2(b), and photocurrent mirroring transistors  $M_2$  and  $M_3$ , voltage  $V_s$  in Fig. 2(c) has to be tied to a higher voltage than ground. The optimum value for  $V_s$  depends on the biases used for  $V_i$ ,  $V_j$ , and  $V_c$  in Fig. 2(b). This stacking arrangement allows to reduce the number of current mirrors, and therefore, mismatch.

The pixel output current  $I_{\mathrm{out}}(x,y)$  is integrated on a capacitor C as shown in Fig. 2(d), which shows a simplified schematic of the pixel integrate and fire block. Initially, the pixel capacitor is reset to a high voltage level  $V_{\mathrm{reset}}$ . The pixel output current  $I_{\mathrm{out}}(x,y)$  integrated on the capacitor decreases its voltage until a certain voltage level  $V_{\mathrm{ref}}$  is reached. When the capacitor voltage goes below that level, an event is sent to the periphery by activating the pixel request signal Rqst. Upon reception of the corresponding acknowledge from the periphery ( $\overline{\mathrm{Ack}}$  signal gets active low) the capacitor is reset to the initial level  $V_{\mathrm{ref}}$ . Assume that the delay caused by the periphery (in the order of nanoseconds) is negligible compared to the pixel operation period (in the order of micro or milli seconds), then the frequency of the events generated by a given pixel is

$$f(x,y) = \frac{I_{\text{out}}(x,y)}{C(V_{\text{reset}} - V_{\text{ref}})}$$

(7)

which is directly proportional to the pixel output current.

$^2\mathrm{Note}$  that for proper sub-pico-ampere operation [61], [62] switches sw1 in Fig. 2(c) and sw2 in Fig. 2(a) should connect the respective gates to ground instead of to the transistor sources. However, this is not necessary in this particular case and we can make a more compact layout by connecting to the sources. In Fig. 2(a) when transistor  $M_4$  is cut off, the output current  $I_{\mathrm{out}}$  is usually several hundreds of nano-amperes. And in Fig. 2(c), since voltage  $V_s$  is far from ground, the off current for transistor  $M_2$  is several femto-amperes for this particular transistor size and technology.

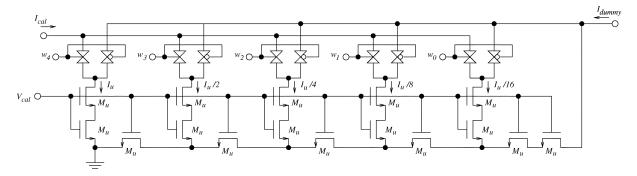

Fig. 3. Compact calibration mini-DACs included in each pixel.

#### III. CALIBRATION

In this AER-based retina the fixed pattern noise appears as a random variation of the pixels output frequencies under uniform illumination conditions. Several sources of fixed pattern noise can be discerned in the present design. One source is the random offset voltage of the pixel output comparator in the integrate and fire circuit. The second source is the mismatch due to the variations of the integrating capacitors. Another source of mismatch is the one generated by the sub-pico-ampere current mirror that reflects the photo generated current. The current mismatch of this reflection is going to be of the order  $\sigma(\Delta I/I) \approx 20\%$ , as this current mirror is designed with  $1 \mu m/1 \mu m$  nMOS transistors operating with extremely low currents [68]. The diffuser network and the translinear multiplier are also designed with reduced area transistors operating with low currents. The current domain operations/replications are the dominant mismatch sources. Experimental results of the retina operating under uniform illumination in the contrast extraction operation mode when no calibration technique is applied show that the precision is well below one bit. The measured output frequency spread  $f_{\text{max}}/f_{\text{min}}$  is about 25. Thus, system calibration is essential for any application.

A calibration technique is designed that equalizes all the pixel frequencies under flat illumination conditions. Rewriting (7), we can express a pixel output frequency in the contrast extraction mode as

$$f(x,y) = \frac{I_{\text{ref}}}{C(V_{\text{reset}} - V_{\text{ref}})} \frac{I_{\text{avg}}(x,y)}{I_{\text{photo}(x,y)}}.$$

(8)

Considering that all the terms in the above equation are affected by some deviation from their nominal values due to mismatch, and doing a first-order Taylor expansion we can re-express the equation in the following terms:

$$f(x,y) = \frac{I_{\text{ref}}}{C(V_{\text{reset}} - V_{\text{ref}})} \frac{I_{\text{avg}}}{I_{\text{photo}}} \Big|_{\text{nominal}} \times \left(1 + \frac{\Delta I_{\text{ref}}}{I_{\text{ref}}} - \frac{\Delta V}{V_{\text{reset}} - V_{\text{ref}}} - \frac{\Delta C}{C} + \frac{\Delta I_{\text{avg}}}{I_{\text{avg}}} - \frac{\Delta I_{\text{photo}}}{I_{\text{photo}}} + \Delta_{\text{TL}}\right) = f|_{\text{nominal}} (1 + \Delta(x, y))$$

(9)

where  $\Delta_{\rm TL}$  is the mismatch introduced by transistors  $M_1-M_4$  of the translinear circuit in Fig. 2(c). We observe that doing a first-order approximation, all the error terms combine in an additive way. This is because in (8) they appear either multiplying or dividing, but without additions nor subtractions. The calibration technique proposed here consists of adding a term  $I_{\rm cal}/I_{\rm ref}$  in (9) independently tunable for each pixel.<sup>3</sup> This term has to compensate independently for each pixel its random total deviation  $\Delta(x,y)$ . A tunable current  $I_{\rm cal}=I_u\alpha(x,y)$  ( $0\leq\alpha<2$ ) for each pixel is added in parallel to current  $I_{\rm ref}$  in such a way that we equalize all the pixel firing frequencies under flat illumination conditions

$$f(x,y) = f|_{\text{nominal}} \left( 1 + \Delta(x,y) + \frac{I_u \alpha(x,y)}{I_{\text{ref}}} \right).$$

(10)

The generation of the tunable calibration current  $I_{\rm cal}$  is based on the mini-DACs calibration technique proposed in [57], which exploits the linear current division technique of MOS transistors [69], [70]. Fig. 3 plots the schematic of the compact mini-DACs used to generate the calibration current  $I_{\rm cal}$  for each pixel. A careful compromise has to be made between precision after calibration, calibration circuitry area, and calibration circuitry power consumption. Following the suggestions in [57], and after performing extensive simulations, we reached the conclusion to use five calibration bits with mini-DACs unit transistors  $M_u$  of size  $W/L=1~\mu{\rm m}/1~\mu{\rm m}$  for the current ranges we needed. Trying to achieve extra bits in precision would result in an exponential growth in area.

Voltage  $V_{\rm cal}$  is applied from the periphery to generate a copy of  $I_u$ , which controls the calibration range of the mini-DACs. Each successive mini-DAC branch generates a current which equals the current of the preceding branch divided by 2. Each mini-DAC is controlled by a 5-bit calibration word  $w_{\rm cal} = \{w_4w_3w_2w_1w_0\}$ , which is stored locally in each pixel using static latches. Calibration words are loaded row by row. A peripheral shift register with 33 5-bit registers is loaded serially from an outside port using a 10-kHz clock. 32 5-bit words are copied in parallel into the registers of the selected array row, and the 33rd register indicates this selected row. The current generated in each branch of the pixel mini-DAC goes either to a dummy node common to all the pixels or is summed to the pixel

<sup>3</sup>If we had implemented the contrast definition of (2) or (3), then we would need to include two independent calibration currents per pixel.

calibration current  $I_{\rm cal}$  depending on the state of the stored bit  $w_i$ . Thus, the calibration current can be expressed as,

$$I_{\text{cal}} = I_u \sum_{i=0}^{4} \frac{w_i}{2^{4-i}}.$$

(11)

After introducing a calibration current  $I_{\rm cal}$  in parallel with the  $I_{\rm ref}$  current, each pixel frequency becomes a function not only of the pixel (x,y) but also of its calibration word. That is,  $f(x,y,w_{\rm cal})$ . The calibration procedure consists of identifying for each pixel (x,y) the optimum calibration word  $w_{\rm opt}(x,y)$ , such that the frequency dispersion among the pixels is minimized under a condition of uniform illumination.

During calibration, it is also important to tune properly the global bias current  $I_u$ . This current has to be comparable to the maximum pixels dispersion  $\Delta I_{\max} = \max_{(x,y)} (I_{\mathrm{ref}}\Delta(x,y))$ . If  $I_u$  is set to a very low current (compared to the maximum pixels dispersion  $\Delta I_{\max}$ ) the calibration range is very small compared to the pixels dispersion range. On the contrary, if  $I_u$  is set to a high value (compared to the maximum pixel deviation  $\Delta I_{\max}$ ), then the granularity of the calibration gets very coarse. In (10), if  $\Delta(x,y)$  varies between a maximum positive value of  $M_p$  and a minimum negative value of  $-M_n$ , then pixels are equalized by setting

$$\Delta(x,y) + \frac{I_u \alpha(x,y)}{I_{\text{ref}}} = M_p. \tag{12}$$

If  $\Delta(x,y)=M_p$  then for this pixel we set  $\alpha(x,y)=0$ . On the other hand, if  $\Delta(x,y)=-M_n$ , then  $\alpha(x,y)$  is set such that

$$-M_n + \frac{I_u \alpha^{\max}(x, y)}{I_{\text{ref}}} = M_p$$

$$\Rightarrow I_u \alpha^{\max}(x, y) = (M_p + M_n)I_{\text{ref}}. \quad (13)$$

According to (11), for a 5 bit mini DACs,  $\alpha^{\max}(x, y) = 1$ .

According to (11), for a 5-bit mini-DACs,  $\alpha^{\max}(x,y) = 1 + 15/16$ . An example procedure for proper selection of  $I_u$  is illustrated in the next section.

## IV. EXPERIMENTAL RESULTS

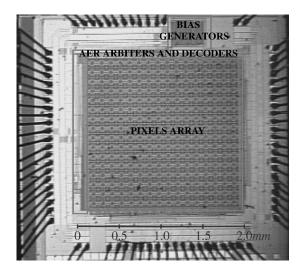

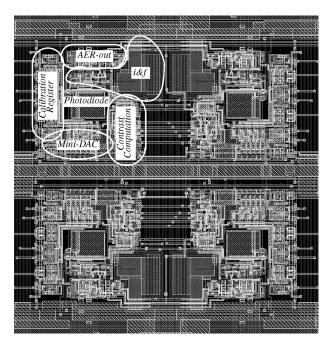

A test prototype retina of  $32 \times 32$  pixels has been fabricated in the AMS-0.35- $\mu$ m double-poly triple-metal CMOS technology. The whole system occupies an area of 2.88 mm  $\times$  2.88 mm. Fig. 4 shows a microphotograph of the fabricated retina. Table I summarizes chip specifications.

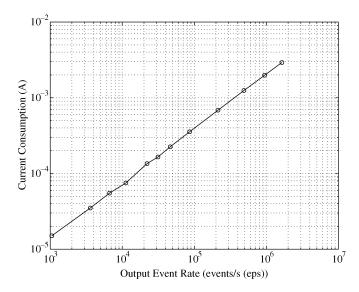

Chip power consumption is basically determined by the output event rate. If no output events are produced by the retina, standby current consumption is around 10  $\mu$ A for the biasing conditions we set. However, current consumption grows quickly with output event rate, and reaches 3 mA at 1.6 Meps. Fig. 5 shows the measured retina current consumption as function of its output event rate. For the AER out circuit we used Boahen's row parallel burst mode circuits [14]. When shorting Ack and Rqst, we measured handshaking cycles of 30 ns per event outside bursts and 15 ns per event within bursts.

The area of each pixel is  $58 \mu m \times 56 \mu m$ . The layout of an assemble of four pixels is shown in Fig. 6. The different pixel parts are highlighted in one of the pixels: photodiode ( $100\mu m^2$ —3% of pixel area), contrast computation

Fig. 4. Microphotograph of the  $32 \times 32$  retina.

#### TABLE I

| array size                                 | 32 x 32                                  |

|--------------------------------------------|------------------------------------------|

| pixel size                                 | 58µm х 56µm                              |

| pixel components                           | 104 transistors + 1 capacitor            |

| photodiode quantum efficiency              | 0.34 @ 450nm                             |

| fill factor                                | 3%                                       |

| pixel current consumption                  | 20nA @ 1keps, 1nA @ standby              |

| matching before calibration (indoor light) | 57%                                      |

| matching after calibration (indoor light)  | 6.6%                                     |

| contrast sensitivity                       | 10 Hz / %relative contrast @<br>400Hz DC |

| range of diffusers                         | ~10 pixels                               |

| noise standard deviation                   | ~6% fluctuation of spike rate            |

| dark current                               | ~500fA                                   |

| Handshaking cycle                          | 15ns/ev (shorting Ack and Rqst)          |

Fig. 5. Retina current consumption as function of its output event rate (in eps).

circuitry (300  $\mu$ m<sup>2</sup>—9%), mini-DAC (300  $\mu$ m<sup>2</sup>—9%), calibration registers (500  $\mu$ m<sup>2</sup>—15%), integrate-and-fire circuit (600 $\mu$ m<sup>2</sup>—18%), AER-out circuit (300  $\mu$ m<sup>2</sup>—9%). The rest of the area goes to routing. The routing channels are shared by contiguous pixels. The digital input and output signals

Fig. 6. Layout of an assemble of  $2 \times 2$  pixels. In one of the pixels we show the area of the photodiode, the contrast computation circuitry, the mini-DACs and calibration registers, the i&f circuit, and the AER-out event generation circuit for communication with chip periphery.

for the transmission of the pixel events are laid out as far as possible from the pixel analog parts (i.e., integrating capacitors, sub-pico-ampere current mirrors, etc.).

The fabricated retina has been extensively tested. In the following, we provide results of different experiments that we designed to investigate the performance of the retina under different conditions.

## A. Calibration Experiments

We have calibrated our contrast retina under three different illumination conditions: darkness, ambient laboratory illumination, and bright illumination. The retina bias currents and voltages were kept the same in the three cases. In the three cases, we obtained a great improvement in the performance after doing calibration. Fig. 7 summarizes the performance of the retina before and after optimum calibration in the three experiments. In Fig. 7, the histograms of the pixels output frequencies under uniform illumination are represented. Each row in Fig. 7 corresponds to a different illumination condition. The left column represents the output frequencies before calibrating the retina, while the right column represents the pixels output frequencies after optimum calibration. We can observe that the performance of the retina is very similar for the indoor illumination and for the illumination under a bright light source. However, the mismatch is higher for darkness. The reason is that in dark conditions the  $\Delta I_{\rm photo}/I_{\rm photo}$  in (9) contains the mismatch due to the sub-pico-ampere current mirrors plus the mismatch of the photodiodes dark currents which becomes significant under this condition. When light shines on the retina, the  $I_{

m photo}$  denominator increases and the mismatch due to dark current becomes negligible. From our experiments, we have also verified that the retina performance is not severely degraded when the retina is calibrated under a given light condition and that illumination

Fig. 7. Frequency histograms of the retina before and after calibration under different illumination conditions. Separate calibration is done for each row. Horizontal axes represent pixel frequency, and vertical axes number of pixels per bin.

condition changes. However, the retina performance is severely degraded if the calibration was done for darkness.

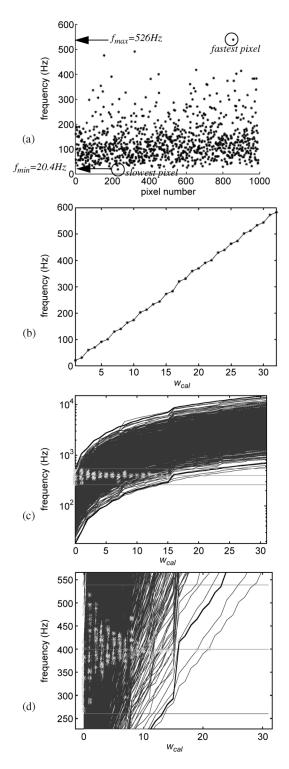

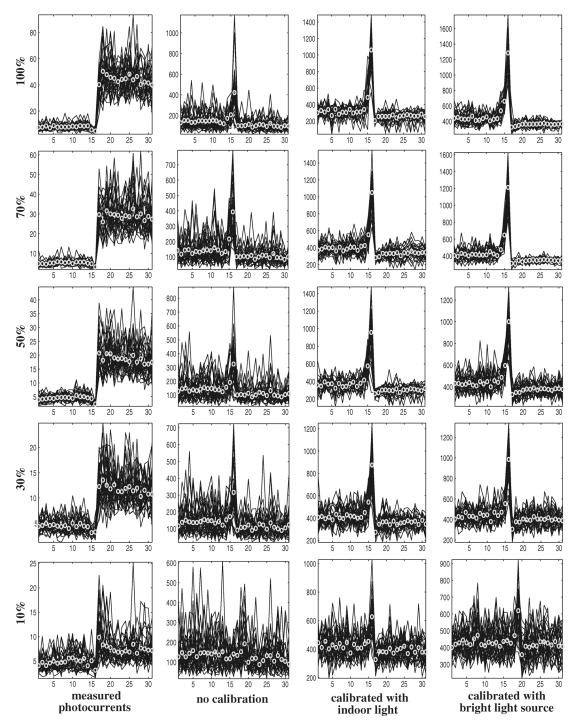

Fig. 8(a) plots the measured output frequencies of all the retina pixels before calibration when the retina is under uniform ambient laboratory light. The maximum measured output frequency is  $f_{\rm max}=526$  Hz and the minimum measured output frequency is  $f_{\rm min}=20.4$  Hz. As explained in Section III, it is important to appropriately set the value of current  $I_u$  to optimize the performance of the calibrated chip. We did this  $I_u$  optimization in two stages.

In the first stage, we followed the following procedure.

- 1) For the uncalibrated retina, we identified the slowest pixel (the pixel with the lowest output frequency).

- 2) We adjusted current  $I_u$  so that the frequency of the slowest pixel for the maximum calibration word ( $w_{\rm cal}=31$ ) equals the frequency of the fastest pixel ( $f_{\rm max}$ ), when its calibration is disabled ( $w_{\rm cal}=0$ ).

- 3) For the determined  $I_u$  value, we measured all the pixels calibration curves. That is, we measured for each pixel its output frequency as a function of the calibration word  $w_{\rm cal}$ .

- 4) We computed the optimum calibration words. That is, we determined the optimum pixels calibration words  $w_{\rm cal} = w_{\rm opt}(x,y)$  that minimize the dispersion in the output frequencies.

Calibration tries to set all pixel frequencies equal to the maximum pixel frequency. Consequently, before calibration, the

Fig. 8. (a) Measured pixels output frequencies of the uncalibrated retina under uniform indoor illumination. (b) Calibration curve of the slowest pixel for  $I_u=0.3\,$  nA. (c) calibration curves for all the retina pixels for  $I_u=0.3\,$  nA. (d) Detail of the region of fitted frequencies.

global bias current  $I_{\rm ref}$  should be adjusted such that the fastest pixel frequency is the one desired for the whole array (after calibration).

Fig. 8 shows some plots that illustrate the first stage of this calibration procedure. Fig. 8(b) plots the output frequency of the slowest pixel as a function of the calibration word for current  $I_u = 0.3$  nA. As can be observed, its maximum frequency

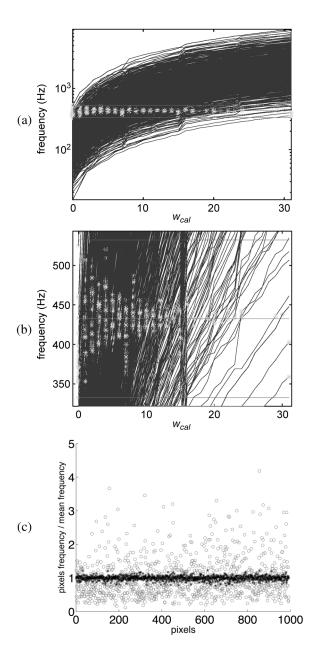

Fig. 9. (a) Calibration curves of all the retina pixels for current  $I_u=0.25~\mathrm{nA}$ . (b) Detail of the optimum fitted frequency region. (c) Measured pixels frequencies before and after calibration divided by the mean output frequency in each case.

equals approximately the frequency of the fastest uncalibrated pixel  $f_{\rm max}$ . Fig. 8(c) plots superimposed the calibration curves for all the pixels. In these measurements, current  $I_u$  is set to 0.3 nA and the output frequency of each pixel is measured versus the calibration word. Fig. 8(d) shows a detail of Fig. 8(c). The asterisks show the selected optimum calibration word and optimum output frequency for each retina pixel. The upper and lower horizontal lines mark the maximum and minimum selected frequencies. The middle horizontal line marks the target optimum output frequency  $f_{\rm opt}$  which in this case is 400 Hz. The precision achieved after calibration is  $\sigma=10.2\%$ . We can observe in Fig. 8(d) that the upper range of calibration words remained unused after the optimization. Thus, we can increase the precision after calibration by reducing current  $I_u$ .

To optimize the setting of current  $I_u$ , we take a second calibration stage. In this second calibration, we reduce current  $I_u$  so that the maximum output frequency of the slowest pixel (with  $w_{\rm cal} = 31$ ) equals the optimum frequency of the previous calibration stage. After that, current  $I_u$  was reduced to 0.25 nA. Then, we go to step 3 of the previous calibration stage. Fig. 9(a) plots superimposed the calibration curves of all retina pixels for  $I_u = 0.25$  nA. Fig. 9(b) shows a detail of Fig. 9(a). The asterisks show the fitted optimum calibration words and fitted output frequencies. The upper and lower horizontal lines mark the maximum and minimum fitted output frequencies. The middle horizontal line signals the target optimum frequency  $f_{\rm opt} = 433 \, {\rm Hz}$ . In this case, the precision achieved after calibration has been improved to  $\sigma = 6.6\%$ . We can observe, that now we are making use of the whole range of calibration words. Fig. 9(c) represents with circles the output frequencies of all retina pixels before calibration. The output frequencies of the same pixels after calibration are represented with asterisks. The frequency spread before calibration is  $f_{\rm max}/f_{\rm min}=41$ , while after calibration is  $f_{\rm max}/f_{\rm min} = 1.6.$

An interesting issue is how long can it take in production to calibrate a retina. The slowest step is to characterize all pixels for all calibration words. Calibration words are loaded at 10-kHz clock rate. This implies about 0.1 s to load all of them. To read out the pixel frequencies, one should take a minimum of ten events per pixels. This will take around 1 s before first calibration [since minimum pixel frequency can be as low as 10 Hz—see Fig. 7 and Fig. 8(b)] and about 50 ms after first calibration (since minimum frequency is easily above 200 Hz). All this has to be repeated 32 times. Then one also needs to add the computation time to calculate the optimum calibration words. Under optimized conditions in production, calibrating one single retina can take around one minute.

#### B. Contrast Extraction Experiments

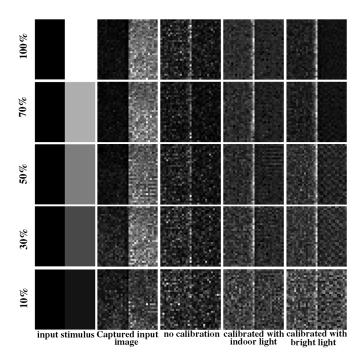

We have done experiments where we presented to the retina a sheet of printed paper (laser printer) composed of half black and half white/gray regions separated vertically. The relative contrast between the two regions varied from a 100% contrast (for half black and half white) to a 10% contrast (half black and half dark gray). For the left half we used always full black  $(I_{\text{left}} = 1)$ while for the right half we changed from full white  $(I_{\text{right}} = 0)$ to dark gray  $(I_{\text{right}} = 0.9)$ . In this experiment we define "relative contrast between the two regions" as  $(I_{\text{left}} - I_{\text{right}})/I_{\text{left}}$ . The pieces of paper of about 5 cm  $\times$  5 cm were hold 3–5 cm away from the lens, which was a wide angle one. Illumination was based on conventional fluorescent ambient laboratory light. The input images presented to the retina are plotted on the first column of Fig. 10. We captured the image with the retina set to its contrast extraction mode but with different calibration conditions: uncalibrated retina, retina with the optimum calibration weights and current  $I_u$  obtained for the indoor light conditions, retina with the calibration weights and current  $I_u$  optimized for the illumination with a bright light source.

Fig. 10 shows some of the images obtained from these experiments. In Fig. 10, the pixels output frequencies were mapped linearly to a gray scale. These images are reconstructed by capturing  $2 \times 10^5$  timestamped events from the retina using a

Fig. 10. Images acquired by the contrast extraction retina when an image of half white and half black regions separated vertically is presented to the retina with different levels of contrast between the two regions. The different rows correspond to images presented with different contrast levels, while the different columns correspond to different settings of the retina. The first column shows the input stimulus. The second column shows directly the photocurrents. The third column shows the uncalibrated retina output. In the fourth column, the retina was calibrated under indoor light. In the fifth column, the retina was calibrated under a bright light source. All the images were acquired under the same illumination conditions, which correspond to the calibration conditions of the last column.

special purpose hardware [72], which stores them into computer memory for later analysis. From these captured timestamped events, we can determine for each pixel its average frequency and jitter. On average, frequency jitter standard deviation was around 6% of the mean frequency. Each row in Fig. 10 corresponds to a different input image presented to the retina. The first row are the reconstructed output images when the retina sees an image with 100% contrast. The contrast is reduced progressively. The last row corresponds to the retina seeing an image with low (10%) contrast. The first column plots the input stimulus printed on the papers. The second column shows the acquired photocurrents, when setting retina pixels sw1 and sw2 in Fig. 2 to integrate directly the mirrored photocurrents. In this case, there is no calibration. The third column in Fig. 10 plots the output images obtained with the uncalibrated retina. The fourth column plots the images obtained with the retina calibrated for indoor light conditions. And the fifth column shows the images obtained with the retina calibrated for bright illumination. All the images in Fig. 10 were obtained under bright illumination conditions, so that the illumination conditions match the calibration conditions of the last column of images.

We can make the following observations. Images acquired with the uncalibrated retina have high fixed pattern noise (FPN), as can be expected from the measurements shown in Section IV-A. Calibration not only reduces FPN but also allows to clearly recognize edges when low contrast images are

Fig. 11. Numerical representation of the output images shown in Fig. 10. Each row is the output obtained for different contrast input images. The four columns correspond to the right most columns in Fig. 10. For each subplot, horizontal axes represent the pixel column number in a row (from 1 to 32). Vertical axes represent the pixel output frequency. Circles indicate the average computed for all rows.

presented to the retina. In the 10% contrast image, edge recognition is impossible with the uncalibrated retina. Finally, as we already claimed in Section IV-A, resolution is not severely degraded when the illumination conditions do not match the calibration conditions (except when calibrating in darkness).

Fig. 11 represents the same information plotted in Fig. 10. However, in this case, we have represented numerically the output frequency of each retina pixel as a function of its position along a row. The output frequencies of the pixels located in the same retina columns are superimposed.

The minimum contrast we could measure without calibration was 30%, while with calibration it was<sup>4</sup> 10%. In Fig. 11, we also show the average contrast frequency computed among all rows. At the regions without contrast, the standby output frequency is about 400 Hz (after calibration). By looking at the difference between the central pixel frequencies and the standby frequency, as a function of input image relative contrast, we can estimate the contrast sensitivity of the retina. This sensitivity is approxi-

<sup>&</sup>lt;sup>4</sup>Note that this 10% contrast limit is estimated with a "by-eye" judgement using a stimulus with an extended edge covering the whole imaging area.

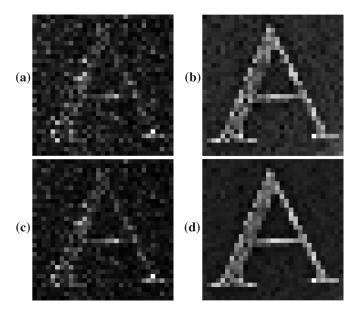

Fig. 12. Retina output acquired: (a) by the uncalibrated retina under indoor illumination, (b) by the calibrated retina under indoor illumination, (c) by the uncalibrated retina under bright illumination, and (d) by the calibrated retina under bright illumination. For (b) and (d) retina was calibrated only once, under indoor illumination.

mately independent of illumination conditions, and has a value of around 10 Hz for every percentage change of input image "relative contrast between the two regions." In the upper range, output frequency tends to saturate.

# C. Performance Under Different Illuminations

To examine the retina performance under different illumination conditions, we acquired the same static input under different illumination conditions. These results are shown in Fig. 12. Fig. 12(a) and (b) were acquired under indoor illumination. Fig. 12(a) was acquired by the uncalibrated retina, while in Fig. 12(b) the retina was calibrated. The calibration used in Fig. 12(b) was the optimum for indoor illumination conditions. Fig. 12(c) and (d) were acquired under bright illumination. In Fig. 12(c), the retina was uncalibrated, and in Fig. 12(d) we were using the same calibration than for Fig. 12(b).

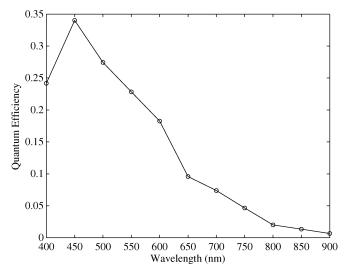

## D. Photosensor Optical Characterization

In order to characterize the pixel photo sensing p-diffusion n-well diode, we mounted the retina chip without lenses on an optical characterization bench. The retina was exposed to uniform light of controlled illumination power and wavelength. The retina was configured to operate in its direct photosensing mode (sw1 on and sw2 off in Fig. 2), and the pixels events were recorded. For each measurement, a total of  $10^5$  retina events were recorded, and the average pixel event frequency was computed. This way, the effect of current mirrors mismatch, capacitors mismatch, and comparators voltage mismatch is averaged out over all pixels in the array. The average total capacitance of the integrate-and-fire node in Fig. 2(d) was estimated, using layout extraction, to be around 280 fF. This way, photocurrent can be directly estimated from the average pixel frequency.

Fig. 13. Measure photodiode quantum efficiency as function of light wavelength.

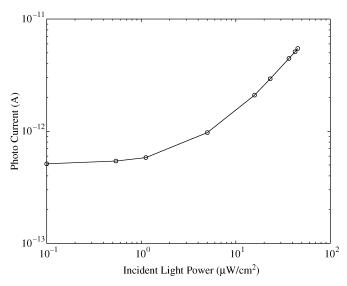

Fig. 14. Pixel photocurrent as function of incident light power at  $\lambda = 55$  nm.

Knowing the average pixel photocurrent  $I_{\rm photo}$  and the incident light power per unit surface  $P_{\rm light}$  at a given wavelength  $\lambda$ , the quantum efficiency QE of the photosensor is given by

$$QE = \frac{I_{\text{photo}}}{P_{\text{light}}\lambda} \frac{hc}{Aq}$$

(14)

where  $h=6.6\times 10^{-34}$  Js is the Plank constant,  $c=3\times 10^8~\rm ms^{-1}$  is light speed,  $q=1.6\times 10^{-19}~\rm C$  is the electron charge, and  $A=100~\mu\rm m^2$  is the photodiode area. This QE is shown in Fig. 13 as function of incident light wavelength. As expected, this photodiode is more sensitive to light in the blue range [71]. Its peak QE is 0.34 at 450-nm wavelength.

Similarly, the pixel average frequency was obtained for different light intensities at a fixed wavelength ( $\lambda=550$  nm). Fig. 14 shows the measured photocurrent as function of incident light power. When there is no light, we obtained a dark current of approximately 500 fA. By exposing the retina directly to sunlight we obtained an average photodiode current of 1.3 nA.

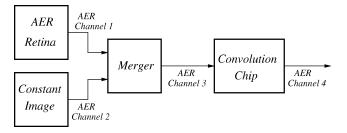

Fig. 15. Setup used to convert the unsigned AER retina output with dc level to a signed AER stream with no dc level.

#### V. TRUE CONTRAST AER OUTPUT

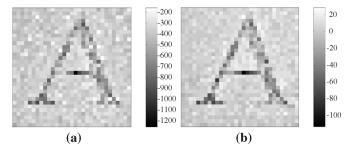

The retina chip presented in this paper suffers from a fundamental limitation, also present in other contrast retinae chips [58]: when the input is uniform there is a nonzero output. This means that there is an output dc level around which the output changes. If contrast is negative, the output goes below this dc level, while when contrast is positive the output goes above it. In our case, since the retina output is given as an AER signal, this is an inconvenience because the retina will consume communication bandwidth even when there is no output signal (zero contrast). A true AER contrast retina should provide a zero event frequency output for those pixels with zero contrast, and a signed nonzero event frequency for those pixels with a nonzero contrast. This is specially important if the output of the retina is going to be fed to an AER-based spike event processing system composed of several AER transceiver stages, each with many chips working in parallel. In this case, a significant amount of energy and communication bandwidth would be consumed when no signal (contrast) is present at the sensor output. Consequently, this plays against the AER scheme fundamental advantage. To overcome this problem, we use the setup illustrated in Fig. 15. This setup includes four AER independent point-to-point channels. These channels are signed AER channels, which means that the event address includes a sign bit. Our AER retina output goes to AER channel-1, for which we set the sign bit constant and negative for all events. This channel goes to a merger block [72]. A merger block is a simple logic circuit, easy to program on a field-programmable gate array (FPGA), which takes input events from several AER channels, arbitrates them and manages their handshaking signals, and copies every input event coming from any input channel to its output channel while generating conveniently its handshaking signals. The second AER input of the merger, channel-2, comes from a uniform image generator. This is an AER sender with  $32 \times 32$  pixels, all generating output events of constant frequency. Their event frequency is set to the same than the dc level of the retina, and the sign bit is set positive for all pixels. A uniform AER image generator can easily be implemented on an FPGA using any of the algorithms reported elsewhere [73]. At the output of the merger, at AER channel-3, there will be all events generated by the retina and all events generated by the uniform image generator, conveniently arbitrated. The event activity on channel-3 will be high. Note that for a pixel with zero contrast in the retina there will be a number of negative events per second (eps) which corresponds to the retina output frequency dc level, plus the same number of positive events. Those events can be subtracted by proper

Fig. 16. Experimentally obtained outputs from the setup of Fig. 15. (a) Image reconstructed from the AER flow at channel-1, and (b) Image reconstructed from the AER flow at channel-4. Vertical sidebar indicates gray level coding of pixel frequency.

integration for each pixel. This is accomplished by the AER convolution chip [38], [74] receiving events from channel-3. This convolution chip has been programmed with a convolution kernel of size 1 × 1. This way, its operation will be equivalent to a simple array of integrators. Consequently, it will just copy the input visual flow to its output. Since each pixel of the convolution chip includes an integrate-and-fire pixel capable of handling signed events, each pixel will produce output events with a frequency proportional to the difference of the event frequencies between channel 1 and 2. Therefore, the AER output of the convolution chip, channel-4, will show zero event frequency for those pixels with zero contrast, and signed events for those pixels with nonzero contrast, while reducing significantly the overall event flow in channel-4 with respect to channel-1 (and channels 2 and 3).

The setup of Fig. 15 was assembled in our lab using the present AER retina, a 32 × 32 convolution chip developed in our labs [38], [74], the FPGA-based synthetic AER image generator reported in [73] and the FPGA-based AER merger and splitter reported in [72]. The results are shown in Fig. 16. Fig. 16(a) shows the image reconstructed from the events coming out directly from the AER contrast retina (events on channel-1). The contrast retina produces unsigned events. Therefore, the sign bit at the channel-1 input of the merger was shorted to ground (negative sign) permanently. The total event rate at channel-1 was 384 keps (kilo eps). The event rate spread for the retina pixels varied between 160 eps and 1300 eps. The dc level (zero contrast) of the pixels was 368 eps. Consequently, the synthetically generated AER stream at channel-2 was such that for all pixels its constant event rate was 368eps, with its sign bit set to "1" (positive). The total event rate at channel-2 was 377 keps. At channel-3, the total event rate was 761 keps. The reconstruction of the convolution chip AER output, channel-4, is shown in Fig. 16(b). As one can see, the information content difference between the images in Fig. 16(a) and Fig. 16(b) is negligible. However, the total event rate at channel-4 has been significantly reduced, down to 9.89 keps. The signed event rate of the pixels varied between +27 eps and -110 eps. The average absolute value event rate of the pixels was 9.66 eps, while the average signed event rate of the pixels was -0.88 eps. Consequently, this setup allows to reduce the total retina event rate by a factor of approximately 40 while adding a sign at the same time, and without eliminating any (contrast) information. This is of crucial importance for assembling multi-layer event-based bio-inspired processing systems, since this allows to reduce significantly the information flow and energy budget at all subsequent stages, and allows to separate positive and negative information flow which is characteristic of many bio-inspired processing systems [60] and biology itself [59].

## VI. CONCLUSION

We have presented a contrast retina chip that provides its output as an AER stream. The contrast is computed as a result of multiplying and dividing currents at each pixel. This fact allows to calibrate mismatch by using one unique trimmable current per pixel. The drawback however is that such approach results in a contrast output with a nonzero dc level. This is particularly negative for AER-based systems, since this introduces a significant extra event flow when information is absent. However, this drawback can be overcome by adding an extra processing before sending contrast information to a more complex AER-based processing system. This also shows the great power and potential of AER processing when one has available a small set of AER blocks (such as synthetic generators, mergers, splitters, and convolution processors) and connects them in an appropriate configuration. In the present paper we have provided detailed descriptions of the design of the retina pixel and how calibration capability has been included. We have also provided extensive experimental results illustrating the correct operation of the retina and how it benefits from its calibration capability. Presently, we are working in the development of a new contrast retina that directly provides signed events and zero output activity when there is zero contrast.

#### ACKNOWLEDGMENT

The authors would like to thank all authors of [72] for developing the AER computer interfaces, and letting them use them for this work. They would also like to thank E. Roca for her assistance in the optical bench measurements, and T. Delbruck for valuable advise and discussions. Finally, special thanks go to the anonymous reviewers who have contributed to improve the final quality of the paper.

#### REFERENCES

- M. Sivilotti, "Wiring considerations in analog VLSI systems with application to field-programmable networks," Ph.D. thesis, Comp. Sci. Div., California Institute of Technology, Pasadena, 1991.

- [2] M. Mahowald, "VLSI Analogs of neural visual processing: A synthesis of form and function," Ph.D. thesis, Comp. Sci. Div., California Institute of Technology, Pasadena, 1992.

- [3] J. Lazzaro, J. Wawrzynek, M. Mahowald, M. Sivilotti, and D. Gillespie, "Silicon auditory processors as computer peripherals," *IEEE Trans. Neural Netw.*, vol. 4, no. 3, pp. 523–528, May 1993.

- [4] M. Mahowald, An Analog VLSI Stereoscopic Vision System. Reading, MA: Kluwer Academic, 1994.

- [5] J. P. Lazzaro and J. Wawrzynek, "A multi-sender asynchronous extension to the address-event protocol," in *Proc. 16th Conf. Adv.Res. VLSI*, W. J. Dally, J. W. Poulton, and A. T. Ishii, Eds., 1995, pp. 158–169.

- [6] W. Maass and C. M. Bishop, Eds., Pulsed Neural Networks. Cambridge, MA: MIT Press, 1999.

- [7] S. Thorpe, D. Fize, and C. Marlot, "Speed of processing in the human visual system," *Nature*, vol. 381, no. 6582, pp. 520–522, Jun. 6, 1996.

- [8] P. F. Ruedi *et al.*, "A 128 × 128, pixel 120-dB dynamic-range vision-sensor chip for image contrast and orientation extraction," *IEEE J. Solid-State Circuits*, vol. 38, no. 12, pp. 2325–2333, Dec. 2003.

- [9] M. Barbaro, P. Y. Burgi, A. Mortara, P. Nussbaum, and F. Heitger, "A 100 × 100 pixel silicon retina for gradient extraction with steering filter capabilities and temporal output coding," *IEEE J. Solid-State Circuits*, vol. 37, no. 1, pp. 160–172, Jan. 2002.

- [10] A. Mortara and E. A. Vittoz, "A communication architecture tailored for analog VLSI artificial neural networks: Intrinsic performance and limitations," *IEEE Trans. Neural Netw.*, vol. 5, no. 3, pp. 459–466, May 1994.

- [11] A. Mortara, E. A. Vittoz, and P. Venier, "A communication scheme for analog VLSI perceptive systems," *IEEE J. Solid-State Circuits*, vol. 30, no. 6, pp. 660–669, Jun. 1995.

- [12] Z. Kalayjian and A. G. Andreou, "Asynchronous communication of 2-D motion information using winner-takes-all arbitration," *Int. J. Analog Integ. Circ. Sign. Proc.*, vol. 13, no. 1–2, pp. 103–109, Mar./Apr. 1997.

- [13] K. A. Boahen, "Communicating neuronal ensembles between neuromorphic chips," in *Neuromorphic Systems Engineering: Neural Net*works in Silicon, T. S. Lande, Ed. Norwell, MA: Kluwer, 1998, ch.

- [14] K. Boahen, "Point-to-point connectivity between neuromorphic chips using address events," *IEEE Trans. Circuits Syst. II, Analog Digit.* Signal Process., vol. 47, no. 5, pp. 416–434, May 2000.

- [15] K. A. Boahen, "A burst-mode word-serial address-event link-I transmitter design," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 7, pp. 1269–1280, Jul. 2004.

- [16] K. A. Boahen, "A burst-mode word-serial address-event link-II: Receiver design," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 7, pp. 1281–1291, Jul. 2004.

- [17] K. A. Boahen, "A burst-mode word-serial address-event link-III: Analysis and test results," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 7, pp. 1292–1300, Jul. 2004.

- [18] E. Culurciello, R. Etienne-Cummings, and K. A. Boahen, "A biomorphic digital image sensor," *IEEE J. Solid-State Circuits*, vol. 38, no. 2, pp. 281–294, Feb. 2003.

- [19] C. Shoushun and A. Bermak, "A low power CMOS imager based on time-to-first-spike encoding and fair AER," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS'05)*, 2005, pp. 5306–5309.

- [20] X. G. Qi, X., and J. Harris, "A time-to-first-spike CMOS imager," in Proc. 2004 IEEE Int. Symp. Circuits Syst. (ISCAS2004), Vancouver, Canada, 2004, pp. 824–827.

- [21] M. Azadmehr, J. Abrahamsen, and P. Häfliger, "A foveated AER imager chip," in *Proc. IEEE Int. Symp. on Circuits Syst. (ISCAS2005)*, Kobe, Japan, 2005, pp. 2751–2754.

- [22] R. J. Vogelstein, U. Mallik, E. Culurciello, R. Etienne-Cummings, and G. Cauwenberghs, "Spatial acuity modulation of an address-event imager," in *Proc. 2004 11th IEEE Int. Conf. Electronics, Circuits Syst.* (ICECS 2004), Dec. 2004, pp. 207–210.

- [23] J. Kramer, "An integrated optical transient sensor," *IEEE Trans. Circuits Syst., II. Analog Digit. Signal Process.*, vol. 49, no. 9, pp. 612–628, Sep. 2002.

- [24] P. Lichtsteiner, T. Delbrück, and J. Kramer, "Improved on/off temporally differentiating address-event imager," in *Proc.* 2004 IEEE Int. Symp. Circuits Syst. (ISCAS2004), Vancouver, Canada, 2004, pp. 211–214.

- [25] P. Lichtsteiner, C. Posch, and T. Delbruck, "A 128 × 128 120 dB 30 mW asynchronous vision sensor that responds to relative intensity change," in *Dig. Tech. Papers IEEE ISSCC*, San Francisco, CA, 2006, pp. 508–509.

- [26] M. Arias-Estrada, D. Poussart, and M. Tremblay, "Motion vision sensor architecture with asynchronous self-signaling pixels," in *Proc.* 7th Int. Workshop Computer Architecture for Machine Perception (CAMP97), 1997, pp. 75–83.

- [27] C. M. Higgins and S. A. Shams, "A biologically inspired modular VLSI system for visual measurement of self-motion," *IEEE Sensors J.*, vol. 2, no. 6, pp. 508–528, Dec. 2002.

- [28] E. Özalevli and C. M. Higgins, "Reconfigurable biologically inspired visual motion system using modular neuromorphic VLSI chips," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 1, pp. 79–92, Jan. 2005.

- [29] G. Indiveri, A. M. Whatley, and J. Kramer, "A reconfigurable neuromorphic VLSI multi-chip system applied to visual motion computation," in *Proc. Int. Conf. Microelectronics for Neural, Fuzzy and Bio-Inspired Systems (Microneuro99)*, Granada, Spain, 1999, pp. 37–44.

- [30] K. Boahen, "Retinomorphic chips that see quadruple images," in Proc. Int. Conf. Microelectronics for Neural, Fuzzy and Bio-Inspired Systems (Microneuro99), Granada, Spain, 1999, pp. 12–20.

- [31] R. Z. Shi and T. K. Horiuchi, "A VLSI model of the bat dorsal nucleus of the lateral lemniscus for azimuthal echolocation," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS2005)*, Kobe, Japan, 2005.

- [32] A. van Schaik and S.-C. Liu, "AER EAR: A matched silicon cochlea pair with address event representation interface," in *Proc. IEEE Int.* Symp. Circuits Syst. (ISCAS2005), Kobe, Japan, 2005, pp. 4213–4216.

- [33] G. Cauwenberghs, N. Kumar, W. Himmelbauer, and A. G. Andreou, "An analog VLSI Chip with asynchronous interface for auditory feature extraction," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 45, no. 5, pp. 600–606, May 1998.

- [34] M. Oster and S.-C. Liu, "Spiking inputs to a spiking winner-take-all circuit," in Advances in Neural Information Processing Systems, Y. Weiss, B. Schölkopf, and J. Platt, Eds. Cambridge, MA: MIT Press, 2006, vol. 18, pp. 1051–1058 [Online]. Available: http://www.books.nips.cc/papers/files/nips18/NIPS2005\_0521.pdf, (NIPS'06)

- [35] J. Abrahamsen, P. Häfliger, and T. S. Lande, "A time domain winner-take-all network of integrate-and-fire neurons," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS04)*, Vancouver, Canada, May 2004, vol. V, pp. 361–364.

- [36] E. Chicca, G. Indiveri, and R. J. Douglas, "An event-based VLSI network of integrate-and-fire neurons," in *Proc. IEEE Int. Symp. on Circuits Syst. (ISCAS2004)*, Vancouver, Canada, 2004, vol. V, pp. 357–360.

- [37] T. Teixeira, A. G. Andreou, and E. Culurciello, "Event-based imaging with active illumination in sensor networks," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS2005)*, Kobe, Japan, 2005, pp. 644–647.

- [38] R. Serrano-Gotarredona, T. Serrano-Gotarredona, A. Acosta-Jiménez, and B. Linares-Barranco, "A neuromorphic cortical layer microchip for spike-based event processing vision systems," *IEEE Trans. Circuits* Syst. I, Reg. Papers, vol. 53, no. 12, pp. 2548–2566, Dec. 2006.

- [39] D. H. Goldberg, G. Cauwenberghs, and A. G. Andreou, "Probabilistic synaptic weighting in a reconfigurable network of VLSI integrate-and-fire neurons," *Neural Netw.*, vol. 14, no. 6–7, pp. 781–793, 2001.

- [40] R. J. Vogelstein, U. Mallik, and G. Cauwenberghs, "Silicon spike-based synaptic array and address-event transceiver," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS'04)*, 2004, vol. 5, pp. 385–388.

- [41] R. J. Vogelstein, F. Tenore, R. Philipp, M. S. Adlerstein, D. H. Goldberg, and G. Cauwenberghs, "Spike timing-dependent plasticity in the address domain," in *Advances in Neural Information Processing Systems*, S. Becker, S. Thrun, and K. Obermayer, Eds. Cambridge, MA: MIT Press, 2003, vol. 15.

- [42] R. J. Vogelstein, U. Mallik, G. Cauwenberghs, E. Culurciello, and R. Etienne-Cummings, "Saliency-driven image acuity modulation on a reconfigurable silicon array of spiking neurons," in *Advances* in *Neural Information Processing Systems*, L. K. Saul, Y. Weiss, and L. Bottou, Eds. Cambridge, MA: MIT Press, 2005, vol. 17, pp. 1457–1464.

- [43] U. Mallik, R. J. Vogelstein, E. Culurciello, R. Etienne-Cummings, and G. Cauwenberghs, "A real-time spike-domain sensory information processing system," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS'05)*, Kobe, Japan, 2005, pp. 1919–1922.

- [44] S.-C. Liu, J. Kramer, G. Indiveri, T. Delbrück, and R. Douglas, "Orientation-selective a VLSI spiking neurons," *Neural Netw.*, vol. 14, pp. 629–643, 2001.

- [45] P. Vernier, A. Mortara, X. Arreguit, and E. A. Vittoz, "An integrated cortical layer for orientation enhancement," *IEEE J. Solid-State Cicuits*, vol. 32, pp. 177–186, Feb. 1997.

- [46] T. Serrano-Gotarredona, A. G. Andreou, and B. Linares-Barranco, "AER image filtering architecture for vision processing systems," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 46, no. 9, pp. 1064–1071, Sep. 1999.

- [47] T. Y. W. Choi, B. E. Shi, and K. Boahen, "An ON-OFF orientation selective address event representation image transceiver chip," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 2, pp. 342–353, Feb. 2004.

- [48] T. Y. W. Choi, P. A. Merolla, J. V. Arthur, K. A. Boahen, and B. E. Shi, "Neuromorphic implementation of orientation hypercolummns," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 6, pp. 1049–1060, Jun. 2005

- [49] M. A. Mahowald and C. Mead, "Silicon retina," in *Analog VLSI and Neural Systems*, C. Mead, Ed. Reading: Addison Wesley, 1989, ch. 15, pp. 257–278.

- [50] A. G. Andreou and K. A. Boahen, "A 590,000 transistor 48,000 pixel, contrast sensitive, edge enhancing, CMOS imager-silicon retina," in *Proc. 16th Conf. on Advanced Research in VLSI (ARVLSI'95)*, 1995, p. 225.

- [51] K. A. Zaghloul and K. Boahen, "Optic nerve signals in a neuromorphic chip: Parts 1," *IEEE Trans. Biomed Eng.*, vol. 51, pp. 657–666, 2004.

- [52] K. A. Zaghloul and K. Boahen, "Optic nerve signals in a neuromorphic chip: Part 2," *IEEE Trans. Biomed Eng.*, vol. 51, pp. 667–675, 2004.

- [53] R. H. Nixon, S. E. Kemeny, B. Pain, C. O. Staller, and E. R. Fossum, "256 × 256 CMOS active pixel sensor camera-on-a-chip," *IEEE J. Solid-State Circuits*, vol. 31, pp. 2046–2050, Dec. 1996.

- [54] G. Jun, C. Zhungjian, L. Wengao, and J. Lijiu, "Correlated-double-sampling design for CMOS image readout integrated circuits," in *Proc. 7th Int. Conf. Solid-State Integrated Circuits Technol.*, Oct. 2004, vol. 2, pp. 1437–1440.

- [55] S. Kavadias, B. Dierickx, D. Scheffer, A. Alaerts, D. Uwaerts, and J. Bogaerts, "A logarithmic response CMOS image sensor with on-chip calibration," *IEEE J. Solid-State Circuits*, vol. 35, no. 8, pp. 1146–1152, Aug. 2000.

- [56] M. Loose, K. Meier, and J. Schemmel, "A self-calibrating single-chip CMOS camera with logarithmic response," *IEEE J. Solid-State Cir*cuits, vol. 36, no. 4, pp. 586–596, Apr. 2001.

- [57] B. Linares-Barranco, T. Serrano-Gotarredona, and R. Serrano-Gotarredona, "Compact low-power calibration mini-DACs for neural massive arrays with programmable weights," *IEEE Trans. Neural Netw.*, vol. 14, no. 5, pp. 1207–1216, Sep. 2003.

- [58] K. A. Boahen and A. G. Andreou, "A contrast sensitive silicon retina with reciprocal synapses," in *Advances in Neural Information Pro*cessing Systems. San Mateo: Morgan Kaufmann Publishers, 1992, vol. 4, pp. 764–772, (NIPS 1991).

- [59] J. E. Dowling, The Retina: An Approachable Part of the Brain. Cambridge, MA: Harvard University Press, 1987.

- [60] S. Grossberg, E. Mingolla, and J. Williamson, "Synthetic aperture radar processing by a multiple scale neural system for boundary and surface representation," *Neural Netw.*, vol. 8, no. 7/8, pp. 1005–1028, 1995.

- [61] B. Linares-Barranco, T. Serrano-Gotarredona, R. Serrano-Gotarredona, and C. Serrano-Gotarredona, "Current-mode techniques for sub-pico-ampere circuit design," *Int. J. Analog Integr. Circuits Signal Process.*, vol. 38, pp. 103–119, 2004.

- [62] B. Linares-Barranco and T. Serrano-Gotarredona, "On the design and characterization of femtoampere current-mode circuits," *IEEE J. Solid-State Circuits*, vol. 38, no. 8, pp. 1353–1363, Aug. 2003.

- [63] C. Mead, Analog VLSI and Neural Systems. Boston, MA: Addison Wesley, 1989.

- [64] A. G. Andreou, "On physical models of neural computation and their analog VLSI implementation," in Workshop on Physics and Computation, IEEE Computer Society, Dallas, Nov. 1994, pp. 255–264.

- [65] E. Vittoz and X. Arreguit, "Linear networks based on transistors," *Electron. Lett.*, vol. 29, pp. 297–299, Feb. 1993.

- [66] A. G. Andreou and K. Boahen, "Translinear circuits in subthreshold CMOS," in *Analog Integrated Circuits and Signal Processing*. : Kluwer, Apr. 1996, pp. 141–166, no. 9.

- [67] S.-C. Liu, J. Kramer, G. Indiveri, T. Delbrück, and R. Douglas, Analog VLSI: Circuits and Principles. Cambridge, MA: The MIT Press, 2002

- [68] T. Serrano-Gotarredona and B. Linares-Barranco, "CMOS mismatch model valid from weak to strong inversion," in *Proc. 2003 Eur. Solid-State Circuits Conf. (ESSCIRC'03)*, Sep. 2003, pp. 627–630.

- [69] K. Bult and J. G. M. Geelen, "An inherently linear and compact MOST-only current division technique," *IEEE J. Solid-State Circuits*, vol. 27, pp. 1730–1735, Dec. 1992.

- [70] C. C. Enz and E. A. Vittoz, "CMOS low-power analog circuit design," in *Proc. Int. Symp. Circuits Syst. (ISCAS'96)*, 1996, pp. 79–132, Tutorials, ch. 1.2.

- [71] A. Moini, Vision Chips. Norwell, MA: Kluwer, 1999.

- [72] F. Gomez-Rodriguez, R. Paz-Vicente, A. Linares-Barranco, M. Rivas, L. Miro, S. Vicente, G. Jiménez, and A. Civit, "AER tools for communications and debugging," in *Proc. IEEE Int. Symp. Circuits Syst.* (ISCAS 2006), Kos, Greece, May 2006, pp. 3253–3256.

- [73] A. Linares-Barranco, G. Jimenez-Moreno, B. Linares-Barranco, and A. Civit-Ballcels, "On algorithmic rate-coded AER generation," *IEEE Trans. Neural Netw.*, vol. 17, no. 3, pp. 771–788, May 2006.

- [74] R. Serrano-Gotarredona, M. Oster, P. Lichtsteiner, A. Linares-Barranco, R. Paz-Vicente, F. Gömez-Rodríguez, H. Kolle Riis, T. Delbrück, S. C. Liu, S. Zahnd, A. M. Whatley, R. Douglas, P. Häfliger, G. Jimenez-Moreno, A. Civit, T. Serrano-Gotarredona, A. Acosta-Jiménez, and B. Linares-Barranco, "AER building blocks for multi-layers multi-chips neuromorphic vision systems," in Advances in Neural Information Processing Systems, Y. Weiss, B. Schölkopf, and J. Platt, Eds. Cambridge, MA: MIT Press, 2006, vol. 18, pp. 1217–1224 [Online]. Available: http://www.books.nips.cc/papers/files/nips18/NIPS2005\_0268.pdf, (NIPS'06)

Jesús Costas-Santos received the B.S. degree in telecommunications engineering from the University of Seville, Seville, Spain, in 2003. He is working toward the Ph.D. degree in electrical engineering at the Instituto de Microelectrónica de Sevilla (IMSE-CNM-CSIC), Seville, Spain.

Since January 2005, he has been a High School Professor at the Spanish Ministry of Education and Science at different cities in Spain. His research interests include analog and mixed-signal VLSI circuit design applied to vision processing systems.

Mr. Costas-Santos was the recipient of a scholarship from the Spanish Research Council (CSIC) for his doctoral work, while he was at IMSE.

Teresa Serrano-Gotarredona was born in Cordoba, Spain, in 1969. She received the B.S. degree in electronic physics and the Ph.D. degree in VLSI neural categorizers from the from the University of Seville, Sevilla, Spain, in 1992, and 1996, respectively, and the M.S. degree in electrical and computer engineering from the Johns Hopkins University, Baltimore, MD, in 1997.

She was an Assistant Professor in the Electronics and Electromagnetism Department, University of Seville from September 1998 until September 2000.

Since September 2000, she is a Tenured Scientist at the National Microelectronics Center, (IMSE-CNM-CSIC), Sevilla, Spain. Since January 2006, she is also a part-time Professor at the University of Seville. Her research interests include analog circuit design of linear and nonlinear circuits, VLSI neural-based pattern recognition systems, VLSI implementations of neural computing and sensory systems, transistor parameters mismatch characterization, address-event-representation VLSI, RF circuit design, and real-time vision processing chips. She is coauthor of the book *Adaptive Resonance Theory Microchips* (Kluwer, 1998)

Dr. Serrano-Gotarredona was corecipient of the 1997 IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS Best Paper Award for the paper "A Real-Time Clustering Microchip Neural Engine." She has also been co-recipient of the 2000 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS Darlington Award for the paper "A General Translinear Principle for Subthreshold MOS Transistors." She is presently Secretary-Elect of the IEEE Circuits and Systems (CAS) Society Sensory Systems Technical Committee.

**Rafael Serrano-Gotarredona** received the B.S. degree in telecommunications engineering from the University of Seville, Sevilla, Spain, in 2002. He is currently working toward the Ph.D. degree (part time) at the Instituto de Microelectrónica de Sevilla (IMSE-CNM-CSIC).

During June and July of 2006, he was with the Department of Electrical and Computer Engineering, Texas A&M University, College Station, as a Visiting Scholar. He has also visited the Neuroinformatics Institute of ETH, Switzerland, in the context of the

European-funded research project CAVIAR. He joined NXP Semiconductors, Graz, Austria, in March 2007, after completing his Ph.D. dissertation in February 2007. His research interests include analog and mixed-signal VLSI circuit design applied to vision processing systems and high-speed LVDS chip communications.

Mr. Serrano-Gotarredona was the recipient of a scholarship from the Spanish Ministry of Education and Science, for his doctoral research.

Bernabé Linares-Barranco received the B.S. degree in electronic physics, the M.S. degree in microelectronics, and the first Ph.D. degree in high-frequency OTA-C oscillator design from the University of Seville, Sevilla, Spain, in 1986, 1987, and 1990, respectively, and the second Ph.D. degree in analog neural network design from Texas A&M University, College Station, in 1991.