## Flexible ΣΔ Modulators for Multi-Standard Wireless Transceivers: Novel Architectures and Circuit Solutions

Alonso Morgado, Rocío del Río and José M. de la Rosa

Instituto de Microelectrónica de Sevilla, IMSE-CNM, (CSIC and Universidad de Sevilla)

C/Américo Vespucio s/n, 41092-Sevilla SPAIN

Phone: +349544666666, Fax: +34954466600, E-mail: {alonso|rocio|jrosa}@imse-cnm.csic.es

The increasing number of wireless standards and applications demands for transceivers capable to handle different sets of specifications, signal conditions and battery status. The trend is towards a maximum hardware reuse, by making as many transceiver building blocks as possible, digitally programmable, reconfigurable and suitable to be integrated in mainstream nanometer CMOS technologies [1]. One of the most challenging building blocks in such multi-standard transceivers is the Analog-to-Digital Converter (ADC), because of the varying sampling rates and resolutions required to digitize the wide range of signals corresponding to each individual operation mode [2]. The majority of reported multi-standard ADCs uses the  $\Sigma\Delta$ Modulation ( $\Sigma\Delta M$ ) technique, being the most commonly applied reconfiguration strategy just changing the OverSampling Ratio (OSR) according to the operation standard [3]. However, the increasing demand for high data rates in new standards restricts oversampling to low values, what forces to increase the noise-shaping filter order and/or the number of bits of the internal quantizers.

This work contributes to this topic and presents two novel  $\Sigma\Delta$ Ms capable to reconfigure themselves with optimized power consumption. The first chip —designed and fabricated in a 0.13µm CMOS technology— is intended to cope with the main requirements of cellular and short-distance communication standards [3], while the second  $\Sigma\Delta$ M —designed in a 90-nm CMOS technology— faces the paradigm of 4G receivers, defined as the inclusion of wireless communication standards (such as WiMax and WLAN) together with the cellular ones [4].

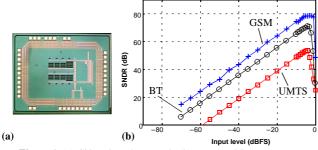

Fig. 1(a) shows the microphotograph of the first chip. This prototype adjusts the biasing of the embedded folded-cascode amplifiers, the sampling frequency (fs), the filtering order and the resolution of the last-stage quantizer to get the required performance with adaptive power consumption. These reconfiguration strategies allow this modulator to adapt its performance to the required specifications. This is illustrated in Fig. 1(b) that shows the measured Signal-to-(Noise+Distortion) (SNDR) curves for all operation modes covered by this chip.

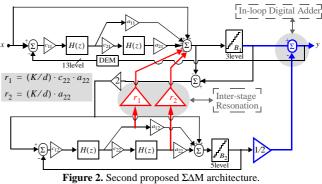

The second design, whose block diagram is shown in Fig. 2, extends the underlying principle of SMASH  $\Sigma\Delta$ Ms to the implementation of global resonation while Unity Signal Transfer Function (USTF) is used in all stages of the modulator [5]. This implies a reduction in the requirements of the amplifiers in terms of DC gain, gain non-linearity and output swing. Besides, the use of adaptive resonation allows to enlarge the resolution when demanded. Moreover, this novel architecture employs a digital adder to implement an inter-stage feed-back path that allows to remove the digital cancellation logic —required in conventional cascade modulators— while the analog adders are used to obtain the USTF at each stage.

Both modulators use reconfigurable folded-cascode amplifiers with adaptive biasing. Indeed, as a result of the architectural-level strategies implemented in the second design, their embedded opamps demand very low DC gain —less than 35dB for all amplifiers. Another appealing feature of

Figure 1. (a) Chip microphotograph, (b) Measured SNDR curves.

this last modulator architecture is the great reduction in the opamp output swing requirements —with maximum respective swings of 1.2V (reference voltage value for both  $\Sigma\Delta$ Ms) and 0.4V for the first and second design—due to the use of USTF in all stages.

At the time of writing this abstract, the first design has been fabricated and measured while the second modulator is not fully electrically implemented yet. However, all its building blocks are already designed at transistor level. In fact, power estimations of all these blocks are done based on their electrical designs while taking into account their corresponding loads and operation frequencies.

Table I summarizes the performance of both designs, considering experimental measurements for the first one and time-domain behavioral simulations (including main non-ideal effects extracted from electrical simulations) for the second one. Both circuits comply with the specifications of the targeted wireless standards, and feature a competitive performance with cutting-edge state-of-the-art reconfigurable  $\Sigma\Delta Ms$  [3], showing the benefits of using the proposed reconfiguration strategies at both architectural- and circuital-level.

## REFERENCES

- M. Brandolini et al.: "Toward Multi-standard Mobile Terminals Fully Integrated Receivers Requirements and Architectures". *IEEE Transactions on Microwave Theory and Techniques*, Vol. 53, pp. 1026-1038, March 2005.

K. Gulati and H.S. Lee: "A Low-Power Reconfigurable Analog-to-Digital

- [2] K. Gulati and H.S. Lee: "A Low-Power Reconfigurable Analog-to-Digital Converter". *IEEE J. of Solid-State Circuits*, Vol. 36, pp. 1900-1910, Dec. 2001.

- [3] A. Morgado *et al.*: "A Triple-Mode Reconfigurable Sigma-Delta Modulator for Multi-Standard Wireless Applications". *Proc. of DATE*, pp. 862-867, 2008.

- [4] V. Gazis et al.: "Toward a Generic Always Best Connected Capability in Integrated WLAN/UMTS Cellular Mobile Networks (and Beyond)". *IEEE Wireless Communications*, pp. 20-29, June 2005.

[5] A Morgado et al.: "A Flexible Resonation-based Cascade ΣΔ Modulator

- [5] A Morgado et al.: "A Flexible Resonation-based Cascade ΣΔ Modulator with Simplified Cancellation Logic." *Proc. of ICECS*, 2009. Accepted for publication.

TABLE I. PERFORMANCE SUMMARY.

| Standard | OSR | fs<br>(MHz)       | Architecture   | Peak<br>SNDR<br>(dB) | DR<br>(dB) | Power<br>Cons.<br>(mW) | Process       | Core<br>Area       | Supply<br>Voltage |

|----------|-----|-------------------|----------------|----------------------|------------|------------------------|---------------|--------------------|-------------------|

|          |     |                   | First prototy  | vpe (Mea             | isured     | results)               |               |                    |                   |

| GSM      | 100 | 40                | 2-1            | 77.8                 | 82.3       | 25.2                   | 130nm<br>CMOS | 1.4mm <sup>2</sup> | 3.3V              |

| BT       | 20  |                   | 2-1-1 (2b)     | 71.3                 | 75.9       | 25.0                   |               |                    |                   |

| UMTS     | 10  | 80                | 2-1-1 (20)     | 53.7                 | 58.7       | 44.5                   |               |                    |                   |

|          | 5   | Second J          | prototype (Est | imated s             | imulat     | tion-base              | d results     | )                  |                   |

| GSM      | 200 | 40<br>80          | 2              | 80.2                 | 90.0       | 4.1                    | 90nm<br>CMOS  | 0.7mm <sup>2</sup> | 1.2V              |

| BT       | 80  |                   |                | 75.6                 | 79.3       | 5.8                    |               |                    |                   |

| UMTS     | 40  | 160<br>240<br>320 |                | 65                   | 69.4       | 8.7                    |               |                    |                   |

| DVB-H    | 20  |                   | 2-2            | 70.0                 | 74.3       | 14.9                   |               |                    |                   |

| WiMax    | 12  |                   |                | 63                   | 67.5       | 20.5                   |               |                    |                   |

| WLANa    | 16  |                   |                | 68                   | 72.0       | 21.5                   |               |                    |                   |

| WLANn    | 8   |                   | 2-2<br>K=0.5   | 62.1                 | 65.1       | 23.5                   |               |                    |                   |