# Flexible CMOS Low-Noise Amplifiers for Beyond-3G Wireless Hand-Held Devices

Edwin C. Becerra-Alvarez (1), Federico Sandoval-Ibarra(2) and José M. de la Rosa(1)\*

(1) Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC/Universidad de Sevilla) C/ Américo Vespucio s/n, 41092-Sevilla, SPAIN

(2) CINVESTAV 0 Unidad Guadalajara Av. Científica No. 1145, 45010, Col. El Bajío, Zapopan, Jalisco, MEXICO

#### ABSTRACT

This paper explores the use of reconfigurable Low-Noise Amplifiers (LNAs) for the implementation of CMOS Radio Frequency (RF) front-ends in the next generation of multi-standard wireless transceivers. Main circuit strategies reported so far for multi-standard LNAs are reviewed and a novel flexible LNA intended for Beyond-3G RF hand-held terminals is presented. The proposed LNA circuit consists of a two-stage topology that combines inductive-source degeneration with PMOS-varactor based tuning network and a programmable load to adapt its performance to different standard specifications without penalizing the circuit noise and with a reduced number of inductors as compared to previous reported reconfigurable LNAs. The circuit has been designed in a 90-nm CMOS technology to cope with the requirements of the GSM, WCDMA, Bluetooth and WLAN (IEEE 802.11b-g) standards. Simulation results, including technology and packaging parasitics, demonstrate correct operation of the circuit for all the standards under study, featuring NF<2.8dB,  $S_{21}$ >13.3dB and IIP3>10.9dBm, over a 1.85GHz-2.4GHz band, with an adaptive power consumption between 17mW and 22mW from a 1-V supply voltage. Preliminary experimental measurements are included, showing a correct reconfiguration operation within the operation band.

Keywords: Low-Noise Amplifiers, reconfigurable/adaptive RF CMOS circuits, multi-standard wireless telecom.

## 1. INTRODUCTION

Beyond-3G (B3G) hand-held terminals will require low-power *multi-standard chipsets*, capable to operate over a variety of standard specifications including different frequency bands, access techniques, number of channels, modulation schemes, data rates, as well as handling different signal conditions, battery status, while optimizing their power dissipation (portability) and silicon area (cost) <sup>1-4</sup>.

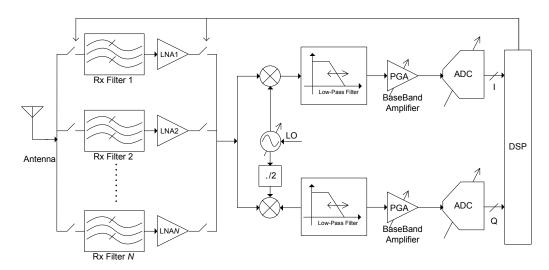

The majority of reported multi-standard Radio-Frequency (RF) receivers use a single down-conversion scheme as conceptually depicted in Fig.1<sup>5-6</sup>. This architecture eliminates the need for both Intermediate-Frequency (IF) and Image Reject (IR) filtering and requires only a single oscillator and mixer, what makes it very suited for multi-standard applications because it increases the level of integration and facilitates hardware sharing. Moreover, the most common situation is that, in order to cope with the requirements of the different standards, separate (switchable) RF front-end paths (usually one per standard) are used whereas a single, digitally-programmed baseband section 0from the mixer to the Analog-to-Digital Converter (ADC) 0 is shared by all standards<sup>5</sup>.

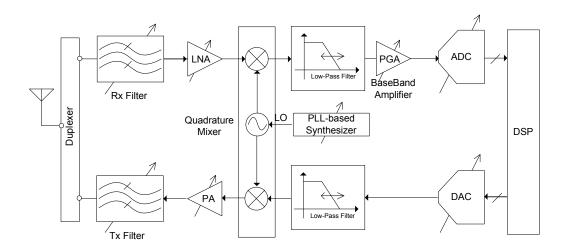

However, the trend is towards a maximum hardware reuse, by making as many transceiver building blocks as possible digitally programmable and reconfigurable<sup>6</sup>. Indeed, an ideal optimized multi-standard transceiver should be as conceptually depicted in Fig.2. Moreover, nanometer CMOS processes are expected to be the base technologies to develop this \* jrosa@imse.cnm.es; phone +34 954466666; fax +34 954466660; www.imse.cnm.es

VLSI Circuits and Systems IV, edited by Teresa Riesgo, Eduardo de la Torre, Leandro Soares Indrusiak, Proc. of SPIE Vol. 7363, 73630Q ⋅ © 2009 SPIE ⋅ CCC code: 0277-786X/09/\$18 ⋅ doi: 10.1117/12.820911

Proc. of SPIE Vol. 7363 73630Q-1

new generation of RF transceivers, assuring mass production at low cost through increased integration levels and extensive use of digital signal processing. Although there has been some approaches to implement an architecture similar to that in Fig.2<sup>7,8</sup>, the integration of increasingly complex RF parts imposes a number of challenges and trade-offs that makes their design a key issue to guarantee the quality of service. Consequently, we are still far from applying this scheme to B3G wireless systems<sup>1</sup>.

One of the most challenging circuits to implement the scheme in Fig.2 is the Low-Noise Amplifier (LNA). The design of this block is specially critical due to its position at the receiver front-end, having to simultaneously match the antenna and to amplify weak input signals with minimum noise contribution, high linearity and isolation from the rest of the receiver chain. This problem is aggravated in the case of multi-standard applications, in which LNAs must operate over different frequency ranges, whereas keeping reduced number of passives to increase the integration <sup>5-8</sup>. In order to solve the above-mentioned problems, several multi-standard LNAs have been reported in literature <sup>9-16</sup>. Most of them increase the number of integrated passive elements (basically capacitors and inductors) as compared to their mono-standard counterparts. These elements contribute significantly to the whole chip area and hence, do not offer a clear advantage with respect to Fig.1.

Figure 1. Commonly used multi-standard RF receiver architecture.

Figure 2. Ideal multi-standard RF transceiver.

This paper contributes to this topic and presents the design and implementation of a flexible CMOS LNA for multi-standard transceivers. The circuit adapts its performance to the requirements of four standards (GSM, WCDMA, Bluetooth and WLAN) without increasing the number of inductors as compared to the mono-standard case. It employs a two-stage topology to separately control the input impedance and the signal gain. A PMOS-varactor tuning network is used in both stages in order to make the resonance frequency programmable without penalizing the LNA noise performance. SpectreRF simulations considering technology parasitics and chip-package effects are shown to verify the operation of the circuit.

# 2. BACKGROUND ON RECONFIGURABLE LOW-NOISE AMPLIFIERS

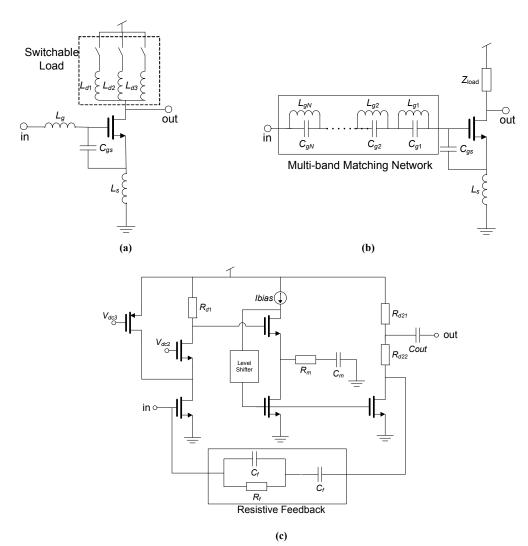

Most reported multi-standard CMOS LNAs are based on the use of a switchable passive network, as shown in Fig.3(a), to select the resonance frequency, thus preserving immunity to out-of-band interferers, although only one signal band is received at one time <sup>10-12</sup>. Besides, the use of switches forces a discrete frequency selection and introduces parasitic switch-on resistances and capacitances, with the subsequent trade-off between noise and speed. Thus, if a low switch-on resistance is used, the size of transistors implementing the switch must be enlarged, thus increasing the associated parasitic capacitances, whereas small switches lead to high switch-on resistances, thus penalizing the Noise Figure (NF).

Figure 3. Different circuit techniques to implement multi-standard LNAs. (a) Switchable resonant tank <sup>11</sup>. (b) Multi-band matching network <sup>15</sup>. (c) Wideband amplification based on resistive feedback <sup>16</sup>.

The above limitations can be partially solved by using concurrent multi-band LNAs <sup>9,15</sup>, as illustrated in Fig.3(b), which allows a simultaneous reception of multiple signal bands without using switches. However, the spurs in one band may corrupt signals in other band due to the LNA non-linear operation.

A common issue in the multi-standard LNAs shown in Fig.3(a) and Fig.3(b) is the need of additional passive components for the input and output matching networks. This fact has motivated exploring other techniques, like the use of wideband resistive-feedback topologies <sup>14</sup> 0 shown in Fig.3(c) 0 that can achieve good performance in a wide signal bandwidth without using inductors <sup>16</sup>, usually at the price of increasing noise.

## 3. PROPOSED ADAPTIVE LNA CIRCUIT

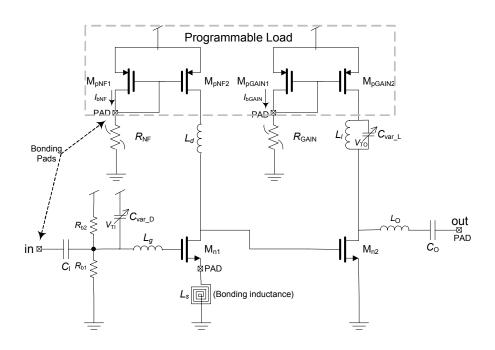

Fig.4 shows the complete schematic of the proposed reconfigurable LNA. It consists of a two-stage topology with separate tuning networks. The input stage, formed by transistors  $M_{n1}$  and  $M_{pNF1,2}$ , uses an inductively degenerated commonsource structure to provide a specified real part for the input impedance and signal gain at a given frequency. The output stage of the LNA, made up of transistors  $M_{n2}$  and  $M_{pGAIN1,2}$ , provides higher gain without significantly degrading the noise performance.

Assuming that inductors  $L_g$  and  $L_s$  are ideal, and neglecting the effect of  $R_{b1,2}$ , the input impedance of the LNA is approximately given by:

$$Z_{\text{in}} \subset \frac{C_{\text{I}} + C_{\text{gsn1}}}{sC_{\text{I}}C_{\text{gsn1}}} + s (L_g + L_s) + \frac{g_{mn1}L_s}{C_{\text{gsn1}}} \left[ 1 - s \frac{g_{mn1}L_sC_{\text{var}\_D}}{C_{\text{gsn1}}} \right]$$

(1)

where  $g_{mn1}$  and  $C_{gsn1}$  are the small-signal transconductance and gate-source capacitance of  $M_{n1}$ . The real part of  $Z_{in}$ , given by  $(g_{mn1}L_s)/C_{gsn1}$ , is usually chosen to be equal to the RF source resistance,  $R_s$ , in the band of interest. In our case, as the LNA is fully integrated as a stand-alone circuit, a termination of  $50\,\mathrm{Z}$  is needed at both the input and the output terminals, within the whole band. For that purpose, in addition to the mentioned input impedance matching network, an output matching network, formed by  $L_0$  and  $C_0$ , is included in the circuit.

Figure 4. Schematic of the proposed adaptive LNA.

The tuning mechanism of the LNA is achieved by varying the resonance frequencies of the passive input- and output-tuning networks, respectively given by:

$$z_{\text{in}} C \frac{1}{\sqrt{C_{\text{gsn1}} [L_g + L_s - [(g_{mn1}L_s)/C_{\text{gsn1}}]^2 C_{\text{var}} D]}}; z_{\text{out}} C \frac{1}{\sqrt{L_l C_{\text{var}} L}}$$

(2)

where  $C_{\rm var\_D}$  and  $C_{\rm var\_L}$  are implemented by accumulation PMOS varactors. The capacitance of these varactors, controlled by voltages  $V_{\rm TI}$  and  $V_{\rm TO}$ , can be varied from 20fF to 10pF, providing a resonance frequency of up to 20GHz.

Programmable biasing is used to separately control the real part of the load of both stages, implemented by transistors  $M_{pNF2}$  and  $M_{pGAIN2}$ . In this way, NF and the voltage gain can be individually controlled by diode-connected transistors  $M_{pNF1}$  and  $M_{pGAIN1}$ , respectively. Thus, the drain current of these transistors,  $I_{bNF}$  and  $I_{bGAIN}$ , are adapted to properly biasing the gate of  $M_{pNF2}$  and  $M_{pGAIN2}$ , in order to achieve the required specifications for each standard with reduced power dissipation. In this prototype,  $I_{bNF}$  and  $I_{bGAIN}$  are generated by external off-chip variable resistors,  $R_{NF}$  and  $R_{GAIN}$  (see Fig.4) in order to probe the concept. However, in a practical application, an on-chip implementation should be used.

# 4. CIRCUIT DESIGN PROCEDURE AND SIZING

The proposed reconfigurable LNA has been designed to fulfil the requirements of a multi-standard wireless direct-conversion receiver for the following standards: GSM, WCDMA, Bluetooth (BT) and WLAN. These requirements were extracted from a number of previously reported RF receivers <sup>13,17,18</sup>. In order to cope with the different sets of specifications, the following design procedure was followed:

- (1) Passive elements of the input matching network,  $C_{\rm I}$ ,  $L_g$  and  $L_s$ , are derived from (1) in order to get the required input impedance, i.e  $Z_{\rm in}=R_s=50{\rm Z}$ .

- (2) Transistors M<sub>n1</sub> and M<sub>pNF1,2</sub>, and R<sub>NF</sub> are sized in order to achieve the minimum value required for NF in the signal bandwidth, whereas trying to achieve the maximum voltage gain possible with the least power dissipation through proper adjustment of R<sub>NF</sub>. At this design step, the values of R<sub>b1</sub> and R<sub>b2</sub> are set to provide the operating point required at the gate of M<sub>n1</sub>, considering both linearity and noise requirement.

- (3) Transistors  $M_{n2}$  and  $M_{pGAIN1,2}$  and resistor  $R_{GAIN}$  are sized in order to get the maximum voltage gain.

- (4)  $L_{\rm O}$  and  $C_{\rm O}$  are calculated to get an output impedance matched to  $Z_{\rm out}$ = 50 z .

- (5)  $L_g$ ,  $L_l$ ,  $C_{\text{var}\_D}$  and  $C_{\text{var}\_L}$  are computed from (2) to get the required LNA tuning frequencies for each standard

- (6) Technology parasitics are considered in an interactive electrical simulation process to re-fine the sizing and biasing obtained in previous steps.

The outcome of the design procedure described above is the sizing and biasing of the LNA, summarized in Table 1. The performance of the circuit is adapted to the different standards specifications by varying the values of  $R_{NF}$  and  $R_{GAIN}$ . These values, together with varactor capacitances, are shown in Table 1.

|                     | 8           |                                      |                   |  |  |  |  |  |

|---------------------|-------------|--------------------------------------|-------------------|--|--|--|--|--|

| Transistors         | W/L (μm/μm) | Capacitors (pF)                      | Inductors (nH)    |  |  |  |  |  |

| M <sub>n1</sub>     | 220/0.3     | $C_{\rm I}$ = 5.7; $C_{\rm O}$ =13.5 | $L_d = 12.1$      |  |  |  |  |  |

| M <sub>n2</sub>     | 124/0.3     | $C_{\text{var}\_D} = (0.6, 1.4)$     | $L_g = 5.9$       |  |  |  |  |  |

| M <sub>pNF1</sub>   | 1/0.1       | $C_{\text{var}\_L} = (0.9, 1.5)$     | $L_s = 0.1$       |  |  |  |  |  |

| M <sub>pNF2</sub>   | 124/0.1     | Resistors (kZ)                       | $L_{l}$ = 4.7     |  |  |  |  |  |

| M <sub>pGAIN1</sub> | 1/0.1       | $R_{\rm NF} = 0.5-1$                 | $L_{\rm O} = 7.1$ |  |  |  |  |  |

| $M_{pGAIN2}$        | 124/0.1     | $R_{\rm GAIN} = 0.5-1$               |                   |  |  |  |  |  |

Table 1: LNA Sizing

## 5. LAYOUT, PACKAGING AND SIMULATION RESULTS

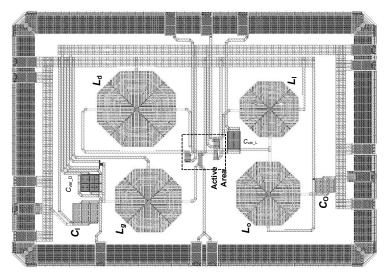

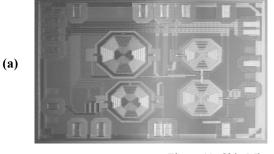

The LNA has been designed and implemented using a 90-nm CMOS technology with a single 1-V supply voltage. Fig.5 shows the layout of the chip highlighting their main parts. Integrated inductors have a patterned ground shield and octagonal shape. Input/output capacitors are implemented by M-O-M structures, which are based on the combination of stacked and finger metal-metal capacitors. All pads are ElectroStatic Discharged (ESD) protected. The die area, including pads, is 1.8 mm², with the core occupying 1.0 mm². As usual, a significant portion of this area is used by integrated inductors. However, in this circuit, and contrary to most reported multi-standard LNAs, the number of inductors is not increased as compared to the mono-standard case, with the subsequent area saving.

The circuit has been extensively verified using CADENCE SpectreRF. Technology parasitics and package effects were considered in the simulations. For that purpose, the circuit in Fig.6 was used. This circuit includes the package and the external components to be included in the PCB. A 4mmx4mm 12-pin QFN plastic package has been used. This package has been modelled using CADENCE PKG tool in order to take into account their associated parasitics during the design process.

Figure 5. Layout of the LNA.

Figure 6. PCB conceptual schematic with QFN package and equivalent circuit.

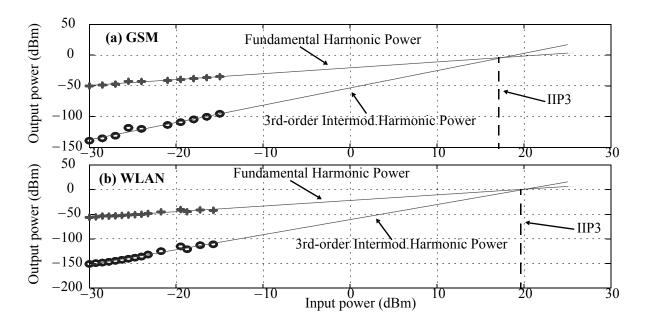

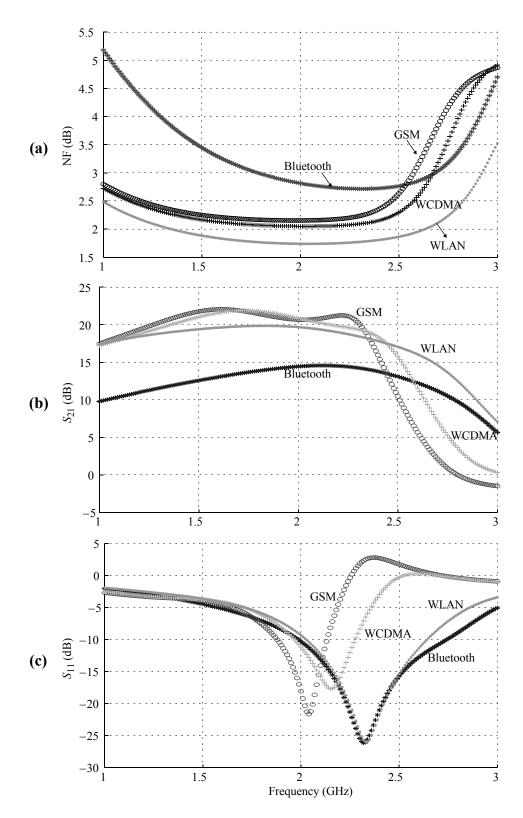

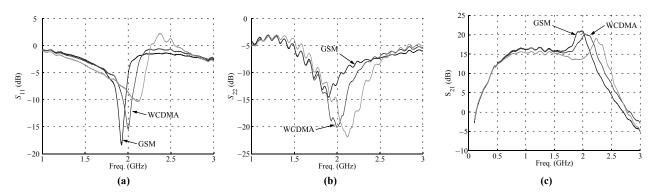

Fig.7(a) represents NF vs. input frequency for all the standards under study. The overall minimum value of NF is 1.8dB, obtained at 2.4GHz, which corresponds to the WLAN operation mode. Fig.7(b) and Fig.7(c) show respectively the forward-gain ( $S_{21}$ ) and the input reflection coefficient ( $S_{11}$ ). The minimum value of  $S_{21}$  within the band of interest is above 13dB, corresponding to Bluetooth, whereas  $S_{11}$  and  $S_{22}$  are below 08.5dB for all standards. The linearity of the LNA has been also taken into account in the design process. The minimum and maximum values achieved of the 3<sup>rd</sup>-order intermodulation intercept point, IIP3, are 10.9dBm and 19dBm, respectively for Bluetooth and WLAN, as illustrated in Fig.8.

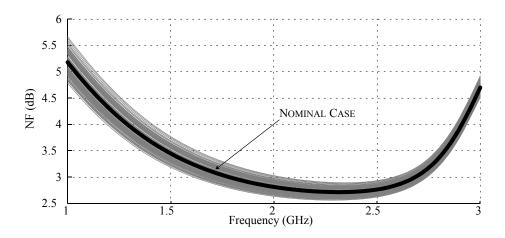

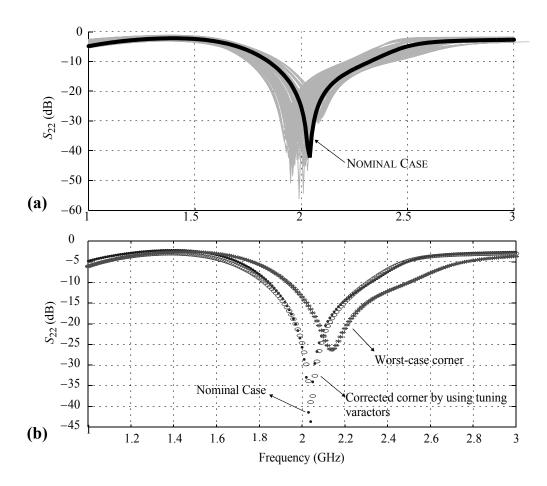

In addition to the nominal simulations describe above, MonteCarlo and technology corners analyses were carried out. As an illustration, Fig.9 shows a 100-run MonteCarlo simulation of NF for Bluetooth, showing a worst-case value of 2.9dB 0 in agreement with required specifications. Fig.10(a) shows the variations of  $S_{22}$  due to technology corners for WCDMA. Note that a worst-case value of 010.8dB is obtained, which is 3.9dB worse than the nominal case. This can be compensated in practice by tuning varactors using  $V_{TI}$  and  $V_{TO}$ , as illustrated in Fig.10(b).

Figure 8. IIP3 for (a) GSM and (b) WLAN.

Figure 9. MonteCarlo simulation of NF for Bluetooth standard.

Figure 7. Simulation of NF and S-parameters. (a) NF. (b)  $S_{21}$ . (c)  $S_{11}$ .

Figure 10. (a) Corner analysis of  $S_{22}$  for WCDMA. (b) Worst-case compensation by tuning.

Finally, Table 2 sums up the simulated performance of the LNA by showing the worst-case values of the different figures for each standard. This performance is compared with previous reported multi-standard CMOS LNAs<sup>††</sup>, by using the following Figures Of Merit (FOM) <sup>19</sup>:

$$FOM_{1} = \frac{Gain}{(NF-1) \circ Power [mW]}; FOM_{2} = \frac{Gain \circ IIP3 [mW] \circ f_{c} [GHz]}{(NF-1) \circ Power [mW]}$$

(3)

where  $f_c$  is the operating frequency of the LNA. Note that the circuit in this paper compares favourably to previous LNAs while covering a larger number of standards. Indeed, a very high value of FOM<sub>2</sub> is obtained as a consequence of the extremely high IIP3 achieved in the simulations (see Fig.8). In practice, measured IIP3 would be degraded as compared to simulations, giving rise to more realistic values of FOM<sub>2</sub>.

..

<sup>††</sup> Although some LNAs in Table Table 2: (including the one in this paper) do not report experimental results, they are included in the comparison study for the sake of completeness. Those ones marked with \* correspond to ICs showing experimental performance.

## 6. PRELIMINARY EXPERIMENTAL RESULTS

At the time of writing this paper, the prototype IC samples have been received and the test has been started. Fig.11(a) shows a chip microphotograph showing the main parts, namely integrated inductors, M-O-M capacitors and PADs. The chip is being tested using a PCB shown in Fig.11(b), that includes the necessary filtering for bias and power supplies as well as decoupling strategies and proper impedance termination to avoid signal reflections.

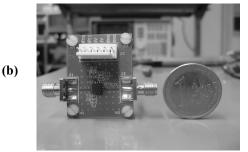

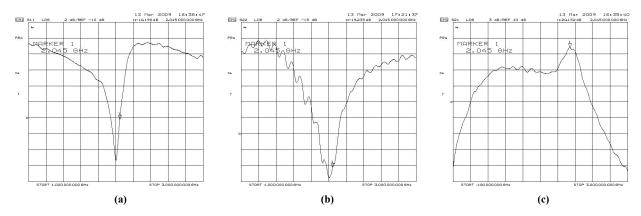

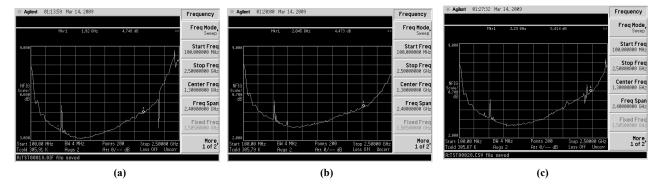

As an illustration, Fig.12 shows the measured S-parameters for the WCDMA standard, showing that  $S_{11}$  and  $S_{22}$  are below 015dB whereas the forward gain, $S_{21}$ , is above 20dB, measured at ~2GHz. The effect of reconfiguration is shown in Fig.13 that depicts how measured S-parameters can be experimentally tuned for GSM, WCDMA and WLAN standards, showing that  $S_{11,22} < 010$ dB and  $S_{21} > 18$ dB for the standards considered.

Finally, NF has been also measured as illustrated in Fig.14. As can be seen, maximum values within the required bands is about 2dB larger than simulated value. This noise increment might be due to the measurement set-up and external noise sources that could be contaminating the chip. For that purpose, a Faraday cage is being fabricated in order to isolate the test chip as much as possible from external noise and interference sources in order to make a more precise measurement of NF.

| Ref.      | Standard        | NF<br>(dB) | S <sub>21</sub> (dB) | IIP3 (dBm) | $f_c$ (GHz) | Power (mW) | FOM <sub>1</sub> | FOM <sub>2</sub> |

|-----------|-----------------|------------|----------------------|------------|-------------|------------|------------------|------------------|

| 10.       | Bluetooth       | 2.2        | 15                   | 3          | 2.4         | 7.2        | 1.2              | 5.7              |

|           | DECT            | 2.3        | 17                   | 0.5        | 1.9         | 14.4       | 0.7              | 1.5              |

|           | WLAN            | 2.3        | 14                   | -1.5       | 2.4         | 50         | 0.1              | 0.01             |

|           | IEEE 802.11 b-g |            |                      |            |             |            |                  |                  |

| 11.       | WLAN            | 4.4        | 13                   | -1.5       | 5.3         | 50         | 0.05             | 0.2              |

|           | IEEE 802.11a    |            |                      |            |             |            |                  |                  |

|           | WiMAX           | 3.2        | 13.9                 | -10        | 3.5         | 50         | 0.09             | 0.03             |

|           | WCDMA           | 3.9        | 23.3                 | -6.3       | 2.1         | 9          | 1.1              | 0.5              |

| 12.       | GSM             | 2.6        | 24.9                 | -21.6      | 0.95        | 9          | 2.4              | 0.02             |

|           | DCS1800         | 5.2        | 28.5                 | -7.5       | 2.1         | 24         | 0.5              | 1                |

| 13.*      | WCDMA           | 5.6        | 23.4                 | 0          | 2.4         | 24         | 0.2              | 0.2              |

|           | WLAN            | 5.8        | 23.4                 | -4.8       | 1.8         | 24         | 0.5              | 0.2              |

|           | GSM             | 4.6        | 18                   | -12.8      | 1.9         | 32.4       | 0.1              | 0.02             |

| 15.*      | WLAN            | 4.4        | 24                   | -15.3      | 2.4         | 32.4       | 0.3              | 0.02             |

|           | Bluetooth       | 4.4        | 24                   | -15.3      | 2.4         | 32.4       | 0.3              | 0.02             |

| 16.*      | 0.3-2 GHz       | 4.5        | 12                   | -16        | 1.15        | 18         | 0.1              | 0.003            |

|           | GSM             | 2.2        | 20.7                 | 17.6       | 1.92        | 21.7       | 0.76             | 83.7             |

| This Work | WCDMA           | 2.1        | 19.9                 | 17.5       | 2.05        |            | 0.7              | 84.3             |

|           | Bluetooth       | 2.8        | 13.3                 | 10.9       | 2.44        | 17.4       | 0.3              | 8.8              |

|           | WLAN            | 1.8        | 17.2                 | 19         | 2.44        | 21.7       | 0.6              | 126.1            |

Table 2: Comparison with Reported Multi-Standard CMOS LNAs

Figure 11. Chip Microphotograph and PCB.

Figure 12. Preliminary measurements of S-parameters for the WCDMA standard configuration. (a)  $S_{11}$ . (b)  $S_{22}$ . (c)  $S_{21}$ .

Figure 13. Preliminary experimental results showing the variation of S-parameters in the proposed reconfigurable LNA. (a)  $S_{11}$ . (b)  $S_{22}$  and (c)  $S_{21}$ .

Figure 14. Preliminary measurements of NF for (a) GSM, (b) WCDMA and (c) WLAN.

## **CONCLUSIONS**

The design and electrical implementation of a multi-standard 90-nm CMOS LNA has been presented. The use of reconfigurable loading and PMOS-varactor based tuning networks allows the amplifier to adapt its performance to the specifications of GSM, WCDMA, Bluetooth and WLAN standards. Simulation results including technology parasitics and packaging effects demonstrate a correct performance, showing a good comparison with previous reported designs. Preliminary experimental results show a correct operation of the circuit, demonstrating that the performance figures can be reconfigured within the desired frequency band.

#### **ACKNOWLEDGMENTS**

This work has been supported by the Spanish Ministry of Science and Education (with support from the European Regional Development Fund) under contract TEC2007-67247-C02-01/MIC, and the Regional Ministry of Innovation, Science and Enterprise under contract TIC-2532.

#### REFERENCES

- 1. V. Gazis et al.: "Toward a Generic Always Best Connected Capability in Integrated WLAN/UMTS Cellular Mobile Networks (and Beyond)". *IEEE Wireless Communications*, pp. 20-29, June 2005.

- 2. X. Li and M. Ismail: Multi-standard CMOS Wireless Receivers: Analysis and Design. Kluwer Academic Publishers, 2002.

- 3. M. Steer: "Beyond 3G." IEEE Microwave Magazine, pp. 76-82, 2007.

- 4. J.M. de la Rosa et al.: "Adaptive CMOS Analog Circuits for 4G Mobile Terminals Review and State-of-the-Art Survey." *Microelectronics Journal*, vol. 40, pp. 156-176, 2009.

- 5. M. Brandolini et al.: "Toward Multi-standard Mobile Terminals 0 Fully Integrated Receivers Requirements and Architectures". *IEEE Trans. On Microwave Theory and Techniques*, pp. 1026-1038, March 2005.

- 6. P. Mak et al.: "Transceiver Architecture Selection: Review, State-of-the-Art Survey and Case Study". *IEEE Circuits and Systems Magazine*, pp. 6-25, Second Quarter 2007.

- 7. H. Darabi et al.: "A Dual-Mode 802.11b/Bluetooth Radio in 0.35 µm CMOS". *Proc. of the IEEE International Solid-State Circuits Conference (ISSCC)*, pp. 86-87, Feb. 2004.

- 8. Y.J. Jung et al.: "A Dual-Mode Direct-Conversion CMOS Transceiver for Bluetooth and 802.11b". *Proc. of the European Solid-State Circuits Conference (ESSCIRC)*, pp. 225-228, Sept. 2003.

- 9. H. Hashemi and A. Hajimiri: "Concurrent Multiband Low-Noise Amplifiers Theory, Design, and Applications." *IEEE Trans. on Microwave Theory and Techniques*, pp. 288-301, January 2002.

- 10. V. Vidojkovic et al.: "Fully-Integrated DECT/Bluetooth Multi-band LNA in 0.18µm CMOS". *Proc. of the 2004 IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 565-568.

- 11. C.S. Wang et al.: "A Multi-Band Multi-Standard RF Front-End For IEEE 802.16a and IEEE 802.11 a/b/g Applications". *Proc. of the 2005 IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 3974-3977.

- 12. Y. Koolivand et al.: "A New Technique for Design CMOS LNA for Multi-Standard Receivers". *Proc. of the 2005 IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 3231-3234.

- 13. A. Liscidini et al.: "A 0.13µm CMOS Front-End, for DCS1800/UMTS/802.11b-g With Multiband Positive Feedback Low-Noise Amplifier". *IEEE J. of Solid-State Circuits*, pp. 981-989, April 2006.

- 14. J. H.C. Zhang and S.S. Taylor: "A 5GHz resistive-Feedback CMOS LNA for Low-Cost Multi-Standard Applications". *Proc. of the 2006 Int. Solid-State Circuits Conference (ISSCC)*, pp. 721-730.

- 15. C.W. Ang et al.: "A Multi-band CMOS Low Noise Amplifier for Multi-Standard Wireless Receivers". *Proc. of the 2007 IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 2802-2805.

- 16. M. Vidojkovic et al.: "A Broadband, Inductorless LNA for Multi-Standard Applications". *Proc. of the 2007 IEEE European Conference on Circuit Theory and Design (ECCTD)*, pp. 260-263.

- 17. J.A.M Jarvinen et al.: "2.4-GHz receiver for sensor applications", *IEEE J. of Solid-State Circuits*, vol. 40, pp.1426-1433, July 2005.

- 18. P. Sivonen et al.: "A 1.2-V RF front-end with on-chip VCO for PCS 1900 direct conversion receiver in 0.13μm CMOS", *IEEE J. of Solid-State Circuits*, vol. 41, pp. 384-394, February 2006.

- 19. D. Linten et al.: "A 5-GHz Fully Integrated ESD-Protected Low-Noise Amplifier in 90-nm RF CMOS". *IEEE J. of Solid-State Circuits*, vol. 40, pp. 1434-1442, July 2005.

Proc. of SPIE Vol. 7363 73630Q-12