This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2017.2737598, IEEE Journal of the Electron Devices Society

# Reducing the Impact of Reverse Currents in Tunnel FET Rectifiers for Energy Harvesting Applications

Juan Núñez and María J. Avedillo

Abstract—RF to DC passive rectifiers can benefit from the superior performance at low voltage of tunnel transistors. They have shown higher power conversion efficiency (*PCE*) at low input power than Si FinFETs counterparts. In this paper, we analyze the limitations of typical TFET rectifier topologies associated with the forward biasing of their intrinsic diode and show that this can occur at relatively weak input signals depending on the specific characteristic of the used tunnel device. We propose a simple modification in the implementation of the rectifiers to overcome this problem. The impact of our proposal is evaluated on the widely used gate cross-coupled topology. The proposed designs exhibit similar peak *PCE* and sensitivity but significantly improve PCE for larger input signal amplitude and larger input power.

*Keywords*— Tunnel transistors, Steep subthreshold slope, Rectifiers, Reverse conduction, Energy harvesting.

## I. INTRODUCTION

The recent advent of Internet of Things (IoT) applications demands portable or remote devices powered by batteries or energy harvesters. CMOS technologies face power density and energy efficiency challenges and they are not able to scale supply voltages to achieve required ultra-low power operation for these applications. Emerging technologies, including emerging transistor devices, circuits, and architectures, provides the opportunity of further power scaling [1].

Tunnel field-effect transistors (TFETs) are one of the most attractive steep subthreshold slope (*SS*) devices currently being investigated as a means of overcoming such limitations of CMOS technology [2]-[4]. A smaller *SS* makes it possible to lower threshold voltage while keeping leakage current under control, facilitating low voltage operation. Many works have addressed the evaluation of these transistors for logic circuit applications, showing power benefits for iso-performance or higher performance at iso-power up to moderate operating frequencies, although opportunity also exists to provide benefits in higher performance domains in power or thermal limited applications [5]-[7]. More recently, other applications domains in addition to logic ones have been identified.

In particular, and relevant to the IoT application field, it has been shown that front-end circuits for energy harvesting can benefit from the superior performance of TFETs at low voltages [8],[9]. High sensitivity RF to DC passive rectifiers exhibiting much higher power conversion efficiency (*PCE*) al low input power than Si FinFETs counterparts (with exactly same topology) have been demonstrated [10]. TFET

Juan Núñez and María J. Avedillo are with the Instituto de Microelectrónica de Sevilla, IMSE-CNM (CSIC/Universidad of Sevilla). Av. Américo Vespucio s/n, 41092, Sevilla, Spain. e-mail: {jnunez/avedillo}@imse-cnm.csic.es.

based rectifiers take advantage of the reduced turn-on voltage of these transistors with respect to Si FinFET to very much improve performance with weaker input signals. In addition, the higher  $I_{ON}$  current exhibited by TFETs at low supply voltages translates into a reduced on-state resistance which contributes to decrease resistive power losses improving PCE. Finally, according also to [10], unidirectional conduction of TFETs has a positive impact on *PCE* through reduced reverse losses. Reverse losses are associated to the symmetric conduction of conventional transistors which conduct under both positive and negative drain to source voltages. However, although P(N) TFETs do not conduct under low positive (negative) drain to source voltages, enough high reversed drain to source voltages produce the forward biasing of their intrinsic *p-i-n* diode which translates in large losses currents. That is, the advantage associated to unidirectional conduction is limited to enough low amplitude input signals (or enough low input power).

In this paper, we analyze in depth the operation limits of TFETs based rectifiers with respect to voltage levels of input signals and input power, and propose tuning the rectifier topology to the specific TFET characteristic to better control reverse currents and thus, extend the voltage/power operation range of TFETs based rectifiers.

The rest of the paper is structured as follows. Section II analyzes a simple 2-transistor (2-T) rectifier topology to illustrate the limitations of TFET rectifiers associated to the forward biasing of the *p-i-n* diode in the TFET devices and introduces the rationale of the proposed modification. Section III evaluates, by means of simulation results, our solution when applied to the more complex and widely used gate cross-coupled topology. Finally, some conclusions are given in Section IV.

## II. ANALYSIS OF TFET BASED RECTIFIER OPERATION

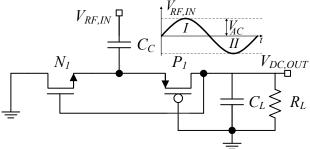

Fig 1 depicts the well-known 2-T passive rectifier [11]. There are two regions of operation. In region I,  $P_1$  transistor is on, while  $N_1$  is off. Current is flowing through  $P_1$  to supply current to the output load. Ideally no current flows through  $N_I$ . In region II,  $P_1$  is off and  $N_1$  is on. Current flows through  $N_1$  to supply  $V_X$ . Ideally no current flows through  $P_I$ . In the stationary state, a DC output voltage is produced ( $V_{DC,OUT}$ ).

Fig 2 compares  $V_{DC,OUT}$  and output power ( $PWR_{OUT}$ ) versus amplitude of input signal ( $V_{AC}$ ) obtained for a Si FinFET and a TFET rectifier. The TFET is a 20nm GaN/InN single gate TFET [12]. Models have been obtained from the nanoHUB website. A predictive 20nm FinFET transistors for HP obtained from the PTM web page is used [13]. The TFET rectifier sizing is similar to that in [10]. Also, the values used for  $C_C$  (100*fF*),  $C_L$  (100*fF*) and  $R_L$  (1M $\Omega$ ) have been taken from that reference. The FinFET transistors have

2168-6734 (c) 2017 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received March 20, 2017, revised May 22, 2017 and June 22, 2017. This work has been funded by Ministerio de Economía y Competitividad del Gobierno de España with support from FEDER (Project TEC2013-40670-P).

been sized identical to the TFET ones. The frequency of the RF input signal is the standard 915MHz.

Advantages for low input amplitudes are evident in Fig 2 in agreement with previous works. It can be observed that, unlike the FinFET, increasing  $V_{AC}$  above 0.3V produces a

Fig 1. Schematic of the 2 transistor passive rectifier proposed in [11].

Fig 2. FinFET/TFET 2-T rectifier. (a)  $V_{DC,OUT}$  vs.  $V_{AC}$ . (b)  $PWR_{OUT}$  vs.  $V_{AC}$ .

Fig 3. (a)  $I_{DS}-V_{DS}$  for *N*-TFET transistor for positive and negative  $V_{GS}$  values. (b) Current through  $P_I$  in 2-T rectifier for two  $V_{AC}$  values.

decrement in both the output voltage and the output power. *PCE* (*PWR<sub>OUT</sub>* / *PWR<sub>IN</sub>*) sharply reduces over this voltage value because decreasing output power occurs for increasing input power (producing a larger amplitude RF signal). This behaviour can be explained on the basis of the *I-V* characteristic of TFET transistor. Fig 3a depicts the *I<sub>DS</sub>*- *V<sub>DS</sub>* curves for the used NTFET for different *V<sub>GS</sub>* values (both positive and negative). Under enough negative *V<sub>DS</sub>*, the forward biased *p-i-n* diode of the TFET conducts a large current. Fig 3b shows currents through *P*<sub>1</sub> for *V<sub>AC</sub>*=0.4V and *V<sub>AC</sub>*=0.6V for the TFET rectifier. Direct (*I<sub>P-TFET</sub>*>0) and reverse (*I<sub>P-TFET</sub>*<0) currents are larger at *V<sub>AC</sub>* =0.6V than at *V<sub>AC</sub>*=0.4V. However, note the larger increment in reverse current with respect to direct one, due to the forward biasing of the diode, leading to the degradation of the rectifier

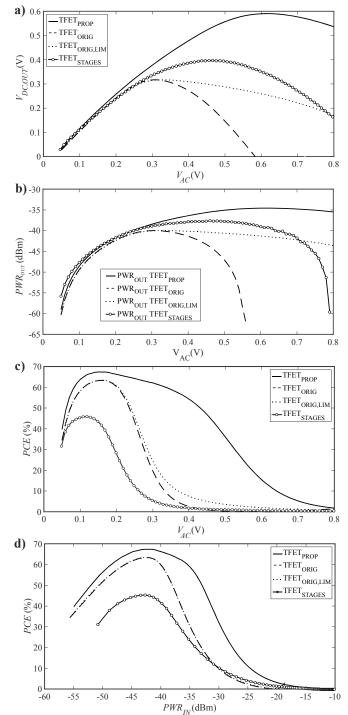

Fig 4. 2-T rectifier performance. (a)  $V_{DC,OUT}$  vs.  $V_{AC}$ . (b)  $PWR_{OUT}$  vs.  $V_{AC}$ . (c) PCE vs.  $V_{AC}$ . (d) PCE vs.  $PWR_{IN}$ .

2168-6734 (c) 2017 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

operation. This behaviour is occurring at an input power around -33dBm. That is, in the sub-micro watt range of applications for which TFET rectifiers have been proposed. In order to overcome this limitation, it is required that transistors are not operated with reversed drain to source bias above the diode's on voltage. This can be achieved if each transistor in the original topology is implemented by the series connection of two transistors. Fig 4 shows output voltage (a) and power (b) versus  $V_{AC}$  and PCE against both  $V_{AC}$  and  $PWR_{IN}$  when this solution is adopted (TFET<sub>PROP</sub>). It can be observed that the unwanted behaviour has been shifted to much larger  $V_{AC}$  and  $PWR_{IN}$  values in the TFET proposed design, improving the PCE performance at larger input voltages or input power. Fig 4 also depicts results for a 2-stage rectifier. Multiple-stages rectifiers are usually employed to obtain higher  $V_{DC,OUT}$ , thus they could be also considered potential candidates to solve the voltage drop phenomenon. A two-stage rectifier in which each stage is sized as the TFET<sub>ORIG</sub> achieves larger  $V_{DC,OUT}$  than any of the alternatives shown in Fig 4a up to  $V_{AC}=0.3V$  ( $V_{DC,OUT}$ =570mV at  $V_{AC}$ =0.3V). However, over this value of input amplitude, it exhibits same behaviour than TFET<sub>ORIG</sub>, and  $V_{DC,OUT}$  sharply falls down, since intrinsic diodes are also forward biased as it occurs in the TFET<sub>ORIG</sub>. An alternative sizing of two stage rectifiers to mitigate the problem has been investigated. We have been able to somehow alleviate the problem (TFET $_{STAGES}$ ). The decrement in output voltage and output power is also evident in this solution, although it shifts to higher input voltages in comparison to TFET<sub>ORIG</sub>.

The voltage drop could be also mitigated by limiting the reverse current. Observe the TFET<sub>ORIG,LIM</sub> curve obtained in Fig 4a. This solution is based on limiting  $V_X$  by decreasing the ratio  $C_C / C_T$ , with  $C_T$  the total transistor capacitance. However, when limiting reverse currents, also direct currents are limited and, thus, small *PCE* improvement is achieved as shown in Fig 4c and Fig 4d.

In [14] a TFET rectifier topology to better control reverse currents is proposed. It is based in forcing the gate to source voltage of the transistors to zero and it has shown to improve *PCE*. Note that the unwanted diode current is independent on  $V_{GS}$ , thus the topology in [14] can still suffer the limitation analysed in this paper. The maximum allowed  $V_{AC}$  (or input power) before it is triggered depends on the specific device. That is, the proposed topology in this paper and the technique in [14] to control  $V_{GS}$  address different targets. *PCE* data shown in Fig 4 could additionally benefit from the application of the  $V_{GS}$  control technique although it is not relevant for the evaluation of the impact of our proposal to avoid the forward biasing of the intrinsic diode.

#### III. EVALUATION OF PROPOSED MODIFICATION

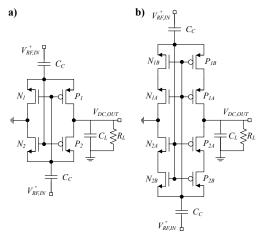

TFET rectifiers based on the gate cross-coupled topology (TFET<sub>ORIG</sub>) depicted in Fig 5a [15] have also shown higher efficiency than those using the two-transistor topology like it occurs in CMOS technologies [10]. The proposed modification (TFET<sub>PROP</sub>, in Fig 5b) is evaluated for this type of rectifier. Designs for  $R_L$ =1MΩ and  $R_L$ =100KΩ have been carried out. In the first case, transistors are sized as in the 2-T design. Results are shown in Fig 6a ( $V_{DC, OUT}$  versus  $V_{AC}$ ) and Fig 6b (*PCE* versus *PWR*<sub>IN</sub>). It can be observed that the limitation identified and analysed in previous section is also exhibited. Note that  $V_{AC}$  is now the amplitude of the difference signal  $V_{RF,IN}^{+}$  -  $V_{RF,IN}^{-}$ . That is, it is

Fig 5. (a) Schematic of the gate cross-coupled rectifier reported in [15]. (b) Schematic of the proposed modification of the gate cross-coupled rectifier.

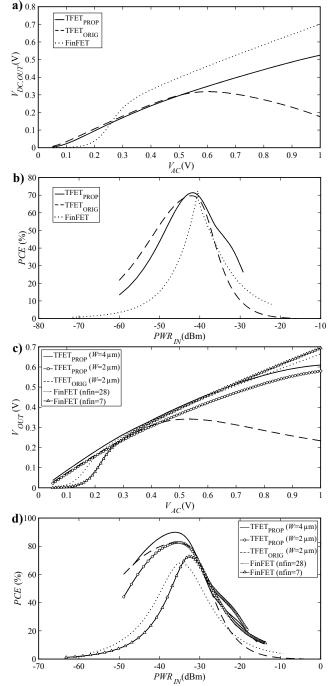

Fig 6. Gate cross coupled rectifier performance for  $R_L=1M\Omega$  (a,b) and  $R_L=100K\Omega$  (c,d).

2168-6734 (c) 2017 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2017.2737598, IEEE Journal of the Electron Devices Society

different from the  $V_{AC}$  in Section II. This explains why the  $V_{DC OUT}$  drops observed for the TFET<sub>ORIG</sub> design are now shifted (towards larger  $V_{AC}$  values) with respect to the 2-T topology. Fig 6b clearly shows the advantages in *PCE* of the proposed design for large input signal amplitudes and input power.

Fig 6c and Fig 6d shows *PCE* results for  $R_L$ =100K $\Omega$ . Larger transistor sizes have now been used to optimize the peak PCE of the original design (W=2µm). Two different sizing of the proposed topologies have been evaluated. First, transistors have been sized to obtain a similar peak PCE to the original design ( $W=2\mu m$ ). Second, the width of the transistors have been multiply by two since two transistors are connected in series ( $W=4\mu m$ ). Both designs exhibit similar sensitivity but improve PCE for larger input signal amplitude and larger input power. The latter design in addition improves also PCE for low input power. For comparison purpose, FinFET rectifiers have been also included. Their performance with the number of fingers has been analysed. Results for two designs are shown. The one optimizing peak PCE (7 fingers) and another one sized similar to the original one (28 fingers). It can be clearly observed the advantages of the tunnel based rectifiers for low input power in agreement with previous works. In addition, the proposed rectifier also exhibits advantages with respect to the FinFET designs for larger input power.

## IV. CONCLUSIONS

Using serial connected transistors in the implementation of the typical rectifier topologies avoids the degradation of their performance produced by the forward biasing of the *p*-*i*-*n* diodes. For the projected tunnel technology we use in this analysis, the above undesired behavior occurs at low input signal amplitudes, thus, it should be taken into account even for applications in the range of micro watts.

#### References

- X. Li, K. Ma, S. George, J. Sampson and V. Narayanan, "Enabling Internet-of-Things: Opportunities brought by emerging devices, circuits, and architectures," 2016 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), Tallinn, 2016, pp. 1-6.

- [2] A. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," *Proceedings of the IEEE*, vol. 98, no. 12, Dec. 2010.

- [3] Nikonov, Dmitri E., and Ian A. Young. "Benchmarking of beyond-CMOS exploratory devices for logic integrated circuits." *IEEE Journal on Exploratory Solid-State Computational Devices and Circuits*, vol. 1 pp. 3-11, Dec. 2015.

- [4] A.M. Ionescu, H. Riel: "Tunnel field-effect transistors as energyefficient electronic switches", *Nature*, no. 479, pp. 329–337, 2011.

- [5] H. Liu, S. Datta, V. Narayanan, "Steep switching tunnel FET: a promise to extend energy efficient roadmap for post-CMOS digital and analog/RF applications", *Symp. on Low Power and Design*, 2013.

- [6] U. E. Avci, D.H. Morris and I.A. Young, "Tunnel Field-Effect Transistors: Prospect and Challenges", *IEEE Journal of the Electron Device Society*, vol. 3, no. 3, pp. 88-95, Jan. 2015.

- [7] J. Núñez, M.J. Avedillo, "J. Núñez and M. J. Avedillo, "Comparison of TFETs and CMOS Using Optimal Design Points for Power–Speed Tradeoffs," in *IEEE Transactions on Nanotechnology*, vol. 16, no. 1, pp. 83-89, Jan. 2017.

- [8] X. Li, U. Dennis Heo, K. Ma, V. Narayanan, H. Liu and S. Datta, "RF-powered systems using steep-slope devices," 2014 IEEE 12th International New Circuits and Systems Conference (NEWCAS), Trois-Rivieres, QC, 2014, pp. 73-76.

- [9] D. Cavalheiro, F. Moll and S. Valtchev, "TFET-Based Power Management Circuit for RF Energy Harvesting," in *IEEE Journal of* the Electron Devices Society, vol. 5, no. 1, pp. 7-17, Jan. 2017.

- [10] H. Liu, X. Li, R. Vaddi, K. Ma, S. Datta and V. Narayanan, "Tunnel FET RF Rectifier Design for Energy Harvesting Applications," in *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 4, no. 4, pp. 400-411, Dec. 2014.

- [11] K. Kotani, et. al, "High Efficiency CMOS Rectifier Circuit with Self-Vth-Cancellation and Power Regulation Functions for UHF RFIDs," in *IEEE Proc. ASSCC '07*, pp. 119–122, Nov. 2007.

- [12] H. Lu T. Ytterdal, A. Seabaugh, "Universal TFET model". nanoHUB. doi:10.4231/D3901ZG9H.

- [13] W. Zhao and Y. Cao, "New generation of predictive technology model for sub-45nm design exploration", *Proc.* 7<sup>th</sup> Int. Symp. Quality Electronic Design, 2006.

- [14] D. Cavalheiro, F. Moll and S. Valtchev, "Insights Into Tunnel FET-Based Charge Pumps and Rectifiers for Energy Harvesting Applications," in *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, vol. 25, no. 3, pp. 988-997, March 2017.

- [15] K. Kotani, et al., "High-efficiency differential-drive CMOS rectifier for UHF RFIDs," *IEEE Journal of Solid State Circuits*, 44(11), pp. 3011-3018, Nov. 2009.