# ESCUELA TÉCNICA SUPERIOR DE INGENIERÍA INFORMÁTICA DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA

#### Tesis Doctoral

Implementación sobre hardware reconfigurable de una arquitectura no determinista, paralela y distribuida de alto rendimiento, basada en modelos de computación con membranas

Realizada por Juan Quirós Carmona Ingeniero en Informática

#### Dirigida por

Dr. Alejandro Millán Calderón

Prof. Contratado Doctor

Dr. Julián Viejo Cortés

Prof. Contratado Doctor Interino

### Resumen

En este documento se presenta el trabajo de tesis doctoral realizado dentro del Programa de Doctorado "Informática Industrial" del Departamento de Tecnología Electrónica de la Universidad de Sevilla. Recoge la investigación centrada en el desarrollo de una implementación en hardware reconfigurable, FPGA, de modelos de computación basados en membranas, también denominados sistemas P. Estos sistemas, de inspiración biológica, son de reciente creación, y tienen aplicaciones directas en procesos de simulación, especialmente de sistemas y procesos biológicos. Se engloban dentro de la computación natural, y se trata de modelos paralelos maximales orientados a máquinas. Este hecho supone un desafío en el desarrollo de implementaciones hardware, ya que es precisa la generación de un diseño diferente para cada problema, incluso para cada instancia. Como consecuencia directa, es necesario el desarrollo de una arquitectura hardware dedicada parametrizada, junto con un desarrollo software, que analice los sistemas de entrada y, en base a sus características, construya un diseño sintetizable dedicado para esa instancia concreta. Además, al ser la disciplina de reciente creación, existen distintos tipos de sistemas P, por lo que es preciso un análisis previo, seguido de una selección, con el propósito de implementar el mayor subconjunto posible de los mismos.

### Agradecimientos

Me gustaría agradecer su ayuda a todas aquellas personas que, de un modo u otro, han contribuido con su granito de arena a la conclusión de este trabajo. Empezando por mis familiares, especialmente mis padres Juan y Mª del Carmen, mi hermana Setefilla, mi novia Gema y mis abuelos. También a todos mis amigos, entre ellos Josemi, Eli, Rocío, Fer y Juanma. No puedo olvidarme de todos mis compañeros del Departamente de Tecnología Electrónica, especialmente a mis directores de tesis, Alejandro y Julián, a Manolo por todo su apoyo, y al resto de mis compañeros del Grupo de Investigación y Desarrollo Digital, ya que sin su ayuda no estaríais leyendo estas líneas. Por último, también dar las gracias al apoyo del Grupo de Computación Natural de la Universidad de Sevilla por su colaboración.

Este trabajo ha sido parcialmente financiado por el Ministerio de Ciencia e Innovación del Gobierno de España a través del proyecto TEC2011-27936 (HI-PERSYS), el proyecto TEC2007-61802 (HIPER), por el Fondo Europeo de Desarrollo Regional (FEDER) y por el Ministerio de Educación, Cultura y Deporte a través de la beca FPU AP2009-3625.

# Índice general

| Re | esum  | en      |                                                         | 1        |

|----|-------|---------|---------------------------------------------------------|----------|

| A  | grade | ecimieı | ntos                                                    | 3        |

| 1. | Intr  | oducci  | ión                                                     | 17       |

|    | 1.1.  | Tecno   | logías de implementación                                | 18       |

|    |       | 1.1.1.  | Sistema de computación secuencial                       | 19       |

|    |       | 1.1.2.  | Sistemas de computación paralelos basados en $software$ | 19       |

|    |       | 1.1.3.  | Sistemas de computación paralelos basados en hardware   | 21       |

|    | 1.2.  | Imple   | mentaciones de modelos de computación con membranas     | 24       |

|    | 1.3.  | Objeti  | ivos y estructura de la tesis                           | 26       |

| I  |       |         | del estado del arte                                     | 29<br>31 |

| ۷. |       | -       | tación con membranas                                    |          |

|    | 2.1.  |         | utación con membranas                                   |          |

|    |       | 2.1.1.  | Definición de un sistema de membranas                   |          |

|    |       | 2.1.2.  | Modelo de computación con membranas. Un ejemplo         |          |

|    | 2.2   | 2.1.3.  | Aplicaciones de los sistemas P                          |          |

|    | 2.2.  |         | mentaciones actuales                                    |          |

|    |       | 2.2.1.  | Requisitos de diseño                                    |          |

|    |       | 2.2.2.  | Trabajos de implementación software                     |          |

|    | 0.2   | 2.2.3.  | Trabajos de implementación hardware                     |          |

|    | 2.3.  | COHCH   | $\operatorname{usiones}$                                | 70       |

6 ÍNDICE GENERAL

| II | $\mathbf{D}$ | $ m Pesarrollo \ de \ la \ arquitectura \ Almond \ PS \ y \ del \ soft-$ | -          |

|----|--------------|--------------------------------------------------------------------------|------------|

| w  | are          | de generación                                                            | 73         |

| 3. | Arq          | quitectura Almond PS                                                     | <b>7</b> 5 |

|    | 3.1.         | -<br>Evolución                                                           | 76         |

|    |              | 3.1.1. La raíz del problema                                              | 76         |

|    |              | 3.1.2. Resolución de otros autores                                       | 77         |

|    |              | 3.1.3. Gramáticas libres de contexto como generadores de series          |            |

|    |              | formales de potencias                                                    | 81         |

|    | 3.2.         | Fundamentos teóricos. Parte formal                                       | 86         |

|    | 3.3.         | Sistemas P aceptados por la arquitectura Almond PS                       | 95         |

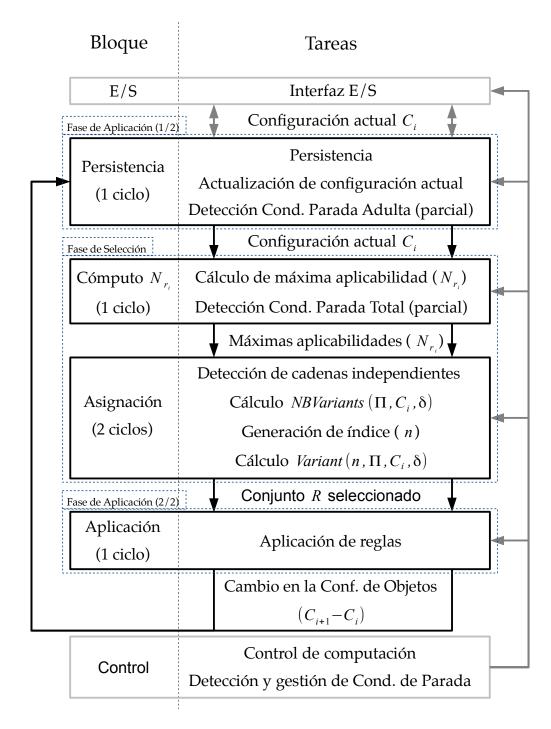

|    | 3.4.         | Implementación hardware                                                  | 99         |

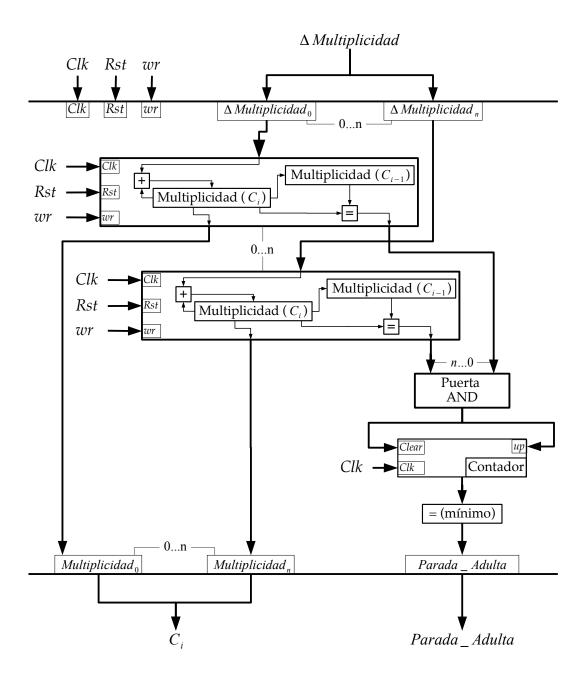

|    |              | 3.4.1. Bloque de persistencia                                            | 101        |

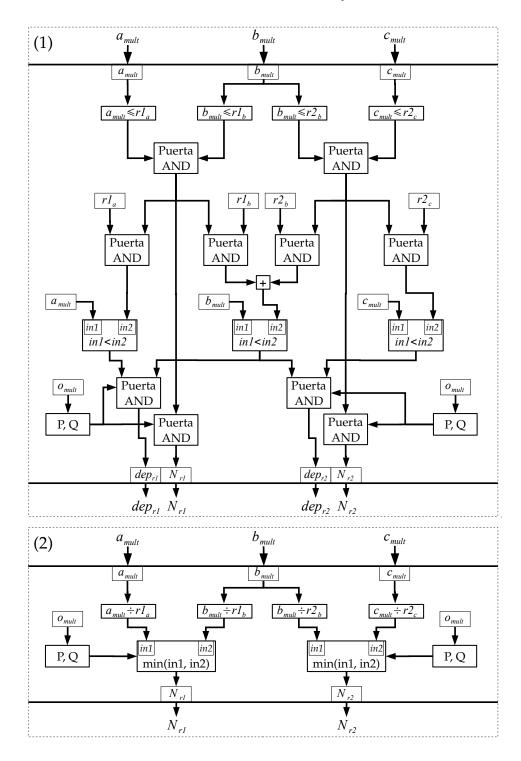

|    |              | 3.4.2. Bloque de cómputo de $N_{r_i}$                                    | 105        |

|    |              | 3.4.3. Bloque de asignación                                              | 107        |

|    |              | 3.4.4. Bloque de aplicación                                              | 117        |

|    |              | 3.4.5. Bloque de entrada/salida                                          | 119        |

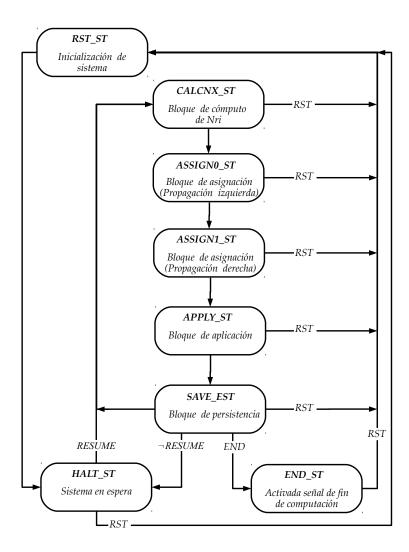

|    |              | 3.4.6. Bloque de control                                                 | 121        |

|    | 3.5.         | Implementando nuevos sistemas P                                          | 124        |

|    | 3.6.         | Conclusiones                                                             | 127        |

| 4. | Soft         | tware de generación de sistemas P                                        | 129        |

|    | 4.1.         | Procesamiento de los sistemas de entrada                                 | 129        |

|    | 4.2.         | Componentes de generación hardware                                       | 131        |

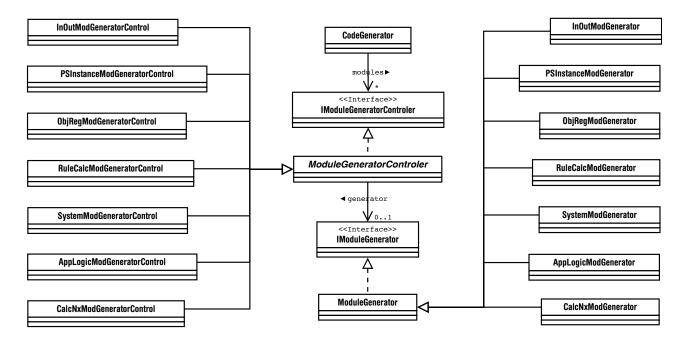

|    |              | 4.2.1. Estructuración de los módulos específicos de generación           | 133        |

|    |              | 4.2.2. Elementos generadores de Almond PS                                | 135        |

|    | 4.3.         | Mejora del software de generación con Model-Driven Engineering           |            |

|    |              | (MDE)                                                                    | 137        |

|    |              | 4.3.1. Breves nociones de MDE                                            | 138        |

|    |              | 4.3.2. Generación de componentes <i>hardware</i> con MDE                 | 141        |

|    |              | 4.3.3. Aplicación de MDE en la generación de pruebas unitarias de        |            |

|    |              | módulos                                                                  | 143        |

|    | 44           | Conclusiones                                                             | 151        |

ÍNDICE GENERAL 7

| II                        | I I   | Escenarios de verifica       | ción, pruebas y resultados                 | 153    |

|---------------------------|-------|------------------------------|--------------------------------------------|--------|

| 5.                        | Aná   | alisis de Almond PS. Pru     | iebas y resultados                         | 155    |

|                           | 5.1.  | Sistemas P de prueba         |                                            | . 155  |

|                           | 5.2.  | Resultados funcionales       |                                            | . 160  |

|                           |       | 5.2.1. Análisis de las confi | iguraciones finales                        | . 160  |

|                           |       | 5.2.2. Análisis de las tran  | siciones necesarias para alcanzar la con-  | -      |

|                           |       | dición de parada to          | tal                                        | . 183  |

|                           |       | 5.2.3. Análisis de la distr  | ibución en el espacio de solución de las   | 3      |

|                           |       | configuraciones fina         | les                                        | . 187  |

|                           | 5.3.  | Recursos hardware            |                                            | . 190  |

|                           |       | 5.3.1. Recursos hardware     | según dependencias entre reglas            | . 191  |

|                           |       | 5.3.2. Recursos hardware     | según complejidad del sistema de entrac    | la 192 |

|                           |       | 5.3.3. Recursos hardware     | según cardinalidades máximas               | . 195  |

|                           |       | 5.3.4. Recursos hardware     | según modo de generación $software$        | . 198  |

|                           |       | 5.3.5. Recursos hardware s   | según tecnologías de $Field\ Programmable$ | ?      |

|                           |       | Gate Array (FPGA             | .)                                         | . 200  |

|                           | 5.4.  | Análisis de rendimiento      |                                            | . 202  |

|                           | 5.5.  | Conclusiones                 |                                            | . 203  |

| C                         | oncl  | usiones finales              |                                            | 207    |

| Pι                        | ublie | caciones                     |                                            | 209    |

| $\mathbf{A}$              | brev  | viaturas                     |                                            | 211    |

| $\mathbf{B}_{\mathbf{i}}$ | iblio | grafía                       |                                            | 217    |

## Índice de tablas

| 3.1. | Interfaz del Bloque de Entrada/Salida                                 | 119 |

|------|-----------------------------------------------------------------------|-----|

| 3.2. | Códigos de estado del sistema ofrecidos por el Bloque de Control.   . | 120 |

| 3.3. | Códigos de control generados por el Bloque de Entrada/Salida          | 120 |

# Índice de figuras

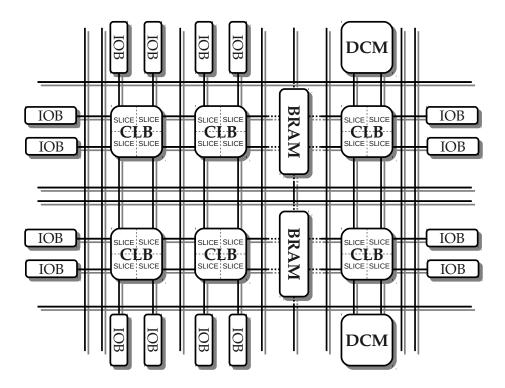

| 1.1. | Estructura por bloques de las FPGA de la marca XILINX 23              |

|------|-----------------------------------------------------------------------|

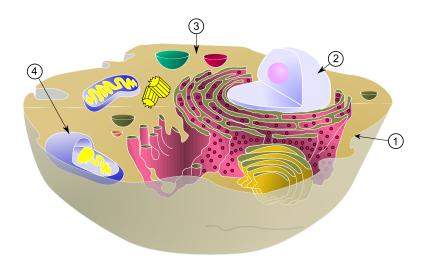

| 2.1. | Estructura de una célula eucariota animal                             |

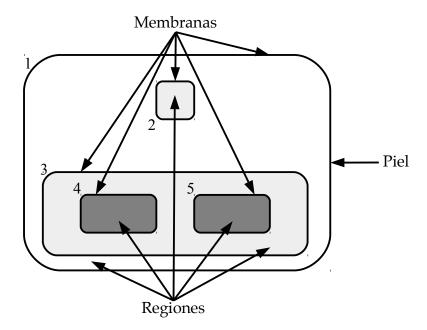

| 2.2. | Representación de una estructura jerárquica de membranas 34           |

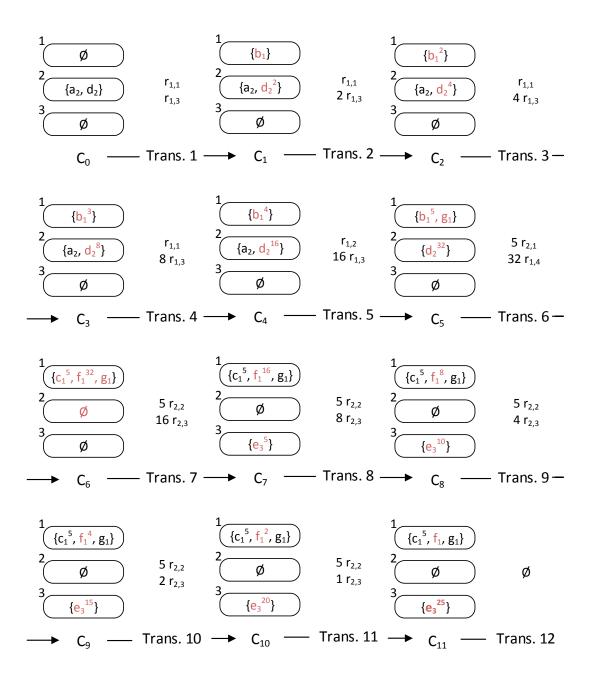

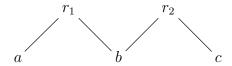

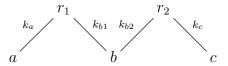

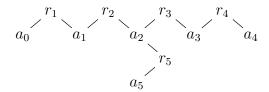

| 2.3. | Representación gráfica de la ejecución del sistema P de ejemplo 46    |

| 2.4. | Esquema de interconexión propuesto por Petreska                       |

| 2.5. | Esquema de un membrane hardware component 60                          |

| 2.6. | Esquema de la arquitectura $Reconfig-P$ $\alpha$                      |

| 2.7. | Esquema de la arquitectura $Reconfig-P$ $\beta$                       |

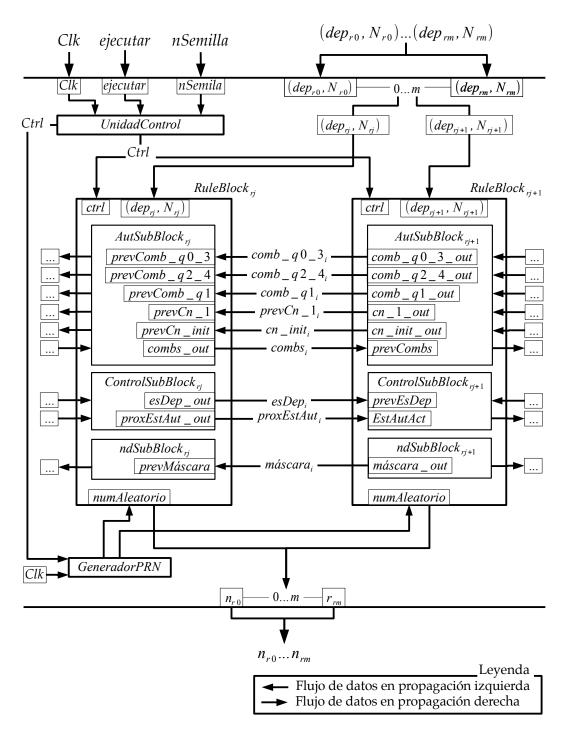

| 3.1. | Diagrama de actividad UML que muestra la división en funcionali-      |

|      | dad de la ejecución de un sistema P                                   |

| 3.2. | Visión general de la arquitectura Almond PS                           |

| 3.3. | Esquemático del bloque de persistencia                                |

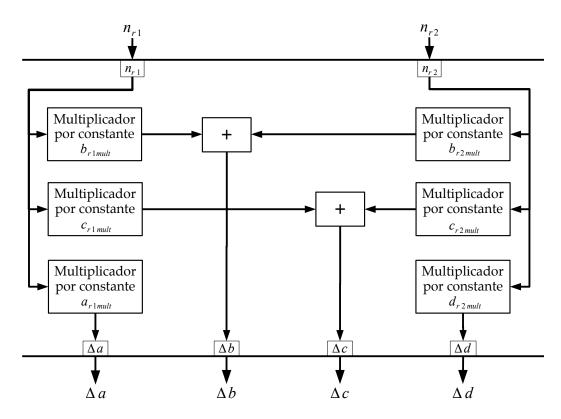

| 3.4. | Esquema del bloque de cómputo de $N_{r_i}$                            |

| 3.5. | Detalle de la arquitectura del bloque de asignación 109               |

| 3.6. | Esquema del bloque de aplicación                                      |

| 3.7. | Diagrama de estados simplificado de la unidad de control              |

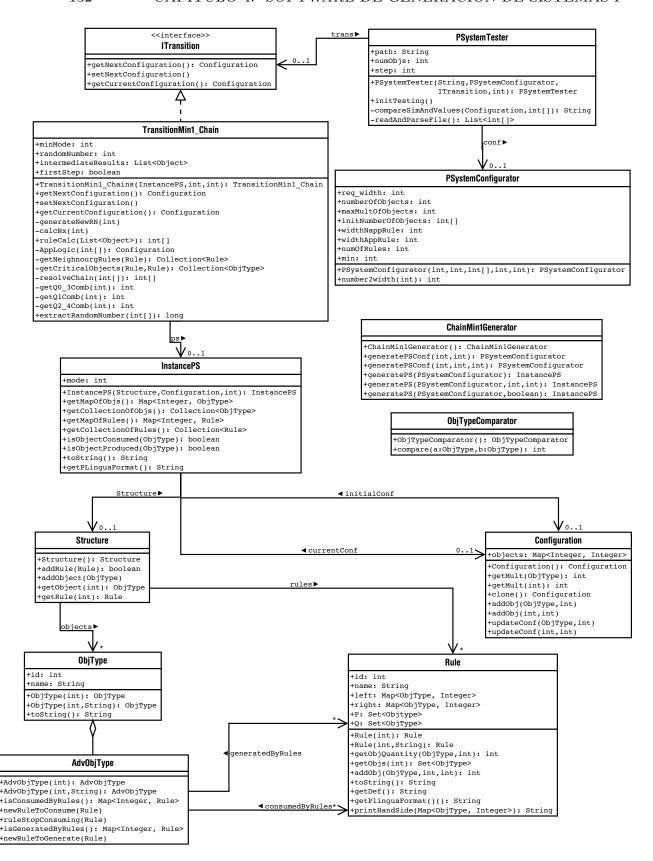

| 4.1. | Diagrama UML simplificado de la solución $software$ de generación 132 |

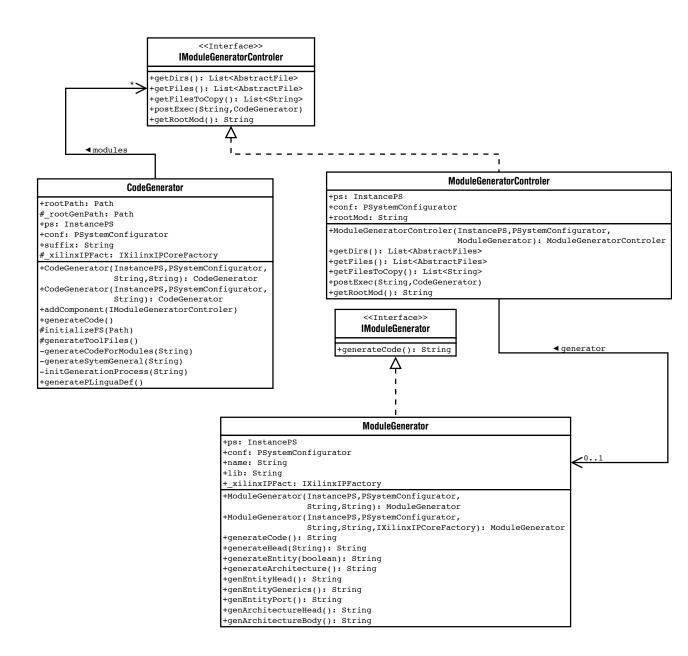

| 4.2. | Diagrama UML simplificado de la estructura base de la herramienta     |

|      | de generación de código                                               |

| 4.3. | Diagrama Unified Modeling Language (UML) simplificado de la so-       |

|      | lución software de generación de código de la plataforma Almond       |

|      | PS                                                                    |

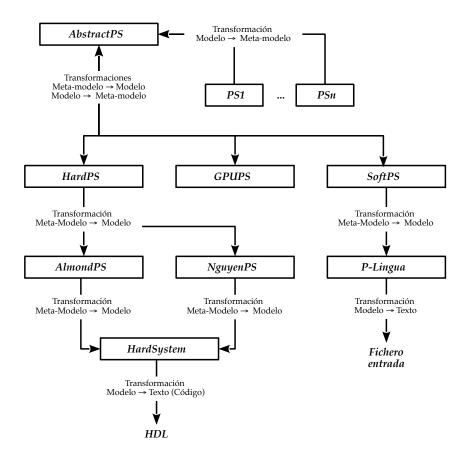

| 4.4.  | Modelos y transformaciones entre modelos de un framework de si-                   |

|-------|-----------------------------------------------------------------------------------|

|       | mulación de sistemas basado en MDE. Las flechas representan trans-                |

|       | formaciones entre modelos                                                         |

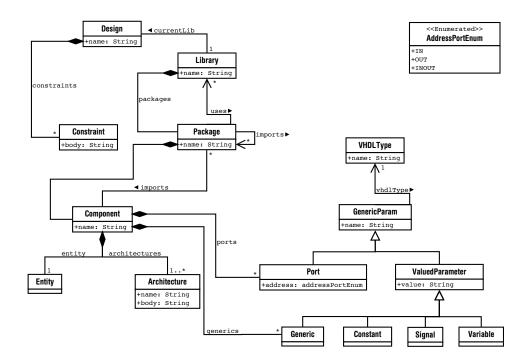

| 4.5.  | Modelo tinyVHDL empleado en el software                                           |

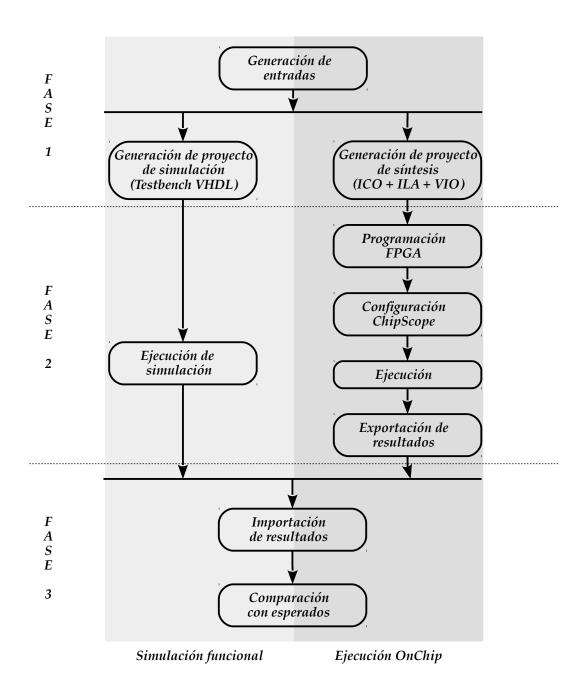

| 4.6.  | Diagrama simplificado de los tres pasos de la metodología de pruebas.147          |

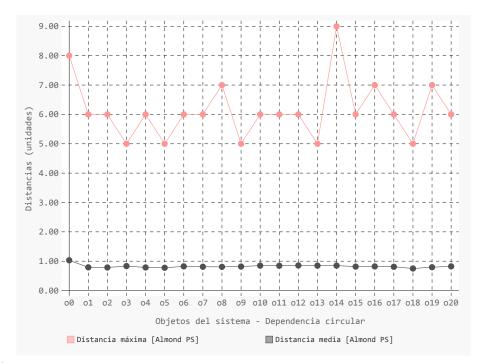

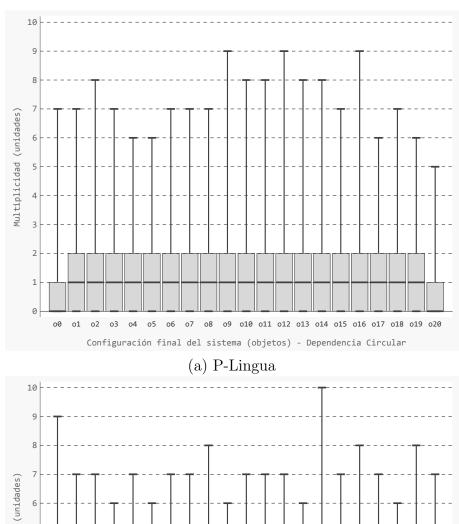

| 5.1.  | Ejemplo de sistemas P de referencia para un tamaño de 10 reglas 157               |

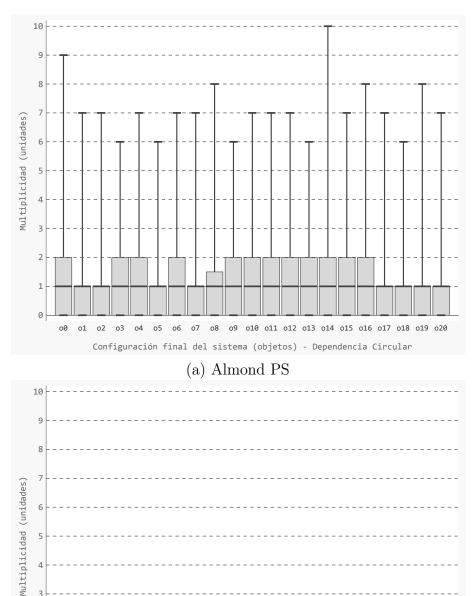

| 5.2.  | Ejecución, con Almond PS, de sistemas P de tamaño 20 reglas y                     |

|       | dependencia circular. Configuración de parada                                     |

| 5.3.  | Distancia de los resultados obtenidos con Almond PS respecto a los                |

|       | resultados más probables. Dependencia circular $\ \ldots \ \ldots \ \ldots \ 163$ |

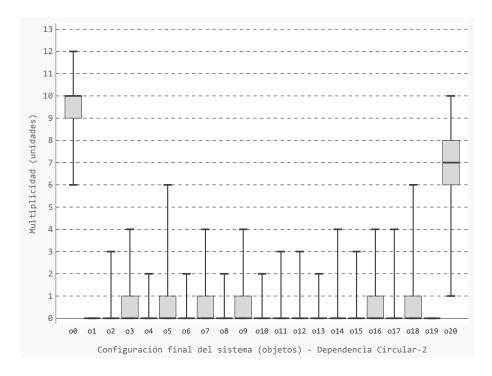

| 5.4.  | Ejecución, con Almond PS, de sistemas P de tamaño 20 reglas y                     |

|       | dependencia circular-2. Configuración de parada                                   |

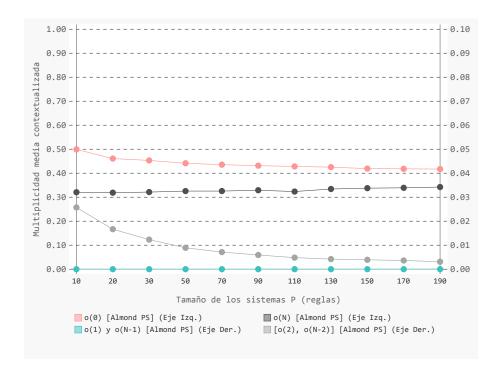

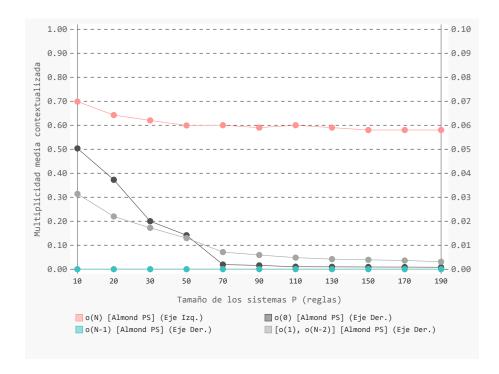

| 5.5.  | Multiplicidad media contextualizada de las distintas ejecuciones con              |

|       | Almond PS de sistemas P con dependencia circular-2 166                            |

| 5.6.  | Ejecución, con Almond PS, de sistemas P de tamaño 20 reglas y                     |

|       | dependencia lineal. Configuración de parada                                       |

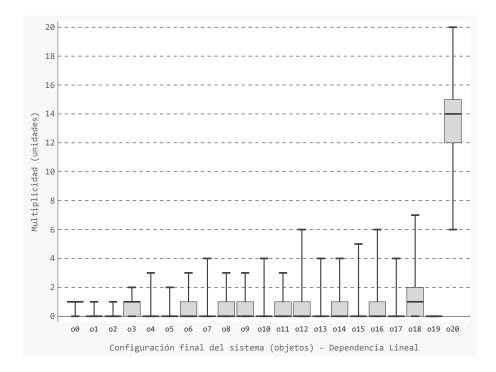

| 5.7.  | Multiplicidad media contextualizada de las distintas ejecuciones con              |

|       | Almond PS de sistemas P con dependencia lineal                                    |

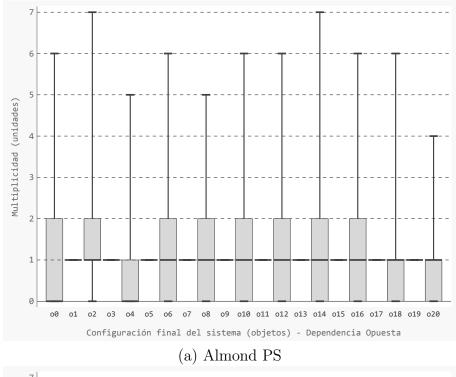

| 5.8.  | Ejecución, con Almond PS, de sistemas P de tamaño 20 reglas y                     |

|       | dependencia opuesta. Configuración de parada                                      |

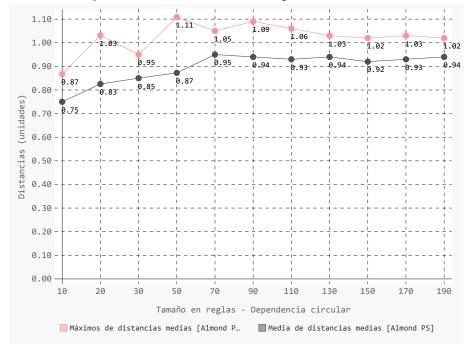

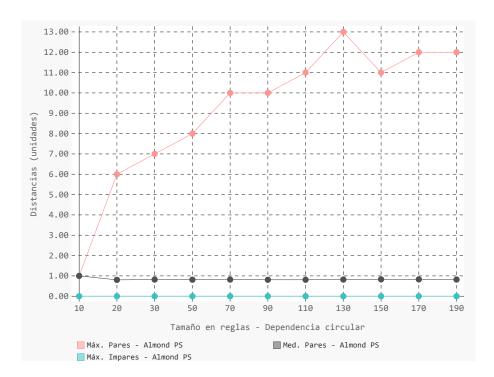

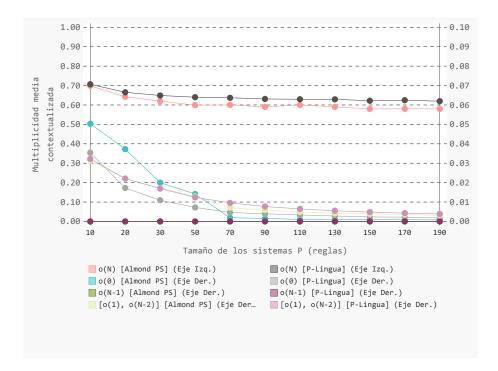

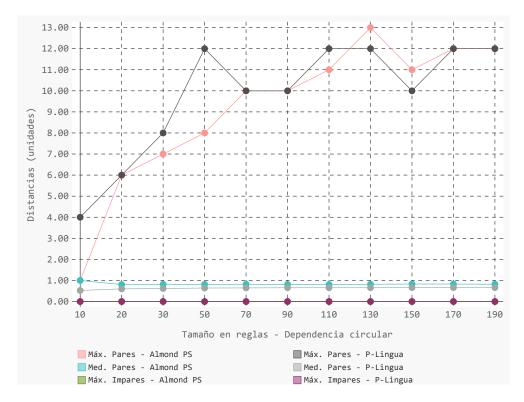

| 5.9.  | Valores medios y máximos de las distancias de las distintas ejecucio-             |

|       | nes de Almond PS en comparación con los resultados más probables. $171$           |

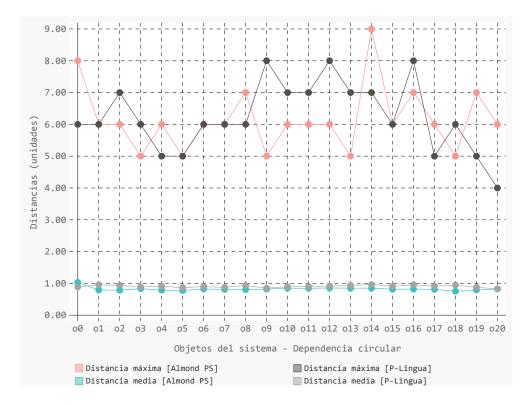

| 5.10. | Ejecución, con Almond PS y P-Lingua, de sistemas P de tamaño 20                   |

|       | reglas y dependencia circular. Configuración de parada 174                        |

| 5.11. | Distancia de los resultados obtenidos con Almond PS y P-Lingua                    |

|       | respecto a los resultados más probables, para un tamaño de 20 re-                 |

|       | glas. Dependencia circular                                                        |

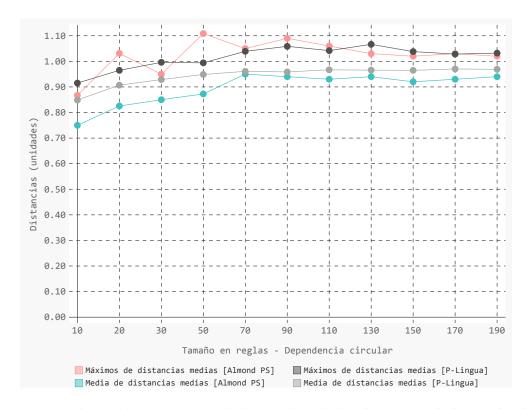

| 5.12. | Distancia de los resultados obtenidos con Almond PS y P-Lingua                    |

|       | respecto a los resultados más probables, para distintos tamaños.                  |

|       | Dependencia circular                                                              |

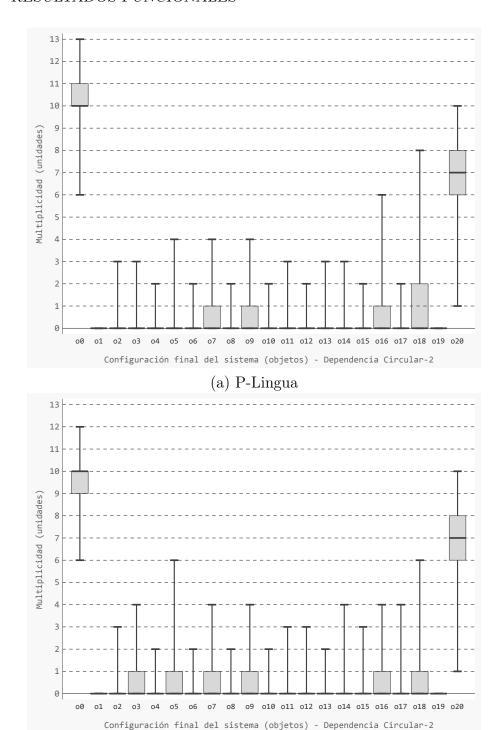

| 5.13. | Ejecución, con Almond PS y P-Lingua, de sistemas P de tamaño 20                   |

|       | reglas y dependencia circular-2. Configuración de parada 177                      |

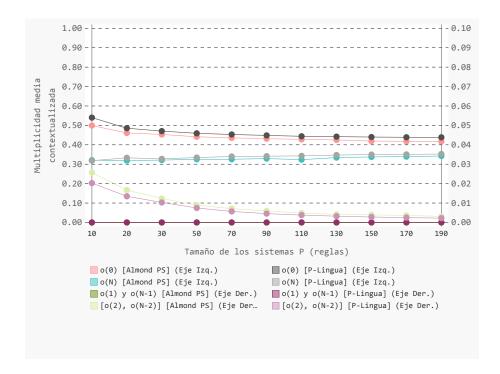

| 5.14. Multiplicidad media contextualizada de las distintas ejecuciones con          |

|-------------------------------------------------------------------------------------|

| Almond PS y P-Lingua de sistemas P con dependencia circular-2 178                   |

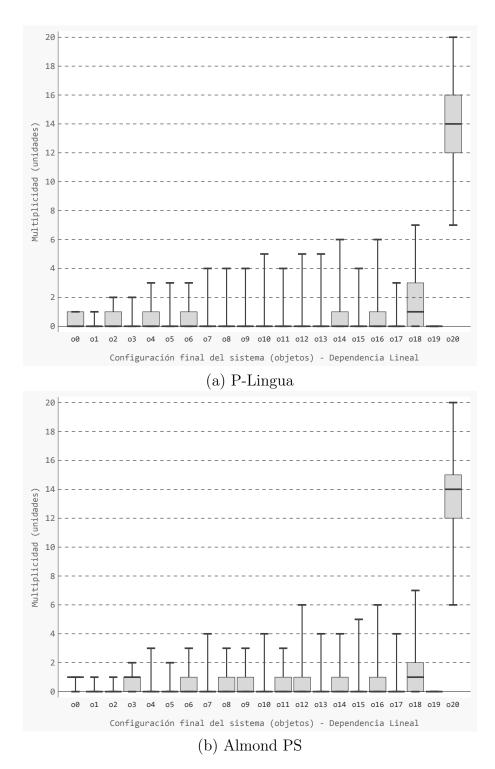

| 5.15. Ejecución, con Almond PS y P-Lingua, de sistemas P de tamaño 20               |

| reglas y dependencia lineal. Configuración de parada                                |

| 5.16. Multiplicidad media contextualizada de las distintas ejecuciones con          |

| Almond PS y P-Lingua de sistemas P con dependencia lineal 181                       |

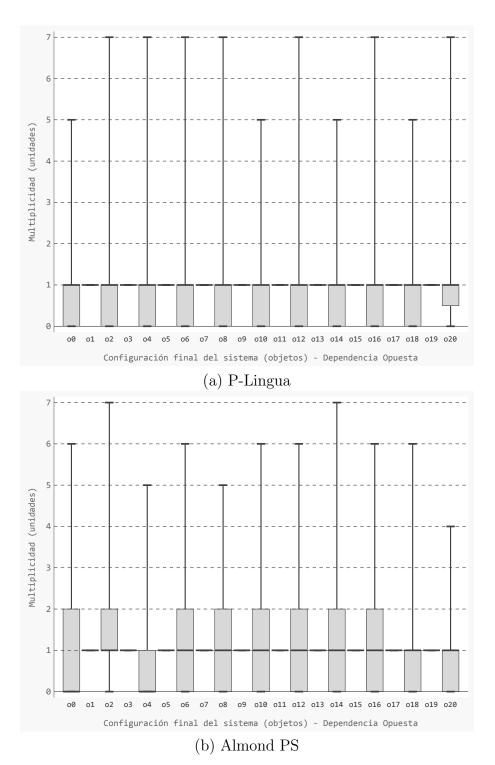

| 5.17. Ejecución, con Almond PS y P-Lingua, de sistemas P de tamaño 20               |

| reglas y dependencia opuesta. Configuración de parada                               |

| 5.18. Valores medios y máximos de las distancias de las distintas ejecu-            |

| ciones de Almond PS y P-Lingua en comparación con los resultados                    |

| más probables                                                                       |

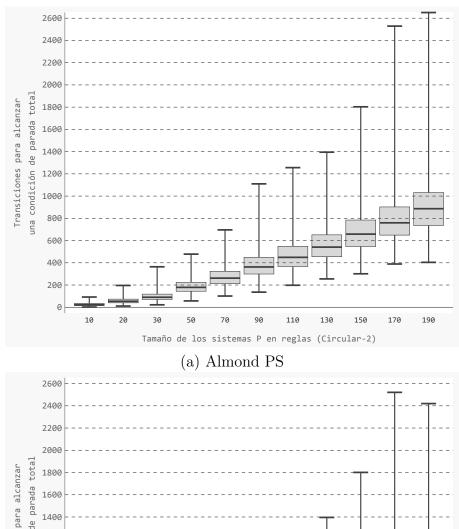

| 5.19. Número de transiciones para alcanzar una condición de parada to-              |

| tal. Comparación de Almond PS y P-Lingua. Modo de dependencia                       |

| circular-2                                                                          |

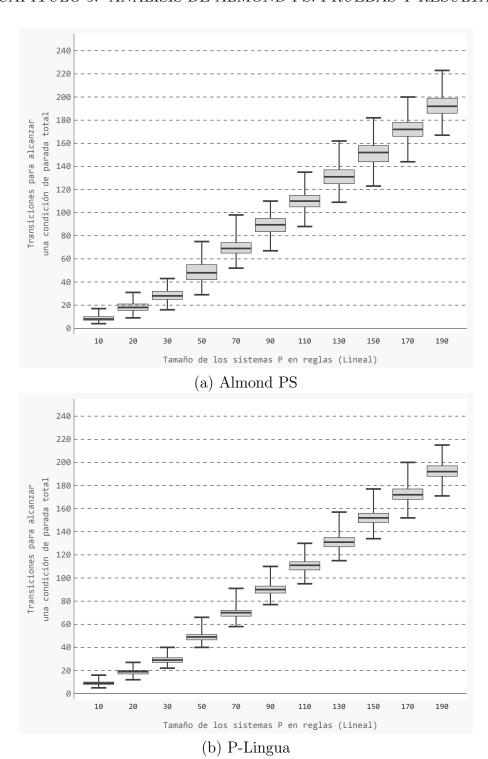

| 5.20. Número de transiciones para alcanzar una condición de parada total.           |

| Comparación de Almond PS y P-Lingua. Modo de dependencia lineal. 186                |

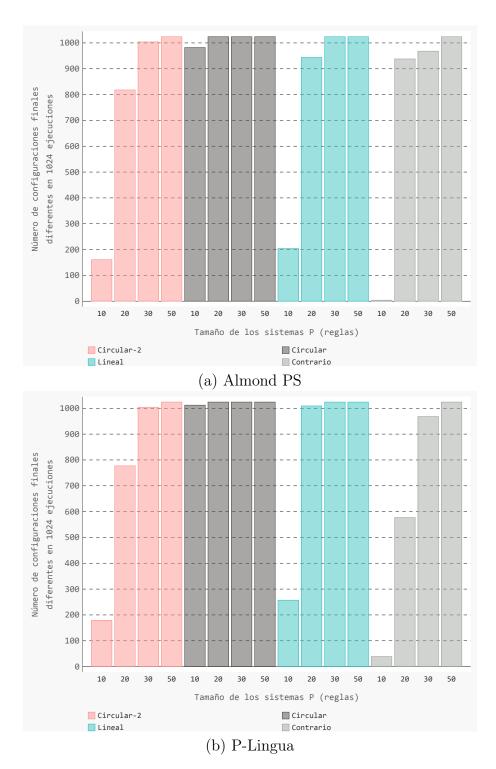

| 5.21. Número de configuraciones finales diferentes para tamaños de 10,              |

| 20, 30 y 50 reglas, de cada uno de los sistemas P de referencia. Se                 |

| muestran los resultados obtenidos con Almond PS (a) y P-Lingua                      |

| (b)                                                                                 |

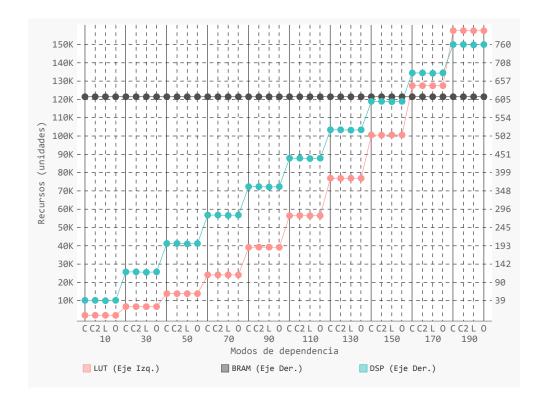

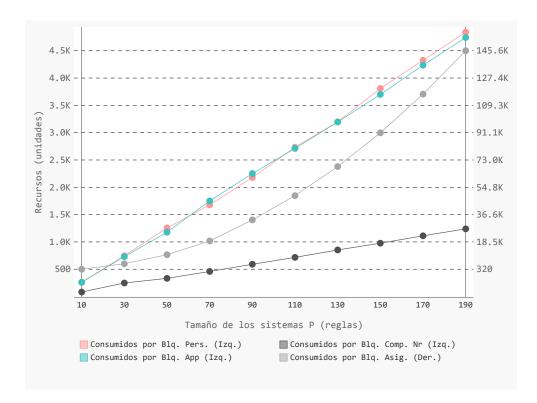

| 5.22. Análisis de recursos $hardware$ consumidos según dependencias de              |

| reglas                                                                              |

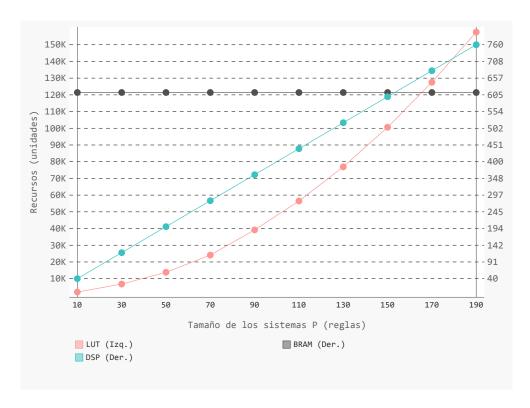

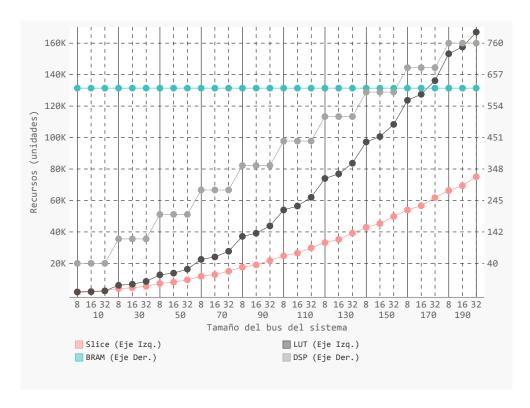

| 5.23. Recursos hardware requeridos por la implementación según la com-              |

| plejidad del sistema, medida en número de reglas. LUT usa el eje                    |

| Y de la izquierda, mientras que BRAM y DSP usan el eje Y de la                      |

| derecha                                                                             |

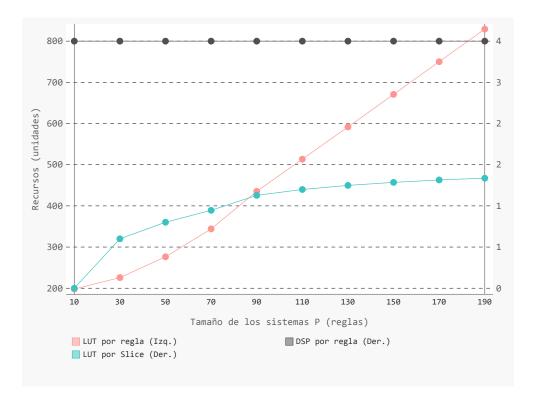

| 5.24. Análisis de recursos $hardware$ consumidos según tamaño de entrada. 194       |

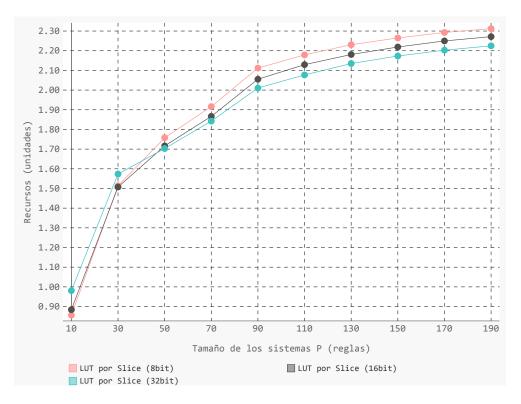

| $5.25.$ Análisis de LUT por regla, LUT por $\mathit{slice}$ y DSP por regla emplea- |

| dos, según tamaño de entrada                                                        |

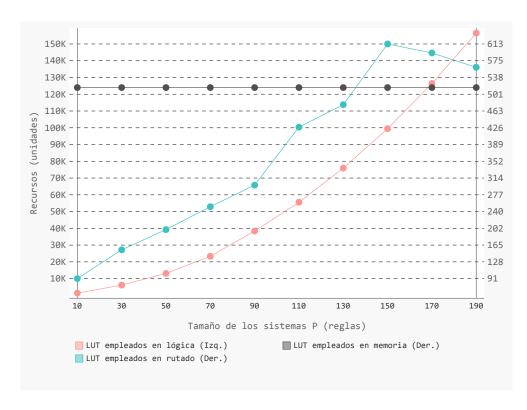

| 5.26. Análisis de la distribución de recursos LUT entre lógica, rutado y            |

| memoria, según tamaño de entrada                                                    |

| 5.27. Análisis de recursos $hardware$ consumidos según tamaño de bus de             |

| datos                                                                               |

| 5.28. Análisis de LUT/Slice empleados según tamano de bus de datos 198                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------|

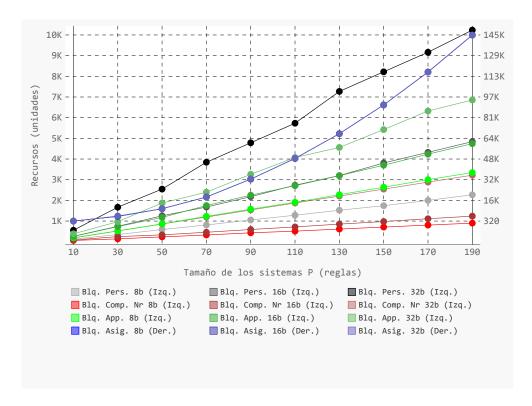

| 5.29. Análisis de recursos $hardware$ consumidos por bloque de la arqui-                                                               |

| tectura según tamaño de bus de datos                                                                                                   |

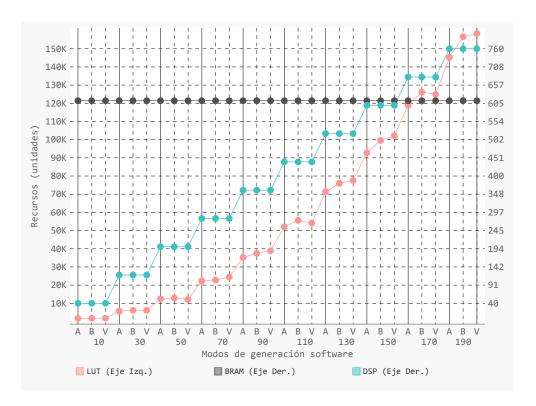

| 5.30. Análisis de recursos $hardware$ consumidos según modo de generación                                                              |

| software                                                                                                                               |

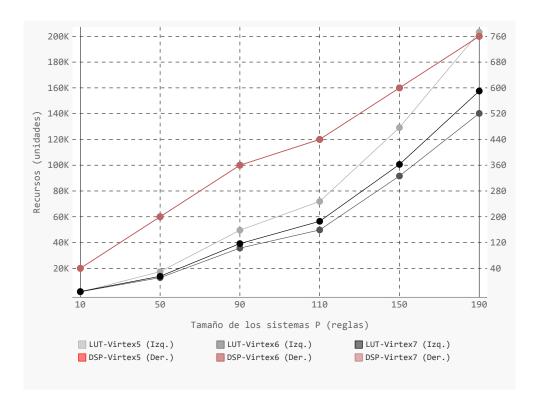

| $5.31.\ {\rm Recursos}\ hardware\ {\rm requeridos}\ {\rm por}\ {\rm la}\ {\rm implementaci\'on}\ {\rm seg\'un}\ {\rm las}\ {\rm tres}$ |

| últimas series de FPGA del fabricante XILINX. LUT usa el eje Y                                                                         |

| de la izquierda, mientras que DSP usa el eje Y de la derecha. Los                                                                      |

| Look-Up Table (LUT) empleados por las tres familias son iguales,                                                                       |

| por lo que su representación está solapada                                                                                             |

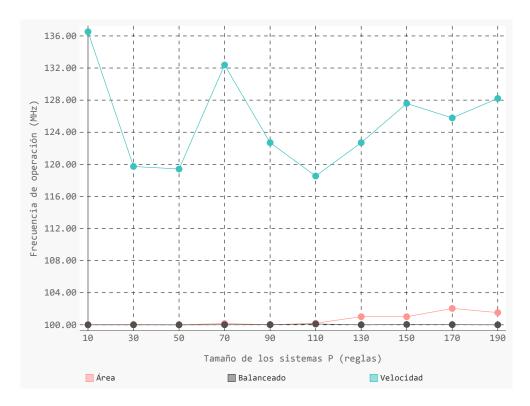

| 5.32. Rendimiento de Almond PS                                                                                                         |

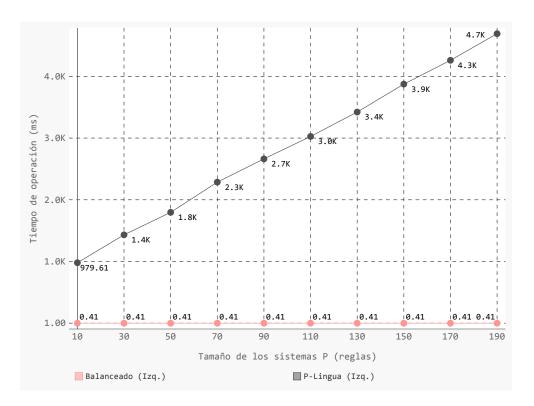

| 5.33. Análisis temporal de Almond PS y comparación con P-Lingua $204$                                                                  |

## Índice de algoritmos

| 2.1.  | Algoritmo de Marcado                                              | • | • | • | • | • | 40  |

|-------|-------------------------------------------------------------------|---|---|---|---|---|-----|

| 2.2.  | Algoritmo paso a paso                                             |   |   |   |   |   | 62  |

| 2.3.  | Algoritmo de aplicación con $\mathit{benchmark}$ de minimalidad   |   |   |   |   |   | 63  |

| 2.4.  | Algoritmo de aplicación con $\mathit{benchmark}$ de minimalidad   |   |   |   |   |   | 64  |

| 3.5.  | Algoritmo para obtener la función $Variant$                       |   |   |   |   |   | 91  |

| 3.6.  | Algoritmia de alto nivel del bloque de asignación                 |   |   |   |   |   | 110 |

| 3.7.  | Funcionalidad específica del bloque de asignación $\ \ . \ \ .$ . |   |   |   |   |   | 111 |

| 3.8.  | Propagación izquierda                                             |   |   |   |   |   | 113 |

| 3.9.  | Valores Auxiliares de Seq. de Padovan                             |   |   |   |   |   | 114 |

| 3.10. | Propagación derecha                                               |   |   |   |   |   | 115 |

| 3.11. | Valores de aplicabilidad con regla dependiente                    |   |   |   |   |   | 116 |

## Capítulo 1

### Introducción

Aunque el estudio y resolución de problemas ha sido una constante a lo largo de la historia del ser humano, no fue hasta el siglo XX cuando se formalizó el concepto de procedimiento mecánico. Este es consecuencia de la búsqueda por parte de un grupo de matemáticos, entre los que destaca D. Hilbert, de un método universal con el que resolver cualquier problema matemático [Hilbert, 1918]. En la década de los 30, K. Gödel publica su Teoría de la Incompletitud [Gödel, 1931] que, junto con resultados posteriores, demuestra que es imposible lo pretendido por D. Hilbert.

A partir del trabajo de K. Gödel se originan los primeros modelos de computación ( $\lambda$ -cálculo de A. Church y S. Kleene [Church, 1936], funciones recursivas de K. Gödel [Gödel, 1931] y máquinas de Touring de A. Touring [Turing, 1937]). Estos modelos de computación sientan las bases para el desarrollo de las máquinas de computación teóricas, entre las que se encuentra la arquitectura de Von Neumann [Neumann, 1945], implementada en la gran mayoría de los ordenadores actuales.

Aunque los primeros ordenadores ofrecían una potencia computacional desconocida hasta la fecha, poseían serias limitaciones de memoria y velocidad de cómputo. De ese modo, el análisis de los recursos requeridos por los algoritmos pasa a cobrar especial relevancia, otorgando un enfoque distinto al estudio y resolubilidad práctica de problemas: la eficiencia de la solución es igual de importante que esta. En consecuencia, aparecen problemas computables que, dada la cantidad de recursos requeridos por los algoritmos que los resuelven, no son abordables en

la práctica con las máquinas del momento (ni actuales), esto es, son intratables. Desgraciadamente, algunos de estos son de interés práctico y los medios de los que disponemos son, claramente, insuficientes.

Es por ello que se empiezan a estudiar modelos de computación alternativos a los convencionales (máquinas de Touring, funciones recursivas y  $\lambda$ -cálculo, entre otros) que amplíen el número de problemas resolubles en la práctica. Dentro de estos nuevos modelos se encuentran aquellos englobados bajo el término de computación natural [Rozenberg et al., 2012], caracterizados por estar inspirados en procesos de la naturaleza. Ejemplos de estos son los algoritmos genéticos, inspirados en la evolución y selección natural; las redes neuronales, basadas en el sistema nervioso; la computación molecular, que emplea moléculas orgánicas como el Ácido desoxirribonucleico (ADN); y la computación con membranas [Păun, 2000], inspirada en las células de organismos vivos.

De entre todos los anteriores, la computación con membranas, o sistemas P en referencia al inventor de la línea de investigación, G. Pâun, constituye la disciplina más reciente. Aunque en la actualidad no es posible aprovechar sus beneficios en materia de potencia de cómputo al no existir una implementación directa, se ha demostrado su utilidad en la resolución de múltiples problemas, especialmente aquellos de simulación de sistemas complejos. Esta aplicación práctica, motiva que sea de especial interés la implementación eficiente de estos modelos.

Este capítulo presenta, en primer lugar, las tecnologías existentes en la actualidad, candidatas a ser escogidas para el desarrollo de sistemas P. En este sentido, la tecnología *Field Programmable Gate Array* (FPGA) se introduce con mayor detalle que el resto, al ser la empleada en el trabajo presentado. Como segundo y último punto, se detallan los objetivos que persigue el trabajo de investigación realizado por el doctorando, así como la estructura de este documento.

#### 1.1. Tecnologías de implementación

En la actualidad existe una gran número de sistemas de computación disponibles, permitiendo elegir el más conveniente en base a los requisitos de diseño del problema. Así, los últimos años han estado marcados por la irrupción de sistemas de procesamiento paralelos, especialmente en la electrónica de consumo. El abara-

tamiento de estos dispositivos, ha permitido obtener mayor potencia computacional a menor coste, haciendo viables muchos desarrollos, anteriormente prohibitivos. Es por ello que se presentan, a continuación, los distintos sistemas de computación disponibles en la actualidad.

#### 1.1.1. Sistema de computación secuencial

Se caracteriza por la ejecución de un software sobre una arquitectura hardware compuesta por un procesador de propósito general o específico. El modo de

ejecución es secuencial, esto es, finaliza una única instrucción por unidad de tiempo. Aunque la potencia de este tipo de arquitecturas puede ser incrementada con

técnicas de diseño entre las que destaca el pipeline, actualmente depende notablemente de los avances en tecnología electrónica y en los procesos de fabricación.

Su principal ventaja reside en ser la plataforma más simple desde el punto de vista del diseño, originando implementaciones extensibles y modulares; no obstante,

es la de menor potencia de cómputo. Esta limitada capacidad de evolución y las

necesidades de computación han ocasionado que en los últimos años se opte por

sistemas de computación multihilo, incluso en dispositivos móviles.

## 1.1.2. Sistemas de computación paralelos basados en soft- ware

En este tipo de sistemas de computación, el *software* es ejecutado sobre uno o más núcleos o procesadores de modo paralelo, por lo que dos o más instrucciones finalizan por unidad de tiempo. En función de la arquitectura *hardware* se puede distinguir entre sistemas distribuidos y no distribuidos.

#### 1.1.2.1. Sistemas de computación basados en software no distribuido

En los sistemas paralelos no distribuidos las unidades de procesamiento son locales, generalmente localizadas en el mismo integrado. Debido a la limitación de las arquitecturas secuenciales, este tipo de plataformas han experimentado una gran difusión en los últimos años, copando el mercado de consumo casi por completo. Dentro de este grupo se distinguen los procesadores multihilo de propósito

general y las *Graphic Processor Unit* (GPU).

Los procesadores multihilo son el resultado de la evolución de los procesadores secuenciales, replicando en el mismo integrado varios núcleos de este tipo. El procesamiento es organizado en hilos, compartiendo recursos tales como espacios de direcciones o datos. El paralelismo se logra al asignar hilos a los distintos núcleos que componen el procesador, aumentando de forma significativa la cantidad de procesado por unidad de tiempo. No obstante, el multiprocesamiento supone un trabajo extra de implementación, originándose problemas de sincronización y de exclusión mutua, que requieren el diseño de algoritmos específicos o adaptación de los existentes en el mejor de los casos. Además, el resto de recursos no es multiplicado por el mismo coeficiente, por lo que pueden originarse cuellos de botella. En conclusión, presentan una potencia de cómputo superior a los anteriores a costa de requerir mayor esfuerzo en su diseño, una extensibilidad similar y una mejor escalabilidad, aunque limitada por el número de núcleos contenidos en el procesador.

Las GPU son unidades de procesado específicas destinadas a la generación de gráficos. Son, por lo tanto, componentes optimizados para una tarea concreta, que se reduce al cálculo de vértices y píxeles. Las aplicaciones gráficas se caracterizan por el predominio de operaciones en coma flotante y un alto grado de paralelismo inherente, posibilitando el uso de unidades de cálculo completamente independientes. Desde sus inicios, en su arquitectura las unidades funcionales se organizaban en dos tipos: aquellas destinadas al procesamiento de vértices y las destinadas al procesamiento de píxeles. En 2006, NVIDIA<sup>1</sup> introduce en el mercado la arquitectura Tesla, que unifica ambas unidades funcionales y las extiende [Lindholm et al., 2008; Sanders and Kandrot, 2011, presentando una matriz escalable de procesadores [NVIDIA, 2011]. La adopción de esta nueva plataforma y el lanzamiento en 2007 de Compute Unified Device Architecture (CUDA), un conjunto de herramientas de desarrollo que permiten la implementación de algoritmos en sus GPU, empleando una variación del lenguaje C, convirtieron a las GPU en sistemas masivamente paralelos de bajo coste [NVIDIA, 2010]. La arquitectura Tesla está basada en el modelo Single Program Multiple Data (SPMD), donde una instrucción Single Instruction Multi-Thread, SIMT, es ejecutada paralelamente sobre un

<sup>&</sup>lt;sup>1</sup>NVIDIA: http://www.nvidia.com

conjunto de datos. En consecuencia, las GPU son adecuadas para algoritmos de gran paralelismo de datos o paralelismo de grano fino (fine-grained), siendo su uso desaconsejado para aplicaciones que requieran un paralelismo de grano grueso (coarse-grained) o a nivel de procesos, o aquellas que precisen gran cantidad de procesos de comunicación o acceso a memoria.

#### 1.1.2.2. Sistemas de computación basados en software distribuido

Los sistemas de computación paralelos y distribuidos están compuestos por varios nodos o hosts comunicados a través de una red de comunicaciones. Gráficamente pueden ser descritos como un grafo en el que las aristas representan los enlaces de comunicación entre equipos, representados por los nodos. Este tipo de sistemas se definen por la topología de la red de interconexión y por los equipos, que pueden ser heterogéneos. Generalmente requieren un importante esfuerzo de implementación, debido a los problemas de sincronización y comunicación, que dependen de las características de la red empleada y del diseño e implementación de la aplicación. Tanto es así que el factor que relaciona el tiempo de comunicación y el de cómputo adquiere especial relevancia y determina la utilidad práctica del sistema diseñado. Los sistemas distribuidos son adecuados para la implementación de algoritmos con paralelismo de grano grueso, en el que las comunicaciones son muy reducidas en comparación con el tiempo de computación.

# 1.1.3. Sistemas de computación paralelos basados en hard-ware

Los sistemas hardware se caracterizan por el paralelismo y la concurrencia. Ofrecen una potencia superior a las implementaciones software, debido a su optimización para resolver un problema concreto, eliminación de la capa software y su paralelismo implícito. No obstante, es la alternativa que supone un mayor esfuerzo de desarrollo, y el área aparece como un recurso crítico que limita la complejidad de los algoritmos a implementar. Considerando los dispositivos lógicos programables, existen dos alternativas hardware: los Application-Specific Integrated Circuit (ASIC) y las FPGA. Con respecto a los primeros, son circuitos integrados hechos a medida para una aplicación específica. Sus principales ventajas son el ren-

dimiento, consumo, coste y frecuencia de reloj; su principal desventaja consiste en que una vez fabricados no es posible modificarlos. Por el contrario, la tecnología FPGA permite reconfigurar el *hardware*, encontrándose en un punto intermedio entre el *software* y los ASIC.

#### 1.1.3.1. La tecnología Field Programmable Gate Array

La tecnología FPGA fue inventada a mediados de los años ochenta por la compañía XILINX<sup>2</sup> y se considera la evolución de al tecnología Complex Programmable Logic Device (CPLD) [Wilson, 2007]. Las FPGA son dispositivos semiconductores programables basados en Configurable Logic Blocks (CLB) conectados entre sí empleando una red de interconexión configurable y con el exterior a través de unos bloques de entrada/salida denominados Input/Output Blocks (IOB) (Fig. 1.1). Los CLB constituyen la unidad reprogramable básica y están formados por varias celdas lógicas denominadas Slices. Los Slices se componen, a su vez, de varias tablas de búsqueda (Look-Up Table, LUT) de un determinado número de entradas que permiten definir cualquier función lógica de aridad igual al número de estas, un sumador completo que incluye lógica de acarreo, multiplexores y biestables (FlipFlops, FF). Además, disponen de bloques de memoria volátil denominados Block RAM (BRAM) y bloques de gestión digital del reloj (Digital Clock Manager, DCM), ambos distribuidos por su área. Con este tipo de dispositivos es posible implementar cualquier circuito digital, siendo las únicas restricciones los recursos hardware disponibles en el chip y la frecuencia máxima de operación que se pueda alcanzar.

Las principales ventajas de las FPGA derivan de su característica fundamental: la reconfigurabilidad<sup>3</sup>. Esta reduce considerablemente los tiempos de desarrollo de un circuito digital, ya que simplifica y determina el ciclo de diseño y posibilita la reconfiguración del dispositivo un número prácticamente ilimitado de veces, incluso de forma remota y parcial en tiempo de ejecución. Estas características les otorgan una gran flexibilidad, convirtiéndolas en una destacada herramienta para labores de investigación y/o de prototipado. Como aspectos negativos, en compara-

$<sup>^2\</sup>mathrm{X}$ ILINX: http://www.xilinx.com

<sup>&</sup>lt;sup>3</sup>Existen FPGA que incorporan una tecnología de memoria de programación basada en fusibles permitiendo configurar el dispositivo una única vez.

Fig. 1.1: Estructura por bloques de las FPGA de la marca XILINX.

ción con los ASIC, cabe citar que estos últimos permiten una mayor especificidad del *hardware* a cambio de perder parte de la flexibilidad proporcionada por las FPGA, consiguiendo una reducción de coste (para grandes tiradas) y de consumo y aumentando la frecuencia máxima de operación.

Actualmente existen varios fabricantes de FPGA. Entre ellos destacan XILINX, ALTERA<sup>4</sup>, LATTICE SEMICONDUCTOR<sup>5</sup> y ACTEL<sup>6</sup>, siendo los dos primeros los líderes del sector.

<sup>&</sup>lt;sup>4</sup>ALTERA: http://www.altera.com

<sup>&</sup>lt;sup>5</sup>LATTICE SEMICONDUCTOR: http://www.latticesemi.com/

<sup>&</sup>lt;sup>6</sup>ACTEL: http://www.microsemi.com/

# 1.2. Implementaciones de modelos de computación con membranas

El desarrollo de implementaciones de sistemas P tuvo sus inicios poco después del nacimiento de la disciplina. De ese modo, las primeras implementaciones se trataban de versiones software secuenciales. Estas versiones, a pesar de resultar las más fáciles de desarrollar, extender y mantener, pronto evidenciaron una falta de potencia de cómputo, que las limitaban a tareas de demostración y asistencia durante el diseño de sistemas.

El siguiente paso fue natural, emplear tecnologías que ofrecieran una mayor potencia de cómputo, a través de su paralelismo inherente. Así, las implementaciones software paralelas atrajeron el interés en el área. En este sentido, se han desarrollado simuladores que hacen uso del paralelismo en procesadores de propósito general, a través del empleo de varias máquinas o del uso de aquellos con más de un núcleo de procesamiento. Sin embargo, la potencia de cómputo ofrecida por estas tecnologías no es suficiente.

Al analizar un sistema de computación con membranas, lo primero que llama la atención es la simplicidad de las operaciones que son requeridas para su ejecución. El gran escollo se presenta en el doble paralelismo inherente de estos sistemas. A grandes rasgos, los sistemas P están compuestos por conjuntos de unidades que transforman recursos existentes en otros nuevos en cada paso de computación. Un sistema está compuesto por cientos de este tipo de unidades, que compiten entre sí por los recursos existentes. Es, por lo tanto, un problema de distribución de recursos, agravado por las fuertes restricciones que se imponen en esta competición, desde la necesidad de agotar solo un determinado número de estos recursos, hasta el máximo posible, y todo ello de un modo no determinista, que hace necesario resolver, a su vez, un problema de gran esfuerzo computacional, el de la distribución de recursos, en cada paso de computación.

Es evidente que el desarrollo de simuladores o implementaciones que empleen tecnología electrónica convencional, no podrá ofrecer el mismo rendimiento que aquellos desarrollados, hipotéticamente, con tecnología orgánica. Es por ello que, actualmente, el objetivo del área es la resolución de aquellos problemas de interés

práctico en un tiempo aceptable. En este sentido, las últimas líneas de investigación se centran en tecnologías donde existe un alto grado de paralelismo: desarrollo software sobre GPU y hardware sobre FPGA.

Son obvias las ventajas en potencia de cómputo que supone un dispositivo hardware especialmente diseñado para la aplicación en este ámbito. De ese modo, la tecnología FPGA se postula como una de las más adecuadas, dado su equilibrio (a nivel hardware) entre potencia y flexibilidad. En este contexto, existen dos trabajos previos, el desarrollado por B. Petreska y C. Teuscher [Petreska and Teuscher, 2004], que presenta a las FPGA como dispositivos válidos para este fin, y el llevado a cabo por V. Nguyen [Nguyen, 2010], donde se describe una solución para un subconjunto de sistemas P, centrados en aquellos deterministas, aunque presenta las primeras líneas para los no deterministas.

Un inconveniente añadido para una implementación hardware de sistemas de computación con membranas, es el hecho de ser modelos orientados a máquina. Es por ello que para cada problema es preciso contruir una máquina distinta, por lo que el desarrollo de una implementación se dirige al diseño de una arquitectura en base a la cual se construirán los distintos sistemas P en función de los problemas de entrada. Además, es preciso acompañar a este desarrollo de un software de generación de instancias concretas para, de ese modo, dotar de utilidad al trabajo realizado. En este sentido, Nguyen ha diseñado una solución para la generación de código. No obstante, esta se encuentra demasiado acoplada con su arquitectura, siendo conveniente el desarrollo de una herramienta que permita la modificación del hardware sin que requiera conocimientos exhaustivos de este.

En consecuencia, el siguiente reto consiste en el desarrollo de una implementación que, además de destacar por su potencia computacional, y mantener una flexibilidad y escalabilidad adecuadas, amplíe el espectro de sistemas P admitidos, centrándose en aquellos no deterministas, que son los de mayor interés práctico. Además, los desarrollos de Nguyen y Petreska toman como referencia de diseño la estructura de los sistemas P. En este sentido, se busca focalizar el diseño en las propias características de la tecnología FPGA, y no en la de los sistemas P, con el objetivo de obtener sistemas con el mayor rendimiento posible. Como elemento adicional, también es necesario el desarrollo de una herramienta software de generación, con un nivel de acoplamiento inferior a la existente, que facilite la

modificación del hardware desarrollado.

### 1.3. Objetivos y estructura de la tesis

El objetivo general de este trabajo de tesis consiste en el desarrollo de una implementación *hardware* de sistemas P. Para ello, es necesario llevar a cabo, previamente, un análisis de los métodos, algoritmos, arquitecturas y soluciones actuales. Dadas las características del modelo computacional objeto de este trabajo, se fija como objetivo el desarrollo de una arquitectura genérica, junto con un procedimiento automático de generación, con el fin de cubrir el conjunto de las necesidades que requieren los sistemas P.

Así, se presenta la arquitectura Almond *P System* (Almond PS). Se trata de una arquitectura modular, en la que se encapsulan los distintos componentes necesarios para la ejecución de los sistemas P, con el propósito de ofrecer la máxima flexibilidad y escalabilidad posibles. Además, a diferencia de otras implementaciones actuales, únicamente es preciso tener en consideración el grafo de dependencias entre sus reglas a la hora de seleccionar los sistemas compatibles. Del mismo modo, también se presenta un *software* de generación de implementaciones de la arquitectura Almond PS, que constituye un primer paso hacia un *framework* de generación de código *Hardware Description Language* (HDL).

A continuación, se detallan los objetivos concretos del trabajo de tesis presentado en este documento:

- 1. Análisis del modelo de computación con membranas, abstracción de aspectos estructurales y funcionales y establecimiento de requisitos.

- 2. Análisis de implementaciones y algoritmos de implementación actuales, incluyendo hardware y sofware.

- 3. Implementación de una arquitectura de computación (Almond PS) que permita la simulación de sistemas P, en base a los requisitos establecidos.

- 4. Diseño de una herramienta software de simulación, que permita la generación automática de instancias concretas de dispositivos bajo la arquitectura Almond PS, y posterior desarrollo de los elementos funcionales básicos.

5. Validación de los resultados obtenidos mediante una extensa batería de pruebas, que permita el análisis del conjunto de factores que influyen en los sistemas generados. Incluye el establecimiento previo de los escenarios de prueba, así como del desarrollo de las herramientas necesarias.

Como punto final, se describe como se organiza el resto del documento:

- Parte I. Está formada por el capítulo 2, y satisface los objetivos 1 y 2 (parcialmente). En este capítulo se presenta la computación con membranas o sistemas P, con una introducción informal, seguida de una definición formal, enfocada a los conceptos necesarios para la comprensión del desarrollo de la arquitectura Almond PS. Esta introducción es completada con la descripción funcional de un ejemplo, y finaliza con la enumeración de las principales aplicaciones actuales, o en un futuro cercano, de los sistemas P. Una vez aportados los conocimientos previos necesarios, se analizan las implementaciones más destacadas de este modelo, haciendo énfasis en aquellos trabajos más próximos a la arquitectura Almond PS.

- Parte II. Los capítulos 3 y 4 le dan cuerpo a esta parte, respondiendo a los objetivos 2 (parcialmente), 3 y 4. El capítulo 3 alberga la descripción de la arquitectura Almond PS. Así, en primer lugar realiza un análisis de las propuesta de otros autores a los problemas de algoritmia observados en los sistemas P. Seguidamente, se introducen los aspectos formales considerados en el diseño de la arquitectura y, por último, esta se describe detalladamente. Respecto al capítulo 4, muestra el desarrollo software que permite la generación automática de instancias concretas basadas en la arquitectura Almond PS, así como la metodología empleada.

- Parte III. En esta sección, formada por los capítulos 5 y 6, se da respuesta al último objetivo, el número 5 siguiendo la numeración anterior. Así, en primer lugar se describen los escenarios de prueba, seguidos por las herramientas empleadas para la adquisición y análisis de estos resultados. Por último, se analizan los resultados obtenidos, de los cuales se extraerán las conclusiones más relevantes de este trabajo, descritas en el capítulo 6.

# Parte I Análisis del estado del arte

## Capítulo 2

### La computación con membranas

Tal y como se ha comentado en el capítulo de introducción, la computación con membranas es una disciplina de reciente creación, que se enmarca dentro de los modelos de computación alternativos. Aunque el actual desarrollo científico no ha permitido plasmar este modelo de computación en dispositivos reales, genera un alto grado de interés debido a las ventajas que presenta en diferentes áreas, especialmente aquellas relacionadas con la simulación de procesos orgánicos e inorgánicos.

Este capítulo persigue ofrecer una visión general del estado de esta disciplina, no únicamente desde un punto de vista teórico, sino también de las distintas implementaciones existentes, sin olvidar los posibles campos de aplicación en los que resulta de utilidad a día de hoy o en un futuro próximo.

Con este propósito, el capítulo se estructura en tres apartados. El primero de ellos está dedicada a la descripción de la computación con membranas, desde un punto de vista teórico. Esta sección empieza con una introducción y definición informal a los sistemas P, enfocada para aquellos lectores para los cuales este documento constituye su primer contacto con este modelo de computación. Seguidamente, se ofrece una definición formal, centrada en aquellos conceptos o desarrollos teóricos alineados con el propósito de la investigación llevada a cabo por el doctorando. A continuación se muestra un ejemplo de un sistema P, al tiempo que se detalla una computación, con la finalidad de afianzar los conceptos introducidos previamente. Como último punto, se enumeran algunas aplicaciones

de interés.

El segundo apartado está dedicado a las implementaciones actuales. Así, se enumeran algunos requisitos de diseño que permitan fijar un criterio de comparación de los diferentes trabajos existentes, los cuales se clasifican en base a los dispositivos que los soportan. Este bloque continúa con la descripción de estos trabajos, ofreciendo un mayor nivel de detalle en aquellas implementaciones que guardan mayor relación con la implementación presentada en este documento.

Tras finalizar el análisis teórico de la computación con membranas y de las implementaciones existentes, se comentan las conclusiones más importantes de este capítulo.

#### 2.1. Computación con membranas

La computación con membranas es un modelo de computación alternativo introducido por G. Păun en 1998 [Păun, 2000]. Está inspirado en el funcionamiento de las células eucariotas y se trata de un modelo paralelo distribuido y computacionalmente universal (capaz de resolver los mismos problemas que las máquinas de Turing. A diferencia de la gran mayoría de modelos utilizados en la actualidad, es un modelo orientado a máquinas, por lo que la implementación de un algoritmo no consiste en una secuencia finita de instrucciones, como sucede con un modelo orientado a programas, el más extendido, sino que se encuentra implícita en la descripción de una máquina.

Una célula (Fig. 2.1) se compone de: (1) una envoltura que le confiere entidad y que, en el caso de las células animales, se corresponde con una membrana celular; (2) el núcleo (en caso de ser una célula eucariota, en caso contrario se denomina célula procariota); y (3) el citoplasma, donde se localizan los orgánulos celulares (4). Por lo tanto, en la célula se distinguen una serie de espacios o compartimentos (el propio citoplasma, los orgánulos y el núcleo celular) delimitados por membranas, existiendo una externa que le confiere individualidad. Las funciones de las membranas son las de actuar como delimitador y como canal de comunicación. En el interior de la región delimitada por la membrana existen moléculas. Estas pueden proceder del exterior, ser transportadas a este o a compartimentos internos a través de los canales de comunicación. Además, en estas regiones se producen reacciones

Fig. 2.1: Estructura de una célula eucariota animal. Se distingue (1) la membrana celular, (2) el núcleo celular, (3) el citoplasma, y (4) los orgánulos con sus membranas celulares. Versión modificada de la original creada por los usuarios MesserWoland y Szczepan1990 en *Wikipedia* y bajo licencia *Creative Commons*.

químicas, originando nuevas moléculas a partir de las existentes a una velocidad que puede ser modificada por los catalizadores.

En la actualidad existen gran cantidad de variantes de modelos de computación con membranas o sistemas P, siendo el sistema P transitivo, o sistema P de transición, el primigenio. Un sistema P de transición posee una estructura jerárquica de membranas (Fig. 2.2) en la que existe una externa, la raíz de la jerarquía, que le confiere entidad y que se denomina piel. De ese modo, una membrana define una región que puede contener más membranas o multiconjuntos de objetos o símbolos. Asociadas a las regiones se definen las reglas de evolución. Estas definen la semántica del sistema P, basada en la manipulación de objetos: transformación y comunicación entre membranas. Adicionalmente, también es posible disolver membranas, pasando todos sus objetos a la membrana padre. Las reglas se ejecutan de un modo síncrono paralelo maximal con prioridades, y en ocasiones no determinista. La componente probabilista intrínseca a las reacciones químicas y a los procesos de comunicación que se originan en el interior de las células es capturada con la definición de una relación de prioridad fuerte entre las reglas de evolución. Este concepto se describe con un ejemplo: si existen tres reglas,  $r_1$ ,  $r_2$  y  $r_3$ , de modo que  $r_1$  y  $r_2$  poseen mayor prioridad que  $r_3$ , esta última se ejecutará si y solo si no

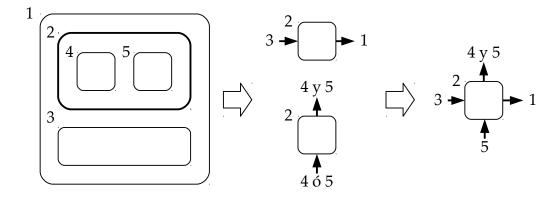

Fig. 2.2: Representación de una estructura jerárquica de membranas.

es posible ejecutar ni  $r_1$  ni  $r_2$ , aunque haya objetos disponibles para que  $r_3$  pueda ser ejecutada, e incluso los objetos implicados en  $r_3$  sean distintos a los implicados en  $r_1$  y  $r_2$ ; para las reglas de igual prioridad o para las que no se establezca relación alguna, su ejecución será no determinista. Para otorgar simplicidad al modelo, se incorpora un reloj universal que rige la aplicabilidad de las reglas. Así, el sistema pasa de una configuración a otra en un ciclo de reloj o transición en el que se ejecutan todas las reglas aplicables, de acuerdo a las relaciones de prioridad y a los símbolos disponibles, un número determinado de veces. Estas se ejecutan de un modo paralelo y maximal. La maximalidad establece que el número de veces que es aplicada una regla en un ciclo de computación debe ser el máximo posible, consumiendo, a su vez, el máximo posible de objetos.

Desde su presentación, la disciplina ha experimentado un gran crecimiento, originándose una gran cantidad de ramificaciones que abarcan desde pequeñas modificaciones del sistema P inicial hasta el desarrollo de variedades nuevas, en las que perduran la inspiración biológica y el esquema de funcionamiento del original. Al ser un modelo computacional orientado a máquinas, el nacimiento de estas ramificaciones generalmente es motivado por la necesidad de resolver problemas

concretos. Ejemplos de estas extensiones son:

- Sistemas basados en la catálisis. Los sistemas P catalíticos (catalytic P systems [Păun, 2000, 2002]) se caracterizan por la presencia de catalizadores, considerados como objetos inalterables por las reglas y que son requeridos para su aplicación.

- Modificación de los procesos de comunicación entre membranas, contemplando la transferencia de objetos por concentración, sistemas P controlados por concentración (concentration controlled P systems [Păun, 2002; Dassow and Păun, 2001]), tal y como sucede biológicamente, asignando cargas a objetos y membranas [Păun, 2000, 2002] o modificando la permeabilidad de estas últimas [Păun, 2000, 2002].

- Eliminación de la membrana de salida, considerando la salida del sistema aquellos objetos enviados al entorno a través de la piel [Păun, 2002].

- Uso de promotores e inhibidores [Bottoni et al., 2002].

- Creación, disolución y división de membranas, dando lugar a los sistemas

P con membranas activas (P systems with active membranes [Păun et al., 2010]).

- Sistemas P con simportadores/antiportadores (P systems with symport/antiport [Păun, 2002]), en los que dos objetos atraviesan la membrana simultáneamente en el mismo u opuesto sentido.

- Sistemas P con portadores (P systems with carriers [Păun, 2002; Păun and Păun, 2002]), en los que se diferencia entre objetos portadores y viajeros, de modo que estos últimos no pueden desplazarse a otra región sin la presencia de los primeros.

- Que afectan a la estructura de los objetos, describiéndolos como compuestos por elementos atómicos, ejemplos son los sistemas de membranas de reescritura/recombinación/contexto/inserción-eliminación (rewriting/splicing/contextual/insertion-deletion membrane systems [Păun, 2002]).

- Sistemas P de conformación (conformon P systems [Frisco, 2008]), basados en las conformaciones de las estructuras moleculares que forman compuestos.

- Sistemas de membranas móviles con objetos de superficie (*mutual mobile membrane systems with surface objects* [Aman and Ciobanu, 2008, 2009]), que incorporan la abstracción de los procesos de endocitosis, exocitosis y fagocitosis.

- Sistemas P basados en energía (energy based P systems [Mauri et al., 2009]), que introducen el concepto de energía.

- Sistemas P estocásticos/probabilistas (probabilistic/stochastic P systems [Păun et al., 2010]), que introducen la probabilidad/azar en la ejecución de las reglas.

Los sistemas iniciales consideraban a la célula como un sistema completo, atendiendo únicamente a sus membranas, regiones, reglas y objetos. Su entorno era utilizado como un método de eliminación de objetos o, en algunos de ellos, como salida de la computación. No obstante, la interacción con el entorno y con otras células es un proceso esencial para la vida. De ese modo, se desarrollan nuevas variedades basadas en redes de membranas: los tejidos de sistemas P (tissue P systems [Carlos Martín-Vide et al., 2005]) y los sistemas P de impulsos neuronales (spiking neural P systems [Păun, 2008; Frisco, 2008]). Los primeros nacen como la abstracción de los tejidos biológicos, contemplando la intercomunicación celular. Subvariedades de estos son las colonias P (P colonies [Kelemen et al., 2004]) y las poblaciones de sistemas P (population P systems [Bernardini and Gheorghe, 2004), diferenciadas en que en las últimas las células se definen como membranas elementales que se comunican entre sí a través del entorno, además de por canales de comunicación específicos y dinámicos. Por su parte, los sistemas P de impulsos neuronales [Păun, 2008; Frisco, 2008] están inspirados en las neuronas que componen el sistema nervioso. Sus principales particularidades son el hecho de que todos los nodos de la red sean membranas simples, la existencia de un único tipo de objeto que modela los impulsos nerviosos y la asignación de estados, active e idle/closed, a las membranas, que modela la limitación biológica de recibir dos impulsos consecutivos.

Actualmente, dado el elevado número de sistemas P existentes, se ha originado una rama de la disciplina que persigue la abstracción de los distintos modelos, con el ánimo de simplificar el número de variedades existentes. Fruto de este esfuerzo son las redes de células que se describirán en la próxima sección o los kernel P systems [Gheorghe et al., 2012].

#### 2.1.1. Definición de un sistema de membranas

Tal y como se comentó anteriormente, existe una gran cantidad de sistemas P que se originan a partir de la definición original [Păun, 2000]. Actualmente, la tendencia es la de generar nuevos sistemas abstractos que reduzcan el número de modelos en la práctica. Así, el trabajo que se presenta en este documento está fundamentado en el entorno formal introducido en [Freund and Verlan, 2007], en el que se diseña un sistema de reescritura de multiconjuntos de clase genérica, que incluyen tanto a los sistemas P originales como a los estáticos basados en tejidos. Es por ello que en este capítulo se describen los aspectos más relevantes del citado trabajo. Para más detalles acerca de los sistemas P, se sugiere la lectura de la siguiente bibliografía: [Păun et al., 2010] y [Păun, 2002]. Para información más específica acerca del entorno formal mencionado sugerimos el trabajo citado [Freund and Verlan, 2007].

En primer lugar se presentarán algunos conceptos previos. Un alfabeto, V, es un conjunto finito o infinito de elementos denominados símbolos, o. Estos pueden combinarse para formar cadenas o palabras, w, de una determinada longitud, |w|, definiéndose como el número de elementos que forman la cadena. La palabra de longitud 0 se denota por  $\lambda$ . Del mismo modo, dada una cadena w, se emplea la notación  $o^k$  o ko con el fin de indicar el número de símbolos o contenidos en la cadena w, esto es, existen k objetos de tipo o en w. Por último, se define  $V^n$  como el conjunto de todas las cadenas de longitud n y  $V^*$  como el conjunto de todas las cadenas que pueden generarse usando los símbolos del alfabeto V.

El entorno basado en una red de células presentado en [Freund and Verlan, 2007] describe un sistema P, Π, del siguiente modo:

**Definición 1.** Un sistema P,  $\Pi$ , se define como una red de células de grado n,

$$\Pi = (n, V, w, Inf, R), \tag{2.1}$$

donde:

n es el número de células (membranas), o grado del sistema P.

V es el alfabeto de símbolos ( $o \in V$ , para cada objeto presente en el sistema).

w es una tupla  $(w_1, \ldots, w_n)$ , donde  $w_i$  corresponde al multiconjunto de objetos,  $o \in V$ , contenido en la célula i. También puede ser denominada como configuración inicial del sistema P, y denotada como  $C_0$ .

Inf representa qué símbolos son suministrados por el entorno. En este caso, una célula puede recibir una cantidad infinita de objetos. De ese modo, Inf =  $(Inf_1, ..., Inf_n)$ , donde  $Inf_i \subseteq V$ , determina qué elementos del alfabeto son recibidos por la célula i desde el entorno.

R es un conjunto finito de reglas,  $r_i$ , con la forma

$$(r_i: X \to Y; P, Q)$$

donde  $X \to Y$  son vectores de multiconjuntos,  $X = (x_1, \ldots, x_n)$ ,  $Y = (y_1, \ldots, y_n)$ ,  $x_i, y_i \in \langle V, \mathbb{N} \rangle$ ,  $1 \leq i \leq n$ , que pueden reescribirse como  $((x_1, 1), \ldots, (x_n, n)) \to ((y_1, 1), \ldots, (y_n, n))$ , indicando que los conjuntos  $x_i/y_i$ , ambos sobre V, son consumidos/añadidos, respectivamente, en la célula  $i, 1 \leq i \leq n$ . Semánticamente, en el momento de aplicación de la regla, el multiconjunto X, denominado también  $lhs(r_i)$  o parte izquierda de la regla (left-hand side), es consumido (deben existir suficientes recursos para que sea posible), mientras que el multiconjunto Y, denominado también  $rhs(r_i)$  o parte derecha (right-hand side), es producido o generado. Atendiendo a P y Q, son vectores de multiconjuntos, denominados condiciones de permiso y condiciones de prohibición, respectivamente, pero de la forma  $P = (p_1, \ldots, p_n)$  y  $Q = (q_1, \ldots, q_n)$ , con  $p_i, q_i \in V$ . Los multiconjuntos P y P0 afectan a la aplicabilidad de la regla de la siguiente forma: una regla

puede aplicarse (o es aplicable) si todos los elementos de P están contenidos en las células y ninguno de los elementos de Q están contenidos en ellas. Obviamente, es necesario que también existan todos los elementos que van a ser consumidos por la regla (es decir, el multiconjunto X).

Tomando como punto de partida la definición anterior, podemos definir, a su vez, el concepto de configuración y regla aplicable:

**Definición 2.** Dado un sistema P,  $\Pi = (n, V, w, Inf, R)$ , una configuración, C de  $\Pi$  es un multiconjunto  $C = \{u_i\}$  sobre V con  $(u_1, \ldots, u_n) \in \langle V, \mathbb{N} \rangle$ ,  $1 \leq i \leq n$ , indicando que la célula i contiene el multiconjunto de objetos  $u_i$ .

Informalmente, se puede definir una configuración de  $\Pi$  como el multiconjunto de objetos presentes en  $\Pi$  en un instante determinado, esto es, los recursos existentes en el sistema. La configuración inicial se denota como  $C_0$ .

**Definición 3.** Dado un sistema P,  $\Pi$ , y una configuración j-ésima tal que  $C_j = \{u_1, \ldots, u_n\}$ , se dice que una regla  $r = (X \to Y; P, Q)$  es aplicable si, y solo si, para todo i, tal que  $1 \le i \le n$ , se cumple:

- Para todo  $p \in p_i$ ,  $p \subseteq u_i$ . Esto es, todos los objetos de P se encuentran en la configuración  $C_i$ .

- Para todo  $q \in q_i$ ,  $q \nsubseteq u_i$ . Esto es, ningún objeto de Q se encuentra en la configuración  $C_j$ .

- $x_i \subseteq u_i$ . Existen suficientes recursos para que puedan ser consumidos por la regla.

La aplicación de r sobre  $C_i$  conlleva el siguiente resultado:

- Los objetos  $u_i \in X$  son consumidos, esto es, sustraídos de la configuración  $C_j$ , dando lugar a la configuración intermedia  $C'_j$ .

- Los objetos  $u_i \in Y$  son añadidos a la configuración intermedia  $C'_j$ , dando lugar a la siguiente configuración,  $C_{j+1}$ .

Algoritmo 2.1 Algoritmo de Marcado. Se describe con el objetivo de introducir el concepto de multiconjunto de reglas aplicables

```

Requiere: \Pi // Sistema P

Requiere: C = \{u_1, \ldots, u_n\} // Configuración

Requiere: \mathcal{R} = \{r_1, \dots, r_n\}, con r_i : X_i \to Y_i; P_i, Q_i // Multiconjunto de reglas

Devuelve: True si todas las reglas r \in \mathcal{R} pueden ser aplicadas simultáneamente,

False en caso contrario.

1. C' = C

2. para r_i \in R hacer

si r_i es aplicable sobre C' entonces

3.

C' = C' - X_i

4.

5.

sino

devolver False

6.

7.

fin si

8. fin para

9. devolver True

```

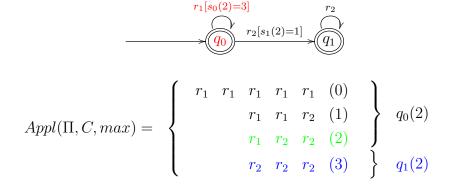

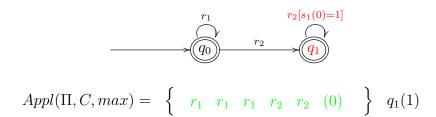

Con el propósito de definir el concepto de multiconjunto de reglas aplicables, es necesario introducir el Algoritmo de Marcado (Algoritmo 2.1), denotado como  $Marcado(\Pi, \mathcal{R}, C)$ , que determina si un multiconjunto de reglas es aplicable.

**Definición 4.** Dado un sistema P,  $\Pi$ , y una configuración,  $C = \{u_1, \ldots, u_n\}$ , se define un multiconjunto de reglas aplicables sobre C,  $\mathcal{R}$ , como aquel multiconjunto tal que  $Marcado(\Pi, \mathcal{R}, C) = True$  (Algoritmo 2.1). El conjunto de multiconjuntos aplicables sobre C se denota como  $Appl(\Pi, C)$ .

Dado un sistema P,  $\Pi$ , una configuración, C, y un conjunto  $Appl(\Pi, C)$ , es posible aplicar determinadas restricciones a los elementos del conjunto  $Appl(\Pi, C)$ , obteniendo como resultado un subconjunto de  $Appl(\Pi, C)$ . Estas restricciones se denominan modo de derivación, denotado como  $\delta$ . Se define el conjunto  $Appl(\Pi, C, \delta)$  como el conjunto de todos los multiconjuntos de reglas aplicables que verifican  $\delta$ . Nótese que Appl se encuentra asociada a un sistema  $\Pi$ , una configuración C y un modo de derivación  $\delta$ ; así como  $Appl(\Pi, C, \delta) \subseteq Appl(\Pi, C)$ .

Existen diversos modos de derivación, por lo que únicamente se comentarán los más relevantes o de mayor interés para el trabajo que se presenta: paralelismo maximal, paralelismo minimal y paralelismo maximal de conjuntos. Se remite al lector a la referencia bibliográfica [Freund and Verlan, 2007] para más detalles

acerca de los mismos.

El modo de derivación paralelismo maximal, denotado como max, fue el primer modo de derivación y el más utilizado hasta la fecha. De manera informal, requiere que todo multiconjunto de reglas aplicables, R, pueda incluirse en Appl si y solo si no existe otra regla, no incluida en R, que pueda ser aplicada; en otras palabras, si se eliminaran del sistema todos los objetos consumidos por las reglas de R, no quedarían recursos suficientes para aplicar ninguna regla más. Formalmente, el paralelismo maximal se define como:

**Definición 5.** El paralelismo maximal es aquel en el que,

$$Appl(\Pi, C, max) = \{ R \mid R \in Appl(\Pi, C) \ y$$

$$\nexists R' \in Appl(\Pi, C) \ tal \ que \ R' \supsetneq R \}$$

Atendiendo al modo de derivación paralelismo minimal, min, es necesario considerar el concepto de una partición de un multiconjunto de reglas, R, en subconjuntos disjuntos  $R_1$  a  $R_h$ . Para cada conjunto  $R' \subseteq R$ , se define ||R'|| como el número de conjuntos de reglas  $R_j$ , con  $1 \le j \le h$ , tal que  $R_j \cap R' \ne \emptyset$ . Informalmente, se puede definir como que todo multiconjunto R' debe contener al menos una regla de cada partición  $R_j$ ,  $1 \le j \le h$ .

Definición 6. El paralelismo minimal es aquel que,

$$Appl(\Pi, C, min) = \{R' \mid R' \in Appl(\Pi, C) \ y$$

$$\sharp R'' \in Appl(\Pi, C) \ tal \ que \ R'' \supseteq R',$$

$$(R'' - R) \cap R_j \neq \emptyset \ y \ R' \cap R_j = \emptyset$$

$$para \ cualquier \ j, 1 \leq j \leq h \}$$

Por último, el modo de derivación paralelismo maximal de conjuntos, denotado como smax, corresponde a la ejecución maximal paralela de las reglas, pero en la que estas no pueden aplicarse más de una vez.

**Definición 7.** El paralelismo maximal de conjuntos puede definirse formalmente

como sigue:

$$S_1 = \{ R \in Appl(\Pi, C) \mid |R|_{r_j} \le 1, 1 \le j \le |R| \},$$

$Appl(\Pi, C, smax) = \{ R \in S_1 \mid no \ existe \ R' \in S_1 \ tal \ que \ R' \supset R \},$

donde  $|R|_{r_j}$  indica la multiplicidad de la regla  $r_j$  en el conjunto R, esto es, el número de veces que aparece.

Nótese que el modo smax se corresponde con el modo  $min_1$  con una partición específica de reglas: el tamaño de la partición es |R| y cada partición  $p_j$  contiene exactamente una regla  $r_j \in R$ .

El modo de derivación determina en gran medida cómo evoluciona el sistema desde una configuración actual,  $C_i$ , a la siguiente,  $C_{i+1}$ . Esta evolución se denomina paso de computación o transición.

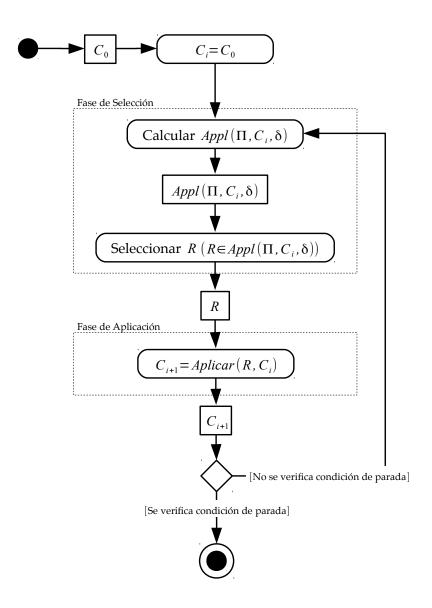

**Definición 8.** Dada una configuración  $C_i$  de un sistema P, notado como  $\Pi = (n, V, w, Inf, R)$ , con un modo de derivación  $\delta$ , una transición se divide en tres pasos. El primero consiste en calcular el conjunto  $Appl(\Pi, C_i, \delta)$ .

En el segundo paso, se debe elegir un elemento,  $\mathcal{R}$ , de este conjunto, según la semántica del sistema. Dado que se están considerando sistemas P no deterministas,  $\mathcal{R}$  será seleccionado empleando un método no determinista, como por ejemplo una distribución uniforme.

Por último, la transición finaliza aplicando el multiconjunto de reglas aplicables seleccionado sobre la configuración actual, con lo que se obtiene la próxima configuración, denotado como  $C_i \Longrightarrow_{(\Pi,\delta)} C_{i+1}$ .

Informalmente, la aplicación de un paso de computación marca la temporización del modelo, esto es, el paso de computación de un sistema P se correspondería con un ciclo de reloj en un sistema hardware síncrono.

Atendiendo a la semántica del modelo, la computación de un sistema P comienza en la configuración inicial,  $C_0$ , a partir de la cual el sistema P evoluciona aplicando transiciones de forma sucesiva, hasta alcanzar una configuración de parada (que verifique una condición de parada). Existen varias condiciones de parada, por lo que nuevamente se remite al lector a la bibliografía [Freund and Verlan,

2007; Păun et al., 2010] y se describen, de un modo informal, las más destacadas (para ello consideremos un sistema P,  $\Pi$ , con un modo de derivación  $\delta$ ):

Condición de parada total En esta condición, el sistema P alcanza una configuración C para la que  $Appl(\Pi, C, \delta) = \emptyset$ . Por lo tanto, el sistema converge hacia una configuración de parada total, al no existir los recursos suficientes para que se pueda aplicar un multiconjunto de reglas aplicables que verifiquen  $\delta$ .

Condición de parada adulta Esta condición considera que la ejecución del modelo  $\Pi$  ha finalizado cuando, al alcanzar una configuración  $C_i$ , para cualquier conjunto  $\mathcal{R} \in Appl(\Pi, C_i, \delta)$ , se origina la transición  $C_i \Longrightarrow_{(\Pi, \delta)} C_{i+1}$ , donde  $C_i = C_{i+1}$ . Por lo tanto, el sistema converge a una configuración de parada total adulta donde, independientemente del multiconjunto de reglas aplicables que se seleccione para ser aplicado, la configuración resultante no varía.

Desde un punto de vista práctico, puede contemplarse una condición de parada adicional que, aunque no se encuentre en la definición formal, suele ser utilizada en las implementaciones existentes. Se considera que la ejecución del sistema II ha finalizado bajo la condición de parada límite de transiciones tras la aplicación de un número fijo de transiciones. Nótese que se trata de una condición de parada artificial, e independiente del resultado del sistema P. Generalmente es usada en problemas de simulación, donde existe una correspondencia entre el tiempo o estados del problema simulado y las transiciones del sistema, por ejemplo, en simulaciones de procesos biológicos.

Una vez presentados los sistemas P, en el siguiente apartado se describe un ejemplo que permite al lector afianzar los conceptos relativos a este modelo de computación.

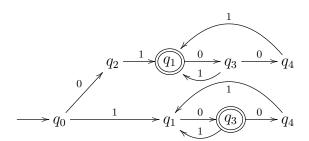

# 2.1.2. Modelo de computación con membranas. Un ejemplo

A continuación, se muestra un ejemplo de un sistema P estático que genera el conjunto de cuadrados  $\{n^2 \mid n \geq 1\}$  (Fig. 2.3). Se trata de una versión modificada por el doctorando del ejemplo del artículo fundacional [Păun, 2000]. En esta nueva versión el ejemplo original se ha adaptado al entorno de redes de células presentado

en el apartado anterior, y que será usado como referencia a lo largo de todo el documento.

En primer lugar se describe formalmente el sistema:

$$\Pi_{1} = (3, \{a_{2}, b_{1}, c_{1}, d_{2}, e_{3}, f_{1}, g_{1}\}, \{\emptyset, \{a_{2}, d_{2}\}, \emptyset\}, \emptyset, \{r_{1,1}, r_{1,2}, r_{1,3}, r_{1,4}, r_{2,1}, r_{2,2}, r_{2,3}\}),$$

donde

$$r_{1,1} = (a_{2} \rightarrow a_{2}b_{1}; \emptyset, \emptyset)$$

$$r_{1,2} = (a_{2} \rightarrow b_{1}g_{1}; \emptyset, \emptyset)$$

$$r_{1,3} = (d_{2} \rightarrow d_{2}^{2}; \{a_{2}\}, \emptyset)$$

$$r_{1,4} = (d_{2} \rightarrow f_{1}; \emptyset, \{a_{2}\})$$

$$r_{2,1} = (b_{1} \rightarrow c_{1}; \{g_{1}\}, \emptyset)$$

$$r_{2,2} = (c_{1} \rightarrow c_{1}e_{3}; \{f_{1}^{2}\}, \emptyset)$$

$$r_{2,3} = (f_{1}^{2} \rightarrow f_{1}; \emptyset, \emptyset)$$

Este sistema cuenta con un modo de derivación paralelo maximal, max, y sus reglas son elegidas de forma no determinista del conjunto  $Appl(\Pi, C_i, max)$ , siguiendo una distribución uniforme discreta.

Con el propósito de ilustrar un ejemplo de computación se considera que el sistema P evoluciona tal y como se muestra en la Fig. 2.3. Según la descripción formal, los símbolos contemplados son  $a_2$ ,  $b_1$ ,  $c_1$ ,  $d_2$ ,  $e_3$ ,  $f_1$  y  $g_1$ . Para facilitar la lectura, se han añadido subíndices a los objetos y reglas que indican a qué células hacen referencia. Del mismo modo, los cambios se han resaltado en color rojo. Así, se parte de una red de tres células o membranas, de las que la célula 2 es la única que contiene objetos, concretamente el multiconjunto  $\{a_2, d_2\}$ .

En el primer paso de computación (Trans. 1), se tiene que el conjunto  $Appl(\Pi, C_0, max) = \{\{r_{1,1}, r_{1,3}\}, \{r_{1,2}, r_{1,3}\}\}$ , ya que ninguna de las reglas  $r_{2,i}$  se pueden aplicar al no existir los recursos necesarios. Nótese que, aunque existen suficientes recursos para que la regla  $r_{1,4}$  pueda ser aplicada, su multiconjunto de

condición de prohibición,  $Q = \{a_2\}$ , lo impide. La elección del conjunto de reglas aplicables es no determinista, tal y como se especificó en la definición del sistema. Para este ejemplo se considera que se aplica el primer conjunto:  $\{r_{1,1}, r_{1,3}\}$ . Como resultado de la computación, se dobla el número de objetos  $d_2$ , se mantiene el número de objetos  $a_2$  y se produce un objeto  $b_1$ .

Para las siguientes transiciones, Trans. 2, 3 y 4, que dan lugar a las configuraciones  $C_2$ ,  $C_3$  y  $C_4$ , respectivamente, se considera la misma suposición de la Trans. 1 a la hora de escoger el multiconjunto de reglas aplicables. Únicamente son aplicables las reglas  $r_{1,1}$ ,  $r_{1,2}$  y  $r_{1,3}$ , originando  $Appl(\Pi, C_{i-1}, max) = \{\{r_{1,1}, r_{1,3}^{2^{i-1}}\}, \{r_{1,2}, r_{1,3}^{2^{i-1}}\}\}, 2 \le i \le 4$ . Se considera que en todas las transiciones se elige aplicar el multiconjunto  $\{\{r_{1,1}, r_{1,3}^{2^{i-1}}\}\}$ . Como resultado, en cada configuración se añade al sistema un objeto  $b_1$  y se dobla el número de objetos  $d_2$  existentes, mientras que el objeto  $a_2$  se mantiene sin cambio. Nótese que, aunque existen suficientes recursos para que  $r_{2,1}$  pueda ser aplicada, su multiconjunto de condición de permiso,  $P = \{g_1\}$ , lo impide.

Al llegar a la configuración  $C_4$ , se mantiene la situación anterior. Sin embargo, para la transición 5 se elegirá el multiconjunto  $\{r_{1,2}, r_{1,3}^{16}\}\}$ . Con ello, se elimina del sistema el objeto  $a_2$ , se añaden los objetos  $b_1$  y  $g_1$ , y se dobla el número de objetos  $d_2$ , dando lugar a  $C_5$ .

Los multiconjuntos de reglas aplicables varían para la transición 6. En este caso  $Appl(\Pi, C_5, max) = \{\{r_{1,4}^{32}, r_{2,1}^{5}\}\}$ , por lo que la elección es sencilla. No existen recursos suficientes para que ninguna de las otras reglas puedan ser aplicadas. Por otro lado, debido a que en la transición anterior se generó un objeto  $g_1$ , ahora sí es posible aplicar  $r_{2,1}$ . Como resultado se obtiene la configuración  $C_6$ , en la que los objetos  $d_2$  son sustituidos por  $f_1$ , y los  $b_1$  por  $c_1$ .

Para las siguientes cinco transiciones, desde la 7 hasta la 11, ambas inclusive, el conjunto  $Appl(\Pi, C_{i-1}, max) = \{\{r_{2,2}^5, r_{2,3}^{2^{11-i}}\}\}, 7 \leq i \leq 11$ , ya que no existen recursos para que se puedan aplicar el resto de reglas. En cada configuración generada, se incrementa en cinco unidades la multiplicidad del objeto  $e_3$ , al tiempo que se reducen a la mitad los objetos  $f_1$ , mientras que  $g_1$  y  $c_1$  permanecen constantes, dando lugar a las configuraciones  $C_7$ ,  $C_8$ ,  $C_9$ ,  $C_{10}$  y  $C_{11}$ .

Al alcanzar la configuración  $C_{11}$ , el número de objetos  $f_1$  es igual que la unidad. Por lo tanto, no son suficientes para que la regla  $r_{2,3}$  pueda ser aplicada.

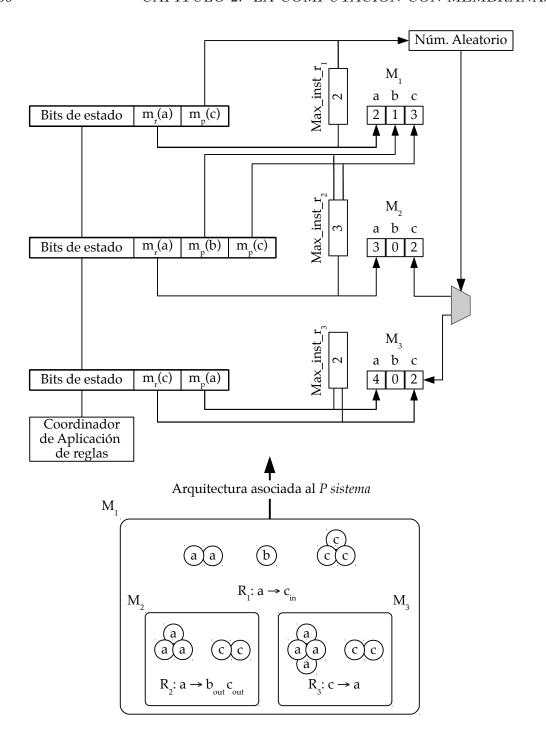

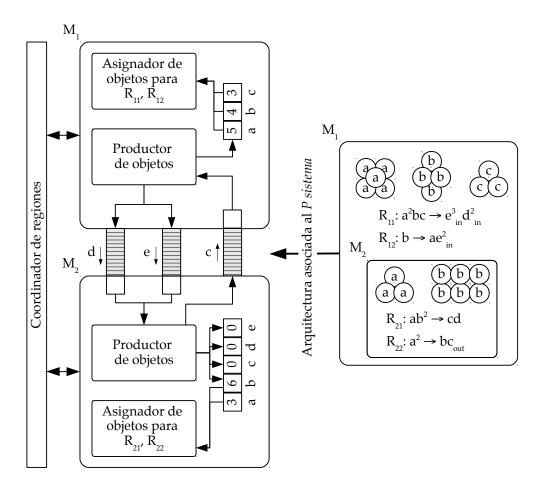

Fig. 2.3: Representación gráfica de la ejecución del sistema P de ejemplo. Se usa la notación x  $r_{i,j}$ , que es equivalente a  $r_{i,j}^x$ , y que representa que la regla  $r_{i,j}$  es ejecutada x veces.

Por otro lado, tampoco se verifica la condición de permiso P de la regla  $r_{2,2}$   $(P = \{f^2\})$ . En consecuencia, ninguna regla puede ser aplicada, obteniéndose que  $Appl(\Pi, C_{11}, max) = \emptyset$ . Es por ello que en esta computación, el sistema P ha alcanzado una configuración final,  $C_{11}$ , verificando una condición de parada total. El cuadrado resultante es la multiplicidad de objetos  $e_3$  presentes en el sistema, por lo que  $|c_1|^2 = |e_3|$ : 25 es el cuadrado de 5.

Nótese que, aunque los sistemas P sean no deterministas, desde el punto de vista del diseño es habitual emplear un no determinismo controlado, con el objetivo de simplificar las tareas y reducir el proceso de abstracción necesario, intentando que estos sean las más parecidos posibles a los requeridos para el diseño de los sistemas deterministas. En este caso, el no determinismo únicamente aparece de forma práctica en las transiciones 1-5, ya que en las siguientes  $|Appl(\Pi, C_i, max)| \in \{0, 1\}$ .