# CIRCUITO ASIC PARA ENLACES RAPIDOS DE COMUNICACIONES POR FIBRA OPTICA.

S. Toral, R.L. Millán, J.M.Quero y L.G.Franquelo

Dpto. de Ingeniería de Sistemas y Automática Escuela Superior de Ingenieros Avda. Reina Mercedes s/n 41012 Sevilla SPAIN

> E-mail: toral@gtex02.us.es FAX: 34-5-4629205

J. Pinilla y J. Serrano Sainco Jiménez Aranda 6 Sevilla

#### Resumen

El circuito integrado que aquí se describe ha sido diseñado con tecnología puramente digital, y tiene como función servir de interfase entre 8 enlaces rápidos de comunicaciones por fibra óptica y un procesador local que utiliza protocolo VME. Este trabajo se enmarca dentro del programa GAME y ha sido desarrollado en colaboración con la empresa SAINCO.

#### 1. Introducción.

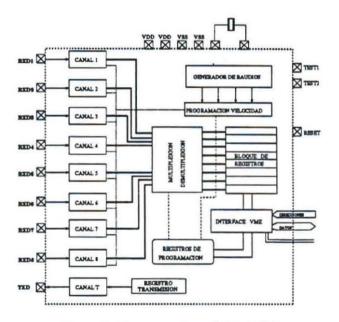

En la figura 1 se muestra el esquema general del circuito, el cual consta de 8 canales que reciben datos via línea serie procedente de un conjunto de equipos de control. El formato de las tramas recibidas en cada canal es fijo, y la velocidad de recepción es programable. El módulo de recepción de cada canal comprueba el formato de la información recibida, cabecera y trama, contemplando además posibles errores de time-out, desbordamiento y CRC. El circuito almacena internamente los datos procedentes de cada canal en registros de recepción, e intercambia esta información con un procesador local a través del VME. Así pues, se contemplan internamente 8 registros de estados y errores y 8 registros de mensajes o estaciones. Los registros de estados y errores poseen 5 bits asociados al canal y 3 asociados a la estación. Cada vez que se recibe un mensaje, tanto si es correcto como si no, se refrescan los bits correspondientes de los registros de estados y errores y , en el caso de que no estén enmascarados, se genera una salida de interrupción al exterior según un nivel programable. La interrupción desaparece

Figure 1: Esquema general del ASIC.

cuando el VME lee el registro de estados y errores que la causó.

El módulo señalado como bloque de registros es accesible tanto por los canales como por el VME. Esto obliga a la existencia de un autómata central de control supervisor encargado de evitar las posibles colisiones, y que debe ser lo suficientemente inteligente como para permitir accesos cruzados de los canales y el bus. El resto de los registros son accesibles únicamente por el bus y

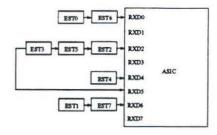

Figure 3: Ejemplo de esquema de conexiones de estaciones al integrado.

comprenden los registros de programación del integrado. También se incorpora un módulo de transmisión serie con objeto de poder transmitir un byte que haya sido escrito en un registro de transmisión.

# 2. Conexión de las estaciones.

El número de estaciones que pueden mandar información, a través de los cables de fibra óptica, es de 8. Dichas estaciones pueden ser conectadas en cascada a cualquiera de los canales de entrada como se muestra a modo de ejemplo la figura 3.

La restricción impuesta a la comunicación consiste en que una estación enviará información por un único canal físico de entrada, dado que en caso contrario dos mensajes recibidos simultáneamente por distintos canales pueden colisionar y degenerarse la información internamente en el ASIC a parte de generar alarmas de mensaje no leído y perdido. Este hecho no impide que las estaciones se conecten en lazo, siempre que se garantice externamente al ASIC que cada estación enviará la información en un sentido del lazo.

# 3. Descripción de módulos funcionales.

A continuación se comentan cada uno de los módulos existentes en el circuito. De todos ellos se ofrecen resultados de tiempo y área, así como simulaciones a nivel de puertas incluyendo retrasos. Todos los datos se refieren al circuito que lleva incluida la circuitería de test.

# 1. Canales de recepción

Los datos se reciben de manera asíncrona por una línea serie de alta velocidad con filtrado de entrada, mediante una interfase de comunicaciones interna al ASIC. La velocidad de recepción es programable, siendo la misma para todos los canales de recepción y para el canal de transmisión.

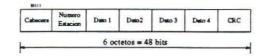

Cada trama enviada por una estación es fija y está constituida por 6 octetos como se aprecia en la figura 4. El primer octeto contiene codificado el número de la estación porque el canal físico de repción no sabe que estación le está enviando. A continuación vienen 4 octetos de datos y, por último, un octeto de CRC que cubre a todos los bytes anteriores.

Figure 4: Formato de una trama.

La trama correctamente recibida por un canal cualquiera (que ha sido previamente almacenada en un registro de desplazamiento) se almacena en un registro auxiliar antes de ubicarla en un registro direccionable por el bus VME. Este buffer de recepción permite ganar tiempo para el caso en el que el bus VME esté accediendo a una trama que mandó la misma estación anteriormente. La máquina de control del integrado pasará dicha información al registro correspondiente cuando no se esté accediendo por el VME a dichos registros. Por consiguiente, se dispone como mínimo de 48 ciclos de reloj para realizar el volcado sin que se genere error de desbordamiento interno. Para evitar que el canal quede bloqueado en la recepción de un mensaje incompleto, se incorpora al sistema un contador programable de tiempo (RTO), en el que se define el tiempo máximo de espera de la recepción de una trama completa. Hay pues que garantizar por el circuito que emite la información al ASIC que una trama completa va a ser enviada antes de que finalice dicha cuenta, y que el tiempo entre dos cabeceras consecutivas es mayor que este tiempo. Asociados a cada canal tenemos 5 bits de los registros de estados y errores (RECx), que se actualizan en el caso de una recepción incorrecta. Cada canal puede ser desactivado mediante la programación del Registro de Deshabilitación de Recepción (RDR). Si el bit x se encuentra a 1 se considera deshabilitada la recepción del canal x, por lo que no se recibirá ningún mensaje ni se modificará ningún bit del registro de estados y errores asociado.

Resultados (1 canal):

Area: 653683.625

Camino más largo: 17.10 ns.

Resultados (8 canales):

· Area: 5230251.000

· Camino más largo: 17.10 ns.

# 2. Módulo de tansmisión

Este módulo permite que se transmita un byte de información ajustándose a la velocidad de recepción programada. El byte transmitido se almacenará previamente en un registro de transmisión. Inmediatamente después de escribirse

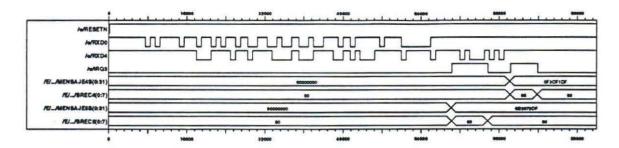

Figure 2: Simulación.

Figure 5: Generación de velocidad de recepción y transmisión.

la información en dicho registro se procede automáticamente a su transmisión, quedando a cero al finalizar ésta. Mientras exista información en el registro de transmisión, el bit de registro de transmisión vacío (RTV) estará a 1, pasando automáticamente a 0 cuando éste quede vacío.

#### Resultados:

Area: 94202.000

· Camino más largo: 13.01 ns.

# 3. Módulo de generación de velocidad

El esquema funcional del módulo de generación de la velocidad de comunicación en transmisión y recepción se muestra en la figura 5: En este bloque se genera la velocidad de recepción de las líneas serie a partir de un reloj externo de 16MHz. Inicialmente, este reloj se dividirá por la cantidad indicada en el registro de selección de velocidad de recepción (RVR). Posteriormente es dividido por 16 para obtener la velocidad de transmisión correspondiente. En el registro RVR se selecciona el divisor considerado como magnitud binaria. Dicho valor servirá como precarga de un registro interno que se decrementará con el reloj del sistema. Por ello, si se desea una velocidad de transmisión de 1MHz, se efectuará una precarga de cero (para que posteriormente sea dividido por 16). Para obtener la velocidad de 300 baudios, RVR se cargará con 0xD00.

En la tabla 1 se muestran algunos ejemplos de velocidades de transmisión conseguidas en función del valor programado en el registro RVR. Caso de emplear otro reloj se guardaría una proporcionalidad con esta tabla.

#### Resultados:

· Area: 85663.398

| RVR   | VEL. COM. (baud) |

|-------|------------------|

| 0     | 1M               |

| 0x068 | 9600             |

| 0x0D0 | 4800             |

| 0xD00 | 300              |

Table 1: Tabla de velocidades de transmisión.

Camino más largo: 16.45 ns.

#### 4. Módulo de interfase VME

Los registros internos del ASIC, tanto de datos recibidos como de programación, son accedidos externamente por un procesador local mediante una conexión a un bus que cumple el protocolo VME. Por ello, debe haber en el ASIC un bloque de interfase con el bus VME. Este bloque cumple las funciones básicas del protocolo, permitiendo la transmisión por octetos o por palabras de 16 bits. La interfase gobierna las señales AS, DSO, DS1, DATACK, datos D0-D15 y direcciones A0-A5.

El criterio seguido en la definición de la máquina es el de garantizar en todo momento la respuesta del integrado ante cualquier solicitud por parte del bus, o, lo que es lo mismo, que no exista ningún estado de espera en el que el funcionamiento de éste no dependa del diálogo con la CPU. Por ello, los datos almacenados en los registros auxiliares de los canales y en espera de pasar a la memoria se volcarán a sus registros correspondientes cuando no exista acceso por el bus a dichos registros.

#### Resultados:

Area: 77341.398

Camino más largo: 11.22 ns.

## 5. Direccionamientos

Todos los registros del integrado son accesibles por el bus en modos de lectura y escritura. Esto facilita el testeo del circuito. Los accesos se pueden realizar con el bus completo de 16 bits, o bien empleando el byte más o menos significativo, en función de los valores de DS0 y DS1.

#### Resultados:

Area: 710884.937

Camino más largo: 17.23 ns.

## 6. Registros

Existen dos grandes grupos de registros: los registros de mensajes y los registros de estados y errores, accesibles por los canales de recepción y por el bus, y los registros de programación del integrado, accesibles únicamente por el bus. Los registros de mensajes constan de 32 bits y almacenan los 4 bytes intermedios del mensaje recibido. Los registros de estados y errores tienen información, por un lado relativa al canal que recibe, y por otra relativa a la estación que almacena. Veamos el significado de los bits:

- Bit 0: Mensaje nuevo no leído.

- Bit 1: Mensaje nuevo no leído y distinto del anterior.

- Bit 2: Desbordamiento a nivel de estación. Se escribe un mensaje en una estación sobreescribiendo el anterior sin que previamente hubiese sido leído por el bus.

- Bit 3: Error de cabecera.

- Bit 4: Error de trama

- Bit 5: Error de CRC.

- · Bit 6: Error de time-out.

- Bit 7: Error de desbordamiento a nivel de canal. Se recibe un mensaje por un canal y, antes de que sea atendida, se sobreescribe el buffer con un nuevo mensaje.

Los registros de programación establecen el funcionamiento general del integrado:

- RMI0...7. Registros de máscaras de interrupción. Un 1 almacenado en el bit i del registro RMIx indica que la interrupción provocada por la activación de uno de los bits del registro de estados y errores no está habilitada. Inicialmente, todas las interrupciones estarán enmascaradas.

- RTO. Registro de Time-Out.Se precarga con 14 ciclos de reloj de transmisión, que equivalen a un incremento del 20% del doble del tiempo mínimo de recepción de un mensaje completo.

- RDR. Registro de deshabilitación de recepción. Si el bit x se encuentra a 1 se considera deshabilitada la recepción del canal x,

por lo que no se recibirá ningún mensaje ni se modificará ningún bit del registro de estado de dicho canal.

- RTD. Registro de transmisión. Se trata del byte a transmitir inmediatamente después de escribirse la información en dicho registro.

- RVR. Registro de velocidad de recepción. En el registro RVR se selecciona el divisor considerado como magnitud binaria.

- RCR. Registro de CRC. El polinomio generador del CRC es 0x85.

- RTV. Registro de transmisión vacío. Mientras exista información en el registro de transmisión, el bit RTV estará a 1, pasando automáticamente a 0 cuando éste quede vacío.

## Resultados:

• Area: 2485450.500

Camino más largo: 23.05 ns.

## 7. Autómata central de control

Por sencillez a la hora de realizar el test, todos los registros del integrado son accesibles en modo lectura y escritura. De aquí surge la necesidad de evitar el acceso simultáneo del bus y las UARTs. El problema se ha resuelto mediante un sistema de semáforos, de modo que aquel que inicie un ciclo de lectura (en su caso) o escritura sobre cualquier registro del integrado accesible por ambos, impedirá al otro su acceso, debiendo esperar éste su turno. Existe un autómata central de control que se encarga de ésta y otras tareas:

- Chequear secuencialmente las ocho UARTs por si alguna de ellas ha tenido un error en la recepción o bien ha validado un mensaje.

- Dar las señales de control necesarias a los multiplexores y demultiplexores.

- Dar las señales de captura a todos los registros del integrado.

- Resetear los registros de estados y errores cuando el bus accede a ellos.

- Llevar el cómputo de posibles desbordamientos.

- Establecer el sistema de semáforos.

Por ejemplo, si el autómata le da paso a una UART para que escriba en una estación, y, justo después, el bus quiere acceder en un ciclo de escritura, éste último deberá esperar a que finalice la UART. Tan sólo se tratará de unos cuantos ciclos de reloj, por lo que no resulta demasiado problemático. Por contra, el autómata es lo suficientemente inteligente como para permitir accesos

cruzados. En todo momento conoce dónde quiere escribir la UART (ya sea mensaje o error de canal) y dónde quiere acceder el bus. De no existir colisión, da paso a ambos evitando ralentizar el funcionamiento. Veamos a continuación qué hipotéticos casos se han contemplado:

Supongamos que por el canal 3 llega un mensaje destinado a la estación 7. Los registros críticos en cuanto a colisión serán el registro de 32 bits correspondiente a la estación 7 y el registro de estados de 3 bits de esa misma estación. En cambio, el registro de errores del canal 3 no opondrá ningún impedimento para su escritura, pues el mensaje que ha llegado fue validado (figura 6).

Figure 6: Colisiones.

Si ahora lo que llega es un mensaje erróneo, tan sólo el registro de errores asociado al canal 3 será crítico, en tanto que el resto será accesible (figura 7).

Figure 7: Colisiones.

#### Resultados:

• Area: 369181.406

- · Camino más largo: 18.76 ns.

- 4. Condiciones iniciales. Tras recibir una señal de RESET, el integrado tomará la siguiente situación inicial:

- Todas las interrupciones están enmascaradas.

- 2. Todos los canales tendrán inhibida la recepción.

- 3. Todos los bits de error a cero.

- El vector de interrupciones tomará el valor 15 en decimal.

- El registro de time-out de recepción se precarga con 144 ciclos de reloj de transmisión, que equivalen a un incremento del 20

- 6. El polinomio generador de CRC es 0x85.

- 7. La velocidad de transmisión es de 9600 baudios.

- Bit indicador de registro de transmisión vacío (RTV) a cero.

# 5. Resultados globales del integrado.

Los siguientes resultados suponen una estimaciones en tiempo y en área. Aparte del área ocupada y los retrasos introducidos por las puertas del esquemático, la herramienta utilizada realiza unas estimaciones respecto al cableado, lo que nos ofrece los siguientes resultados:

Area: 369181.406

· Camino más largo: 18.76 ns.

## 6. Conclusiones.

Las herramientas utilizadas en la realización del integrado han sido VHDL (Synopsys), CADENCE y el emulador hardware METASYSTEM. Se han empleado las librerías de ES2, con una tecnología de  $0.7\mu$ . El reloj de funcionamiento es de  $16 \mathrm{MHz}$ .

VHDL es un stándard IEEE que nos permite la realización de complejas funcionalidades a partir de un alto nivel de abstracción. Sus potentes herramientas de síntesis nos permiten establecer restricciones de tiempo y área, fundamentalmente. En nuestro caso, la limitación fundamental ha sido de tiempo, dada la elevada velocidad de trabajo. Por lo que respecta al proceso de diseño, seãlaremos que los lenguages de descripción hardware, como VHDL, nos permiten hacer descripciones independientes de la tecnología; es decir, podemos realizar simulaciones a partir del código, lo que nos permite una prematura verificación de la funcionalidad. Así pues, en primer lugar se realiza una verificación de la funcionalidad a nivel de código. Si ésta es correcta, se lleva a cabo la síntesis, comprobando el estricto cumplimiento

de las restricciones impuestas. Finalmente, se efecúan simulaciones a partir de los esquemáticos generados e incluyendo los retrasos de puertas. Evidentemente, estas simulaciones sí que dependen de la tecnología. Este proceso se lleva a cabo manteniendo la jerarquía en el diseño, para facilitar futuras etapas.

CADENCE se usa para la realización del placement y routing, así como de simulaciones admitidas por el fabricante. Antes del rutado, CADENCE proporciona unas estimaciones de fan-out. Nuestra experiencia demuestra que estas estimaciones se encuentran del lado de la seguridad, y, siempre que no sean demasiado abultadas, nos causarán errores en el resultado final.

El emulador hardware ha servido para probar funcionalidades complejas de reproducir en simulaciones en pantalla.

## REFERENCES

- [1] VHDL Compiler Reference. Synopsys, Inc. 1994.

- [2] Design Analyzer Reference Manual. Synopsys, Inc. 1994.

- [3] Design Compiler Family Reference. Synopsys, Inc. 1994.

- [4] Test Compiler Reference. Synopsys, Inc. 1994.

- [5] Library Databook. European Silicon Structures. 1995.

- [6] META User Guide V1.1. Meta Systems. 1994.

- [7] ES2 Cadence Design Kit User Guide. European Silicon Structures. 1995.