## Adaptive Miller Compensation under Extreme Load Variations in IC-LDO regulators

José María Hinojo, Clara Luján-Martínez, and Antonio Torralba Electronic Engineering Department Universidad de Sevilla Sevilla, Spain {jhinojo, cilujan, torralba}@us.es

Abstract— A new frequency compensation technique for output buffers able to manage a wide range of loads, is proposed in this paper. To improve the stability, this technique implements a variable zero nulling resistor in a classical Miller compensation. A replica circuit senses the operating region of the output stage and generates the required value of the nulling resistor. In order to validate the effectiveness of the proposed technique, an Internally Compensated Low Dropout (IC-LDO) regulator based on a classical topology has been chosen and designed in a 65 nm standard CMOS technology. Results show that the proposed compensation scheme improves the Phase Margin of the IC-LDO regulator keeping it higher than 54° for load currents from 0 to 100mA at the cost of increasing only 10% the total quiescent power consumption and negligible area.

Keywords— Adaptive compensation, low dropout (IC-LDO) regulator, stability, Miller compensation.

## I. INTRODUCTION

Stability has been a key concern in electronic design, as it determines the performances of linear feedback systems [1]. In modern electronics, the stability has become a technical challenge as, in addition to the high performance and efficiency that the market demands for electronic systems, the designer faces the constraints coming from the downscaling of CMOS technologies. This is of especial interest in the design of low power, highly efficient buffers, which should be able to handle the wide range of loads required for the power supply and input/output circuitry [2].

A significant circuit intended to efficiently handle a wide range of loads with low power consumption is the Internally Compensated Low Dropout (IC-LDO) regulator, whose stability is a major issue. These circuits play a key role in power management and in System-on-Chip designs, and they are attracting a lot of attention for new compensation methods [3]–[7]. IC-LDO regulators require small area, low power consumption, low supply voltage, good line and load regulation, short settling time and high efficiency and, at the same time, they are required to remain stable under extreme variations of the line voltage ( $V_{\rm IN}$ ), load current ( $I_{\rm LOAD}$ ) and load capacitance ( $C_{\rm LOAD}$ ).

This paper proposes an adaptive and continuous compensation scheme that adjusts the value of the nulling resistor of a Miller-based compensation scheme to keep the nulling zero close to the unit gain frequency (UGF), regardless

the working conditions. As a proof of concept, this technique has been applied to a classical IC-LDO regulator topology, which has been designed and implemented in a standard 65 nm CMOS technology.

The document is organized as follows: first of all, a brief review of different compensation schemes applied to IC-LDO regulators is made in Section II. Then, the proposed compensation method is described in Section III. Section IV and V focus on an IC-LDO regulator designed to evaluate the proposed technique, showing both, post-layout simulations and experimental results. Finally, some conclusions are drawn in Section VI.

## II. REVIEW OF COMPENSATION SCHEMES APPLIED TO IC-LDO REGULATORS FOR STABILITY IMPROVEMENT

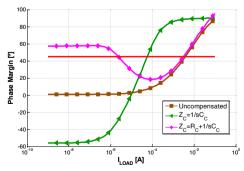

In order to enhance the Phase Margin (PM), a pole-splitting technique such as the Miller-based compensation scheme can be used. It is well known that the Miller compensation introduces a Right-Half-Plane (RHP) zero, which depends on the ratio between gm<sub>PASS</sub>, and the total Miller capacitance C<sub>gd,PASS</sub>+C<sub>C</sub>. The negative effects of this RHP zero can be neutralized by means of a nulling resistor (R<sub>C</sub>) in series with the compensation capacitor. Unfortunately, as both, gm<sub>PASS</sub> and C<sub>gd,PASS</sub>, are strongly dependent on I<sub>LOAD</sub>, the value of R<sub>C</sub> that stabilizes the IC-LDO regulator for zero-load current is not adequate for middle-range load currents, as it is shown in Fig. 1 where the variation of the PM versus I<sub>LOAD</sub> in the case of an uncompensated IC-LDO regulator, and a compensated Miller version with, and without, ZNR. It can be observed that there is range of values of  $I_{\text{LOAD}}$  where the PM is not large enough. Consequently, the IC-LDO regulator is not stable for the whole range of I<sub>LOAD</sub>.

Fig. 1. PM variation vs  $I_{LOAD}$  for an uncompensated IC-LDO regulator, and Miller compensated IC-LDO regulator with, and without, ZNR.

TABLE IV. COMPARISON OF RECENTLY PUBLISHED IC-LDO REGULATORS

|                                             |                    | [4]    | [5]     | [6]     | [7]     | [8]   | [14]    | [13]    | This Wo | rk     |

|---------------------------------------------|--------------------|--------|---------|---------|---------|-------|---------|---------|---------|--------|

| Technology                                  | [µm]               | 0.065  | 0.35    | 0.18    | 0.065   | 0.35  | 0.6     | 0.5     | 0.065   |        |

| $V_{IN}$                                    | [V]                | 1.2    | 1.2-1.5 | 1.1-1.5 | 1.2     | 1.2   | 1.5-4.5 | 1.4-4.2 | 1.0-1.2 |        |

| $V_{OUT}$                                   | [V]                | 1.0    | 1.0     | 1.0     | 1.0     | 1.0   | 1.3     | 1.21    | 0.8     |        |

| $V_{DROPOUT}$                               | [mV]               | 200    | 200     | 100     | 200     | 200   | 200     | 200     | 200     |        |

| $I_{LOAD,max}$                              | [mA]               | 50     | 50      | 50      | 100     | 50    | 100     | 100     | 100     |        |

| $I_q _{max}$                                | [µA]               | 23.7   | 45      | 54      | 82.4    | 65    | 38      | 45      | 17.88   |        |

| $C_{LOAD}$                                  | [pF]               | 10000  | 1000    | 100     | 100     | 100   | 100     | 105     | 100     |        |

| Area                                        | [mm <sup>2</sup> ] | -      | 0.263   | -       | 0.017   | 0.350 | 0.307   | 0.400   | 0.0436  |        |

| On-chip Capacitor                           | [pF]               | 8.0    | 41      | 5       | 4.5     | 7     | 12      | 67      | 18.48   |        |

| Settling time                               | [µs]               | 1.65   | 5       | 2       | 6       | 15    | 2       | 4       | 17.05   |        |

| $\Delta V_{OUT}$ varying $V_{IN}$           |                    |        |         |         |         |       |         |         |         |        |

| <ul> <li>maximum</li> </ul>                 | [mV]               | -      | 23      | -       | 8.91    | 90    | 160     | -       | 78.4    |        |

| • minimum                                   | [mV]               | -      | -12     | -       | -10.63  | -10   | -1.5    | -       | -49.3   |        |

| $\Delta V_{IN}/tr$                          | [mV/µs]            | -      | 1/0.1   | -       | 0.2/10  | 1/1   | 3/6     | -       | 0.2/0.1 |        |

| ΔV <sub>OUT</sub> varying I <sub>LOAD</sub> |                    |        |         |         |         |       |         |         |         |        |

| • maximum                                   | [mV]               | 19     | 47      | 100     | 0       | 80    | 100     | 70      | 242     | 96.39  |

| • minimum                                   | [mV]               | -58    | -48     | -80     | -68.8   | -80   | -90     | -70     | -336    | -39.36 |

| $\Delta I_{LOAD}/tr$                        | [mA/µs]            | 50/0.1 | 100/0.1 | 50/0.1  | 100/0.3 | 50/1  | 90/0.5  | 49/1    | 100/0.1 | 90/0.5 |

| Load Regulation                             | [µV/mA]            | -      | 250     | -       | 300     | -     | -       | 408     | 780.57  |        |

| Line Regulation                             | [mV/V]             | 8.8    | 0.098   | -       | 4.7     | -     | -       | -       | 26.5    |        |

| FOM                                         | [fs]               | 7300   | 2331    | 388.80  | 56.69   | 416   | 72.20   | 63000   | 103.35  | 24.37  |

In order to validate the effectiveness of this technique, an IC-LDO regulator was designed. It is a representative example, as these cells suffer, not only from large variations of the load current, but also from variations in the input voltage and in the output capacitance. When the proposed technique is particularized to IC-LDO regulators, it results in a simple, robust and power-efficient solution. This circuit has been designed and manufactured in a 65 nm standard CMOS technology. The measured value of a typical FOM shows that it is in the state of the art. Even more, additional transient response enhancement techniques could also be applied to improve the transient response, although it is beyond the interest of this paper. Regarding current and area consumption, the circuitry required by the proposed compensation method only requires 10% of the total quiescent consumption and negligible area.

## REFERENCES

- [1] P. R. Gray, P. J. Hurst, S. H. Lewis, and R. G. Meyer, *Analysis and Design of Analog Integrated Circuits*. Wiley, 2001.

- [2] D. C. Daly, L. C. Fujino, and K. C. Smith, "Through the Looking Glass -- The 2017 Edition: Trends in Solid-State Circuits from ISSCC," *IEEE Solid-State Circuits Magazine*, vol. 9, no. 1, pp. 12–22, 2017.

- [3] Y. Kim and S.-S. Lee, "A Capacitorless LDO Regulator With Fast Feedback Technique and Low-Quiescent Current Error Amplifier," Circuits Syst. II Express Briefs, IEEE Trans., vol. 60, no. 6, pp. 326– 330, 2013

- [4] X. L. Tan, K. C. Koay, S. S. Chong, and P. K. Chan, "A FVF LDO Regulator With Dual-Summed Miller Frequency Compensation for Wide Load Capacitance Range Applications," *Circuits Syst. I Regul. Pap. IEEE Trans.*, vol. 61, no. 5, pp. 1304–1312, May 2014.

- [5] G. Giustolisi, G. Palumbo, and E. Spitale, "Robust Miller Compensation With Current Amplifiers Applied to LDO Voltage Regulators," *Circuits Syst. I Regul. Pap. IEEE Trans.*, vol. 59, no. 9, pp. 1880–1893, Sep. 2012.

- [6] L.-G. Shen, Z.-S. Yan, X. Zhang, and Y.-F. Zhao, "A capacitor-less low-dropout regulator for SoC with bi-directional asymmetric buffer," in *Circuits and Systems*, 2008. ISCAS 2008. IEEE International Symposium on, 2008, pp. 2677–2680.

- [7] S. Chong and P. K. Chan, "A 0.9-\textmu A Quiescent Current Output-Capacitorless LDO Regulator With Adaptive Power Transistors in 65-nm CMOS," Circuits Syst. I Regul. Pap. IEEE Trans., vol. 60, no. 4, pp. 1072–1081, 2013.

- [8] R. J. Milliken, J. Silva-Martinez, and E. Sanchez-Sinencio, "Full On-Chip CMOS Low-Dropout Voltage Regulator," Circuits Syst. 1 Regul. Pap. IEEE Trans., vol. 54, no. 9, pp. 1879–1890, Sep. 2007.

- [9] C. Zhan and W. H. Ki, "Output-capacitor-free adaptively biased low-dropout regulators," 2010 IEEE Int. Conf. Electron Devices Solid-State Circuits, EDSSC 2010, vol. 57, no. 5, pp. 1017–1028, 2010.

- [10] A. Maity and A. Patra, "Tradeoffs Aware Design Procedure for an Adaptively Biased Capacitorless Low Dropout Regulator Using Nested Miller Compensation," *Power Electron. IEEE Trans.*, vol. 31, no. 1, pp. 369–380, 2016.

- [11] G. Palumbo and S. Pennisi, Feedback Amplifiers: Theory and Design. Springer US, 2007.

- [12] R. G. H. Eschauzier and J. Huijsing, Frequency Compensation Techniques for Low-Power Operational Amplifiers. Springer US, 2013.

- [13] A. Garimella, M. W. Rashid, and P. M. Furth, "Reverse Nested Miller Compensation Using Current Buffers in a Three-Stage LDO," *Circuits Syst. II Express Briefs, IEEE Trans.*, vol. 57, no. 4, pp. 250–254, 2010.

- [14] K. N. Leung and P. K. T. Mok, "A capacitor-free CMOS low-dropout regulator with damping-factor-control frequency compensation," *Solid-State Circuits*, *IEEE J.*, vol. 38, no. 10, pp. 1691–1702, Oct. 2003.

- [15] C. C. Enz, F. Krummenacher, and E. A. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications," *Analog Integr. Circuits Signal Process.*, vol. 8, no. 1, pp. 83–114, 1995.

- [16] E. A. Vittoz, "Pseudo-resistive networks and their applications to analog collective computation," in *Artificial Neural Networks --- ICANN'97: 7th International Conference Lausanne, Switzerland, October 8--10, 1997 Proceedings*, W. Gerstner, A. Germond, M. Hasler, and J.-D. Nicoud, Eds. Berlin, Heidelberg: Springer Berlin Heidelberg, 1997, pp. 1131–1150.

- [17] C.-J. Park, M. Onabajo, and J. Silva-Martinez, "External Capacitor-Less Low Drop-Out Regulator With 25 dB Superior Power Supply Rejection in the 0.4-4 MHz Range," *Solid-State Circuits, IEEE J.*, vol. 49, no. 2, pp. 486–501, Feb. 2014.

- [18] P. Hazucha, T. Karnik, B. A. Bloechel, C. Parsons, D. Finan, and S. Borkar, "Area-efficient linear regulator with ultra-fast load regulation," *Solid-State Circuits, IEEE J.*, vol. 40, no. 4, pp. 933–940, 2005.