## IC-LDO Regulator with 600 nA Quiescent Current Using a Class AB Buffer

José María Hinojo, Clara Luján-Martínez, Enrique López-Morillo, and Antonio Torralba

> Electronic Engineering Department Universidad de Sevilla Sevilla, Spain {jhinojo, cilujan, yeorwo, torralba}@us.es

Abstract— An ultra-low power Internally Compensated Low-Dropout (IC-LDO) regulator with a quiescent current consumption lower than 600 nA is proposed. It is based on the classical IC-LDO topology, which has been modified to include a class AB buffer between the output of the error amplifier and the gate of the pass transistor (MPASS). This way, a fast charge/discharge of its parasitic capacitance is achieved with the inherent low quiescent power consumption of class AB circuits. The proposed regulator has been fabricated in a standard 0.18-µm CMOS technology. Experimental results show that the proposed regulator has a Figure of Merit in the state of the art.

Keywords— Internally Compensated Low-Dropout Regulator, ultra-low power

## I. INTRODUCTION

Power management systems have become very important in recent years, especially in the design of System-on-Chips (SoCs) for low power applications [1], [2]. Of special interest is their use in Wireless Sensor Networks (WSNs) [3], where the sensor nodes are usually powered by batteries and, in some cases, the energy they consume is harvested from the environment [4]. In this scenario, reducing the energy consumption of the blocks that build these nodes means prolonging the lifetime of the batteries, and/or reducing the requirements of the energy harvester [5].

Within the power management circuits, one of the most critical blocks is the voltage regulator, as it supplies sensitive subsystems such as RF stages or analog-to-digital converters. When the main design requirement for a Low-Dropout (LDO) regulator is ultra-low-power consumption (for instance, a quiescent current lower than 1 µA), two critical aspects must be taken into account. Firstly, extremely low bias currents make the output impedance of the error amplifier (as well as that of the intermediate stages) very high. This translate into low frequency poles that degrade the frequency response and, hence, the stability. Compensation techniques based on active blocks, like those presented in [6], [7] should be avoided due to the extra power they consume. Secondly, extremely low quiescent currents slow down the transient response, as they are not sufficient to rapidly charge / discharge the high gate capacitance of the pass transistor.

Jaime Ramírez-Angulo

Klipsch School of Electrical and Computer Engineering

New Mexico State University

Las cruces, New Mexico, USA

jairamir@nmsu.edu

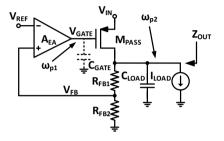

Fig. 1. Classical topology for an IC-LDO regulator.

In order to deal with this limitations, several approaches have been proposed in the literature to achieve high performance in ultra-low power internally compensated LDO (IC-LDO) regulators. They include adaptive biasing [8]–[10], splitting of the pass transistor [11], push-pull stages [12], and RC coupling [13], [14]. Attending to these solutions, a low quiescent power buffer placed between the error amplifier (EA) and the pass transistor (M<sub>PASS</sub>) is appropriate to improve the stability and transient response. Based on this idea, a new Internally Compensated Low-Dropout (IC-LDO) regulator with ultra-low quiescent power consumption is presented. It is based on the classical LDO topology, Fig. 1, where a class AB buffer, placed at the output of the EA, provides the large currents necessary to charge / discharge the parasitic gate capacitance of M<sub>PASS</sub> (C<sub>GATE</sub>) with a low consumption.

This paper is organized as follows: the proposed ultra-low power IC-LDO regulator is presented in Section II, while its frequency response is studied in section III. Experimental results are shown in Section IV. Finally, some conclusions are drawn in Section V.

## II. PROPOSED IC-LDO REGULATOR

The proposed LDO regulator is shown in Fig. 2. As it can be seen in Fig. 3, the EA consists of a Folded Cascode operational amplifier, including the in-built  $A_0$  and  $A_1$  amplifiers. They are low voltage, high signal range amplifiers [15] that improve the open-loop gain of the whole system. For the sake of completeness, their schematics are reproduced in Fig. 4.a and Fig. 4.b, respectively.

TABLE III. COMPARISON OF RECENTLY PUBLISHED LDO REGULATORS

|                                             |         | [8]                    | [9]       | [10]      | [11]    | [19]     | This Work |

|---------------------------------------------|---------|------------------------|-----------|-----------|---------|----------|-----------|

| Technology                                  | [µm]    | 0.35                   | 0.35      | 0.11      | 0.065   | 0.35     | 0.18      |

| V <sub>IN</sub>                             | [V]     | 1.0-1.8                | 2.5-4.0   | 1.8-3.8   | 1.2     | 1.28-3.3 | 1.164-1.8 |

| V <sub>OUT</sub>                            | [V]     | 0.9                    | 2.35      | 1.6-3.6   | 1.0     | 1.1      | 1.0       |

| $V_{DROPOUT}$                               | [mV]    | 100                    | 150       | 200       | 200     | 180      | 164       |

| $I_{LOAD,max}$                              | [mA]    | 50                     | 100       | 200       | 100     | 100      | 100       |

| $I_q _{max}^{ a}$                           | [µA]    | 1.2                    | 7.0       | 41.5      | 82.4    | 25       | 0.585     |

| $C_{LOAD}$                                  | [pF]    | 1e2                    | 1e2       | 4e1       | 1e2     | 1e2      | 1e2       |

| Settling time                               | [µs]    | 4.0                    | 0.15      | 0.65      | 6.00    | 1.4      | 731.6     |

| ΔV <sub>OUT</sub> varying V <sub>IN</sub>   |         |                        |           |           |         |          |           |

| Maximum                                     | [mV]    | 200 <sup>d</sup>       | 196       | _e        | 8.91    | 20       | 246       |

| Minimum                                     | [mV]    | -120 <sup>d</sup>      | -183      | _e        | -10.63  | 0        | -281      |

| $\Delta V_{IN}/t_r^{f}$                     | [mV/µs] | 0.5/1 <sup>d</sup>     | 0.5/0.5   | _e        | 0.2/10  | 1/100    | 0.6/1     |

| ΔV <sub>OUT</sub> varying I <sub>LOAD</sub> |         |                        |           |           |         |          |           |

| Maximum                                     | [mV]    | 200 <sup>d</sup>       | 231       | 200       | 0.00    | 31       | 274       |

| Minimum                                     | [mV]    | -425 <sup>d</sup>      | -243      | -385      | -68.8   | -80      | -368      |

| $\Delta I_{LOAD}/t_r^f$                     | [mA/µs] | 49.50/0.2 <sup>d</sup> | 99.95/0.5 | 199.5/0.5 | 100/0.3 | 100/0.5  | 99.9/1    |

| Load Regulation                             | [µV/mA] | 148                    | 80        | 108       | 300     | 190      | 85.44     |

| Line Regulation                             | [mV/V]  | 3.625                  | 1.0       | 8.9       | 4.70    | _e       | 2.50      |

| FOM                                         | [fs]    | 30                     | 33.18     | 24.28     | 56.7    | 27.75    | 3.76      |

a. aWorst-case, bEffective area, cPADS are included, dEstimation based on published results, Not available, and tr.: Rise time

the pass transistor to provide the large currents required to ensure a good transient response while maintaining ultra-low quiescent power consumption. Experimental results show that the proposed regulator features, in the authors' knowledge, the best Figure of Merit of the IC-LDO regulators published to date.

## REFERENCES

- D. D. Buss, "Technology in the Internet age," in Solid-State Circuits Conference, 2002. Digest of Technical Papers. ISSCC. 2002 IEEE International, 2002, vol. 1, pp. 18-21 vol.1.

- [2] D. El-Damak and A. P. Chandrakasan, "A 10 nW 1µW Power Management IC With Integrated Battery Management and Self-Startup for Energy Harvesting Applications," IEEE J. Solid-State Circuits, vol. 51, no. 4, pp. 943–954, 2016.

- I. F. Akyildiz, W. Su, Y. Sankarasubramaniam, and E. Cayirci, "A survey on sensor networks," Commun. Mag. IEEE, vol. 40, no. 8, pp. 102-114, 2002

- [4] N. Ansari and T. Han, "Freenet: Spectrum and energy harvesting wireless networks," Network, IEEE, vol. 30, no. 1, pp. 66-71, 2016.

- M. Alioto, "Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial," IEEE Trans. Circuits Syst. I Regul. Pap., vol. 59, no. 1, pp. 3–29, 2012.

- [6] K. N. Leung and P. K. T. Mok, "A capacitor-free CMOS low-dropout regulator with damping-factor-control frequency compensation," Solid-State Circuits, IEEE J., vol. 38, no. 10, pp. 1691–1702, Oct. 2003.

- R. J. Milliken, J. Silva-Martinez, and E. Sanchez-Sinencio, "Full On-Chip CMOS Low-Dropout Voltage Regulator," *Circuits Syst. I Regul. Pap. IEEE Trans.*, vol. 54, no. 9, pp. 1879–1890, Sep. 2007.

- [8] T. Y. Man, P. K. T. Mok, and M. Chan, "A High Slew-Rate Push-Pull Output Amplifier for Low-Quiescent Current Low-Dropout Regulators With Transient-Response Improvement," Circuits Syst. II Express Briefs, IEEE Trans., vol. 54, no. 9, pp. 755-759, Sep. 2007.

- X. Ming, Q. Li, Z. Zhou, and B. Zhang, "An Ultrafast Adaptively Biased Capacitorless LDO With Dynamic Charging Control," Circuits Syst. II Express Briefs, IEEE Trans., vol. 59, no. 1, pp. 40-44, 2012.

- [10] Y. Kim and S.-S. Lee, "A Capacitorless LDO Regulator With Fast Feedback Technique and Low-Quiescent Current Error Amplifier,"

- Circuits Syst. II Express Briefs, IEEE Trans., vol. 60, no. 6, pp. 326-330. 2013.

- [11] S. Chong and P. K. Chan, "A 0.9-µA Quiescent Current Output-Capacitorless LDO Regulator With Adaptive Power Transistors in 65nm CMOS," Circuits Syst. I Regul. Pap. IEEE Trans., vol. 60, no. 4, pp. 1072-1081, 2013.

- [12] J. Guo, M. Ho, K. Y. Kwong, and K. N. Leung, "Power-area-efficient transient-improved capacitor-free FVF-LDO with digital detecting technique," Electron. Lett., vol. 51, no. 1, pp. 94-96, 2015.

- [13] M. Ho and K. N. Leung, "Dynamic Bias-Current Boosting Technique for Ultralow-Power Low-Dropout Regulator in Biomedical Applications," Circuits Syst. II Express Briefs, IEEE Trans., vol. 58, no. 3, pp. 174–178, 2011.

- [14] C. Zheng and D. Ma, "Design of Monolithic CMOS LDO Regulator With D<sup>2</sup> Coupling and Adaptive Transmission Control for Adaptive Wireless Powered Bio-Implants," Circuits Syst. I Regul. Pap. IEEE Trans., vol. 58, no. 10, pp. 2377–2387, Oct. 2011.

- [15] L. Sumanen, M. Waltari, and K. A. I. Halonen, "A 10-bit 200-MS/s CMOS parallel pipeline A/D converter," Solid-State Circuits, IEEE J., vol. 36, no. 7, pp. 1048-1055, Jul. 2001.

- [16] J. Ramirez-Angulo, A. J. Lopez-Martin, R. G. Carvajal, A. Torralba, and M. Jimenez, "Simple class-AB voltage follower with slew rate and bandwidth enhancement and no extra static power or supply requirements," Electron. Lett., vol. 42, no. 14, pp. 784-785, 2006.

- [17] M. Yavari, O. Shoaei, and F. Svelto, "Hybrid cascode compensation for two-stage CMOS operational amplifiers," in 2005 IEEE International Symposium on Circuits and Systems, 2005, p. 1565-1568 Vol. 2.

- [18] P. J. Hurst, S. H. Lewis, J. P. Keane, F. Aram, and K. C. Dyer, "Miller compensation using current buffers in fully differential CMOS two-stage operational amplifiers," IEEE Trans. Circuits Syst. I Regul. Pap., vol. 51, no. 2, pp. 275–285, Feb. 2004.

- [19] C.-M. Chen, T.-W. Tsai, and C.-C. Hung, "Fast Transient Low-Dropout Voltage Regulator With Hybrid Dynamic Biasing Technique for SoC Application," Very Large Scale Integr. Syst. IEEE Trans., vol. 21, no. 9, pp. 1742-1747, Sep. 2013.

- [20] P. Hazucha, T. Karnik, B. A. Bloechel, C. Parsons, D. Finan, and S. Borkar, "Area-efficient linear regulator with ultra-fast load regulation," Solid-State Circuits, IEEE J., vol. 40, no. 4, pp. 933-940, 2005.