### High-Voltage Compliant Neurostimulator With On-Chip Power Management in Standard CMOS Technology

Memoria presentada por

### DAVID PALOMEQUE MANGUT

para la obtención del Grado de Doctor por la Universidad de Sevilla.

Directores

MANUEL DELGADO RESTITUTO ÁNGEL RODRÍGUEZ VÁZQUEZ

Tutor

ÁNGEL RODRÍGUEZ VÁZQUEZ

Sevilla, 2022

### **Tesis doctoral**

High-Voltage Compliant Neurostimulator With On-Chip Power Management in Standard CMOS Technology Programa de Doctorado en Ciencias y Tecnologías Físicas Universidad de Sevilla

### Autor

David Palomeque Mangut Graduado en Ingeniería Electrónica y Automática (Rama Industrial) Máster en Investigación en Ingeniería y Arquitectura (Rama Industrial)

### Director

Manuel Delgado Restituto Investigador Científico Instituto de Microelectronica de Sevilla (IMSE) Consejo Superior de Investigaciones (CSIC)

#### Director y Tutor

Ángel Rodríguez Vázquez Catedrático de Universidad Departamento de Electrónica y Electromagnetismo Universidad de Sevilla (US)

#### Instituciones

Universidad de Sevilla (US) Consejo Superior de Investigaciones Científicas (CSIC) Centro Nacional de Microelectrónica (CNM) Instituto de Microelectrónica de Sevilla (IMSE)

## Agradecimientos Acknowledgments

La realización unas Tesis Doctoral suela comenzar con mucha ilusión y ganas. Después, llegan el estrés, las jornadas interminables y las alegrías entremezcladas con frustraciones. Al final, si todo va bien, el Doctorando reconoce el gran aprendizaje y el logro que conlleva la realización de una Tesis. Además del trabajo personal llevado a cabo por el Doctorando, en cualquier Tesis hay una dimensión colectiva, una serie de personas sin cuya participación no podría salir adelante el trabajo. En estas líneas reconozco a las personas que han hecho posible esta Tesis Doctoral.

Mis logros son, sobre todo, mérito de mis padres, que son una fuente inagotable de apoyo, cariño y comprensión. Ellos me inculcaron la importancia del estudio. Además, durante mi niñez, adolescencia y el principio de mi adultez, se encargaron de que mis únicas preocupaciones fueran crecer como persona y cumplir con mis objetivos académicos y profesionales. Tampoco sería quien soy si no fuera por la influencia de Sergio: mi hermano, colega y amigo, con el que siempre tengo conversaciones muy estimulantes. ¡Gracias a los tres!

Esta Tesis también ha salido adelante gracias a Irene, que me ha escuchado, me ha entendido, me ha dado cariño y me ha enseñado otras maneras de ver el mundo. Es, además, una excelente Ingeniera de la que aprendo todos los días. Con ella todo es mucho más fácil. Gracias.

La vida tendría poco sentido sin rodearse de buenos amigos, y yo tengo la suerte de contar con Alex, Antonio, Borja A., Borja N., Fidel, Fran, Javi, Jaime, Miguel, Nacho, Nico, Pablo G., Pablo M. y tantos otros. Gracias por las risas y por estar ahí. Agradezco especialmente su apoyo a Jaime, que conoce de primera mano las dificultades del mundo de la investigación y con

el que llevo años teniendo grandes conversaciones y pasando muy buenos ratos.

Quiero poner en valor también a la comunidad de investigadores/as predoctorales del Instituto de Microelectrónica de Sevilla (IMSE). Aunque la situación mejora progresivamente gracias a colectivos como "FPU Investiga" o "Red de Doctorand@s del CSIC", en general, el trabajo de un Doctorando no está justamente remunerado ni reconocido. Esto da aún más relevancia al hecho de que los/as investigadores/as predoctorales del IMSE son personas con un enorme conocimiento técnico y que no dudan en invertir horas de su tiempo en ayudar al resto de compañeros y compañeras. Así, esta Tesis no habría sido posible sin Norberto, Franco, Valentín, Antonio, Rubén, Rafa, José Luis y Carlos D. Todos ellos son muy buenos diseñadores de circuitos integrados y mejores colegas. Quiero hacer una mención especial a Norberto, con el que compartí (muchos) momentos de estrés y apoyo mutuo. También quiero agradecer su apoyo y compañerismo a Juan, Pablo P., Manu, Pablo F., Marco, Virginia y Kourosh.

Tener buenos supervisores puede facilitar mucho la vida de un Doctorando. Agradezco al Prof. Ángel Rodríguez todas las conversaciones de carácter técnico, docente y formativo que tuvimos durante mi colaboración como docente en una asignatura coordinada por él. Aprendí mucho de ellas. También su labor como Director y Tutor de esta Tesis Doctoral. Agradezco al Dr. Manuel Delgado, Director de esta Tesis Doctoral, su supervisión durante estos cuatro años. Por último, quiero mencionar al Prof. Juan Antonio Leñero, que siempre fue muy amable y del que aprendí sobre fotodiodos CMOS todo lo que se refleja en esta Tesis.

I would also like to thank Prof. Alexander Schmid for his supervision when I was a Guest PhD Student at Swiss Federal Institute of Technology Lausanne (EPFL). Besides his kindness in welcoming me into his research group, his guidance in the field of inductive links for neural implants was fundamental for me to having a fruitful stay. I also thank Ph.D. Student Mohammad Javad Karimi for his kindness and for the technical discussions in a field in which he is becoming an expert.

Por último, agradezco al Ministerio de Universidades del Gobierno de España la financiación, dentro del programa para la Formación del Profesorado Universitario (FPU), de mi contrato predoctoral durante la mayor parte de esta Tesis (FPU18/00247) y de mi estancia de 3 meses en EPFL (EST21/00407); a la Universidad de Sevilla la financiación, dentro del VI Plan Propio de Investigación, de mi contrato predoctoral durante varios

meses; a la USA Office of Naval Research la financiación de los proyectos con referencias N00014-14-1-355 y N00014-19-12156; al Ministerio de Economía, Industria y Competitividad del Gobierno de España la financiación del proyecto con referencia TEC2016-80923-P; y al Ministerio Ciencia e Innovación del Gobierno de España por la financiación del proyecto con referencia PID2019-110410RB-I00.

### Abstract

This thesis is devoted to the design and development of Application-Specific Integrated Circuits (ASICs) in a standard 1.8V/3.3V CMOS process towards the implementation of a neural stimulator with high compliance voltage, which is a fundamental part of the neural implant that is being developed in this research group. Thus, most of this work deals with circuit-level and block-level techniques for the design and implementation of high-voltage-tolerant circuits in standard CMOS technologies, in the context of implantable systems.

Besides, this thesis preliminary addresses the wireless powering of the neural implant, including: (1) light harvesting with solar cells implemented on a standard CMOS technology and (2) the design and optimization of inductive links for wireless transfer of power and data to/from the neural implant.

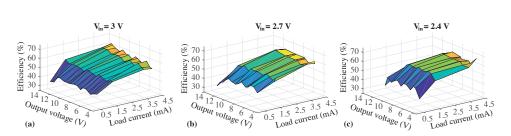

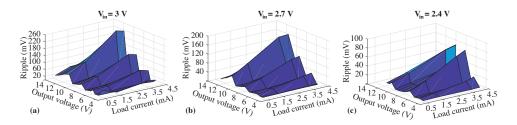

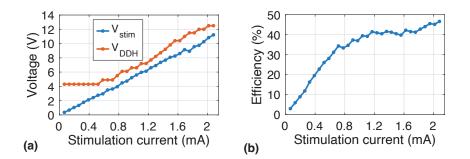

Two ASICs were designed an fabricated. One includes the neural stimulator front-end and the power management unit. The other implements a CMOS solar cell with a novel stacked-diode configuration. Experimental results of both ASICs are shown and discussed. Summarising: (1) the neural stimulator front-end delivers currents up to 2.08 mA and has a compliance voltage of roughly 12.5 V; (2) the output voltage of the DC-DC converter in the power management unit ranges from 4.2 V up to 13.2 V, from a 3 V input source; (3) overall peak efficiency is close to 50%; and (4) the measured peak power generation of the CMOS solar cell was around 18  $\mu$ W mm<sup>-2</sup>.

Regarding the design and optimization of inductive Wireless Power and Data Transfer (WPDT) systems, a topology for the transmission of mWpower and Mbps-data over a single pair of coils was designed and simulated at the block-level. This topology shows promising results towards the implementation of a millimeter-sized wirelessly-powered neural implant with moderate power consumption and moderate data transmission rate.

## Contents

| Li       | st of | figures                                                       | i            |

|----------|-------|---------------------------------------------------------------|--------------|

| Li       | st of | tables                                                        | iii          |

| A        | crony | yms                                                           | $\mathbf{v}$ |

| 0        | bject | ives, contributions, and thesis structure                     | ix           |

| 1        | Fun   | damentals of Neural Stimulation                               | 1            |

|          | 1.1   | Introduction                                                  | 1            |

|          | 1.2   | The Electrode-Tissue Interface (ETI)                          | 2            |

|          |       | 1.2.1 Faradaic and non-faradaic charge transfer               | 2            |

|          |       | 1.2.2 Electrochemical reversal                                | 3            |

|          | 1.3   | Efficacious and safety of electrical neural stimulation       | 3            |

|          | 1.4   | Optogenetic stimulation                                       | 5            |

|          |       | 1.4.1 Opsins used in optogenetic neural stimulation           | 5            |

|          |       | 1.4.2 Light interaction in cerebral cortex                    | 6            |

| <b>2</b> | Lite  | erature Review of Neural Stimulators                          | 9            |

|          | 2.1   | An introduction to neural stimulators from an electrical per- |              |

|          |       | spective                                                      | 9            |

|          |       | 2.1.1 Types of neural stimulators                             | 9            |

|          |       | 2.1.2 Optical Neural Stimulators                              | 12           |

|          | 2.2   | Literature review                                             | 13           |

| 3        | Wii   | celess Power and Data Transfer                                | 19           |

|          | 3.1   | CMOS photovoltaic cell                                        | 19           |

|          |       | 3.1.1 Introduction                                            | 19           |

|          |       | 3.1.2 Photodiode operation                                    | 20           |

|       | 80 |

|-------|----|

|       | 79 |

|       | 77 |

|       | 74 |

|       | 74 |

|       | 69 |

|       | 68 |

|       | 68 |

|       | 68 |

|       | 66 |

|       | 64 |

|       | 64 |

|       | 61 |

|       | 61 |

|       | 58 |

|       | 55 |

|       | 52 |

|       | 51 |

|       | 49 |

|       | 47 |

|       | 37 |

|       | 36 |

|       | 35 |

|       | 35 |

|       | 31 |

|       | 28 |

|       | 26 |

| vstem | 25 |

|       | 24 |

|       |    |

# List of Figures

| 1    | Microphotographs of two ASICs implemented in this thesis                                        | xiii |

|------|-------------------------------------------------------------------------------------------------|------|

| 1.1  | Electrical model of the Electrode-Tissue Interface (ETI) and the extracellular fluid [15], [16] | 2    |

| 2.1  | Conceptual electrical schemes for the major approaches for<br>neural stimulators.               | 10   |

| 2.2  | Evolution of results appearing in PubMed's search engine                                        | 13   |

| 2.3  | Current-Controlled Stimulator (CCS)                                                             | 15   |

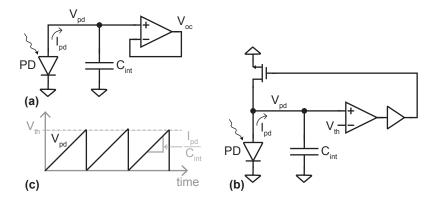

| 3.1  | Diagrams describing photodiodes' operation.                                                     | 20   |

| 3.2  | Photodiode configurations under study.                                                          | 21   |

| 3.3  | Current-voltage curves of two parallel diodes operating simul-                                  |      |

|      | taneously.                                                                                      | 22   |

| 3.4  | Integrated test circuits to compare the two diode configura-                                    |      |

|      | tions performance.                                                                              | 23   |

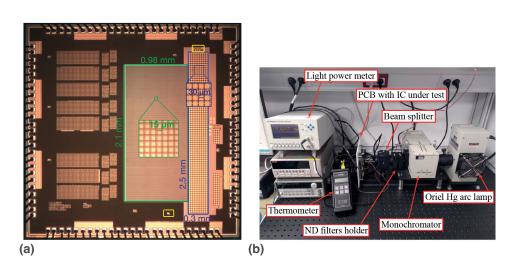

| 3.5  | CMOS solar cell microphotograph and experimental setup.                                         | 24   |

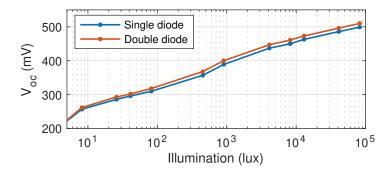

| 3.6  | Open-circuit voltage, $V_{oc}$ , versus illumination. [6]                                       | 25   |

| 3.7  | Measurements on the photodiode array for different illumina-                                    |      |

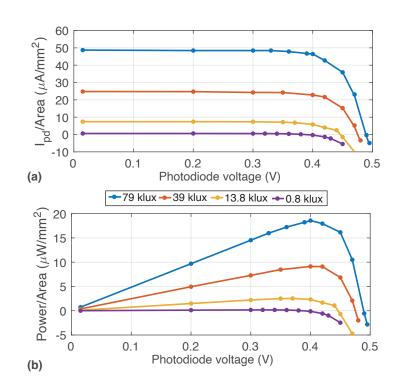

|      | tion values.                                                                                    | 26   |

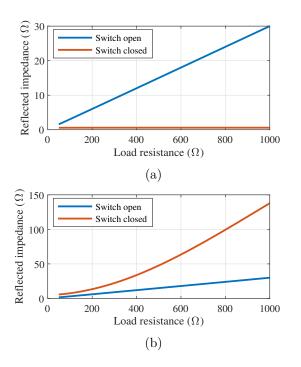

| 3.8  | Simplified schematic of a resonant inductive WPDT system                                        | 27   |

| 3.9  | Reflected impedance magnitude variation under different load                                    |      |

|      | resistances with/without Load-Shift Keying (LSK)                                                | 29   |

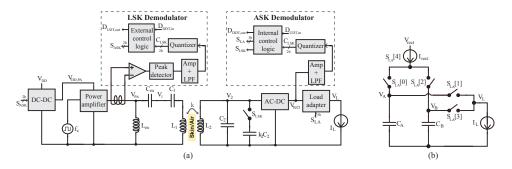

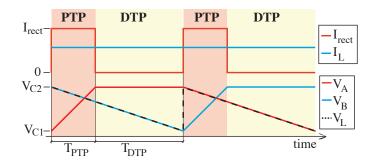

| 3.10 | Simplified block diagram of the proposed WPDT system                                            | 30   |

| 3.11 | Timing diagram of the load adapter block. [7]                                                   | 31   |

|      | Power transmission to a 15 mA load.                                                             | 32   |

|      | Power transmission to a 15 mA load and Uplink Data Trans-                                       |      |

|      | mission (UDT) of two-bytes package                                                              | 33   |

|      |                                                                                                 |      |

| i

| 3.14 | Power transmission to a 5 mA load and Downlink Data Trans-             |    |  |  |

|------|------------------------------------------------------------------------|----|--|--|

|      | mission (DDT) of two-bytes package                                     | 33 |  |  |

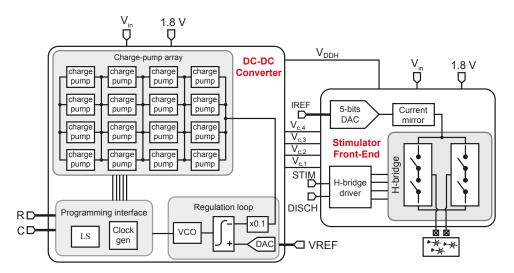

| 4.1  | Simplified schematic of the proposed DC-DC converter                   | 36 |  |  |

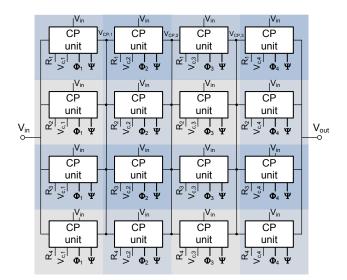

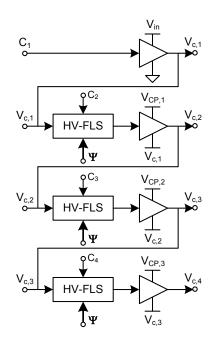

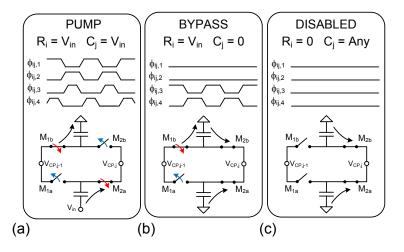

| 4.2  | Block diagram of the charge-pump array.                                | 37 |  |  |

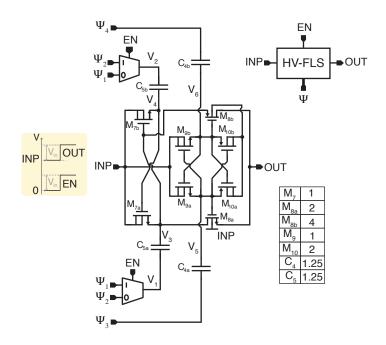

| 4.3  | Schematic and symbol of the High-Voltage Floating Level                |    |  |  |

|      | Shifter (HV-FLS) for sliding configuration bits.                       | 38 |  |  |

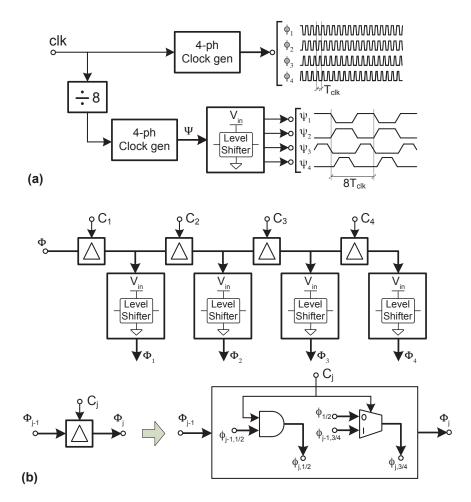

| 4.4  | Timing diagram of the 4-phase clock signals.                           | 39 |  |  |

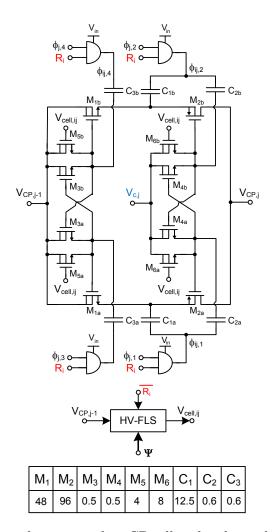

| 4.5  | Proposed cross-coupling charge-pump cell                               | 40 |  |  |

| 4.6  |                                                                        |    |  |  |

|      | signals $V_{c,j}$ from the configuration bit $C_j, j = 1, \ldots, 4$ . | 42 |  |  |

| 4.7  | Simplified schematic of the proposed charge-pump cell                  | 44 |  |  |

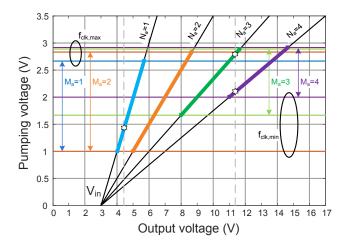

| 4.8  | Graphical representation of the converter operation range for          |    |  |  |

|      | different row/column configurations.                                   | 45 |  |  |

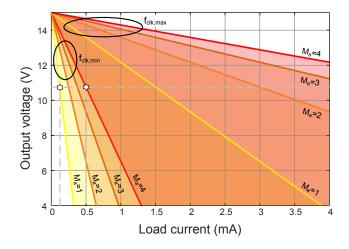

| 4.9  | Graphical representation of the High-Voltage Switched-Capacito         | r  |  |  |

|      | Regulated DC-DC Converter (HV-SCRC)'s operation range.                 | 46 |  |  |

| 4.10 | Regulation loop circuit.                                               | 48 |  |  |

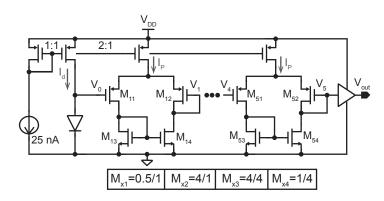

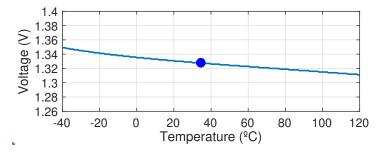

| 4.11 | On-chip bandgap voltage reference                                      | 49 |  |  |

| 4.12 | Voltage-temperature curve of the bandgap voltage reference.            | 50 |  |  |

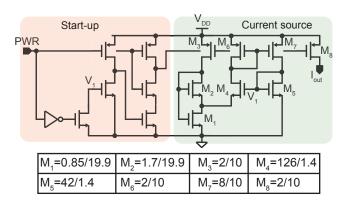

| 4.13 | On-chip self-biased current reference                                  | 51 |  |  |

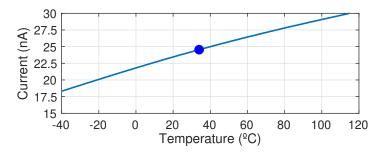

| 4.14 | Current-temperature curve of the self-biased current reference.        | 51 |  |  |

| 4.15 | Microphotograph of the fabricated chip                                 | 52 |  |  |

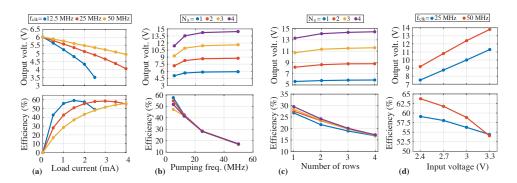

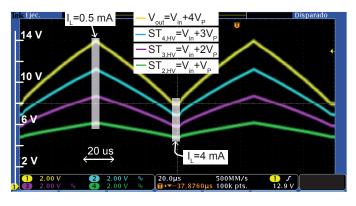

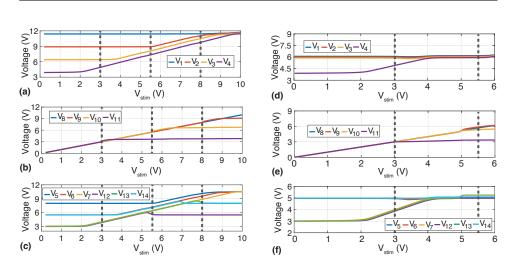

| 4.16 | Open loop measurements                                                 | 53 |  |  |

| 4.17 | Experimental measurements in open-loop arrangement                     | 54 |  |  |

| 4.18 | Experimental measurements in an open-loop arrangement                  | 55 |  |  |

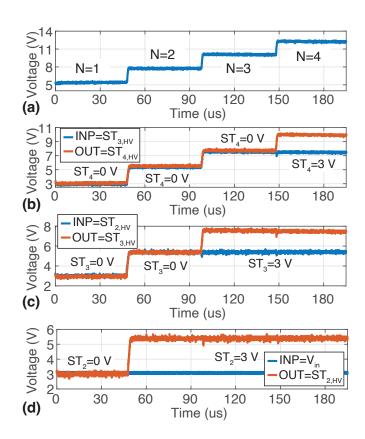

| 4.19 | Closed loop measurements: power efficiency                             | 56 |  |  |

| 4.20 | Closed loop measurements: output voltage ripple                        | 56 |  |  |

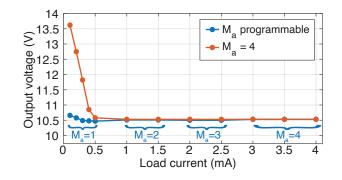

| 4.21 | Closed loop measurements.                                              | 57 |  |  |

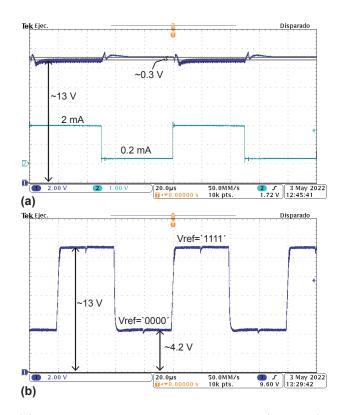

| 4.22 | Response to a switching $I_L$ and to a change in <i>VREF</i>           | 58 |  |  |

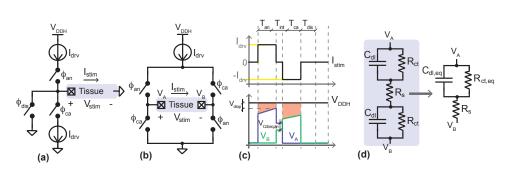

| 5.1  | Current-controlled stimulators.                                        | 62 |  |  |

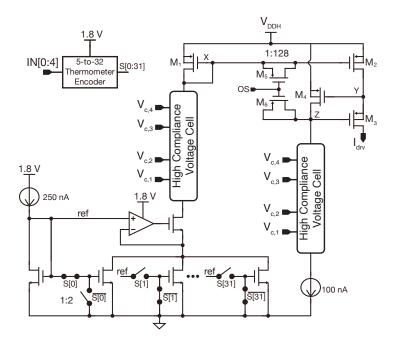

| 5.2  | Block-level scheme of the proposed HV neural stimulator                | 63 |  |  |

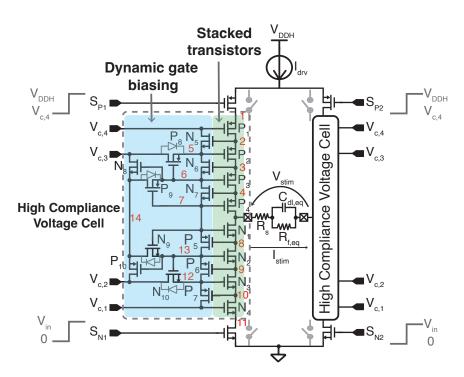

| 5.3  | Proposed high-voltage-tolerant H-bridge                                | 65 |  |  |

| 5.4  | Evolution of the voltages at the nodes of the HCVC                     | 66 |  |  |

| 5.5  | Schematic of the current driver                                        | 67 |  |  |

| 5.6  | H-bridge driver                                                        | 68 |  |  |

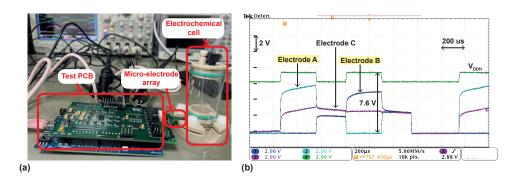

| 5.7  | Testbench.                                                             | 69 |  |  |

| 5.8  | Photography of the micro-electrode arrays                              | 70 |  |  |

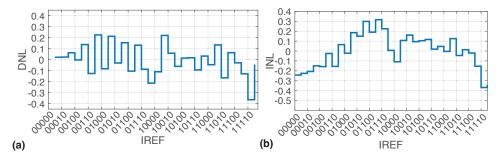

| 5.9  | Measured stimulation current's DNL                                     | 70 |  |  |

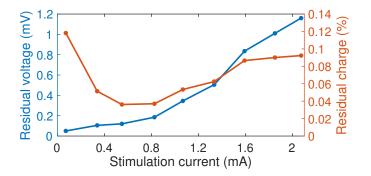

| 5.10 | Measured residual voltage and residual charge                          | 71 |  |  |

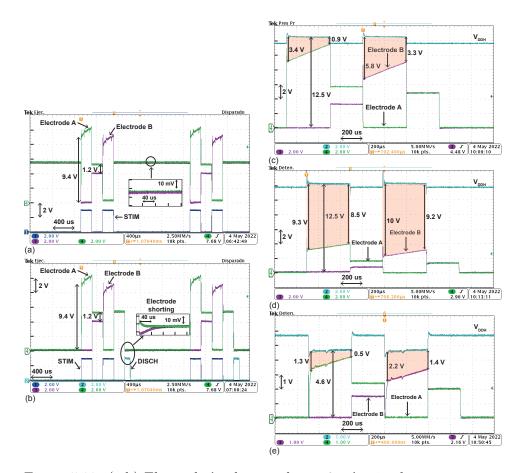

| 5.11 | Oscilloscope screenshots                               | 72 |

|------|--------------------------------------------------------|----|

| 5.12 | Measured stimulation voltage and overall efficiency    | 73 |

| 5.13 | Electrodes' voltages when stimulating the PBS solution | 74 |

iv

### List of Tables

| 1.1          | Charge/phase threshold and pulse width required for different neural prostheses. Reproduced from [19].          | 4   |

|--------------|-----------------------------------------------------------------------------------------------------------------|-----|

| 2.1          | Qualitative comparison of different electrical neurostimula-<br>tion approaches.                                | 12  |

| 2.2          | Performance comparison of neural stimulators reported in the                                                    | 1 - |

| 2.3          | literature                                                                                                      |     |

| $4.1 \\ 4.2$ | Values of the voltage-shifted column selection signals<br>Performance comparison with previously reported works | 42  |

| 5.1          | Performance comparison with previously reported HV neural stimulators.                                          | 75  |

vi

### Acronyms

- ${\bf AP}\,$  Action Potential. 6, 7

- **ASIC** Application-Specific Integrated Circuit. , i, xii, xiii, xv, 13, 68, 69, 79

- ASK Amplitude-Shift Keying. 27, 31, 32, 33

- CCS Current-Controlled Stimulator. i, 9, 10, 11, 12, 13, 14, 15, 16

- **CE** Counter Electrode. 1, 5

- **CP** Charge-Pump. 36, 37, 40, 41, 42, 43, 44, 52, 54

- **DAC** Digital-to-Analog Converter., 14, 47, 48, 64, 66, 67

- **DBS** Deep-Brain Stimulation. 1, 5

- DDT Downlink Data Transmission. ii, 31, 33

- **DNL** Differential Non-Linearity. ii, 69, 70

- **DNW** Deep N-type Well. 20, 21, 41

- **ECS** Electrical-Cortical Stimulation. 1, 2, 5

- ENS Electrical Neural Stimulator. 13, 64

- **ETI** Electrode-Tissue Interface., i, xi, 1, 2, 4, 5, 10, 13, 14, 16, 35, 61, 62

- HCVC High Compliance Voltage Cell. ii, xii, 64, 65, 66, 67, 73

- **HV** High-Voltage. ii, xii, xiii, 16, 36, 59, 63, 64, 74

- HV-NSFE High-Voltage Neural Stimulator Front-End. xii, 61, 68, 69, 78

- **HV-SCRC** High-Voltage Switched-Capacitor Regulated DC-DC Converter. ii, xii, xv, 35, 36, 43, 44, 45, 46, 47, 51, 52, 53, 54, 58, 64, 68, 69, 72, 73, 78, 79

- **HV-FLS** High-Voltage Floating Level Shifter. ii, 38, 39, 40, 41, 42, 53, 54, 55, 68

- INL Integral Non-Linearity. 69, 70

**LED** Light-Emitting Diode. 12

- LSB Least-Significant Bit. 70

- LSK Load-Shift Keying. i, 27, 28, 29, 31, 33

- LUT Look-Up Table. 51, 52

- ${\bf LV}$  Low-Voltage. xii, 59, 74

- MIM Metal-Insulator-Metal. 24, 41, 48

- MOM Metal-Oxide-Metal. 37

- **ND** N-type Diffusion. 21, 24

- **ONS** Optical Neural Stimulator. 13

- **OTA** Operational Transconductance Amplifier. 49

- **PBS** Phosphate-Buffered Saline. , iii, 69, 74

- **PS** P-type Substrate. 21

- **PTAT** Proportional To Absolute Temperature. 49

- **PW** P-type Well. 21, 24

- **SCS** Switched-Capacitor Stimulator. 9, 10, 11, 12, 16 **SPI** Serial-Peripheral Interface. 51

- TC Temperature Coefficient. 49, 50

- UDT Uplink Data Transmission. i, 26, 27, 28, 31, 33

- VCO Voltage-Controlled Oscillator. 37, 48, 49

- VCR Voltage Conversion Ratio. 35, 36

- $\mathbf{VCS}$ Voltage-Controlled Stimulator. 9, 10, 11, 12, 16, 17

- ${\bf WE}\,$  Working Electrode. 1, 5

- **WPDT** Wireless Power and Data Transfer. , i, 14, 19, 25, 26, 27, 28, 30

X\_\_\_\_\_

## Objectives, contributions, and thesis structure

This chapter outlines the objectives posed at the beginning of this thesis, the contributions made to fulfill those objectives, and the thesis structure.

### Objectives

Studying neuronal circuits at cellular level for the understanding of brain functions is a challenging endeavor which requires neural interfaces. These neural interfaces perform two tasks. First, they record the neural activity of the target brain area. Second, they stimulate that brain area in order to modulate neural activity.

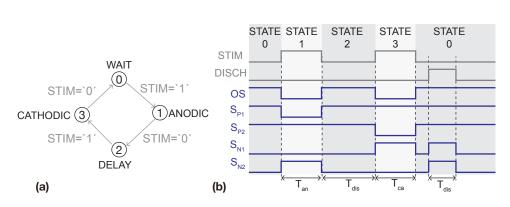

Thus, the efficacy of neural interfaces ultimately depends on their ability to trigger a functional response in the target tissue by inducing a flow of current between two or more electrodes. This is typically done by applying a series of biphasic current pulses with cathodic and anodic phases whose amplitudes and durations are adjusted to result in an overall zero net charge in the tissue. A major concern in the implementation of stimulators is the impedance at the Electrode-Tissue Interface (ETI). Such impedance depends on the geometry and materials of the electrodes; the physiological parameters of the tissue; and the degree of electrical contact at the stimulation zone. Further, the interface is not stationary in nature and the impedance changes throughout the life cycle of the implant. These factors make that the stimulation currents practically range from some tens of  $\mu A$  up to some mA and that the voltage compliance of the current drivers vary from a few volts up to over 10 V. The main objective of this thesis was thus the design and development of a neural stimulator with wide stimulation current range and high compliance voltage.

Besides, the neural interface in which the stimulator shall be included should be highly power efficient for two reasons. First, high power consumption translates to high power dissipation in the form of heat, which is undesirable in the context of implantable systems. Second, the neural interface shall be powered through an wireless power link so as to avoid wires, thus minimizing the risk of infection. The specifications of that wireless power link should be relaxed as much as possible so as to reduce its size and complexity.

Another objective of this thesis was to investigate and propose circuit solutions to implement the mentioned high compliance voltage, highly efficient, neural stimulator in a standard 1.8V/3.3V CMOS process. Implementing it in such process instead of using a High-Voltage (HV) CMOS technology was mandatory in order to avoid time-consuming migration of previously designed Low-Voltage (LV) circuitry [1], [2].

Last, this thesis was meant to preliminary explore the possibilities regarding the wireless transfer of both power and data to/from the neural implant by means of inductive links and CMOS solar cells..

### Contributions

This thesis introduces several innovative solutions both at the circuit-level and block-level in the field of mixed-signal ASIC design, including:

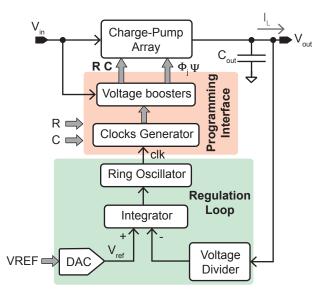

- A high-voltage-tolerant versatile charge-pump cell has been designed and implemented. It can operate under three different modes: PUMP, PASS, and DISABLE. This enabled the design of a programmable charge-pump array, which is the core of the proposed High-Voltage Switched-Capacitor Regulated DC-DC Converter (HV-SCRC).

- A High-Voltage Neural Stimulator Front-End (HV-NSFE) with roughly 12.5 V compliance voltage has been proposed [3]. Circuit-level contributions include a High Compliance Voltage Cell (HCVC) which adapts its equivalent impedance in order to withstand large voltages or act as a closed switch, as needed.

- A high-voltage-tolerant floating level-shifter with charge refreshing has been designed [4], [5]. This cell is extensively used in the High-Voltage Neural Stimulator Front-End (HV-NSFE) and the HV-SCRC. Its fundamental features are: high-voltage tolerant operation, tracking of the low-supply rail, and handling of non-periodical input signals.

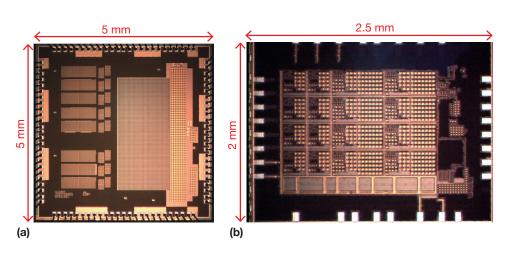

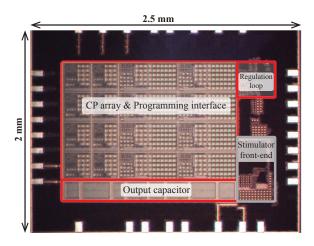

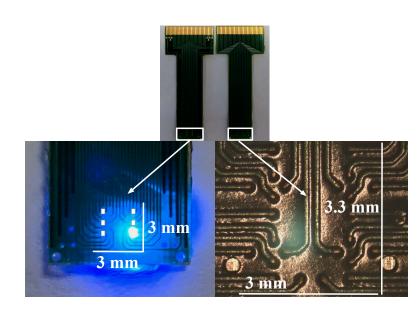

Figure 1: Microphotographs of two ASICs implemented in this thesis. (a) CMOS solar cell. (b) Neural stimulator.

- A novel stacked-photodiode configuration was implemented and characterized. Its use in CMOS solar cells and CMOS image sensors was discussed [6].

- A novel inductive-link topology for the wireless transfer of Mbps-data and mW-power over a single pair of coils has been proposed [7]. It was electrically modeled at the system level. Simulation results have been shown an discussed.

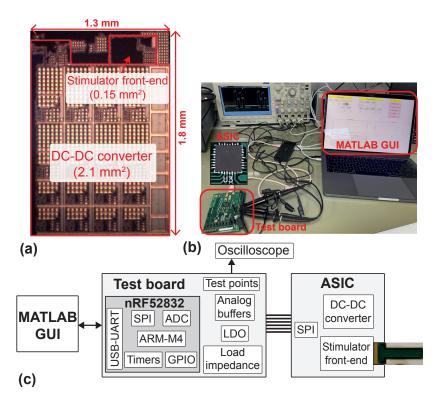

Experimental results shown in this thesis were obtained from two ASICs implemented in the TSMC 180 nm 1.8V/3.3V CMOS process. On the one hand, Fig. 1(a) shows the microphotograph of the ASIC including a CMOS photovoltaic solar cell, which was characterised to determine if it is feasible to power the neural implant with light harvesting. In Chapter 3, the design and characterization of this ASIC is discussed. Further analysis and experimental characterization were carried out to evaluate the performance of the integrated photodiodes in the context of CMOS image sensors. However, since this lies out of the scope of this thesis, the interested reader is referred to [6] for more insights. On the other hand, Fig. 1(b) depicts the proposed neural stimulator with on-chip HV generation, whose design and implementation are discussed in Chapters 4 and 5. Furthermore, for the experimental validation of the neural stimulator, a complete firmware was developed for the nRF52832 microcontroller: ADC, UART, timers, and SPI modules were used for controlling the neural stimulator and measuring its

response, sending commands from a custom MATLAB GUI.

The following publications cover most of the material presented in this thesis.

- R. Gómez-Merchán, D. Palomeque-Mangut, J. A. Leñero-Bardallo, M. Delgado-Restituto, and A. Rodríguez-Vázquez, «A Comparative Study of Stacked-Diode Configurations Operating in the Photovoltaic Region», IEEE Sensors Journal, vol. 20, n.º 16, pp. 9105-9113, 2020.

- D. Palomeque-Mangut, A. Rodriguez-Vazquez, and M. Delgado-Restituto, «A Wide-Range, High-Voltage, Floating Level Shifter with Charge Refreshing in a Standard 180 nm CMOS Process», IEEE 13th Latin America Symposium on Circuits and System (LASCAS), Puerto Varas, Chile, 2022, pp. 01-04.

- D. Palomeque-Mangut, A. Schmid, Á. Rodríguez-Vázquez, and M. Delgado-Restituto, «Electrical Model of a Wireless mW-Power and Mbps-Data Transfer System Over a Single Pair of Coils», International Conference on PhD Research in Microelectronics and Electronics (PRIME), Sardinia (Italy), 2022.

- D. Palomeque-Mangut, Á. Rodríguez-Vázquez, and M. Delgado-Restituto, «Experimental Validation of a High-Voltage Compliant Neural Stimulator Implemented in a Standard 1.8V/3.3V CMOS Process», accepted at the IEEE Biomedical Circuits and Systems Conference (BioCAS), Taipei (Taiwan), 2022.

- D. Palomeque-Mangut, Á. Rodríguez-Vázquez, and M. Delgado-Restituto, «A High-Voltage Floating Level Shifter for a Multi-stage Charge-Pump in a Standard 1.8V/3.3V CMOS Process», accepted for publication at AEU - International Journal of Electronics and Communications, 2022.

- D. Palomeque-Mangut, Á. Rodríguez-Vázquez, and M. Delgado-Restituto, «A Fully Integrated, Power-Efficient, 0.07-2.08 mA, High-Voltage Neural Stimulator in a Standard CMOS Process», accepted for publication at Sensors, 2022.

- D. Palomeque-Mangut, Á. Rodríguez-Vázquez, and M. Delgado-Restituto, «A 4.2-13.2 V, On-Chip, Regulated, DC-DC Converter in a Standard 1.8V/3.3V CMOS Process», sent to AEU - International Journal of Electronics and Communications, 2022.

### Thesis structure

This thesis work is structured as follows:

- An introduction to fundamental concepts of neural stimulation is given in Chapter 1.

- Chapter 2 discusses the fundamental electrical specifications of neural stimulators and presents a literature review of neural stimulators.

- Chapter 3 presents the preliminary work carried out regarding the wireless transfer of power and data to/from the neural implant. First, the designed and implemented CMOS solar cell shown in Fig. 1(a) is discussed, including experimental results. Second, an inductive-link topology over a single pair of coils is proposed. In this case, simulation results are discussed.

- In Chapter 4, the proposed HV-SCRC –included in the ASIC presented in Fig. 1(b)– is discussed. Experimental results are also given.

- The proposed neural stimulator –i.e. the whole ASIC shown in Fig. 1(b)– is presented in Chapter 5, where experimental results are also shown and discussed.

- Finally, Chapter 6 presents the conclusions of the thesis as well as an overview of the possible future works.

xvi

### Chapter 1

## Fundamentals of Neural Stimulation

In this chapter, fundamental neural stimulation concepts are discussed. First, Section 1.1 introduces the topic. Then, Section 1.2 describes the Electrode-Tissue Interface (ETI). Methods for assuring efficacy and safety of electrical stimulation are shown in Section 1.3. Finally, optogenetic stimulation is introduced in Section 1.4.

### 1.1 Introduction

Electrical neurostimulation techniques consist on forcing an electrical current to flow from an electrode –the Working Electrode (WE)– through extracellular fluid of some excitable tissue of the nervous system. This current is finally sought by a distant Counter Electrode (CE). The final purpose of such technique is the alteration of neural activity. This is also called *neuromodulation*. In this work, we are interested in two neuromodulation techniques: Deep-Brain Stimulation (DBS) and Electrical-Cortical Stimulation (ECS).

DBS is a neuromodulation technique in which precise amounts of electrical charge are delivered to specific deep anatomical structures of the central nervous system [8]. Clinical applications of DBS include Parkinson's disease, essential tremor, dystonia, neuro-behavioral disorders, epilepsy, pain, and others [8]–[10].

ECS is also a neuromodulation technique in which electrical charge is delivered thorugh electrodes placed on the cerebral cortex. The main clinical application of ECS is the identification of functional brain regions [11]. Besides, it has been used for inducing vestibular responses [12], treating epilepsy [13], and others [14].

### **1.2** The Electrode-Tissue Interface (ETI)

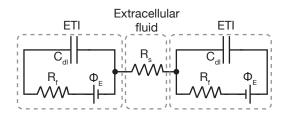

The ETI is formed when the metal electrode is placed inside extracellular fluid of the neural tissue [15], [16]. In this interface, electrode's electronic charge is transduced into ionic charge. Even though the ETI has non-linear impedance, it can be electrically modeled as a parallel resistor-capacitor. On the one hand, the resistive element  $R_f$  models the faradaic current generated by the chemical reactions taking part in the interface. On the other hand, the capacitive element  $C_{dl}$  models the electrical double layer that is formed. Besides,  $\Phi_E$  stands for the potential that exists across the interface at equilibrium. Finally, the electrolyte (extracellular fluid) can be electrically modeled as a linear resistor  $R_s$ . This electrical model is depicted in Fig. 1.1.

Figure 1.1: Electrical model of the ETI and the extracellular fluid [15], [16].

### 1.2.1 Faradaic and non-faradaic charge transfer

As previously said, both faradaic and non-faradaic reactions occur in the ETI. On the one hand, faradaic currents result from the direct transfer of electronics via reduction or oxidation reactions at the ETI. On the other hand, non-faradaic currents include currents that result from other processes where direct transfer of electrodes does not occur in the ETI [17].

During stimulation, non-faradaic charge transfer takes place when the net charge of the electrode varies and, accordingly, the charge in the solution is redistributed. If the polarity of stimulation is reversed, so it is the charge distribution. Thus, the charge injected from the electrode into the electrolyte may be recovered [15]. This behavior is modeled by the double layer capacitance  $C_{dl}$ .

Besides, charge may also be injected from the electrode to the electrolyte (extracellular fluid) by faradaic processes such as reduction or oxidation. Contrary to the aforementioned capacitive behavior, faradaic charge injection is characterised by the formation of products in the solution that might not be recovered by reversing the polarity during stimulation. This behavior is electrically modeled by the resistor  $R_f$ . These irreversible faradaic reactions lead to changes in the chemical environment that can damage the tissue or the electrode. Thus, when designing an electrical neurostimulator it is mandatory to establish mechanisms for reducing irreversible faradaic reactions.

### 1.2.2 Electrochemical reversal

If irreversible Faradaic reactions wants to be avoided, biphasic stimulation schemes must be used. Biphasic stimulation is at least formed by two phases: anodic phase and cathodic phase. During anodic phase, electrons are transferred to the electrode –the electrode is a *current source*– whereas in cathodic phase, electrons are transferred from the electrode to the electrolyte –the electrode is a *current sink*–. With a two-electrode scheme, there is always one electrode sinking current and one electrode sourcing current. Thus, the anodic and cathodic phases are defined by looking at what happens in the vicinity of one electrode of interest –the working electrode (WE)–.

During the *active* phase of biphasic stimulation, electrochemical processes occur. The *reversal* phase is applied in order to invert the direction of those processes, minimizing unrecoverable charge. The final goal is to perform charge transfer through non-faradaic or reversible-faradaic processes, avoiding the injection of toxic materials into the tissue [18].

### 1.3 Efficacious and safety of electrical neural stimulation

Stimulation charge per phase and pulse-width thresholds vary according to the application and the species in which stimulation is delivered. In this regard, Table 1.1 summarizes charge/phase and pulse-width requirements for different neural prosthesis, depending on the application and species

| Deference  | Application | Species | Placement            | Charge/phase Pulse width |           |

|------------|-------------|---------|----------------------|--------------------------|-----------|

| Reference  |             |         |                      | (nC)                     | $(\mu s)$ |

| [20]       | Vision      | Human   | Epi-retinal          | 6-1120                   | 1000      |

| [21]       | Vision      | Human   | Epi-retinal          | 24 - 100                 | 2000      |

| [22]       | Vision      | Human   | Optic nerve          | 7-124                    | 25 - 400  |

| [23]       | Vision      | Human   | Introacortical       | 0.4 - 4.6                | 200       |

| [23]       | Vision      | Human   | Cortical             | 200000                   | 200       |

| [24], [25] | Hearing     | Cat     | VCN                  | 0.75 - 1.5               | 40-150    |

| [26], [27] | Hearing     | Human   | AB                   | 10-200                   | 300       |

| [28]       | Micturition | Cat     | Intraspinal          | 9                        | 100       |

| [29]       | DBS         | Human   | $\operatorname{STN}$ | 135-400                  | 60-200    |

| [30]       | Motor       | Cat     | Intrafascicular      | 4                        | 50        |

| [31]       | Motor       | Cat     | Sciatic nerve        | 5                        | 200       |

| [31]       | Motor       | Cat     | Sciatic nerve        | 46                       | 200       |

Table 1.1: Charge/phase threshold and pulse width required for different neural prostheses. Reproduced from [19].

If electrode corrosion or tissue damage wants to be avoided, perfectly chargebalanced biphasic stimulation should be applied [18]. However, one concern is that the *reversal* phase do not only reverses electrochemical reactions induced during the *active* phase, but also suppresses AP that were trying to be evoked. In this regard, an interphase delay can be introduced [32]. However, during the interphase delay, the electrode potential remains relatively negative and non-desirable faradaic reactions can occur. A delay of 100 µs has proven to be enough for overcome the suppressing effect of the reversal phase without causing potential damage to the electrode or the tissue.

In order to assure safety stimulation, active and/or passive methods for charge balancing must be added to the neurostimulator. Two scenarios could lead to a drift in electrode potential after biphasic stimulation: (1) biphasic stimulation could be slightly charge-unbalanced *i.e.* there might a mismatch between anodic/cathodic stimulation current or pulse-width and (2) different amounts of charge could be lost in irreversible faradaic reactions during each stimulation phase. Both factors are related: a slightly chargeimbalanced biphasic stimulation could lead to an accumulation of charge in the ETI thus causing an unsafe increase in the electrode potential that can trigger irreversible faradaic reactions.

[19].

There are two main approaches to improve charge balancing in biphasic stimulation: passive charge balancing and active charge balancing [33]. The most common charge-balancing method is electrode shorting, in which the WE to the CE are shorted during a discharge period  $T_{dis}$ . In order to successfully discharge the WE,  $T_{dis}$  must be larger than the time constant of the ETI impedance and the discharge impedance. Designers usually establish a worst-case scenario with the largest expected ETI impedance and set a discharge period long enough. This technique might not be feasible for compensating highly charge-imbalanced neurostimulators, so it is commonly used to discharge any residual charge generated by precise biphasic current stimulators.

### 1.4 Optogenetic stimulation

Stimulation of excitable tissue with light is possible thanks to the photosensitization of neuron cells with optogenetic tools. Optogenetic tools comprises the combination of genetic and optical methods that allow to control a number of cellular functions, including: stimulation/inhibition of cells, gene activation, intracellular signaling, and migration [34]–[36]. Specifically, optical stimulation of neural tissue allows to activate or inhibit neural cells with high temporal and spatial resolution. Photosensitization of neurons is achieved by means of *opsins*. *Opsins* are membrane-bound proteins that are activated with light which can be genetically targeted to specific cells [36]. The catalog of opsins have increasing during the last decade [37] but the most widely used in state-of-the-art optical neurostimulators is *Channelrhodopsin-2* (ChR2) [38]. Both DBS and ECS can be performed by means of optogenetic tools [39], [40].

### 1.4.1 Opsins used in optogenetic neural stimulation

Opsins are light-activated proteins which are found in organisms such as microbes or primates [36]. They can be used for cell activation (depolarization of the neuronal membrane) or inhibition (hyperpolarization of the neuronal membrane). Activation (inhibition) is achieved by the creation of cation (anion) channels in the membrane of opsin-expressing neurons.

#### Channelrhodopsins

As it was aforementioned, ChR2 is a blue-light gated cation channel that, when activated, depolarizes the neuronal membrane. Millisecond-width pulses of blue light can induce single Action Potential (AP) in neurons expressing ChR2. Besides, neural spiking activity can be light-driven with high precision at frequencies up to 30 spikes per second.

Opsins with faster temporal kinetics have been developed for applications in which the goal is the extremely fast control of neural activity at high firing rates. Examples of these opsins are ChETA and ChEF/ChIEF [41], [42].

#### Spectrally shifted opsins

Great effort has been put into the development of opsins with an excitation spectra different from blue. With such opsins, independent optical control of different populations of neurons can be achieved. Red-light activated opsins are particularly interesting because 1) the red wavelength interval (635 nm-700 nm) does not overlap with the blue wavelength interval (450 nm-490 nm) and 2) red electromagnetic radiation enables deeper penetration into the tissue with reduced scattering than blue electromagnetic radiation. Thus, different opsins with red-shifted activation wavelength have been proposed [43], [44].

#### Opsins for inhibition of neural activity

Inhibition of neural activity comprises the hyperpolarization of neuronal membrane in order to suppress AP. NpHR is a widely used halorhodopsin – light-gated ion pump– that hyperpolarize the neuronal membrane by pump-ing ions into the cell [45]. A series of revision were made in order to improve the performance of this opsin, leading to the development of eNpHR3.0 [46]. eNpHR3.0 has its maximum excitation at 590 nm and it thus can be driven by green, yellow or red light sources.

However, there are two limitations when using light-gated pumps for inhibiting neural activity. First, these pumps are less efficient than excitatory channel opsins. In other words, the rate of ions per absorbed photon flowing through the channel is much higher in excitatory opsins than in the inhibitory ones [36]. Second, techniques used to increase the light sensitivity cannot be used in pumps in an efficient manner.

### 1.4.2 Light interaction in cerebral cortex

There is another concern to think about when delivering light to the tissue: *irradiance*. Light *irradiance* is defined as the optical power or flux per unit area striking a surface. In this regard, there is a threshold that have to

be overcome in order to successfully evoke AP. In the case of ChR2, the irradiance threshold is  $\approx 1 \,\mathrm{mW}\,\mathrm{mm}^{-2}$  [47].

When the light radiation strikes the neural tissue, a number of light-medium interactions occur. Thus, light intensity and propagation direction might change [48]. Among these interactions one can find reflection, refraction, absorption, and scattering. Even though the analysis of such interactions is outside the scope of this thesis, it is worth noting that absorption –the conversion of light into heat in the tissue– can lead to an increase in the neural tissue temperature. Since many physiological processes are sensitive to temperature, the amount of irradiance delivered has to be carefully set in order not to unwillingly alter brain function [49].

### Chapter 2

## Literature Review of Neural Stimulators

This chapter introduces some fundamental concepts of neural stimulator from an electrical perspective and presents an analysis of state-of-the-art neural stimulators.

# 2.1 An introduction to neural stimulators from an electrical perspective

In this section, neural stimulators are analysed from an electrical point of view. First, the major approaches for implementing neurostimulators are compared. Second, the importance of compliance voltage is highlighted. Third, particularities of optical neurostimulators are remarked.

### 2.1.1 Types of neural stimulators

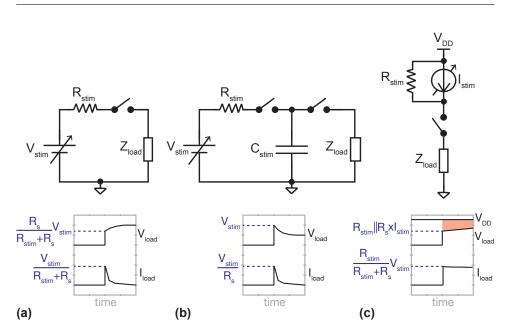

Fig. 2.1(a-c) show the three major approaches used for implementing neural stimulators: Voltage-Controlled Stimulator (VCS), Switched-Capacitor Stimulator (SCS), and Current-Controlled Stimulator (CCS). It also shows the load current,  $I_{load}$ , and load voltage,  $V_{load}$ , waveforms obtained during stimulation.

In VCS, a stimulation voltage is directly applied to the neural tissue during a certain period of time. Alternatively, in SCS a previously charged capacitor

Figure 2.1: Conceptual electrical schemes for the major approaches for neural stimulators. (a) Voltage-Controlled Stimulator (VCS), (b) Switched-Capacitor Stimulator (SCS), and (c) Current-Controlled Stimulator (CCS).

is discharged through the neural tissue. Last, in CCS the current source draws a certain level of current from the supply voltage to the neural tissue.

These approaches can be compared in terms of energy efficiency and precision at charge delivering. For that purpose, efficiency is defined as defined as the power delivered to the load,  $P_{load}$ , divided by the power drawn from the stimulator's power source,  $P_{stim}$

$$\eta = \frac{P_{load}}{P_{stim}}.$$

(2.1)

Besides, precision at charge delivering can be obtained from the definition of charge

$$Q_{load} = \int_0^{T_{stim}} I_{load}(t) dt, \qquad (2.2)$$

where  $T_{stim}$  corresponds to the stimulation time and  $I_{load}(t)$  is the instantaneous current delivered to the neural tissue. Next, (2.1) and (2.2) are particularized for the three types of electrical stimulators by modelling both the neural tissue and ETI with its electrical equivalent –shown in Fig. 1.1–, but considering that  $R_f \to \infty$  for simplicity.

The expression of efficiency of VCS is

$$\eta_{VCS} = 1 - \frac{1}{2} \frac{R_{stim}}{R_{stim} + R_s} \frac{1 - exp\left(-2\frac{T_{stim}}{(R_{stim} + R_s)C_{dl}}\right)}{1 - exp\left(-\frac{T_{stim}}{(R_{stim} + R_s)C_{dl}}\right)} \approx \frac{R_s}{R_s + R_{stim}}, \quad (2.3)$$

where  $R_s$  and  $C_{dl}$  are the extracellular fluid resistance and the doublelayer capacitance, as shown in Fig. 1.1. The approximation is valid for  $T_{stim} << (R_{stim} + R_s)C_{dl}$ . Since  $R_s$  is usually in the range of some kiloohms, efficiencies above 90% can be obtained for moderate values of  $R_{stim}$ .

In the case of SCS, power efficiency is maximum when  $C_{stim}$  is discharged to the load. However, the efficiency when charging  $C_{stim}$  to  $V_{stim}$  is

$$\eta_{SCS} = 1 - \frac{1}{2} \frac{1 - exp\left(-2\frac{T_c}{R_{stim}C_{stim}}\right)}{1 - exp\left(-\frac{T_c}{R_{stim}C_{stim}}\right)} \approx 0.5, \qquad (2.4)$$

where  $T_c$  is the charging time and the approximation holds for  $T_c >> R_{stim}C_{stim}$ .

Regarding CCS, power efficiency was calculated assuming  $R_{stim} \to \infty$  for simplicity

$$\eta_{CCS} = \frac{I_{stim} T_{stim}}{V_{DD}} \left( R_s + \frac{T_{stim}}{2C_{dl}} \right).$$

(2.5)

Power efficiency in CCS depends on how close  $V_{DD}$  is to  $V_{load}$  because the larger that voltage difference the larger the power losses at  $I_{stim}$  –as depicted by the shaded region in Fig. 2.1(c)–. It is thus desirable to have a programmable voltage supply,  $V_{DD}$ , in order to maximize power efficiency.

The charge delivered by a VCS is

$$Q_{stim,VCS} = V_{stim}C_{dl} \left[ 1 - \exp\left(-\frac{T_{stim}}{(R_{stim} + R_s)C_{dl}}\right) \right] \approx \frac{V_{stim}T_{stim}}{R_{stim} + R_s},$$

(2.6)

where the approximation holds if  $T_{stim} \ll (R_{stim} + R_s)C_{dl}$ . Charge delivered is strongly dependent on  $R_s$ .

The charge delivered by an SCS is

$$Q_{stim,SCS} = V_{stim} \frac{\tau_{SCS}}{R_s} \left[ 1 - \exp\left(-\frac{T_{stim}}{\tau_{SCS}}\right) \right], \qquad (2.7)$$

$$Q_{stim,SCS} \approx \frac{V_{stim} T_{stim}}{R_s},$$

(2.8)

which shows that stimulation charge is also highly dependent on  $R_s$ . Finally, the stimulation charge in CCS is

$$Q_{stim,CCS} = R_{stim}C_{dl} \left[ 1 - \exp\left(-\frac{T_{stim}}{\tau_{CCS}}\right) \right], \qquad (2.9)$$

where  $\tau_{CCS} = (R_s + R_{stim}) \cdot C_{dl}$ . Assuming that  $T_{stim} \ll \tau_{CCS}$

$$Q_{stim,CCS} = \frac{R_{stim}}{R_{stim} + R_s} I_{stim} T_{stim}, \qquad (2.10)$$

which shows that, even with moderate values of  $R_{stim}$ , stimulation charge is highly controlled in CCS.

The analysis of these three approaches for electrical stimulation is summarized in Table 2.1. VCS achieves the best power efficiency but charge delivered is load-dependent. SCS has a 50% efficiency but the charge delivered is also load-dependent. Finally, CCS achieves load-independent charge delivery at the cost of a power efficiency which depends on the load, the stimulation current, and the supply voltage. Given these characteristics, most of the neural stimulators found in the literature implement CCS topologies in which most design effort is put into maximizing power efficiency. This thesis intends to make a contribution in this endeavour.

#### 2.1.2 Optical Neural Stimulators

Optical neurostimulation is carried out by driving a Light-Emitting Diode (LED) or a laser diode in order to deliver light to neural tissue. In either way, the neurostimulator must deliver a precise and constant light irradiance to

| Type           | Efficiency    | Precision at charge delivering | Fully integrable |

|----------------|---------------|--------------------------------|------------------|

| VCS            | >90%          | Load-dependent                 | Yes              |

| $\mathbf{SCS}$ | 50%           | Load-dependent                 | No               |

| CCS L          | oad-dependent | Load-independent               | Yes              |

Table 2.1: Qualitative comparison of different electrical neurostimulation approaches.

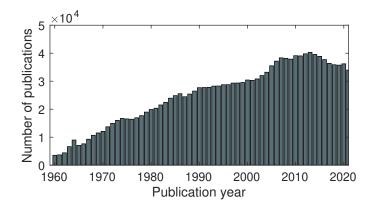

Figure 2.2: Evolution of results appearing in PubMed's search engine when aggregating results for "neural stimulation" and "neuromodulation".

neural tissue. Thus, they are usually implemented with the CCS approach, as shown in Fig. 2.1(c).

Optical stimulation pulses are also delivered at frequencies below 1 kHz, and pulse widths can be well below 100 µs. However, in Optical Neural Stimulators (ONSs) charge balancing is not an issue anymore. Thus, the setting time constraints are less restrictive than in Electrical Neural Stimulators (ENSs).

The neural stimulator here presented was designed to comply with electrical stimulation specifications, but it can also be used as an optical neural stimulator.

## 2.2 Literature review

In the last decades, a vast amount of scientific literature related to neuromodulation has been published –see Fig. 2.2–. There is thus a need of implantable devices that health researchers can use for exploring and modulating the brain activity. Mixed-signal ASIC designers have been working on offering solutions for the design and development of integrated circuits that meet this need. In this regard, challenges in the design of cutting edge neural stimulators are:

• Charge balance. Biphasic stimulation demands that the charge delivered during both stimulation phases is the same so as to have zero net charge stored at the ETI after a stimulation round [15].

- Compliance voltage. The ETI depends on the geometry and materials of the electrodes; the physiological parameters of the tissue; and the degree of electrical contact at the stimulation zone [15]. Further, the interface is not stationary in nature and the impedance changes throughout the life cycle of the implant. These factors make that the voltage compliance of the neural stimulator front-end varies from a few volts up to over 10 V.

- WPDT. Wired transmission of power and data should be avoided in order to maximize the safety of the implant. The design of highly-efficient fully-implantable WPDT systems is a challenging topic which is experiencing a great development in the last decade [7], [50]–[57].

- Power efficiency. Power dissipation in the form of heat should be minimized for long-term safety of the implant. Besides, a wirelesslypowered implant should demand as little power as possible in order to relax the specifications of the wireless power supply and expand the autonomy of the implant. Both things depend on increasing neural stimulator's power efficiency as much as possible.

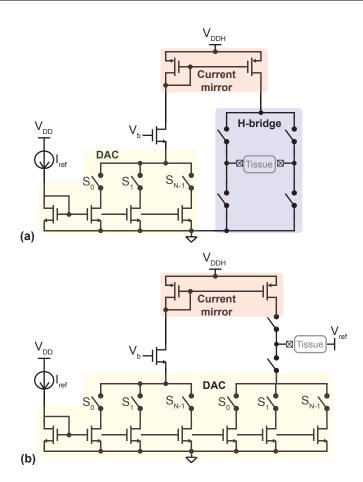

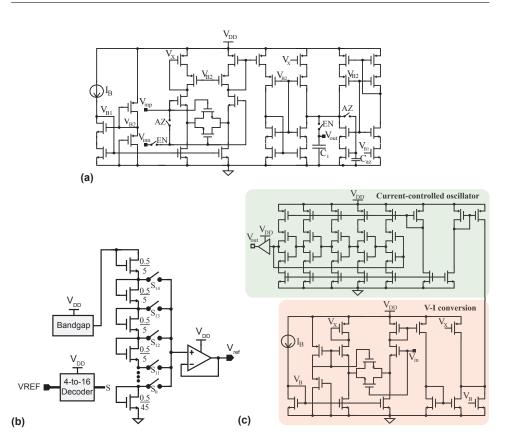

Neural stimulators with programmable power supply have been widely studied in the literature. In the case of CCS, they are usually implemented either with single or dual current sources, as shown in Fig. 2.3. Fundamental parts of these stimulator topology are: the current-steering Digital-to-Analog Converter (DAC), current mirror, switches, and DC-DC converter for generating  $V_{DDH}$ .

In [58], a CCS with on-chip voltage generator was proposed. It uses a single current source for delivering asymmetrical biphasic pulses. The circuit achieves a 11.5 V compliance voltage, but it was implemented in a 180 nm HV CMOS process. Besides, the DC-DC converter has limited programmability and lacks a regulation loop. A high-voltage-tolerant neurostimulator with an on-chip regulated 5-stages charge pump was proposed in [59]. Implemented in a 180 nm 1.8V/3.3V CMOS process, the compliance voltage reaches 10 V. Nonetheless, power efficiency of the solution was not discussed. Besides, the stimulation current is fixed at 30 µA and charge balancing was not tackled.

Another CCS with programmable power supply was presented in [60]. Implemented in a standard CMOS process, an on-chip voltage generator provides an adjustable voltage supply from 6.7 V up to 12.3 V. A dynamic gate biasing circuit that controls the state of some stacked transistors is proposed for having a compliance voltage up to  $3 \times V_{DD}$ . Nonetheless, the different

Figure 2.3: Current-Controlled Stimulator (CCS). (a) Single current source. (b) Dual current sources.

power supplies needed for biasing the H-bridge do not adapt to  $V_{DDH}$ . Thus, it is expected that the H-bridge shows a non-negligible on-resistance in situations with small  $V_{DDH}$ , leading to lower power efficiency.

A slightly different approach was followed in [61], where a Dickson ladder DC-DC converter was implemented to dynamically supply the neural stimulator front-end. The adiabatic solution permits charge recycling but no programmability for disabling unused stages of the Dickson ladder were devised. Besides, there is no regulation loop for locking the output voltage of the DC-DC converter to some reference value. It implements a single current source topology in which a discharging phase can be triggered to

remove any residual charge. However, no experimental results on this were reported.

A CCS implementing the topology shown in Fig. 2.3(b) is discussed in [62]. It was implemented in a standard CMOS process and it delivers up to 3 mA of current and uses an on-chip  $\pm 6$  V voltage generator. A maximum current mismatch between anodic and cathodic phases of 1.94% is reported. Thus, a discharging phase lasting 2 ms has to be applied after some stimulation rounds in order to limit the charge stored at the ETI.

SCSs have also been addressed in the literature [63], [64]. Even though good efficiencies are generally reported, they all rely on off-chip capacitors. Besides, load-dependent charge delivery and charge mismatch are intrinsic disadvantages of this topology.

VCSs have received less attention because charge delivery is highly loaddependent. In [65], a  $3 \times V_{DD}$  compliant neural stimulator is shown. However, no on-chip voltage generator was reported. In [66], a stimulator delivering 1.5-4.5 V pulses with on-chip voltage generator is presented. Nonetheless, power efficiency is low and residual charge is not discussed.

A VCS based on a buck-boost converter is presented in [67]. The system was implemented in a 180 nm HV CMOS process and uses a  $22 \,\mu\text{H}$  inductor as the only off-chip component. It shows efficiencies around 40% for average output powers above 5 mW. Though, power efficiency rapidly drops at lower output power values. Besides, an external 20 V supply is needed and residual charges left at the ETI after biphasic stimulation rounds were not discussed.

As it was pointed out, most of this thesis is devoted to the design of a fully integrated CCS with high compliance voltage in a standard CMOS process. Thus, it builds on the knowledge reported in previous works such as [59]–[62]. Both discussed and additional references are listed in Table 2.2 and Table 2.3.

| Ref. Year Process                                                         | Type             | Ranges                                                               | Supply                                                                           | Charge<br>balancing   | $\frac{\rm Area/ch}{\rm (mm^2)}$ |

|---------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|----------------------------------|

| [30] 2013 (HV)                                                            | Biphasic<br>CCS  | $\begin{array}{c} 0.5\mathrm{mA}\\ (6\mathrm{bits}) \end{array}$     | $\begin{array}{c} 3{,}6{,}9{,}12\mathrm{V}\\ \mathrm{(unregulated)} \end{array}$ | No                    | 0.35                             |

| [59] 2014 $\frac{0.18 \mathrm{nm}}{(\mathrm{LV})}$                        | Biphasic<br>CCS  | $30\mu A$                                                            | $4.510\mathrm{V}$                                                                | No                    | -                                |

| $[61] 2015 \frac{65 \mathrm{nm}}{(\mathrm{LV})}$                          | Biphasic<br>CCS  | $\begin{array}{c} 0.9\mathrm{mA} \\ (6 \mathrm{\ bits}) \end{array}$ | 1.3-9.1 V                                                                        | Electrode<br>shorting | 0.068                            |

| $[63] 2015 \frac{0.35\mu\mathrm{m}}{(\mathrm{LV})}$                       | Biphasic<br>SCS  | 5 bits                                                               | $2\mathrm{V}$                                                                    | Charge calculation    | -                                |

| [65] 2015 $\frac{0.18\mu m}{(LV)}$                                        | VCS              | Up to $9.9\mathrm{V}$                                                | $9.9\mathrm{V}$                                                                  | No                    | 0.10                             |

| [66] 2016 $\frac{0.18\mu m}{(LV)}$                                        | Biphasic<br>VCS  | 1.5-4.5 V<br>(5 bits)                                                | 1 V                                                                              | No                    | -                                |

| $[67] 2016 \frac{0.18\mu\mathrm{m}}{(\mathrm{HV})}$                       | Biphasic<br>VCS  | $<\!20\mathrm{mA}$                                                   | $20\mathrm{V}$                                                                   | Pulse<br>insertion    | -                                |

| $[68] 2017 \frac{0.18\mu\mathrm{m}}{(\mathrm{LV})}$                       | Biphasic<br>CCS  | $\begin{array}{c} 0.25\mathrm{mA}\\ (8 \mathrm{\ bits}) \end{array}$ | $3.3\mathrm{V}$                                                                  | Charge calculation    | 0.078                            |

| [64] 2017 $\frac{0.18\mu m}{(HV)}$                                        | Biphasic<br>SCS  | $190\mathrm{nC}$                                                     | $5\mathrm{V}$                                                                    | Pulse<br>insertion    | 0.035                            |

| $[69] 2017 \frac{0.13\mu\mathrm{m}}{(\mathrm{LV})}$                       | Arbitrary<br>CCS | $\begin{array}{c} 1.35\mathrm{mA}\\ (8 \mathrm{\ bits}) \end{array}$ | $3.3\mathrm{V}$                                                                  | Electrode<br>shorting | 0.130                            |

| [70] 2018 $\frac{0.18\mu m}{(HV)}$                                        | Biphasic<br>CCS  | $5 \mathrm{mA}$<br>(8 bits)                                          | $15\mathrm{V}$                                                                   | Electrode<br>shorting | -                                |

| [71] 2018 $\begin{array}{c} 0.6\mu\mathrm{m}\\ (\mathrm{HV}) \end{array}$ | Chopped<br>CCS   | $1 \mathrm{mA}$<br>(8 bits)                                          | $12\mathrm{V}$                                                                   | Charge calculation    | -                                |

| [60] 2018 $\frac{0.18\mu m}{(LV)}$                                        | Biphasic<br>CCS  | $3 \mathrm{mA}$<br>(4 bits)                                          | $6.7	ext{-}12.3\mathrm{V}$                                                       | Electrode<br>shorting | -                                |

| [72] 2018 $\frac{0.18  \mu m}{(HV)}$                                      | Biphasic<br>CCS  | 5.1 mA<br>(7 bits)                                                   | $5 \mathrm{V}$ (prog)                                                            | Electrode<br>shorting | -                                |

| [73] 2018 $\frac{0.18  \mu m}{(HV)}$                                      | Biphasic<br>CCS  | $\begin{array}{c} 3.15\mathrm{mA}\\ (6 \mathrm{\ bits}) \end{array}$ | $30\mathrm{V}$                                                                   | Charge calculation    | 0.260                            |

| [74] 2019 $\frac{0.18\mu\text{m}}{(\text{SOI})}$                          | Biphasic<br>CCS  | $\begin{array}{c} 145\mu\mathrm{A}\\ (5\mathrm{bits}) \end{array}$   | $1\text{-}3.9\mathrm{V}$                                                         | Electrode<br>shorting | 0.220                            |

Table 2.2: Performance comparison of neural stimulators reported in the literature.

| Ref. Yea  | ar Process                                   | Type                 | Ranges                                      | Supply          | Charge<br>balancing | $\frac{\rm Area/ch}{\rm (mm^2)}$ |

|-----------|----------------------------------------------|----------------------|---------------------------------------------|-----------------|---------------------|----------------------------------|

| [75] 201  | $9 \frac{0.18  \mu m}{(HV)}$                 | Biphasic<br>CCS      | 21.7 mA<br>(10 bits)                        | 5-24 V          | No                  | -                                |

| [76] 201  | 0.12.000                                     | Biphasic             | $\frac{(10 \text{ bits})}{1.86 \text{ mA}}$ | 2 V             | Electrode           |                                  |

| [76] 2019 | (LV)                                         | CCS                  | (5  bits)                                   | ZV              | shorting            | -                                |

| [77] 201  | $9 \frac{0.18  \mu m}{(LV)}$                 | Biphasic<br>CCS      | $0.3\mathrm{mA}$<br>(4 bits)                | $3.3\mathrm{V}$ | Electrode shorting  | -                                |

| [78] 2020 | 65 nm                                        | Biphasic             | 2 mA                                        | X-11 V          | Electrode           | 0.360                            |

|           | (LV)                                         | CCS                  | (8  bits)                                   | <u> </u>        | shorting            |                                  |

| [79] 202  | $20 \frac{0.25\mu\mathrm{m}}{(\mathrm{HV})}$ | Biphasic<br>CCS/VCS  | $5 \mathrm{mA}/10 \mathrm{V}$<br>(6 bits)   | $20\mathrm{V}$  | Electrode shorting  | 0.220                            |

| [62] 202  | 0.18 μm                                      | Biphasic             | 3.2 mA                                      | $6\mathrm{V}$   | Electrode           | 0.080                            |

|           | (LV)                                         | $\operatorname{CCS}$ | (7  bits)                                   |                 | shorting            | 0.000                            |

Table 2.3: Performance comparison of neural stimulators reported in the literature (cont).

# Chapter 3

# Wireless Power and Data Transfer

In this chapter, the wireless transfer of power and data from an external unit to/from the neural implant is tackled. On the one hand, a CMOS photovoltaic cell was designed and fabricated in a standard 180 nm CMOS process –see shown in Fig. 1(a)– to experimentally check the feasibility of performing light harvesting for powering the implant [6]. This work was done with the supervision of Prof. Juan Antonio Leñero Bardallo –whose research focuses on the design of CMOS image sensors– and the help of Ph.D. candidate Rubén Gómez Merchán. On the other hand, a topology of inductive WPDT system over a single pair of coils was studied and proposed as the main power source of the implant [7]. This work was carried out at the Swiss Federal Institute of Technology Lausanne (EPFL) with the supervision of Prof. Alexandre Schmid.

## 3.1 CMOS photovoltaic cell

This section is organised as follows. First, an introduction to CMOS photovoltaic cells is given. Second, the operation of the photodiodes used in the CMOS cell is devised. Third, experimental results are shown and discussed.

#### 3.1.1 Introduction

Diodes implemented in standard CMOS processes can be used as photodiodes if they are biased in the photovoltaic region. This can lead to selfpowered image sensors or to implantable systems that can eventually use solar energy to reduce power drawn from batteries. Different stacked diodes can be implemented using Deep N-type Well (DNW) in standard CMOS processes [80], [81]. Hence, there are many combinations possible which should be investigated for improving the performance of classic light detectors based on single isolated diodes. For instance, several authors have already implemented sensors that can concurrently sense light and harvest energy simultaneously [82]–[84]. Moreover, different diode configurations to harvest energy more efficiently have been proposed [85], [86].

#### 3.1.2 Photodiode operation

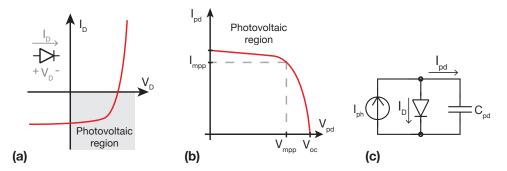

Figs. 3.1(a-c) show (a) a single diode's voltage-current curve, (b) the photovoltaic region, and (c) its electrical model, where  $I_{ph}$  is the photocurrent generated by the electron-hole pairs captured near the diode depletion region and  $C_{pd}$  models the diffusion and junction capacitances. According to this model, the DC current flowing through a single-photodiode configuration,  $I_{pd}$ , is given by

$$I_{pd} = I_{ph} - I_D = I_{ph} - I_s \left( e^{\frac{V_{pd}}{n_D U_T}} - 1 \right),$$

(3.1)

where  $I_s$  is the specific current,  $n_D$  is the emission coefficient,  $V_{pd} = V_D$  is the forward voltage of the diode, and  $I_D$  is the current flowing through the diode with no illumination.

Figure 3.1: (a) Diode I-V curve, (b) photovoltaic region, and (c) circuit model for the diode in the photovoltaic region. The optimum operating point,  $(I_{mpp}, V_{mpp})$ , provides the highest power than can be harvested. [6]

The open-circuit voltage,  $V_{oc}$ , is defined as the voltage at which no current

flows through the photodiode

$$V_{oc} = V_{pd}(I_{pd} = 0) = nU_T \ln\left(\frac{I_{ph}}{I_s} + 1\right).$$

(3.2)

To increase photodiodes' performance, two parameters have to be maximized: the current generated,  $I_{pd}$ , and the open circuit voltage,  $V_{oc}$ . The last amounts typically between 100 mV and 450 mV under usual illumination conditions in standard CMOS technologies. It is thus important to choose diode configurations that can provide the highest open-circuit voltage to maximize the operation range at which the harvested energy can be directly used to power circuits with minimum previous DC-DC conversion.

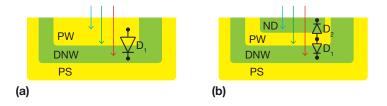

Fig. 3.2(a-b) show the two diode configurations under study. The first configuration, shown in Fig. 3.2(a), is a diode based on the P-type Well (PW)-DNW junction. The second configuration, shown in Fig. 3.2(b), adds another diode, implemented with the N-type Diffusion (ND)-PW junction, in parallel to the previous one. Another possibility based on the isolated P-type Substrate (PS)-ND junction photodiode has been discarded because its quantum efficiency is much lower than in the other cases [80].

For the double diode configuration, the contribution of each diode has to be taken into account in the current expression

$$I_{pd,double} = I_{ph_1} - I_{D_1} + I_{ph_2} - I_{D_2}$$

=  $I_{ph_1} - I_{s_1} \left( e^{\frac{V_{pd}}{nU_T}} - 1 \right)$

+  $I_{ph_2} - I_{s_2} \left( e^{\frac{V_{pd}}{nU_T}} - 1 \right)$  (3.3)

where it has been assumed that  $n_1 = n_2 = n$ . Whenever  $I_{pd,double} = 0$ , the double diode configuration's open circuit voltage,  $V_{oc,double}$ , is reached.

Figure 3.2: Photodiode configurations under study. (a) Isolated PW-DNW junction diode. (b) PW-DNW and ND-PW diodes connected in parallel. [6]

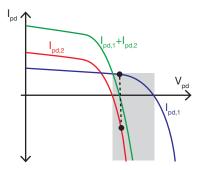

Figure 3.3: Current-voltage curves of two parallel diodes operating simultaneously. [6]

Operating with (3.3), it is easy to deduce that

$$V_{oc,double} = nU_T \ln\left(\frac{I_{ph_1}}{I_{s_1}} \frac{1 + \frac{I_{ph_2}}{I_{ph_1}}}{1 + \frac{I_{s_2}}{I_{s_1}}} + 1\right).$$

(3.4)

Comparing (3.2) and (3.4), it is deduced that  $V_{oc,double} > V_{oc,single}$  when the ratio between diodes' photocurrents and specific currents satisfies

$$V_{oc,double} > V_{oc,single} \iff \frac{I_{ph_1}}{I_{ph_2}} < \frac{I_{s_1}}{I_{s_2}}$$

(3.5)

The specific current value in an abrupt PN junction is given by this expression [87]

$$I_s = qWL\left(\frac{D_p p_n}{L_p} + \frac{D_n n_p}{L_n}\right),\tag{3.6}$$

where W and L are the diode dimensions;  $D_p$  and  $D_n$  are the holes and electrons diffusion coefficients, respectively;  $L_p$  and  $L_n$  are the holes and electrons diffusion lengths, respectively; and  $p_n$  and  $n_p$  and the minority carriers concentration in the P- and the N-regions, respectively. Doping profiles were not disclosed by the foundry.

The ratio between the specific currents can be considered constant in the photovoltaic region. Assuming similar doping profiles for the two PN-junctions,  $I_{s_1} > I_{s_2}$ , because  $D_1$  is larger than  $D_2$ . Finally, it must remarked that diodes photocurrent values in (3.4) depend on the incident light wavelength: while  $D_2$  is more sensitive to shorter wavelengths,  $D_1$  has a sensitivity peak at higher wavelengths [81], [88], [89]. Overall, if technological

Figure 3.4: Integrated test circuits to compare the two diode configurations performance. (a) Test circuit devised to gauge open circuit voltages  $(V_{oc})$ . (b-c) Astable oscillator to compare the relative photocurrents values of each diode. [6]

parameters are unknown, it is not direct to guess which diode configuration offers higher  $V_{oc}$  without a previous experimental characterization.

When the two diodes operate simultaneously in the photovoltaic region, the configuration shown in Fig. 3.2(b) is more efficient in terms of current generation. However, there may be situations in which one diode can be forward biased outside the photovoltaic region while the other one still operates in photovoltaic region. Fig. 3.3 shows this case, where the green line represents the total current of two parallel diodes with different I-V curves (blue and red lines). Note that, at  $V_{oc}$ , the first diode generates the forward current of the second one. Thus, they can compete between them degrading the performance. Hence, the resultant  $V_{oc}$  voltage has to be measured and analyzed to decide which diode configuration performs better.

Two circuits were implemented to characterise both photodiode configurations. Fig. 3.4(a) shows a circuit to measure  $V_{oc}$ , in which a buffer architecture with low offset, rail-to-rail operation and large current driving capability was chosen [90]. Fig. 3.4(b) shows an astable oscillator that pulses with a frequency proportional,  $f_{osc}$ , to illumination [80]

$$f_{osc} \approx \frac{I_{pd}}{C_{int} \cdot V_{th}},\tag{3.7}$$

where  $C_{int} = C_{pd} + C_{par}$  accounts for all the parasitic capacitances at the input node of the comparator. Hence, if the two diode configurations gener-

Figure 3.5: (a) Chip microphotograph. The array of 7800 photodiodes with dimension of  $15 \,\mu m x 15 \,\mu m$  is highlighted in green. The array of 684 Metal-Insulator-Metal (MIM) capacitors with dimension of  $30 \,\mu m x 30 \,\mu m$  is highlighted in blue color. Test circuits depicted in Fig. 3.4 are surrounded by yellow lines. (b) Experimental setup devised to characterize both diode configurations. [6]

ate pulses with the same frequency, the double diode is generating a higher current.

#### 3.1.3 Experimental results

Fig. 3.5(a) shows a micro-photograph of the test chip implemented in a standard 180 nm 1.8V/3.3V CMOS process. It contains (1) an array of 7800 photodiodes –with the configuration shown in Fig. 3.2– with dimensions of 15 µmx15 µm and connected to an array of 684 MIM capacitors with dimensions of 30 µmx30 µm; and (2) test circuits shown in Fig. 3.4(a-b) for characterizing both diode configurations. Fig. 3.5(b) depicts the experimental setup used for the extensive characterization of both photodiode configurations.

Fig. 3.6 shows both photodiode configurations' open-circuit voltage for different illumination levels. For the two diode configurations,  $V_{oc}$  depend logarithmically on  $I_{ph}$ . Besides,  $V_{oc}$  is always higher in the double diode configuration. It can thus be assumed that, for some wavelengths towards blue and green, the ND-PW top diode contributes positively with current

Figure 3.6: Open-circuit voltage,  $V_{oc}$ , versus illumination. [6]

values that decrease the current ratio  $I_{ph_1}/I_{ph_2}$ , satisfying the condition of (3.5) to achieve a higher  $V_{oc}$ . This spectral response is consistent with prior results reported by several authors that have already studied the spectral sensitivity of these diodes separately [81], [88]. Under typical illumination values in indoor environments,  $V_{oc}$  ranges between 300 mV and 400 mV. In outdoor environments on sunny days,  $V_{oc} \in [410, 500]$  mV. For low illumination values,  $V_{oc}$  tends to zero.

Fig. 3.7 depicts current measurements performed. Since the light source was close to the chip, their temperature could affect the measurements. To avoid that, temperature was monitored with a thermometer and kept constant at  $35,^{\circ}$ C during the experiment. Illuminance on sunny days ranges roughly between 30 klux and 100 klux, thus the  $18 \,\mu\text{W}\,\text{mm}^{-2}$  harvested at 79 klux serve as a reference value of the amount of power that can be harvested in a standard CMOS process. Given these results, a  $20 \,\text{mm}^2$  CMOS solar cell mounted on the external unit of the neural interface might be enough for powering the implanted side when it not in stimulation mode.

# 3.2 Inductive Wireless Power and Data Transfer (WPDT) system

This section is organised as follows. First, an introduction to inductive WPDT is given along with the main limitations of topologies with a single pair of coils. Second, the proposed topology of WPDT system is described. Third, simulation results of an electrical model are shown and discussed.

Figure 3.7: Measurements on the photodiode array for different illumination values. (a) Current-voltage curves. (b) Power-voltage curves. [6]

#### 3.2.1 Introduction

WPDT systems are widely used in many applications such as Near-Field Communication (NFC) systems and Implanted Medical Devices (IMD) [91]–[93]. In the latter, the WPDT subsystem allows the implant to be powered and programmed without the need of wires, thus minimizing the risk of infection.

In electrical neuro-modulators, currents from a few hundreds of microamperes up to some milliamperes must be delivered in multiple stimulation sites. Thus, the power demand of the system can range from under 1 mW up to tens of milliwatts. Besides, real time monitoring of neural activity requires sending data from the electrical neuro-modulator to the external unit at rates –i.e. UDT– above 1 Mbps.

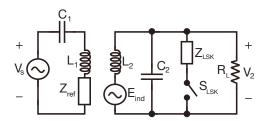

To illustrate how WPDT can be performed over a single inductive link, a simplified system is shown in Fig. 3.8. For the sake of simplicity, the

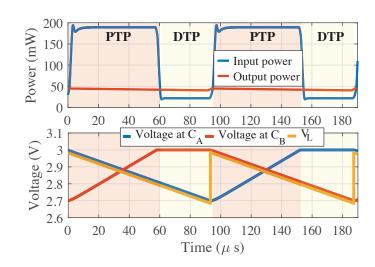

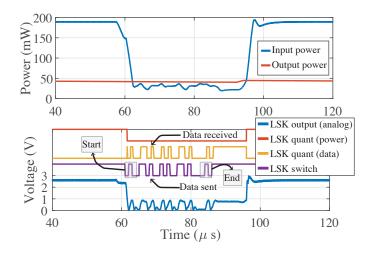

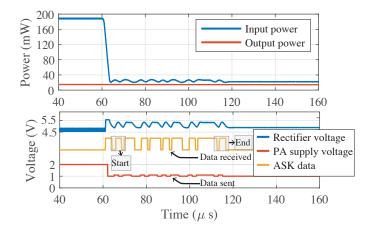

Figure 3.8: Simplified schematic of a resonant inductive WPDT system. Downlink data transfer is performed with ASK by changing the amplitude of  $V_s$ . Uplink data transfer is performed with LSK. [7]