OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

①Número de publicación: 2 373 282

Número de solicitud: 200930175

51 Int. Cl.:

HO3M 1/10 (2006.01)

(12)

# PATENTE DE INVENCIÓN

В1

22 Fecha de presentación:

14.05.2009

43 Fecha de publicación de la solicitud:

02.02.2012

Fecha de la concesión:

05.12.2012

45) Fecha de publicación del folleto de la patente:

18.12.2012

(73) Titular/es:

CONSEJO SUPERIOR DE INVESTIGACIONES CIENTÍFICAS (CSIC) (67.0%) SERRANO, 117 28006 MADRID, (Madrid), ES y UNIVERSIDAD DE SEVILLA (33.0%)

(72) Inventor/es:

GINÉS ARTEAGA, Antonio José; PERALÍAS MACÍAS, Eduardo José y RUEDA RUEDA, Adoración

74 Agente/Representante:

PONS ARIÑO, Ángel

(54) Título: PROCEDIMIENTO ADAPTATIVO DE CALIBRACIÓN DÍGITAL CONCURRENTE DEL OFFSET EN COMPARADORES EN CONVERTIDORES ANALÓGICO-DIGITALES (ADCS).

(57) Resumen:

El objeto de la presente invención es un procedimiento adaptativo para la calibración del offset de comparadores en convertidores analógico-digitales (ADCs). La técnica que implementa permite ajustar mediante un control digital de bajo coste la tensión umbral efectiva o transición de los comparadores sin afectar al camino natural de señal, y por tanto, sin interrupción de la conversión A/D de la entrada analógica. Se trata, por tanto, de una técnica de calibración concurrente.

FIG 1

t<sub>M-2</sub> t<sub>M-1</sub> t<sub>M</sub>

## DESCRIPCIÓN

Procedimiento adaptativo de calibración digital concurrente del *offset* en comparadores en convertidores analógicodigitales (ADCs).

## Objeto de la invención

El objeto de la presente invención es un procedimiento para la calibración del *offset* de comparadores en convertidores analógico-digitales (ADCs). La invención es completamente general y puede aplicarse a una arquitectura genérica de comparador La técnica que implementa permite ajustar mediante un control digital de bajo coste la tensión umbral efectiva o transición de los comparadores sin afectar al camino natural de señal, y por tanto, sin interrupción de la conversión A/D de la entrada analógica. Su aplicación a una topología de conversión directa (conocida como ADC de tipo *flash*) permite la calibración concurrente de la no-linealidad debido a dicho *offset*. La invención puede aplicarse sin restricción a otras topologías de conversión A/D que utilizan el convertidor *flash* como elemento constitutivo. Entre estas arquitecturas se incluyen las topologías sigma-delta, subranging, de interpolación, de aproximaciones sucesivas, interleaved, así como multi-etapa (también conocida como Pipeline).

## Antecedentes de la invención

20

5

En un convertidor analógico-digital, denotado como convertidor A/D o simplemente ADC (Analog to Digital Converter, según sus siglas en inglés), la cuantificación de la señal de entrada en aplicaciones de alta velocidad se realiza mediante comparadores regenerativos de tipo *latch*. Gracias a la realimentación positiva se minimiza el tiempo de decisión para un consumo específico de potencia y área, y por tanto, se puede aumentar la frecuencia de conversión. Desafortunadamente, esta arquitectura es bastante sensible al proceso tecnológico, condiciones ambientales, así como al desapareamiento entre transistores y diferencias de cargas (véase la publicación J. He, S, Zhan, D. Chen, y R. Geiger, "A simple and accurate method to predict *offset* voltage in dynamic comparators", *Proc. of IEEE Inter. Symp. on Cir. and Systems*, ISCAS, pp. 1934-1937, May 2008), presentando *offsets* aleatorios (desviaciones de los umbrales de comparación respecto a la situación ideal) que pueden llegar a alcanzar los 300 mV en los procesos CMOS actuales. La gran variabilidad de los comparadores basados en un único *latch* (conocidos como *stand-alone latch*) limita su aplicación a convertidores de muy baja precisión, con resoluciones típicas de 1-2 bits.

El problema del *offset* en los comparadores se ha tratado de reducir tradicionalmente, e independientemente de la arquitectura de ADC considerada, mediante el empleo de técnicas en el dominio analógico. En la publicación, M. Bruccoleri y P. Cusinato, "*Offset* reduction technique for use with high speed CMOS comparators", *IEE Electronics Letters*, vol. 32, no. 13, pp. 1193-1194, Jun 1996, se introdujo un comparador de tipo *stand-alone latch* con múltiples realimentaciones para la reducción del *offset*. La principal desventaja de este método, al margen de la complejidad, es que provoca un aumento de la carga en los nudos internos que obviamente se traslada a una degradación de las prestaciones dinámicas. Otra posibilidad comúnmente considerada en la bibliografía, es el uso de un preamplificador a la entrada del *latch*, con o sin fase de cancelación del *offset* propio (véase B. Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill, 2000). Aunque este bloque adicional atenúa la contribución al *offset* total del *latch* por su ganancia, introduce un aumento no despreciable en el consumo total de potencia, al mismo tiempo que incrementa el tiempo de decisión reduciendo la frecuencia máxima de operación.

Una alternativa para solventar las limitaciones de las técnicas anteriores en aplicaciones de baja potencia y alta velocidad es la calibración. Como se detalla a continuación, estos métodos pueden clasificarse en dos grupos dependiendo de si la compensación del *offset* en los comparadores afecta o no al camino natural de la señal analógica de entrada.

En el primer grupo (técnicas de calibración con fase de medida no-concurrente) se incluyen todos aquellos procedimientos que rompen el camino de entrada para inyectar un estimulo de calibración. Por la naturaleza no-concurrente del proceso de medida, estas técnicas requieren en general la interrupción de la conversión A/D de la entrada, por lo que los errores debidos al envejecimiento de los componentes o cambios ambientales (temperatura, polarización, etc.) únicamente pueden ser calibrados en los periodos de inactividad del ADC.

55

En aquellos sistemas que operan de forma continua, y por tanto no disponen de periodos de inactividad, se utilizan recursos adicionales de hardware y/o procesamiento especial de señal que permitan realizar el proceso de medida no-concurrente sin afectar a la conversión A/D. En la publicación, I. R. Nadi, R. Baird, M. M. Kostelnik y M. Wesley, "Multi-bank flash ADC array with uninterrupted operation during *offset* calibration and auto-zero", U.S. Pat. No. 6,459,394, Oct. 2002, este proceso de calibración, de aquí en adelante llamado "concurrente-virtual", se lleva a cabo mediante el empleo de hardware redundante. Se incluyen comparadores adicionales que permiten mantener la conversión A/D de la entrada mientras se realiza la caracterización del *offset* en los dispositivos seleccionados. Una vez concluida la fase de medida la función de los comparadores se intercambia y comienza un nuevo ciclo de calibración. La principal desventaja de esta aproximación, al margen de los espúreos provocados por el intercambio periódico de los comparadores, es el coste adicional en hardware y potencia debido al hardware redundante.

En las publicaciones, R. Croman, M. Goldenberg, J. P. Hein, "Method and Circuit for Calibration of Flash Analog to Digital Converters", U.S. Pat. No. 5,990,814, Mar. 1999 y M. M. Kostelnik, R. Croman, M. Goldenberg, "Offset

Calibration of Flash ADC Array", U.S. Pat. No. 6,084,538, Jul. 2000, se introdujo una técnica alternativa para la lograr la calibración concurrente-virtual. En este método se evita la duplicación de hardware, eliminando ocasionalmente una muestra de la señal de entrada, para sustituirla por un estímulo en DC que permita la compensación del offset. Para recuperar la información perdida durante el ciclo de calibración, la lógica digital realiza una interpolación de la muestra omitida reconfigurando los comparadores restantes. Al margen de la complejidad de la lógica resultante, la gran sensibilidad a la frecuencia de interpolación y la efectividad limitada para señales de alta frecuencia, esta técnica requiere un refresco periódico de las medidas de calibración ya que el valor del offset se almacena, siguiendo un método similar al introducido en B. Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill, 2000, de forma analógica en un condensador. En B. Jonsson, C. Jansson, "Comparator offset calibration for A/D converters", U.S. Pat. No. 7,075,465, Oct. 2005, se presentó un método de calibración no-concurrente que solventaba el problema de almacenamiento realizando una medida digital del offset. Durante la fase de medida de esta técnica, se interrumpe la conversión de entrada para inyectar un estímulo en DC, al mismo tiempo que se realiza un barrido en rampa de un código digital de calibración. Este código modifica mediante un convertidor digital-analógico adicional (los autores sugieren una realización capacitiva del mismo) la tensión umbral efectiva del comparador. El valor óptimo para la cancelación del offset se selecciona monitorizando independientemente la salida digital de cada comparador. De forma similar a los casos anteriores, para alcanzar un proceso de calibración concurrente (en modo virtual), esta técnica va a necesitar, bien incluir hardware adicional, con el consiguiente consumo de potencia y área, o bien omitir una de las muestras de entrada para incluir los estímulos de calibración (con la consiguiente degradación de las prestaciones debido a la interpolación).

20

25

El segundo grupo de técnicas de calibración existentes en la bibliografía, denominadas en contraposición al caso anterior "técnicas de calibración concurrente-real", realizan una corrección del *offset* en los comparadores sin afectar al camino natural de señal analógica de entrada, y por tanto, sin interrumpir la conversión A/D (fase de medida concurrente a la operación natural del comparador). Esta nueva aproximación hace uso de procedimientos digitales adaptativos de bajo coste para realizar una estimación indirecta de los códigos de calibración, sin necesidad de duplicación de dispositivos y evitando los problemas asociados a la lógica de interpolación. En la publicación, Z. Gu, W. M. Snelgrove, "A novel self-calibrating scheme for video-rate 2-step flash analog-to-digital converter", IEEE International Symposium on Circuits and Systems, ISCAS, vol.2, pp.601-604, May 1992, se propuso una técnica adaptativa para la calibración del *offset* en comparadores. Este método, basado en las propiedades estadísticas del sistema, modifica digitalmente las tensiones umbrales de los comparadores suponiendo una distribución uniforme de la señal de entrada. El gran inconveniente de este método es, como ya los autores reconocieron, que no opera correctamente cuando la distribución de entrada se aleja del caso nominal uniforme. Así en una situación genérica con una distribución arbitraria, como puede ser una señal de entrada sinusoidal o una entrada con distribución gausiana, el proceso de adaptación puede llevar a un *offset* y no-linealidad superior al estado de partida sin calibrar.

35

50

55

La dependencia del procedimiento de calibración en el estímulo particular de entrada se puede reducir mediante la inyección de una secuencia digital pseudoaleatoria en el sistema y su posterior correlación. Esta idea, originalmente desarrollada para convertidores A/D de tipo Pipeline, se ha aplicado recientemente a la calibración del *offset* en comparadores (véase C. C. Huang, J. T. Wu, "Background comparator *offset* calibration technique for flash analog-to-digital converters", U.S. Pat. No. 7,064,693, Jun. 2006). En este método se realiza, de forma similar al sistema compensación del *offset* global en ADCs propuesto en S. M. Jamal, Daihong Fu, N.C.-J. Chang, P. J. Hurst y S. H. Lewis, "A 10-b 120-msample/s time-interleaved analog-to-digital converter with digital background calibration", IEEE J. of Solid-State Circuits, vol.37, Dec. 2002, pp. 1618-1627, una modulación del *offset* del sistema commutando las entradas del comparador. Mediante este procedimiento, conocido como *chopper*, se puede obtener una estimación digital del código de calibración necesario analizando para cada comparador de forma independiente la distribución del bit de salida para los dos posibles valores de la secuencia moduladora. La mayor desventaja de esta técnica es que, al tratarse de un método basado en correlación, requiere un tiempo de convergencia bastante elevado. Este tiempo se ve incrementado notablemente al realizar la calibración de forma independiente para cada comparador, sin tener en cuenta la información del ADC completo, ya que el error de cuantización en esta situación está fuertemente correlado con la entrada.

## Descripción de la invención

Un primer aspecto de la presente invención describe un procedimiento adaptativo para la calibración digital concurrente del *offset* en los comparadores de un ADC de tipo *flash* (en lo que sigue denotado como, ADCUC, Analog to Digital Converter Under Calibration, de acuerdo con sus siglas en inglés). Teniendo en cuenta la desviación existente respecto a la situación nominal para un convertidor ideal, dicho procedimiento permite ajustar mediante un control digital de bajo coste el umbral efectivo o transición de los comparadores cancelando el error existente sin afectar al camino natural de señal, y por tanto, sin interrupción de la conversión A/D de la entrada analógica. Se trata por tanto, atendiendo a la nomenclatura introducida en la sección de revisión bibliográfica, de una implementación de calibración concurrente-real. Obviamente, la aplicación de dicho procedimiento en modo no concurrente, aunque menos interesante, es también una solución válida.

El procedimiento adaptativo propuesto evita los inconvenientes de las técnicas de calibración concurrente existentes, eliminado la necesidad de hardware redundante, suprimiendo los problemas asociados a la lógica de interpolación, y garantizando una velocidad de convergencia elevada frente a las técnicas basadas en correlación con números pseudoaleatorios, todo ello con unas modificaciones insignificantes en la topología estándar del ADCUC. Como resultado,

se van a poder relajar las especificaciones de precisión en el diseño de los comparadores, permitiendo así, un diseño optimizado en términos de potencia y velocidad. Aunque la invención es completamente general y puede aplicarse a una topología genérica de comparador con o sin preamplificador, su aplicación directa a comparadores de tipo *standalone latch* en procesos CMOS va a permitir: a) un incremento notable en la precisión por encima del límite tecnológico, b) la corrección de derivas debido a cambios en el proceso y condiciones ambientales, c) el uso de transistores con dimensiones mínimas (con las consiguientes ventajas en consumo de potencia, velocidad, ruido de *kick-back*, etc.), así como, d) la generación interna de las referencias de comparación sin red resistiva, relajando así los requerimientos del circuito de polarización.

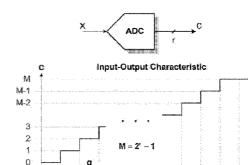

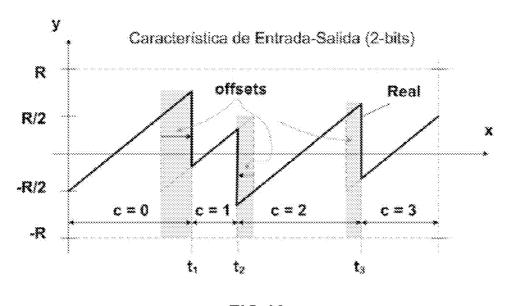

A continuación se introducen los términos y notaciones empleadas en el presente documento. Como su propio nombre indica, un convertidor analógico-digital es un sistema que traslada el valor analógico de una cierta señal x a una representación digital. El código de salida resultante c se codifica, como se muestra en la Fig. 1, mediante una palabra digital de r-bits,  $c \in [0, M]$ , donde r es la resolución del convertidor y el parámetro M define el código máximo dado usualmente por  $2^{r-1}$ .

15

20

55

60

Cada uno de los M+1 códigos identifica un zona particular dentro del rango de entrada (Full-Scale Range, FSR, según sus siglas en inglés) del ADC (FSR = 2R). De hecho, el intervalo de la entrada analógica (x) correspondiente al j-ésimo nivel digital, dónde j es un número entero que barre todos los códigos posibles desde 1 hasta M-1, viene dado por,

cuando

$$c = j \in [1, M-1] \implies x \in [t_j, t_{j+1}]$$

(1)

donde *t*<sub>j</sub> define el valor analógico correspondiente a la transición de código para el cual la salida cambia del código *j* al código *j*+1.

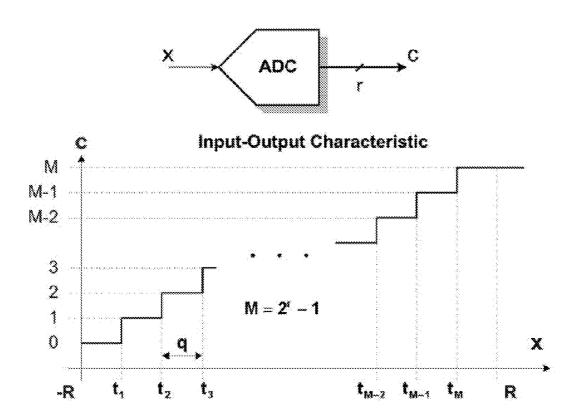

En un ADC ideal, la diferencia entre dos transiciones consecutivas, también denominada umbrales, es una constante,  $q = t_{j+1} - t_j$ , llamada cuanto del convertidor o bit menos significativo (Least Significant Bit, LSB, de sus siglas en inglés) que define la mínima resolución discriminada en el proceso del cuantización de la entrada analógica (x). El valor del cuanto ideal q puede evaluarse en función de la resolución r y referencia R del convertidor como  $q = 2R/2^r$ . En la práctica, los efectos de segundo orden en el sistema, como el desapareamiento aleatorio entre componentes, los errores de ganancia y *offset*, así como, las variaciones dependientes de cambios en la temperatura y polarización, introducen una desviación respecto al comportamiento nominal que puede degradar las prestaciones del ADC. El impacto de estos errores en el comportamiento estático se caracteriza clásicamente mediante la INL (véase el estándar de la IEEE, "IEEE standard for terminology and test methods for analog-to-digital converters", IEEE Std 1241-2000, 2001). Como se muestra en la Fig. 2, este parámetro se define como la desviación de cada transición  $t_j$  respecto a su valor ideal  $t_i^{(ideal)}$  normalizado por el LSB del convertidor,

$$INL_j = 1/q \cdot (t_j - t_j^{\text{(ideal)}})$$

(2)

Hay que destacar, que en el caso particular de un ADC de tipo *flash* la medida de la INL se encuentra directamente relacionada con el *offset* efectivo en los comparadores analógicos del ADC, en la forma,

$$off_i = (t_i - t_i^{\text{(ideal)}}) = q INL_i$$

(3)

ya que para esta topología existe un comparador específico ( $Comp_j$ ) por cada transición  $t_j$  del ADC. Por tanto, conocida la INL se tiene determinado unívocamente el *offset* en los comparadores analógicos.

Como resumen de la notación y términos empleados a lo largo del documento destacamos que:

- Denotaremos por *x* la señal analógica de entrada del ADCUC, que es el ADC de tipo *flash* con calibración del *offset* de los comparadores.

- La señal c define el código de salida del ADCUC, que generalmente vendrá afectada por los errores de nolinealidad del mimo provocados, de acuerdo con la ecuación (3), por el offset efectivo en sus comparadores.

- El código digital  $T_j$  define una estimación digital de las transiciones reales  $t_j$  del ADCUC. De forma similar, el código digital  $OFF_j$  define una estimación digital del offset ( $off_j$ ) en los comparadores.

- $T_{\rm j}^{\rm (ideal)}$  identifica los valores digitales de la transiciones correspondientes a un convertidor *flash* ideal. Nótese que fijada la resolución y la codificación del ADCUC, dichos valores se encuentra unívocamente definidos, y por tanto, se conocen *a priori*.

5

10

15

45

- El código digital  $K_j$  define la posición concreta de transición efectiva  $t_j$  en el j-ésimo comparador bajo calibración ( $Comp_j$ ). El conjunto de códigos  $K = \{K_j\}$  define los códigos de calibración para el ADCUC completo.

- La variable mayúscula X con resolución N representa una estimación digital de la entrada analógica x con mayor precisión que el código de salida del ADCUC, previamente definido por c.

- El número entero *n* es el índice de actualización del procedimiento. Salvo que sea estrictamente necesario, esta variable será implícitamente asumida para simplificar la notación.

- En lo que sigue, distinguiremos con el índice j, la transición  $t_j$  y código de calibración  $K_j$ , asociado al j-ésimo comparador ( $Comp_j$ ), definido por el código de salida c del ADCUC, es decir, j = c; mientras que el índice i es una variable muda que identifica a cualquier comparadores del ADCUC.

- Para sistemas de señal mixta en los que se realizan la calibración (de forma secuencial o simultánea) de más de un ADCUC, como puede ser en el convertidor ADC de tipo Pipeline, introduciremos, cuando sea preciso, un primer sub-índice adicional.

El procedimiento de calibración de la invención requiere, como datos de partida, además del código de salida (c) del ADCUC, una representación digital (X) de mayor precisión que c de la señal analógica de entrada (x), así como, una estimación digital  $T_i$  de las transiciones actuales del ADCUC asociadas a cada comparador ( $Comp_i$ ). Esta medida o estimación de las transiciones reales actuales  $T_i$  se puede realizar de cualquier modo concurrente que pudiera existir en la bibliografía, aunque posteriormente se describe en el presente documento un procedimiento preferido. Se entiende que dada la relación univoca existente entre INL<sub>i</sub>, la estimación digital de la transición  $T_i$  y la representación digital  $OFF_i$  del offset en el comparador, sólo es necesario conocer uno de estos valores, siendo su elección totalmente irrelevante en el procedimiento.

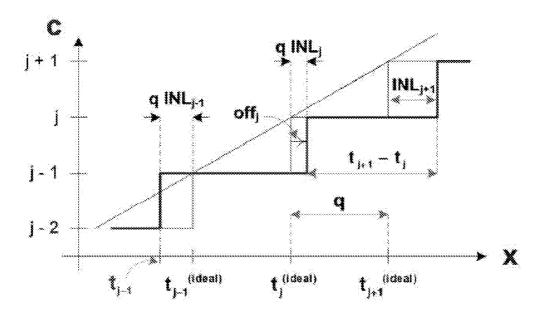

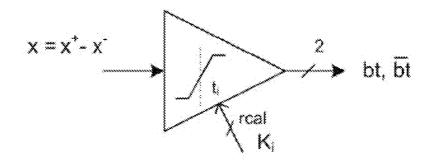

Usando los datos de partida anteriores, el procedimiento de la invención genera unos códigos de calibración,  $K = \{K_i\}$ , que aplicados a los comparadores del ADCUC, consiguen la modificación de las transiciones reales de dichos comparadores. Cada código de calibración digital  $K_i$  mueve adaptativamente la transición del comparador bajo calibración asociado ( $Comp_i$ ) para cancelar el *offset* existente. Esta cancelación del *offset* se alcanza efectivamente introduciendo un desapareamiento programable en la topología del comparador, con un paso mínimo adaptativo  $\delta$ . Aunque, como ya hemos comentado, la invención es completamente general y puede aplicarse a una arquitectura genérica de comparador con o sin preamplificador, en el caso particular de un comparador regenerativo tipo latch, el término de corrección se introduce considerando un banco de transistores programables controlado por la señal digital  $K_i$  que modifica la impedancia en algunos de los nodos internos del comparador. La Fig. 3 muestra una realización propuesta en este documento para aplicaciones de bajo voltaje sin referencia externa de comparación. La implementación considera, al margen de un desapareamiento fijo para la generación del umbral por defecto, un banco de transistores programables. Otras implementaciones de comparador programable válidas para la invención pueden estar basadas, como en K. Wong, C. Yang, "Offset compensation in comparators with minimum input-referred supply noise", IEEE I. of Solid-State Circuits, vol. 39, no. 5, pp. 837-840, May 2004, en un banco de fuentes de corrientes en paralelo, o como en D. C. Daly, A. P. Chandrakasan, "A 6b 0.2-to-0.9V Highly-Digital Flash ADC with Comparator Redundancy", IEEE Inter. Solid-State Circuits Conference, ISSCC, pp. 554-555, Feb. 2008, en la conexión en serie de transistores.

Independientemente de la realización física particular seleccionada, la posición de la transición para el comparador programable,  $Comp_i$ , viene dada por,  $t_i = t_i^{(0)} - t_{cor}(K_i)$ , donde  $t_i^{(0)}$  define la posición inicial antes de la calibración, y  $t_{cor}(K_i)$  es un término de corrección dependiente del código de calibración  $K_i$ . En el caso específico de que consideremos una codificación binaria con (rcal+1) bits para el código de calibración,  $K_i = \{-2^{rcal}, ..., -1, 0, +1, ..., +2^{rcal} -1\}$ , la anterior ecuación general puede particularizarse como,  $t_i = t_i^{(0)} - \delta \cdot K_i$ , donde  $\delta \approx off_{max}/2^{rcal}$  representa el paso adaptativo para un offset máximo corregible dado por  $off_{max}$ . Obviamente, el criterio de signo elegido para la señal  $K_i$  es totalmente arbitrario, siempre y cuando (como veremos posteriormente en el documento) se garantice una realimentación negativa en el bucle adaptativo, es decir, se puede considerar,  $t_i = t_i^{(0)} + \delta \cdot K'_i$ , con un cambio de signo consecuente en  $K'_i = K_i$ .

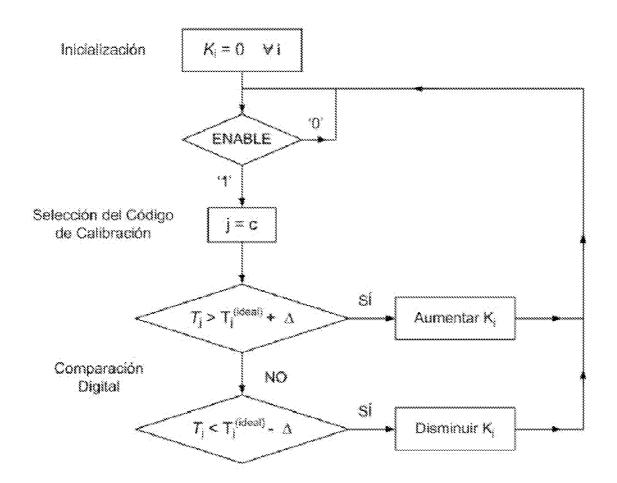

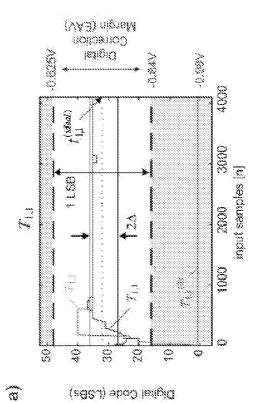

La Fig. 4 muestra un diagrama de flujo simplificado del procedimiento de generación de códigos de calibración  $K_i$  de la invención. Partiendo de un estado inicial de  $K_i=0$ , la operación adaptativa del procedimiento en una realización óptima se habilita únicamente cuando la estimación digital de las transiciones  $T_j$  definidas por el código de salida del ADCUC c (es decir, j=c) se ha modificado respecto al ciclo del procedimiento previo para dicho comparador. En esta situación, la señal digital ENABLE es igual a "1" y se selecciona el código de calibración particular,  $K_j$ , a ser actualizado. Si la estimación  $T_j$  verifica  $T_j > T_j^{(ideal)} + \Delta$ , donde  $T_j^{(ideal)}$  es el umbral nominal para el convertidor ideal y  $\Delta$  es la representación digital asociada al mínimo paso adaptativo del comparador  $\delta$ , se aumenta el valor de  $K_j$ . En caso de que  $T_j < T_j^{(ideal)} - \Delta$ , se disminuye el valor de  $K_j$ . En cualquier otra situación,  $T_j^{(ideal)} - \Delta \le T_j \le T_j^{(ideal)} + \Delta$ , el código de calibración mantiene el valor previo. Obviamente, es irrelevante el orden en que se realizan estas comparaciones, que también se podrían realizar en paralelo.

Nótese que si conocemos la resolución N considerada para la estimación digital X de la entrada analógica (x), el valor de  $\Delta$  se encuentra perfectamente definido para cada codificación particular del código  $K_j$ . Así en el caso de una codificación binaria,  $\Delta$  viene dada por  $\Delta \approx 2^N \delta/(2R)$ , donde R es la referencia analógica del convertidor. En virtud a las relaciones anteriores se hace evidente que el valor  $\delta$ , o equivalentemente  $\Delta$ , determina la precisión con la que la invención realiza la cancelación del *offset*. Una vez que el proceso adaptativo alcanza la situación estacionaria, el *offset* residual en los comparadores es inferior al mínimo paso adaptativo  $\delta$ . Téngase en cuenta que dicho *offset* residual puede reducirse aumentando el número de bits (rcal+1) que codifican la señal  $K_i$ , o bien reduciendo por consideraciones de diseño el *offset* máximo admisible,  $off_{max}$ , para el comparador.

En resumen, el procedimiento de la invención requiere poner inicialmente a cero los códigos de calibración ( $K_i$ ). A continuación, se realizan las siguientes operaciones:

- 1) Usar el código de salida digital (c) del ADCUC para seleccionar el código de calibración  $(K_j)$  particular a actualizar, así como, el valor actual real de la transición  $T_j$ , es decir, j = c. Nótese que el índice de actualización n se ha asumido implícitamente para simplificar la notación  $(c = c[n], K_j = K_j[n])$  y  $T_j = T_j[n]$ ).

- 2) A continuación, se compara el valor actual real de la transición  $T_j$  con el valor ideal de la transición  $(T_j^{(ideal)})$  más un valor  $\Delta$  correspondiente a la representación digital del mínimo paso adaptativo  $\delta$  del comparador a calibrar.

- En función del resultado de esta comparación, se realizan las siguientes acciones:

- si  $T_i > T_i^{\text{(ideal)}} + \Delta$ , aumentar  $K_i$ ;

15

20

25

30

35

- si  $T_i < T_i^{\text{(ideal)}}$   $\Delta$ , disminuir  $K_i$ ;

- En caso de que no se cumpla ninguna de las dos condiciones anteriores, no se modificaría el valor del código de calibración  $K_i$ .

- Se entiende que el orden en el que se efectúan las comparaciones anteriores es irrelevante. También se considera irrelevante un cambio de variable en el código de calibración K<sub>j</sub> consecuente con el comparador programable que mantenga la realimentación negativa en el lazo.

Nótese que los códigos de calibración  $K = \{K_j\}$  pueden actualizase utilizando un paso adaptativo constante, aunque también sería posible diseñar un procedimiento en que los pasos fuesen variables.

3) Por último, se aplica el código de calibración  $(K_j)$  calculado al comparador, consiguiéndose así la corrección del offset.

Este procedimiento de generación de códigos de calibración de la invención se realiza en modo concurrente-real sin interrumpir la conversión A/D de la entrada analógica, siendo bastante robusto a los efectos no-ideales existentes en el sistema (ruido electrónico, ruido de cuantización, distorsión, etc.). Estas propiedades van a permitir, como veremos en las realizaciones prácticas de la invención para sistemas de señal mixta con más de un ADC *flash* es su topología (como es el caso del ADC de tipo Pipeline), realizar la compensación del *offset* en varios ADCs de forma simultánea, sin provocar interferencias perjudiciales entre los mismos. Obviamente, los ADCs bajo calibración (ADCUCs) se pueden calibrar también secuencialmente, en cuyo caso se pueden rehusar parte o todos los recursos de hardware de calibración.

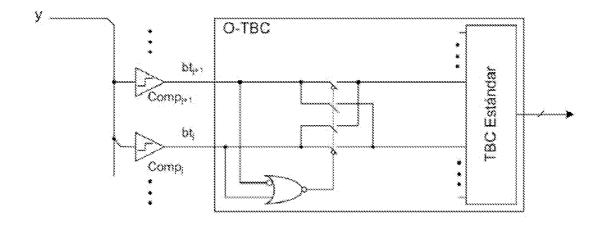

El sistema de calibración de la invención es eficiente incluso si el *offset* inicial en los comparadores del ADCUC (o ADCUCs) es superior al medio cuanto, produciéndose así, una inversión de transiciones. Para garantizar un comportamiento monótono, en esta situación, se emplea un codificador termométrico-binario (Thermometer to Binary Codifier, TBC, según sus siglas en inglés), que realiza la suma (o cuenta de unos) del código termométrico proporcionado por los comparadores, independientemente de la posición relativa entre los mismos. Una implementación posible del TBC utiliza, como en D. C. Daly, A. P. Chandrakasan, "A 6b 0.2-to-0.9V Highly-Digital Flash ADC with Comparator Redundancy", *IEEE Inter. Solid-State Circuits Conference, ISSCC*, pp. 554-555, Feb. 2008, el sumador en árbol de Wallace (véase la publicación, C. S. Wallace, "A suggestion for fast multipliers", *IEEE Trans. Electron. Comput.*, vol. EC-13, pp. 14-17, Feb. 1964). La calibración del *offset* usando un TBC basado en sumador se realiza sin considerar la relación específica entre un comparador en particular y su transición asociada, ya que esta información se elimina en el proceso de cuenta de unos. En consecuencia cada comparador ( $Comp_i$ ) tiene asociada *a priori* una transición fija  $t_i$  respecto a la cual se actualiza el código de calibración independientemente de error de *offset* existente. Aunque esta opción resulta óptima cuando el ADCUC presenta una característica monótona, es decir  $t_{i+1} > t_i$ , en el caso de *offset* superiores al medio LSB, para las cuales puede producirse una inversión de transiciones,  $t_{i+1} < t_i$ , resulta más eficiente en velocidad de convergencia realizar una reordenación de los bits de salidas de los comparadores, así como, de los códigos de calibración de los mismos.

La Fig. 5 muestra una realización particular preferente del TBC con reordenación optimizada de comparadores (O-TBC) propuesta en esta invención, constituido por un TBC estándar y un simple bloque de decisión basado en la lógica de llaves. En este sistema se sensan los bits de salida  $bt_i$  y  $bt_{i+1}$  de dos comparadores consecutivos, denotados como

$Comp_i$  y  $Comp_{i+1}$  respectivamente. Si  $bt_i$  toma el valor lógico "1", y  $bt_{i+1}$  es igual "0", se ha detectado una inversión, por lo que deben conmutarse sus valores para mantener una característica monótona en términos de transiciones. En cualquier otra situación, los bits de salidas se mantienen inalterados. Obviamente, una reordenación en los bits de salida debe ir acompañada de una conmutación entre los códigos de calibración asociados a dichos comparadores,  $K_i$  y  $K_{i+1}$ , respectivamente. La anterior realización puede extenderse al sensado de múltiples bits, para poder discriminar posibles inversiones afectado a múltiples comparadores, como por ejemplo en el caso de que  $t_i > t_{i-1} > t_{i+1}$ . Otra implementación posible para reordenar las transiciones considera una pequeña memoria.

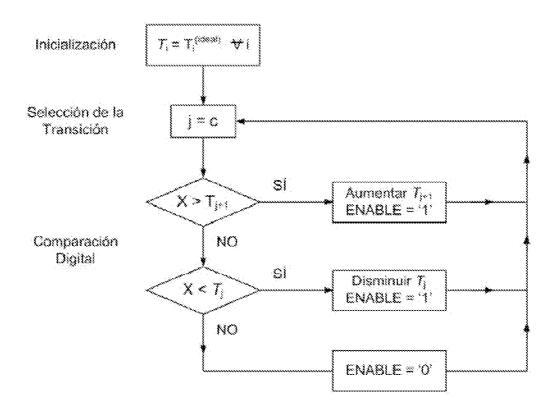

Independientemente del número de ADCUC bajos calibración, y como se ha mencionado anteriormente en el presente documento, la obtención de la estimación digital  $T_j$  de la posición actual de las transiciones  $t_i$  de un ADCUC se puede realizar de diferentes modos. En una realización preferida de la invención, esta estimación se realiza mediante un segundo procedimiento adaptativo. Este segundo procedimiento de estimación de transiciones inicializa, como se detalla en el diagrama de flujo simplificado de la Fig. 6, el valor de las estimaciones de las transiciones digitales reales  $T_j$  del ADCUC con el valor de las transiciones ideales a priori conocidas  $T_j^{(ideal)}$ . A continuación, se realizan las siguientes operaciones:

- 1) En primer lugar, se obtiene el código (c) que es de la la representación digital de la señal analógica (x) dada por el ADCUC. Esta representación digital (c), por tanto, lleva información de las transiciones reales del ADCUC.

- 2) De forma sincronizada con la operación del ADCUT, se obtiene una estimación digital (X) de la entrada analógica (x) más precisa que la representación digital (c) de la operación anterior.

- 3) Seguidamente, se compara la estimación digital (X) con las estimaciones de las transiciones digitales reales ( $T_j$ ,  $T_{j+1}$ ) donde el índice j viene dado por la representación digital (c) obtenida:

- Si  $X > T_{j+1}$ , se aumenta la estimación de la transición digital real  $T_{j+1}$ ;

- Si  $X < T_{\rm j}$  se disminuye la estimación de la transición digital real  $T_{\rm j}$ .

20

25

30

- En caso de que no se cumpla ninguna de las dos condiciones anteriores, no se modificaría el valor de ninguna de las estimaciones  $(T_i, T_{i+1})$ .

- Se entiende que el orden en el que se efectúan las comparaciones anteriores es irrelevante.

Nótese que de forma similar al procedimiento de calibración de la invención las estimaciones de las transiciones digitales pueden actualizase utilizando un paso adaptativo constante, aunque también sería posible diseñar un procedimiento en que los pasos fuesen variables.

Por último, el valor actual de las transiciones  $T_i$  se transmite a los siguientes pasos del procedimiento para la generación de los códigos de calibración correspondientes. En una realización óptima de la invención el procedimiento de calibración únicamente se habilitaría, mediante la señal ENABLE, cuando el estimación de la transición  $T_j$  definida por la salida c del ADCUC (es decir j=c) se ha actualizado. Se entiende, como ya hemos comentado previamente en el documento, que dada la relación univoca existente entre INL<sub>i</sub>, la estimación digital de la transición  $T_i$ , y la representación digital  $OFF_i$  del offset en el comparador, cualquiera de estas estimaciones u otras derivadas de éstas son válidas para el procedimiento de calibración. La elección de una de estas estimaciones es irrelevante.

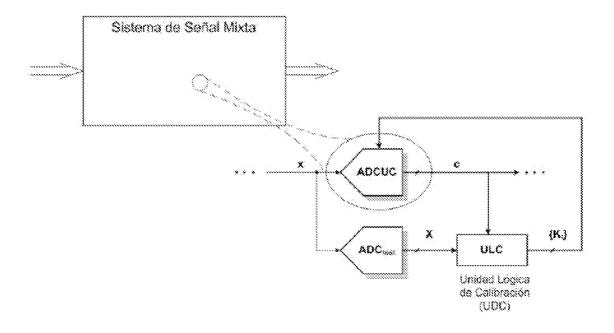

Existen diferentes modos de implementar este segundo procedimiento de estimación. Por ejemplo, la estimación digital (X) de la entrada analógica (x) se puede realizar, como se muestra en el sistema mixto genérico de la Fig. 7, empleando un ADC adicional (ADC<sub>test</sub>) dispuesto en paralelo al convertidor que se desea calibrar ADCUC y que trabaja de forma sincronizada con el mismo. Nótese que este convertidor adicional puede ser de bajo coste en potencia y área, ya que: a) su resolución debe permitir la detección del paso mínimo  $\delta$ , b) debe ser monótono sin especificaciones de linealidad relevantes, y c) puede operar a una frecuencia inferior a la del convertidor *flash* bajo calibración (ADCUC), reduciendo la frecuencia de trabajo del procedimiento. Así mismo, existe la posibilidad de controlar el ciclo de conversión del ADC<sub>test</sub> mediante un generador de número pseudoaleatorio (realizado mediante un simple registro realimentado de desplazamiento).

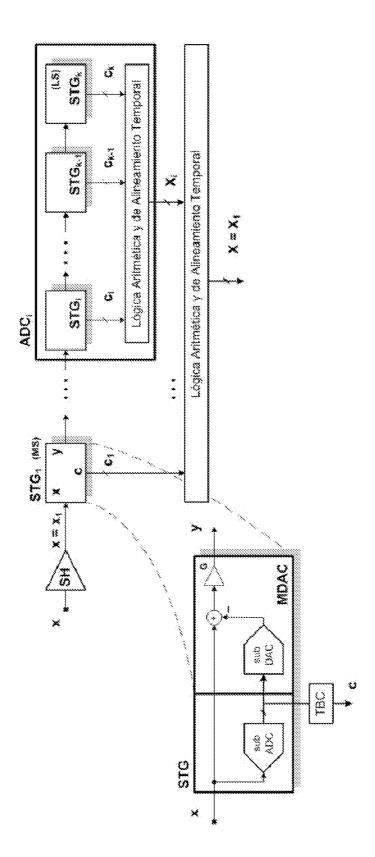

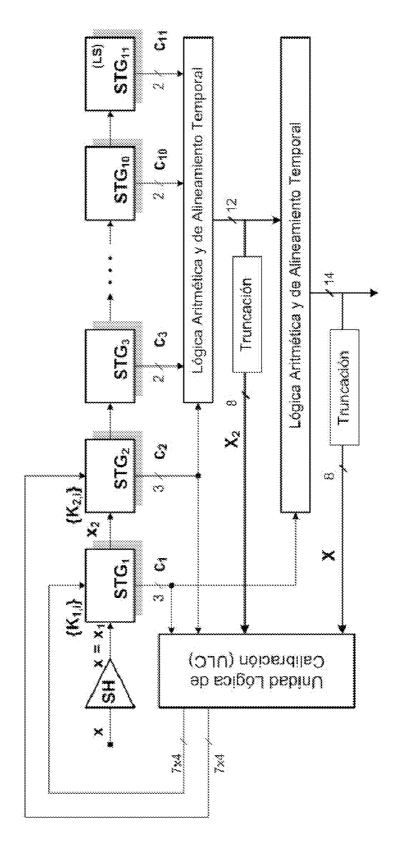

Por otro lado, en aquellos sistemas dónde exista disponible por construcción una estimación digital (X) de la señal analógica de entrada (x), la implementación del procedimiento de estimación se realiza con un coste mínimo en el dominio analógico, ya que no se requiere el ADC<sub>test</sub>. Éste es el caso, como se mostrará en detalles en la sección de realizaciones preferentes, del convertidor A/D de tipo Pipeline. Este convertidor está constituido por múltiples etapas (STGs), cada una de las cuales posee un sub-ADC de tipo flash susceptible de ser calibrado con la invención con un bajo coste, ya sea de forma simultánea o secuencial (con o sin rehuso del hardware de calibración). De hecho, la señal digital X correspondiente al i-ésimo sub-ADC bajo calibración (sub-ADCUC) dentro de la etapa (STG<sub>i</sub>) se obtiene directamente combinando el sub-código de salida de dicha etapa (c) con los sub-códigos de las etapas siguientes. Obviamente, si se desea se puede realizar una truncación de la señal digital X resultante para reducir el tamaño de palabra.

Un segundo aspecto de la presente invención está dirigido a una unidad lógica de calibración concurrente del *offset* de los comparadores de un convertidor analógico-digital (ADC) de tipo *flash*, que lleva a cabo el procedimiento de calibración descrito anteriormente, que comprende los siguientes elementos:

- a) un banco de registros (RB), que almacena el valor actual de los códigos de calibración,  $K = \{K_i\}$ , del ADCUC; en la estado inicial, dichos códigos se cargan a un valor nulo, es decir  $K_i = 0$ ;

- b) un bloque de comparación digital (CB), que compara el valor actual real de la transición  $T_i$ , donde el índice j viene definido por el código digital (c), con el valor ideal de la transición  $(T_j^{(ideal)})$  correspondiente más un valor  $\Delta$  correspondiente la representación digital del mínimo paso adaptativo  $\delta$  del comparador a calibrar, y genera un señal de de control (Sgn); en una implementación óptima este bloque será habilitado por una señal ENABLE únicamente cuando el valor de la transición  $T_i$  se haya actualizado;

- c) un bloque sumador/restador, habilitado en una realización óptima por la señal ENABLE, y controlado por (Sgn), que aumenta el código de calibración (K<sub>j</sub>) cuando T<sub>j</sub> > T<sub>j</sub> + Δ, y disminuye el código de calibración (K<sub>j</sub>) cuando T<sub>j</sub> < T<sub>j</sub> Δ.

- Una realización preferente de la unidad lógica de calibración de la invención comprende además unos medios para la estimación digital del *offset* de los comparadores del ADC, o equivalentemente la transiciones efectivas asociadas  $T_i$ . En caso de seleccionar las transiciones como variables del proceso, estos medios comprenden:

- a) un banco de registros (RB), que almacena el valor actual de un conjunto de estimaciones de las transiciones digitales (T<sub>j</sub>) del ADCUC; en el estado inicial dichos códigos se cargan con el código digital correspondiente a un convertidor ideal (T<sub>j</sub><sup>(ideal)</sup>);

- b) un bloque de comparación digital (CB), que compara la estimación digital (X) con las estimaciones de las transiciones digitales ( $T_j$ ,  $T_{j+1}$ ), donde el índice j viene definido por el código digital (c), y genera una señal de habilitación ENABLE (o simplemente EN) y control (Sgn);

- c) un bloque sumador/restador habilitado por la señal EN y controlado por (Sgn), que aumenta la estimación de la transición digital  $(T_{i+1})$  cuando  $X > T_{i+1}$ , y disminuye la estimación de la transición digital  $(T_i)$  cuando  $X < T_i$ .

- Se entiende, como ya se ha comentado anteriormente, que un cambio de variable en este procedimiento, como puede ser  $INL_i = T_i T_i^{(ideal)}$ ) u otro similar, es irrelevante en la invención.

## Descripción de los dibujos

40

Para complementar la descripción que se está realizando y con objeto de ayudar a una mejor comprensión de las características de la invención, de acuerdo con un ejemplo preferente de realización práctica de la misma, se acompaña como parte integrante de dicha descripción, un juego de dibujos en donde con carácter ilustrativo y no limitativo, se ha representado lo siguiente:

- Fig. 1. Característica de entrada-salida de un ADC ideal de r-bits con detalles de las definiciones de las transiciones  $t_i$ .

- Fig. 2. Definición del *offset* (*off*) en los comparadores con detalle de relación directa con la No-Linealidad Integral 50 (INL) en un ADC de tipo *flash*.

- Fig. 3. Implementación CMOS para aplicaciones de bajo voltaje de comparador con control digital de las transiciones considerando un banco de transistores o varactores programables en paralelo a las ramas de sensado de la señal de entrada (sin referencias de comparación externa).

- Fig. 4 Diagrama de flujo del procedimiento para la generación del código de calibración para la compensación del *offset* en los comparadores bajo calibración con comparación digital en serie.

- Fig. 5 Realización particular del TBC para reordenación de transiciones optimizada (O-TBC), basada en la lógica de llaves.

- Fig. 6. Diagrama de flujo del procedimiento digital de medida para la estimación concurrente de las transiciones efectivas de los comparadores con comparación digital en serie.

- Fig. 7 Aplicación de la invención para la calibración del *offset* en comparadores con un ADC adicional (ADC<sub>test</sub>) para la estimación digital (*X*) de la señal analógica de entrada.

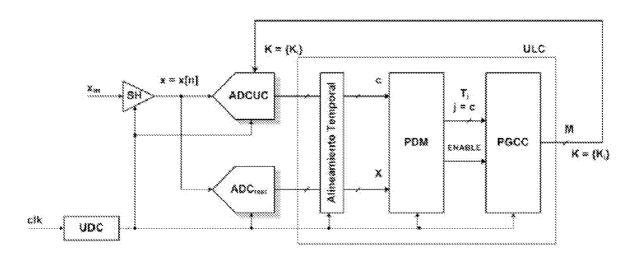

- Fig. 8. Diagrama simplificado de la realización preferente para la calibración del *offset* en comparadores en un ADC de tipo *flash*.

- Fig. 9. Diagrama simplificado de un ADC de tipo Pipeline constituido por un Sample&Hold (SH) de entrada seguido por *k* etapas desde la más significativa (MS) a la menos significativa (LS).

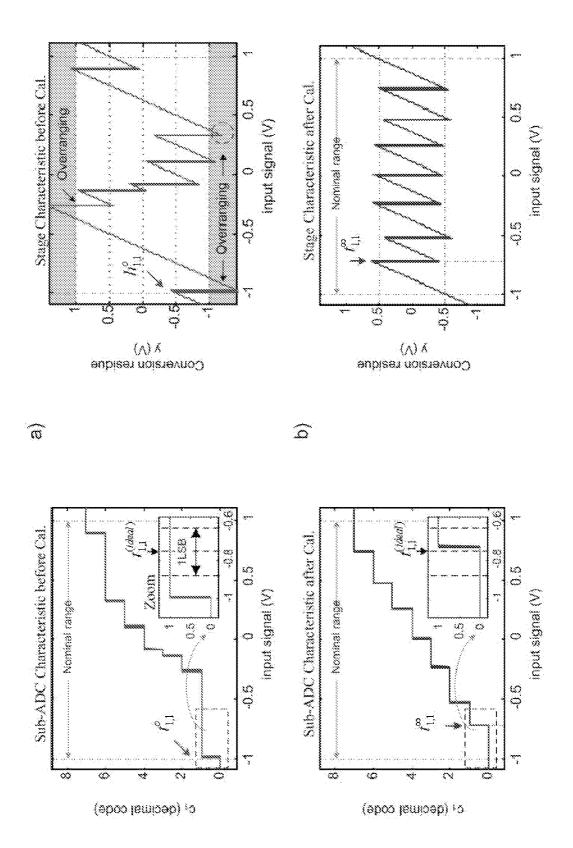

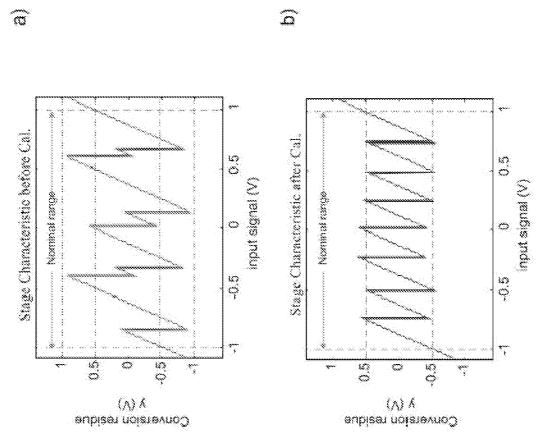

- Fig. 10. Característica de entrada-salida para una etapa de 2 bits con desviaciones en las transiciones debido al *offset* en los comparadores, ilustrando su impacto en el rango de salida (OS) del amplificador del MDAC.

- Fig. 11 Convertidor A/D Pipeline con 14 bits de resolución constituido por 2 etapas de 3 bits seguida por 9 etapas de 1.5 bits.

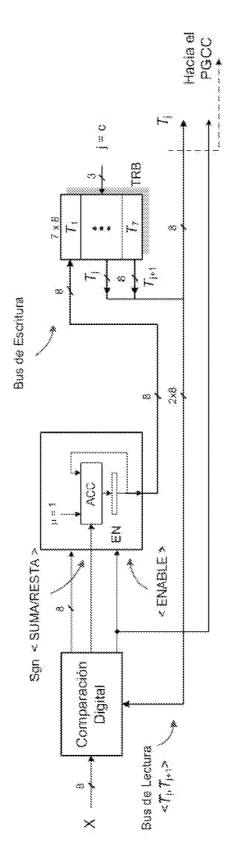

- Fig. 12 Esquema simplificado de la implementación hardware del dispositivo (PDM) para el procedimiento digital de medida considerada en el caso de estudio.

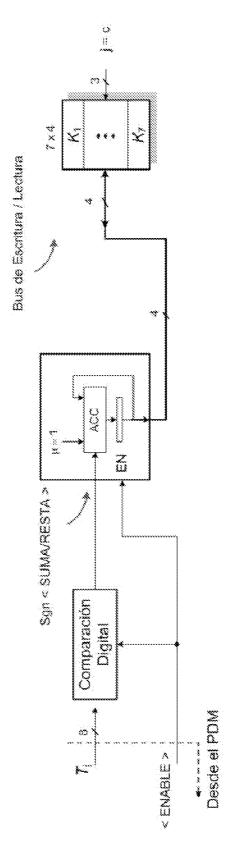

- Fig. 13 Esquema simplificado de la implementación hardware del dispositivo (PGCC) para el procedimiento de generación de códigos de calibración considerada en el caso de estudio.

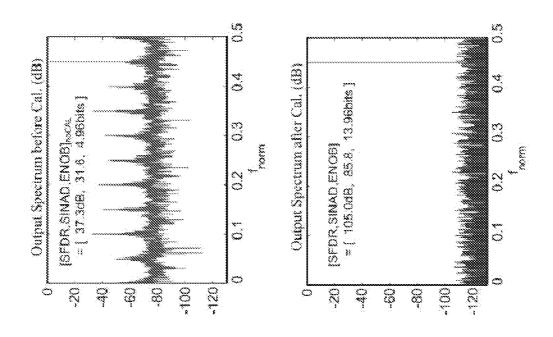

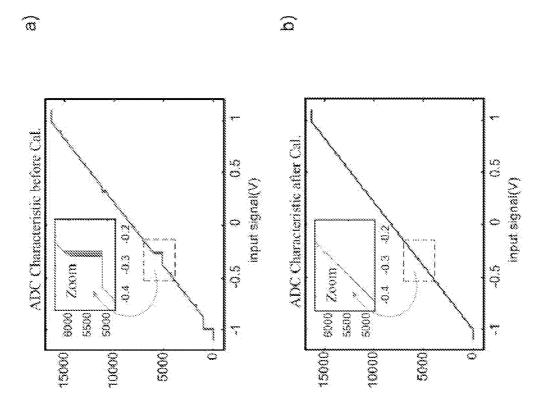

- Fig. 14 Características de entrada-salida del sub-ADC<sub>1</sub> y STG<sub>1</sub> en el caso de estudio 1 del ejemplo 2 con violación de la redundancia: a) antes y b) después de la calibración adaptativa del *offset*.

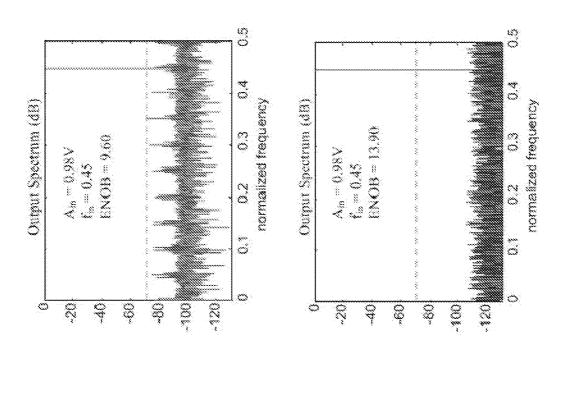

- Fig. 15 Código de salida *X* del convertidor A/D completo con detalles del espectro resultante en el caso de estudio 1 del ejemplo 2 con violación de la redundancia: a) antes y b) después de la calibración adaptativa del *offset* en las dos primeras etapas.

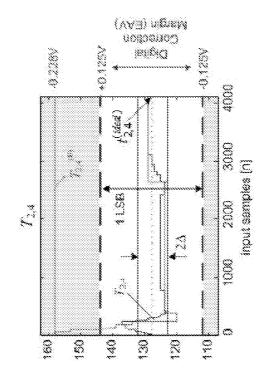

- Fig. 16 Evolución transitoria de las medidas adaptativas de calibración para uno de los comparadores de las etapas en el caso de estudio 1 del ejemplo 2 con violación de la redundancia: a) STG<sub>1</sub>, b) STG<sub>2</sub>.

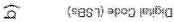

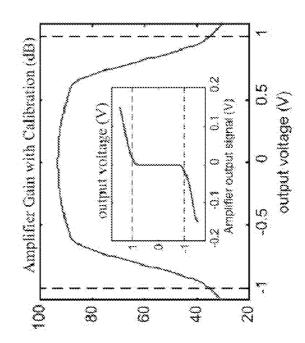

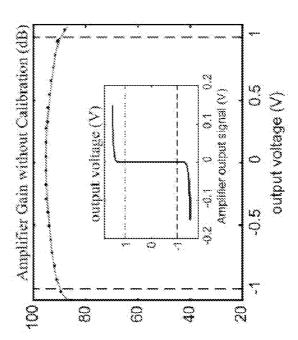

- Fig. 17 Rango dinámico de salida del amplificador del MDAC exigido para un número efectivo de bits (ENOB) de 13.9 bits en el caso de estudio 2 del ejemplo 2: a) sin calibración del *offset*, b) con calibración del *offset* (amplificador no-lineal con reducción del rango de salida).

- Fig. 18. Función de transferencia de la primera etapa bajo calibración en el caso de estudio 2 del ejemplo 2 (sin violación de la redundancia) con detalle del espectro final de salida: a) antes y b) después de la calibración adaptativa del *offset*.

## Realización preferente de la invención

Se muestran a continuación unos ejemplos de realizaciones preferentes de la invención donde se hace referencia a las figuras adjuntas. En primer lugar describiremos brevemente los componentes básicos de la calibración del *offset* en los comparadores de un ADC de tipo *flash* (ADCUC). Posteriormente, se describirá con mayor detalle la realización de la invención en el caso particular de que el convertidor, o convertidores, tipo *flash* bajo calibración forme parte de un ADC Pipeline de mayor resolución. La implementación de la lógica de estimación y calibración de este segundo caso, son directamente extrapolables al primer caso.

#### Ejemplo 1

15

- 50 Medida y calibración de un ADC de tipo Flash

- La Fig. 8 muestra un diagrama simplificado de la realización preferente para la calibración del *offset* en comparadores en un ADC de tipo *flash*. El sistema está formado por:

- Una unidad digital de control (UDC) para la generación de los relojes y señales de control del sistema de forma sincronizada a partir del reloj maestro clk.

- Un Sample&Hold (SH) que realiza un muestreo de la señal analógica de entrada, x = x[n], garantizando una operación sincronizada de los bloques analógicos. Una alternativa válida sin SH a esta solución preferente, es el empleo de un PLL dentro de la UDC.

- El ADC de tipo *flash* bajo calibración (ADCUC) con salida (c) cuyos errores de *offset* en los comparadores se desea compensar. El control efectivo de la transiciones  $t_i$  se realiza mediante el bus de calibración  $K = \{K_i\}$ .

- Un ADC adicional (ADC<sub>test</sub>) que permite obtener una representación digital (X) de la señal analógica (x) con mayor precisión que el código de salida (c) del ADCUC. Como ya hemos comentado, este convertidor puede operar a una frecuencia inferior a la del ADCUC, permitiendo relajar las especificaciones de potencia y área del mismo. Alternativamente, el reloj ADC<sub>test</sub> se puede generar considerando en la UDC un generador de número aleatorios (RNG).

En cualquier caso, el ciclo de operación del  $ADC_{test}$  determina en una realización óptima el ciclo de operación n en la unidad lógica de calibración (ULC), cuyos bloques constitutivos se describen a continuación.

- Un bloque digital (básicamente, formado por dos registros) que permiten mantener el alineamiento temporal entre las salidas del ADCUC y el ADC<sub>test</sub>. Para no introducir variables intermedias en la descripción, asumimos de forma implícita que las señales *X* y *c* se encuentran sincronizadas.

- Una bloque digital adaptativo (PDM) que realiza el procedimiento de medida de las transiciones actuales  $T_i$  del ADCUC. En una realización óptima este bloque genera una señal ENABLE que habilita la lógica de calibración (PGCC).

- Un bloque digital adaptativo (PGCC) para la generación de los códigos de calibración. Como se ha comentado anteriormente, dicho bloque se habilita en una implementación óptima únicamente cuando la señal ENABLE permite la operación.

Para más detalles sobre la realización práctica de la lógica de estimación y calibración, véanse los ejemplos prácticos de la siguiente sección.

#### Ejemplo 2

15

25

Medida y calibración de sub-ADCs en un ADC de tipo Pipeline

La Fig. 9 muestra un diagrama simplificado de un ADC de tipo Pipeline constituido por un Sample&Hold (SH) de entrada seguido por k etapas desde la más significativa (MS) a la menos significativa (LS). El número total de comparadores en cada etapa puede variar entre 2<sup>r</sup>-2 y 2<sup>r</sup>-1 dependiendo de la implementación considerada, con y sin eliminación de unos de los comparadores (véase la publicación, S. Lewis, H. Fetterman, G. Gross Jr., R. Ramachandran y T. R. Viswanathan, "A 10-b 20-Msample/s Analog-to-Digital Converter", IEEE J. of Solid-State Circuits, vol. 27, no. 3, pp. 351-358, Mar. 1992), gracias a la redundancia unidad. En adelante, distinguiremos estas dos situaciones considerando la notación de resolución fraccionaria, así para r = 2, distinguiremos entre etapas con resolución 2 y 1.5 bits, respectivamente. Cada etapa (STG) realiza una cuantización grosera de su entrada analógica x, mediante un convertidor A/D de tipo *flash*, identificado como sub-ADC. Esta salida digital, denotada por el subcódigo c se encuentra generalmente codificada en binario gracias a un codificador termométrico-binario (TBC). Usando la información de los comparadores se genera (excepto en la última etapa) el residuo de salida y para ser procesado por las etapas menos significativas. Esta función la realiza un convertidor D/A multiplicativo (MDAC), que agrupa las operaciones de conversión digital-analógica del subcódigo c, resta con la entrada y amplificación por una ganancia especifica G. En lo que sigue, cuando haya ambigüedad se introducirá un sub-índice adicional para referirnos a una etapa en concreta. Así, la representación digital  $X = X_1$  asociada a la señal de entrada analógica  $x = x_1$  se obtiene mediante una simple función binaria pesada de los diferentes sub-códigos  $\{c_i\}$ , con i = 1, ..., k, una vez se ha realizado el proceso de alineamiento temporal o sincronización de los mismos. De forma análoga, la representación digital  $X_i$  de la entrada analógica  $x_i$  de la i-ésima etapa (STG<sub>i</sub>), combina los sub-códigos de dicha etapa con los las menos significativas  $X_i = X_i$  ( $c_i, ..., c_k$ ).

En términos de *offset* en los comparadores en esta estructura, la técnica de corrección digital (véase la publicación, S. Lewis, H. Fetterman, G. Gross Jr., R. Ramachandran y T. R. Viswanathan, "A 10-b 20-Msample/s Analog-to-Digital Converter", *IEEE J. of Solid-State Circuits*, vol. 27, no. 3, pp. 351-358, Mar. 1992) proporciona una tolerancia al *offset* igual a la mitad del paso de cuantización asociado a cada etapa. Sin embargo, debido a los compromisos existentes entre precisión, consumo y tiempo de desarrollo, la resolución *r* del sub-ADC (y por tanto de la etapa), suele estar limitada por consideraciones prácticas a 2 bits con comparadores de tipo *stand-alone lacth*. Como veremos en los siguientes casos de estudio, esta limitación práctica desaparece en nuestra invención, permitiendo el empleo de este tipo de comparadores en aplicaciones de mayor resolución, incluso en un contexto de bajo voltaje. Téngase en cuenta, como se puede ver en el ejemplo de la Fig. 10 para una etapa de 2 bits, que las posiciones concretas de las transiciones de la etapa coinciden por definición con los umbrales efectivos (o transiciones) de los comparadores del sub-ADC, y por tanto, el *offset* de los mismos afecta drásticamente a la excursión del residuo de salida y de la etapa demando unos amplificadores en el MDAC con mayor rango de salida (*output swing*, OS, de sus siglas en inglés).

A continuación presentamos dos demostradores de la invención para la calibración concurrente del *offset* en comparadores. Para evitar cualquier confusión con el ADC Pipeline de alta resolución, distinguiremos el ADC *flash* bajo calibración dentro de la etapa como sub-ADCUC. En los dos ejemplos se considera, como se muestra en la Fig. 11, un convertidor A/D Pipeline con 14 bits de resolución constituido por 2 etapas de 3 bits seguida por 9 etapas de 1.5 bits. La referencia del convertidor R es igual a 1 V, lo que define un cuanto o bit menos significativo (LSB) para las etapas de 3 y 1.5 bits de 250 mV y 500 mV, respectivamente.

Los errores de linealidad en los sub-ADCs *flash* de cada etapa se han modelado considerando una desviación sistemática en las transiciones de los comparadores respecto a las posiciones nominales. Adicionalmente, se ha tenido en cuenta la incertidumbre variable con el tiempo debido a las fuentes de ruido electrónico en el comparador incorporando un término aleatorio adicional Gausiano y desviación estándar de 5 mV.

En los dos casos, la unidad lógica de calibración (ULC) realiza simultáneamente una compensación del *offset* en los comparadores de las dos etapas más significativas,  $STG_1$  y  $STG_2$  (es decir, tenemos dos ADCs tipo *flash* bajo calibración: sub-ADCUC<sub>1</sub> y sub-ADCUC<sub>2</sub>). Estas etapas por ser las de mayor resolución imponen unos requerimientos más restrictivos en términos de *offset*, al mismo tiempo que por ser las más significativas requieren un mayor rango dinámico de salida (*output swing*) en el diseño de los amplificadores en los MDACs. Ambas etapas emplean una topología común del comparador programable usando una codificación binaria para el código de calibración  $K_i$  con resolución 4 bits y *offset* máximo corregible  $off_{max}$  de 300 mV. Con el fin de emular posibles errores en la implementación, se ha introducido una desviación del 10% en el control efectivo de  $K_i$ .

En el detalle de la realización particular de la Fig. 12, el PDM de cada etapa emplea un paso adaptativo constante  $\mu = 1$  para la actualización de las estimaciones  $T_i$ , mientras que la resolución de la representación digital X se trunca a 8 bits. Aunque es posible considerar una implementación con un paso adaptativo dependiente de la estimación actual, el empleo de un paso constante permite realizar el proceso de actualización mediante una lógica de bajo coste con un único acumulador de 8 bits controlado por el bloque de Comparación Digital, y un banco de registros (TRB) para guardar los estados previos, todo sin merma significativa en la velocidad de convergencia. En cada instante, el subcódigo c de la etapa actúa como dirección f para determinar qué transición se encuentra actualmente bajo calibración y direccionar el banco de registros. Esta alternativa permite aumentar la reusabilidad frente a implementaciones basadas en un acumulador distinto por cada comparador bajo calibración. La Fig. 13 muestra una realización práctica del PGCC. De forma similar al PDM, esta implementación emplea un acumulador de 4 bits para realizar la generación del código de calibración f, considerando un paso adaptativo constante igual a 1. Nótese que igual que en el caso anterior, es siempre posible considerar un acumulador distinto por cada comparador bajo calibración. Obviamente, dadas la similitudes entre el PDM y PGCC, se puede aumentar la reusabilidad del hardware (acumulador, sumador, lógica de dirección, etc.) realizando el proceso de medida y generación de códigos de calibración de forma secuencial para cada etapa (y entre etapas), a costa de una reducción en la velocidad de convergencia.

A continuación pasamos a detallar los dos casos de estudios considerados en el ejemplo 2 como demostradores de la invención. Se mostrarán resultados que permiten resaltar la robustez de la técnica, así como la mejora de la linealidad del ADC, poniendo un especial énfasis en aplicaciones de bajo voltaje.

Caso: 1

25

30

35

40

60

Offset en los Comparadores Incompatibles con la Corrección Digital

En el primer caso de estudio se ha considerado una distribución aleatoria para el *offset* sistemático en los comparadores con una dispersión máxima de ±230 mV sobre el valor medio nulo. Esta gran dispersión justifica la calibración para las dos etapas más significativas de 3 bits, ya que para dichas etapas el *offset* máximo se encuentra por encima del medio LSB (125 mV). Para garantizar un comportamiento monótono de los sub-ADCUCs, se emplea un codificador termométrico-binario (TBC) basado en sumador sin reordenación optimizada de transiciones.

Las Fig. 14a y Fig. 14b muestran las características de entrada-salida del sub-ADCUC<sub>1</sub> y STG<sub>1</sub> antes y después de la calibración, respectivamente. En el estado inicial el residuo de salida y supera la referencia del convertidor, produciéndose como se ilustra en la Fig. 15a un escalón en el código de salida  $X = X_1$  del convertidor completo que limita el número efectivo de bits (ENOB) a 4.4 bits. Tras la compensación del *offset* (Fig. 15b), este comportamiento no-lineal desaparece completamente aumentando la linealidad del ADC hasta un ENOB  $\approx$  14 bits, al mismo tiempo que mantiene el valor máximo del residuo cercano al valor ideal R/2, como se aprecia en la Fig. 14b. Aunque se ha omitido, por razones de espacio, se aprecia las mismas mejoras de prestaciones para la segunda etapa.

Las Fig. 16a y Fig. 16b muestran la evolución transitoria de las medidas adaptativas de calibración, correspondientes a los resultados previos, para uno de los comparadores de los sub-ADCUCs, sub-ADCUC<sub>1</sub> y sub-ADCUC<sub>2</sub>, respectivamente. En ambos casos, distinguidos por el primer subíndice, se muestra la posición real de las transiciones  $T_i$  durante el proceso de calibración, así como la estimación de las mismas,  $T_i$ , proporcionadas por el PDM. Nótese que la invención puede reducir de forma robusta el gran *offset* inicial de los comparadores  $T_i^{(0)}$  sin calibración por debajo de un intervalo de confianza con amplitud  $\Delta$  alrededor de la posición ideal  $T_i^{(ideal)}$ . Como se puede apreciar, el estado estacionario para un estímulo sinusoidal de entrada con amplitud igual a la referencia R se alcanza con únicamente 1000 muestras. La técnica desarrollada garantiza una operación correcta de la etapa incluso si el error inicial de *offset*, se encuentra bastante alejado del límite de medio LSB, en un diseño con redundancia unidad, dentro de la región sombreada. En consecuencia, se puede minimizar la excursión del residuo de salida, y por tanto, aumentar la robustez del amplificador en aplicaciones de bajo voltaje.

Caso: 2

Offset en los Comparadores Compatibles con la Corrección Digital

En el segundo caso de estudio se ha considerado en el diseño de los comparadores un *offset* máximo de ±110 mV inferior al medio LSB de las etapas. Estas desviaciones son totalmente compatibles con la técnica de corrección digital (véase la publicación, S. Lewis, H. Fetterman, G. Gross Jr., R. Ramachandran y T. R. Viswanathan, "A 10-b

20-Msample/s Analog-to-Digital Converter", *IEEE J. of Solid-State Circuits*, vol. 27, no. 3, pp. 351-358, Mar. 1992) usando un diseño estándar del codificador termométrico-binario (TBC). Aunque en esta situación no hay necesidad *a priori* de calibrar los sub-ADCs, las desviaciones debido al *offset* en los comparadores van a tener un impacto bastante notable en la definición del rango dinámico de los amplificadores en los MDACs, sobre todo en las etapas más significativas de 3 bits. De hecho, si consideramos un diseño común en ambas etapas por simplicidad, se debe garantizar una ganancia del amplificador superior a los 93dB con rango de salida próximo a los 2 Vpp, para alcanzar un ENOB entorno a los 13.9 bits (Fig. 17a).

En este contexto la aplicación de nuestra invención permite relajar, como se ilustra en la Fig. 17b los requerimientos del amplificador necesarios para las prestaciones deseadas, reduciendo el rango de salida, respecto al caso anterior sin calibración, a 1.2 Vpp. Se facilita, por tanto, la realización de un diseño optimizado en términos de velocidad y potencia. Las Fig. 18a y Fig. 18b muestran una comparativa del empleo de este amplificador con especificaciones relajadas antes y después de la calibración, respectivamente. En ambos casos se incluye un detalle de la función de transferencia para la primera etapa bajo calibración, así como el espectro final de salida. Nótese que gracias a la compensación del *offset* se pueden reducir las excursiones del residuo, y por tanto limitar el rango de salida efectivo del amplificador en los MDACs, con las consiguientes ventajas para aplicaciones de bajo voltaje.

## REIVINDICACIONES

- 1. Procedimiento adaptativo de calibración digital concurrente del *offset* de los comparadores en convertidores analógico-digitales (ADCs) de tipo *flash*, **caracterizado** por disponer de un control digital en cada uno de los comparadores ( $Comp_i$ ) del ADC bajo calibración (ADCUC), definido por un código digital,  $K_i$ , inicializado a cero, que modifica la posición efectiva de la transición o umbral de comparación  $t_i$  asociado a dicho comparador ( $Comp_i$ ) con un paso mínimo adaptativo  $\delta$ , y que además comprende realizar las siguientes operaciones:

- realizar un control de la posición actual de la transición  $t_i$  del comparador  $Comp_i$  mediante la siguiente ecuación,  $t_i = t_i^{(0)}$   $t_{cor}(K_i)$ , donde  $t_i^{(0)}$  es la posición inicial de la transición de dicho comparador y  $t_{cor}(K_i)$  es una función monótona creciente de  $K_i$ ;

- seleccionar para su actualización el código de calibración  $K_j$  asociado al comparador  $Comp_j$  con transición  $t_j$  definido por un código de salida c del ADCUC, es decir j = c;

- obtener una representación digital (T<sub>j</sub>) de la posición actual de la transición t<sub>j</sub> correspondiente al código de calibración (K<sub>j</sub>) a actualizar;

- comparar el valor actual real de la transición  $T_j$  con un valor ideal conocido de la transición de un ADC ideal  $(T_j^{(déal)})$  más un valor  $\Delta$  correspondiente a una representación digital del mínimo paso adaptativo  $\delta$  del comparador a calibrar:

- si  $T_j > T_j^{\text{(ideal)}} + \Delta$ , aumentar  $K_j$ ;

10

15

20

25

40

45

- si  $T_i < T_i^{\text{(ideal)}}$   $\Delta$ , disminuir  $K_i$ ; y

- aplicar el código de calibración actualizado  $(K_i)$  al comparador asociado.

- 2. Procedimiento de acuerdo con la reivindicación 1, donde el aumento y disminución del código de calibración  $K_j$  se llevan a cabo según pasos constantes.

- 3. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde la operación de obtener una representación digital  $(T_j)$  de las transiciones actuales  $t_j$  de los comparadores en el ADCUC se realiza mediante las siguientes operaciones:

- asignar el valor de las transiciones digitales ideales  $(T_i^{(ideal)})$  a los valores iniciales de las transiciones digitales reales  $(T_i)$ ;

- obtener un código digital de salida (c) del ADC bajo calibración (ADCUC) que es una representación digital de una entrada analógica (x) del mismo;

- de forma sincronizada, obtener una estimación digital (X) de la entrada analógica (x) más precisa que la representación digital (c) de la operación anterior; y

- comparar la estimación digital (X) con las estimaciones actuales de las transiciones digitales reales  $(T_j, T_{j+1})$  donde el índice j viene definido por la representación digital (c) obtenida y:

- $\operatorname{si} X > T_{i+1}$ , aumentar  $T_{i+1}$ ;

- $\operatorname{si} X < T_{i}$ , disminuir  $T_{i}$ .

- 4. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde el aumento de  $T_{j+1}$  y la disminución de  $T_i$  de la estimación de las transiciones se llevan a cabo según pasos constantes.

- 5. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, que comprende la realizar un cambio de variable según la ecuación,  ${\rm INL_j} = T_{\rm j}$   $T_{\rm j}^{\rm (ideal)}$  u otro similar, de modo que las operaciones se realizan directamente sobre la nueva variable obtenida.

- 6. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, que comprende realizar un cambio de variable en el código de calibración  $K_j$  consecuente con el comparador programable que mantenga la realimentación negativa.

- 7. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde la estimación digital (*X*) se obtiene a partir de un segundo convertidor analógico-digital ADC<sub>test</sub> conectado en paralelo al ADCUC.

- 8. Procedimiento de acuerdo con la reivindicación 7, donde el ciclo de conversión del ADC<sub>test</sub> es controlado mediante un generador de número pseudoaleatorio.

- 9. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde el ADCUC es un sub-ADC de una de las etapas (STG<sub>i</sub>) de un ADC de tipo Pipeline, donde:

- la representación digital (c) de la entrada analógica (x) de la etapa (STG<sub>i</sub>) viene dada por un sub-código digital de salida del sub-ADC; y

- la estimación digital (X) correspondiente a la entrada analógica (x) del *i*-ésimo sub-ADC bajo calibración (ADCUC en la etapa STG<sub>i</sub>) se obtiene mediante una operación aritmética lógica (con o sin truncación) del sub-código de salida de dicha etapa (c) y los sub-códigos de salida las etapas siguientes.

- 10. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde cada uno de los comparadores programables  $Comp_i$  comprende al menos un banco de transistores controlados por la señal  $K_i$  destinado a modificar la impedancia de al menos uno de los nudos internos de la arquitectura del comparador programable  $Comp_i$ .

- 11. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde cada uno de los comparadores programables  $Comp_i$  comprende adicionalmente al menos un banco de transistores controlados por la señal  $K_i$  conectado en paralelo a unos dispositivos de entrada de señales analógicas del  $Comp_i$ .

- 12. Procedimiento de acuerdo con cualquiera de las reivindicaciones anteriores, donde el ADCUC de tipo *flash* comprende un codificador termométrico-binario (TBC) sumador para la generación del código de salida *c* del ADCUC que determina un comportamiento monótono del ADCUC.

- 13. Procedimiento de acuerdo con cualquiera de las reivindicaciones 1-11, donde el ADCUC de tipo *flash* hace uso de un codificador termométrico-binario optimizado (O-TBC) que comprende;

- un codificador termométrico-binario TBC estándar precedido por,

- un bloque de decisión que capta los bits de salida  $bt_i$  y  $bt_{i+1}$  de dos comparadores consecutivos,  $Comp_i$  y  $Comp_{i+1}$ , respectivamente, para la generación del código de salida (c) que comprende la siguientes operaciones:conmutar entre sí las estimaciones de transiciones  $(T_i, T_{i+1})$  y códigos decalibración  $(K_i, K_{i+1})$  asociados a dichos comparadores; si:

- bt<sub>i</sub> toma el valor lógico "1", y bt<sub>i+1</sub> es igual "0",

10

25

35

40

45

50

55

- no realizar ninguna conmutación en cualquier otra situación.

- 14. Procedimiento de acuerdo con cualquiera de las reivindicaciones 1-11, donde el ADCUC de tipo flash usa un codificador termométrico-binario optimizado para la generación del código de salida c con reordenación de transiciones de comparadores  $t_j$  y códigos de calibración  $K_j$ , que comprende una memoria

- 15. Unidad lógica (ULC) para la calibración concurrente del *offset* de los comparadores en un convertidor analógico-digital bajo calibración (ADCUC) según el procedimiento de la reivindicación 1, **caracterizado** porque comprende:

- un dispositivo (PDM) de obtención en tiempo real de las estimaciones digitales  $T_i$  de las transiciones  $t_i$  de los comparadores;

- un banco de registros (RB), que almacena el valor actual de los códigos de calibración,  $K = \{K_i\}$ , del ADCUC, e inicializa dichos valores a cero;

- un bloque de comparación digital (CB), que compara el valor actual real de la transición  $T_j$ , donde el índice j viene definido por un código digital (c) de salida del ADCUC, con el valor ideal de la transición ( $T_j^{\text{(ideal)}}$ ) correspondiente más un valor  $\Delta$  correspondiente la representación digital del mínimo paso adaptativo  $\delta$  del comparador a calibrar, y genera una señal de de control (Sgn); y

- un bloque sumador/restador, controlado por (Sgn), que aumenta el código de calibración ( $K_j$ ) cuando  $T_j > T_j + \Delta$ , y disminuye el código de calibración ( $K_j$ ) cuando  $T_j < T_j \Delta$ .

- 16. Unidad lógica de calibración (ULC) de acuerdo con la reivindicación 15, donde la variación de  $K_j$  se lleva a cabo mediante pasos constantes.

- 17. Unidad lógica de calibración (ULC) de acuerdo con cualquiera de las reivindicaciones 15-16, donde la habilitación del bloque de comparación (CB) y/o el bloque sumador/restador proviene de una señal ENABLE (EN) dependiente de la actualización del valor de la estimación de la transición  $T_{\rm j}$ .

- 18. Unidad lógica de calibración (ULC) de acuerdo con cualquiera de las reivindicaciones 15-17, donde el dispositivo (PDM) para la estimación digital de transiciones ( $T_i$ ) del ADCUC a partir de una salida digital (c) del ADCUC y de una estimación digital (x) de su entrada analógica (x) más precisa que dicha representación digital (c), a su vez comprende:

- un banco de registros (TRB), que almacena el valor actual del conjunto de estimaciones de las transiciones digitales ( $T_i$ ) del ADCUC, e inicializa dichos valores al código asociado a las transiciones del ADC ideal  $T_i^{(ideal)}$ ;

- un bloque de comparación digital (CB), que compara la estimación digital (X) con las estimaciones de las transiciones (T<sub>j</sub>, T<sub>j+1</sub> (ideal)), donde el índice j viene definido por el código digital (c), y genera un señal de habilitación (EN) y control (Sgn);

- un bloque sumador/restador habilitado por la señal (EN) y controlado por (Sgn), que aumenta la estimación de la transición digital  $(T_{j+1})$  cuando  $X > T_{j+1}$ , y disminuye la estimación de la transición digital  $(T_j)$  cuando  $X < T_j$ .

- 19. Unidad lógica de calibración (ULC) de acuerdo cualquiera la reivindicación-18, donde el aumento de  $T_{j+1}$  y la disminución de  $T_i$  se llevan a cabo según pasos constantes.

- 20. Unidad lógica de calibración (ULC) de acuerdo con cualquiera de las reivindicaciones 16-19, donde los elementos a, b y c del dispositivo de estimación de transiciones (PDM) están adaptados para funcionar directamente con una estimación digital de la no-linealidad integral (INL<sub>j</sub>) según un cambio de variable dado por la ecuación INL<sub>i</sub> =  $T_i$   $T_i$  (ideal).

- 21. Unidad lógica de calibración (ULC) de acuerdo con cualquiera de las reivindicaciones 15-20, donde los elementos a, b, c y d están adaptados para funcionar con un código de calibración  $K'_j$  según un cambio de variable dado por la ecuación,  $K'_j = -K_j$ .

FIG 1

FIG 2

FIG 3

FIG 4

FIG 5

FIG 6

FIG 7

FIG 8

FIG 9

FIG 10

FIG 11

FIG 12

FIG 13

**FIG 14**

FIG 15

FIG 16

$\widehat{\Omega}$

B

FIG 17

**FIG 18**

(2) N.º solicitud: 200930175

Pecha de presentación de la solicitud: 14.05.2009

3 Fecha de prioridad:

# INFORME SOBRE EL ESTADO DE LA TECNICA

| ⑤ Int. Cl. : | <b>H03M1/10</b> (2006.01) |

|--------------|---------------------------|

|              |                           |

# **DOCUMENTOS RELEVANTES**

09.01.2012

| ategoría                     | 69                                                                                                                                                                                                                                    | Documentos citados                                                                                                                                                                                                                    | Reivindicacione<br>afectadas |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Α                            | US 6567022 B1 (REUVENI et al.) 2 todo el documento.                                                                                                                                                                                   | 20.05.2003,                                                                                                                                                                                                                           | 1-21                         |

| Α                            | CA 2092666 A1 (GU ZHIQIANG et todo el documento.                                                                                                                                                                                      | al.) 28.10.1994,                                                                                                                                                                                                                      | 1-21                         |

| A                            | analog-to-digital converters". System IEEE International Workshop on Ba                                                                                                                                                               | roperty module for auto-calibration of time-interleaved pipelined em-on-Chip for Real-Time Applications, 2004.Proceedings. 4th anff, AB, Canada 19-21 Julio 2004, 20040719; NJ, USA, IEEE. Páginas: 111-114. XP010714011 7695-2182-7. | 1-21                         |

| X: de<br>Y: de<br>M<br>A: re | egoría de los documentos citados<br>e particular relevancia<br>e particular relevancia combinado con ot<br>nisma categoría<br>efleja el estado de la técnica<br>presente informe ha sido realizado<br>para todas las reivindicaciones | de la solicitud<br>E: documento anterior, pero publicado después d<br>de presentación de la solicitud                                                                                                                                 |                              |

|                              | F                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                       | Página                       |

J. Botella Maldonado

1/4

# INFORME DEL ESTADO DE LA TÉCNICA Nº de solicitud: 200930175 Documentación mínima buscada (sistema de clasificación seguido de los símbolos de clasificación) НозМ Bases de datos electrónicas consultadas durante la búsqueda (nombre de la base de datos y, si es posible, términos de búsqueda utilizados) INVENES, EPODOC, WPI, NPL, XPESP, XPAIP, XPI3E, INSPEC.

Nº de solicitud: 200930175

Fecha de Realización de la Opinión Escrita: 09.01.2012

Declaración

Novedad (Art. 6.1 LP 11/1986) Reivindicaciones 1-21 SI Reivindicaciones

NO

Actividad inventiva (Art. 8.1 LP11/1986) Reivindicaciones 1-21 SI

Reivindicaciones NO

Se considera que la solicitud cumple con el requisito de aplicación industrial. Este requisito fue evaluado durante la fase de examen formal y técnico de la solicitud (Artículo 31.2 Ley 11/1986).

## Base de la Opinión.-

La presente opinión se ha realizado sobre la base de la solicitud de patente tal y como se publica.

Nº de solicitud: 200930175

#### 1. Documentos considerados.-

A continuación se relacionan los documentos pertenecientes al estado de la técnica tomados en consideración para la realización de esta opinión.

| Documento | Número Publicación o Identificación                                                                                                                                                                                                                                                                                                                                                                    | Fecha Publicación |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| D01       | US 6567022 B1 (REUVENI et al.)                                                                                                                                                                                                                                                                                                                                                                         | 20.05.2003        |

| D02       | CA 2092666 A1 (GU ZHIQIANG et al.)                                                                                                                                                                                                                                                                                                                                                                     | 28.10.1994        |

| D03       | MORIN D et al. "An intellectual property module for auto-calibration of time-interleaved pipelined analog-to-digital converters". System-on-Chip for Real-Time Applications, 2004.Proceedings. 4th IEEE International Workshop on Banff, AB, Canada 19-21 Julio 2004, 20040719; 20040719-20040721 Piscataway, NJ, USA, IEEE. Páginas: 111-114. XP010714011 ISBN 978-0-7695-2182-4; ISBN 0-7695-2182-7. |                   |

2. Declaración motivada según los artículos 29.6 y 29.7 del Reglamento de ejecución de la Ley 11/1986, de 20 de marzo, de Patentes sobre la novedad y la actividad inventiva; citas y explicaciones en apoyo de esta declaración

El documento más próximo del estado de la técnica es el D01 que presenta un método y un dispositivo para calibrar dos ADC aplicando a ambos una señal de prueba y un primer valor de corrección. Las salidas corregidas se comparan y se ajustan la una en función de la otra, mediante una nueva corrección.

Con el conocimiento de este documento, la invención no se puede considerar obvia para un experto en la materia. Tampoco hay sugerencias que dirijan al experto en la materia hacia la invención definida por las reivindicaciones de la 1ª a la 21ª. Por lo tanto, el objeto de estas reivindicaciones cumple los requisitos de novedad, actividad inventiva.