# A Signed Spatial Contrast Event Spike Retina Chip

J. A. Leñero-Bardallo, T. Serrano-Gotarredona, and B. Linares-Barranco Instituto de Microelectrónica de Sevilla (IMSE-CNM-CSIC). Américo Vespucio s/n, 41092 Sevilla, Spain.

E-mail: bernabe@imse-cnm.csic.es

Abstract- Reported AER (Address Event Representation) contrast retinae perform a contrast computation based on the ratio between a pixel's local light intensity and a spatially weighted average of its neighbourhood. This results in compact circuits, but with the penalty of all pixels generating output signals even if they sense no contrast. In this paper we present a spatial contrast retina with bipolar output: contrast is computed as the relative normalized difference (not the ratio) between a pixel's local light and its weighted spatial average, normalized to average light. As a result, contrast includes a sign, is ambient light independent, and the output will be zero if there is no contrast. Furthermore, an adjustable thresholding mechanism has been included, such that pixels remain silent until they sense an absolute contrast above the adjustable threshold. The pixel contrast computation circuit is based on Boahen's Biharmonic operator contrast circuit, which has been improved to include mismatch calibration and adaptive current based biasing. As a result, the contrast computation circuit shows much less mismatch, is almost insensitive to ambient light illumination, and biasing is much less critical than in the original voltage biasing scheme. The retina also includes an optional TFS (Time-to-First-Spike) integration mode. A full AER retina version has been fabricated and tested. In the present paper we provide preliminary experimental results.

## I. Introduction

AER (Address Event Representation) is a spike based representation hardware technique for communicating spikes between layers of neurons in different chips. AER was first proposed in 1991 in one of the Caltech research labs [1], and has been used since then by a wide community of neuromorphic hardware engineers. Computing spatial contrast on the focal plane reduces data flow significantly, although relevant information for shape and object recognition is conserved. In a conventional luminance sensor (a commercial camera) all pixels are sampled with a fixed period and its light intensity (integrated over this period) is communicated out of the sensor to the next stage. In an AER sensor pixels are not sampled. On the contrary, the pixels are the ones who initiate an asynchronous communication cycle, called "event", when a given condition is satisfied. For example, a spatial contrast retina pixel would send an event whenever the computed local contrast exceeds a given threshold. As a consequence, AER systems can be made frame-less: there is no sequence of still frames as in conventional video. Rather, the information flows in a continuous manner between AER modules as events are generated at the pixel level, either in the sensors or at later processing stages.

Previously reported spatial contrast retinae [2]-[3] compute contrast as the ratio between a pixel's locally sensed light intensity  $I_{ph}(x,y)$  and a spatially weighted average of its surrounding neighborhood  $I_{avg}(x,y)$  computed with some kind of diffusive network

$$I_{cont}(x,y) = I_{ref} \frac{I_{ph}(x,y)}{I_{avg}(x,y)}$$

(1)

Since this is always positive, let us call it "unipolar" contrast computation. This yielded circuits where no subtraction operation was required. This was crucial to maintain mismatch (and precision) at reasonable levels. Note that for computing  $I_{avg}$  and  $I_{cont}$  circuits have to handle directly photo currents, which can be as low as pico-amperes or less. Performing a simple mirroring

operation introduces mismatches with errors in the order of 100% [4]. This can be overcome by increasing transistor area, but then leakage currents may become comparable to the available photo currents. Consequently, while handling photo currents, it is desirable to keep complexity at a minimum. Therefore, from a circuits point of view, the way of computing contrast as in eq. (1) was very convenient. However, this presents an important drawback: when there is no contrast ( $I_{avg} = I_{ph}$ ) then  $I_{cont} \neq 0$ . In an AER circuit this means that a pixel sensing no contrast will be sending out information (events) and consuming communication bandwidth on the AER channels. This is contrary to the advantages of AER (where it is expected that only information relevant events will be transmitted) and contrary to the advantages of computing contrast at the focal plane (so that only contrast relevant pixels need to send information). In prior work [3], although spatial contrast was computed by eq. (1) in the retina, a post-processing with AER (convolution) modules was added to effectively compute the contrast as the signed (or bipolar) quantity

$$I_{cont}(x,y) = I_{ref}\left(\frac{I_{ph}(x,y)}{I_{avg}(x,y)} - 1\right)$$

(2)

This reduced significantly the data flow from 400keps (kilo events per second) to 10keps, but also at the expense of reducing the speed response of a pixel by a factor of about 10.

In the present paper we present a new spatial contrast retina design, where the contrast computation follows directly eq. (2) instead of eq. (1). Contrast computation is ambient light independent. The design is based on the original contrast computation circuit by Boahen [2], which has been improved to overcome its inherent limitations on mismatch, ambient light dependence, and critical controllability. The retina also includes an optional Time-to-First-Spike (TFS) operating mode [5], which will be described elsewhere [6]. Section II summarizes a prior AER mismatch-calibrated contrast retina pixel that followed eq. (1), Section III summarizes briefly Boahen's spatial contrast computation circuit, Section IV summarizes a more compact in-pixel calibration circuit than the one used in [3] and which has been used in the present design, and Section V introduces the new pixel design. Finally, Section VI provides experimental results.

# II. Prior AER Mismatch-Calibrated Unipolar Spatial Contrast AER Retina

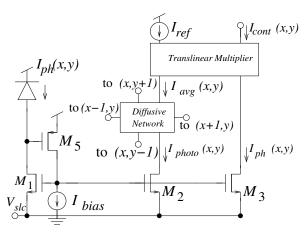

Fig. 1 shows the basic schematic of the contrast computation circuit used in a previous unipolar spatial contrast retina [3]. A p+/nwell photo diode sensed current  $I_{ph}(x,y)$  which is replicated twice using a sub-pico-ampere current mirror [7]. The first replica is used in a cascoded diffusive network [8], which implements the discrete approximation of the 2D Laplacian equation

$$I_{ph}(x,y) = \left(1 - \lambda_x \frac{\partial^2}{\partial x^2} - \lambda_y \frac{\partial^2}{\partial y^2}\right) I_{avg}(x,y)$$

(3)

This equation provides a good spatial average of  $I_{ph}$  over neighboring pixels, such that closer pixels contribute more to this

Fig. 1: Block diagram of pixel in prior unipolar contrast retina.

average than distant pixels. The second replica of the photo current is fed together with  $I_{avg}(x,y)$  to a translinear circuit computing the ratio between both, scaled by reference current  $I_{ref}$ . The resulting current  $I_{cont}(x, y)$  is thus proportional to a unipolar contrast (as in eq. (1)) and is fed to an integrate-and-fire neuron generating periodic spikes with a frequency proportional to  $I_{cont}(x, y)$  . Scaling current  $I_{ref}$  is made locally trimmable for each pixel in order to compensate for all mismatch contributions from the photo diode, current mirror, diffusive network, translinear circuit, and integrate-and-fire neuron. As a result, inter-pixel mismatch contrast computation could be reduced from about  $\sigma \approx 60\%$  to  $\sigma \approx 6\%$  using 5-bit pixel registers to control  $I_{ref}(x, y)$ . Pixel complexity was kept relatively simple. The main drawback is that pixels with no contrast would generate output events at a constant rate proportional to  $I_{ref}$ . To overcome this, a 4-AER-module system [3] was assembled to compute effectively a bipolar contrast as in eq. (2). As a result, the background DC component in eq. (1) was removed, yielding a computation equivalent to that in eq. (2). However, as a backside effect, the effective firing rate of a pixel at the output channel was reduced by a factor of around 10, thus diminishing its speed response. In the design presented in this paper, this is solved by performing all the bipolar contrast computation at the sensor chip using an improved version of Boahen's original biharmonic contrast computation circuit.

## III. Boahen's Biharmonic Contrast Circuit

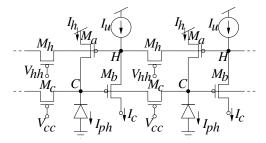

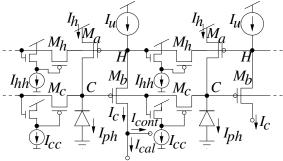

A trivial solution to subtract the DC component of the circuit in Fig. 1 is to subtract another DC current  $I_{ref2}(x,y)$  from  $I_{cont}(x,y)$ . However, this second DC current also needs to be trimmable to compensate for its own mismatch. Note that the available trimming current  $I_{ref}(x,y)$  will not compensate it together with the rest of mismatch sources [3]. However, the same result can be achieved by using Boahen's compact biharmonic spatial contrast computation circuit [2]. Thus, by using a slightly more complex diffuser network, we will not require any more the sub-pico-ampere current mirror nor the translinear circuit. The original circuit, in its all-PMOS version, is shown in Fig. 2. The schematic only shows two neighboring pixels of a 1-D retina version. In practice, the horizontal transistors form a 2D mesh. The continuous approximation of this circuit solves approximately the following equations [8]

$$I_h(x,y) = I_{ph}(x,y) + a\nabla^2 I_c(x,y)$$

$$I_c(x,y) = I_u - b\nabla^2 I_h(x,y)$$

(4)

Fig. 2: Boahen original contrast computation circuit

Fig. 3: Digitally-controlled-length MOS used for calibration

Solving for  $I_h$  results in the biharmonic equation used in computer vision to find an optimally smooth interpolating function of the stimulus  $I_{ph}$ . Consequently, the output  $I_c(x,y)$  is the second order spatial derivative of the interpolation  $I_h$  according to the bottom eq. (4). Since the interpolation is a spatially integrated version of the stimulus,  $I_c$  can be interpreted as a version of a first order derivative of the stimulus, therefore, spatial contrast. The original circuit implementation of this model suffered from a series of drawbacks. First, mismatch was comparable to output signal. Second, output signal would degrade for the same contrast stimulus when changing lighting conditions. Third, bias voltages  $V_{cc}$  and  $V_{hh}$  in Fig. 2 had very narrow and critical tuning range. All three drawbacks have been improved with the present implementation.

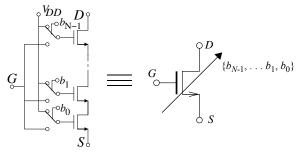

# IV. Compact Calibration Circuit

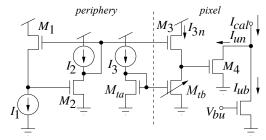

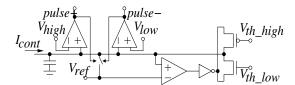

We reduce mismatch by introducing calibration. One dominant source of mismatch is the DC component in the bottom of eq. (4). Since this current is set constant, independent of lighting conditions, we can directly subtract it with a trimmable current source. The output current will thus be directly the bipolar contrast current we were looking for. To implement the trimmable current source, we follow the recently reported very compact circuit based on series transistors association [10]. Fig. 3 shows the basic principle behind this circuit. Each switched MOS operates as a segment of an effective longer MOS whose length is controlled digitally by switching individual segments from ohmic to saturation, and vice versa. The key consists in making each segment to contribute approximately as a power of  $2^n$  to the total length. As a result, the effective length is digitally controlled as in a digital-to-analog conversion. Fig. 4 shows the circuitry used to subtract the DC component of the contrast current. Transistors to the left of the dashed line are shared by all pixels, while those to the right are replicated for each pixel. Transistors  $M_{1-4}$  form a translinear loop [8], thus  $I_{un} = I_1I_2/I_{3n}$ . Current  $I_{3n}$  is a mirrored version of  $I_3$  by transistors  $M_{ta}$  and  $M_{tb}$ . Transistor  $M_{tb}$  is made of the digitally-controlled-length MOS of Fig. 3. Consequently,  $I_{un}$  is proportional to its length.  $I_{un}$  is added to the base bias current  $I_{ub}$ , thus compensating mismatch originated at  $I_{uh}$  and in the pixel.

Fig. 4: Translinear tuning circuit

# V. The improved spatial bipolar contrast pixel

Fig. 5 shows how the pixel has been modified to include a current biasing scheme for controlling the original voltages  $V_{cc}$ and  $V_{hh}$  in Fig. 2. This way, gate voltages  $V_{cc}$  and  $V_{hh}$  tend to follow voltage excursions at nodes 'C' and 'H'. The first advantage of this is that biasing will adapt to ambient light conditions. For example, if all photodiode currents are scaled up/down by the same factor, the voltage at all nodes 'H' will follow it logarithmically. Also, since  $I_u$  is constant, the voltage at node 'C' will also tend to follow the same shift. Since bias currents  $I_{hh}$  and  $I_{cc}$  are kept constant, the gate voltages of transistors  $M_h$  and  $M_c$  will thus follow also this same global voltage shift, adapting to the global light change. Another beneficial effect of this current biasing scheme is that it attenuates mismatch. After doing careful mismatch analysis and identifying the main sources of mismatch for this circuit, one can find out that transistor  $M_a$  and current  $I_u$  are the dominant sources of mismatch. The effect of  $I_u$  will be compensated by calibration, and the effect of  $M_a$  will be attenuated by the current biasing scheme. Note that mismatch in all  $M_a$  transistors will introduce random voltage variations at nodes 'H' and 'C'. These variations will be transformed into random lateral currents through transistors  $M_h$  and  $M_c$ . The random currents through  $M_h$  will be collected by output current  $I_c$  and can be compensated by calibration. However, random currents through  $M_c$  transistors operate as if they were generated by the photodiodes. Thanks to the current biasing scheme, an increase in 'C' will increase the gate voltage of the new bottom NMOS transistor, increasing its source voltage, thus increasing the gate voltage of  $M_c$ , which will reduce the lateral random current. A similar effect will be happening for transistors  $M_h$ . Finally, the third advantage is a more robust means for biasing the lateral transistors. In the original scheme, voltages  $V_{cc}$  and  $V_{hh}$ suffered from a very narrow and critical tuning range (about 100mV or less). Now, bias currents  $I_{cc}$  and  $I_{hh}$  can be tuned over several decades, while still perceiving their effect. Another modification introduced is thresholding. This is done at the integrate-and-fire neuron, as is shown in Fig. 6. Since contrast current  $I_{cont} = I_c - I_{cal}$  can now be positive or negative, we

Fig. 5: Boahen improved circuit with current biasing

Fig. 6: Integrate and fire bipolar neuron with thresholding

#### Table 1

| Process               | Standard CMOS 0.35µm 4M 2P     |

|-----------------------|--------------------------------|

| Die size              | 2.5 x 2.6 mm <sup>2</sup>      |

| Array size            | 32 x 32                        |

| Pixel size            | 80 x 80 μm <sup>2</sup>        |

| Pixel complexity      | 131 transistors + 2 capacitors |

| Fill factor           | 1.6%                           |

| Power Consumption     | 0.66-6.6mW (depends on eps)    |

| Max output event rate | 66Meps (shorting Rqst & Ack)   |

| FPN                   | 0.9% over 5 decades of light   |

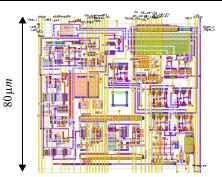

Fig. 7: Layout of 80x80μm<sup>2</sup> bipolar spatial contrast pixel

need two comparators to detect whether the net contrast integration has reached an upper threshold  $V_{high}$  (generating a positive event at pulse+) or a lower one  $V_{low}$  (generating a negative event at pulse-). In either case, the capacitor will be reset to a central voltage  $V_{ref}$ . For introducing thresholding a third comparator detects whether capacitor voltage is above or below  $V_{ref}$  and turns on either a positive or negative threshold current, which  $I_{cont}$  needs to exceed for producing an event. The thresholding transistors in Fig. 6 use large area (2/30) to reduce mismatch impact.

# VI. Experimental Results

A full 32 x 32 pixel AER bipolar spatial contrast retina has been designed and fabricated in a double poly 4-metal 0.35µm CMOS process. Table 1 summarizes retina specifications. Fig. 7 shows the layout of one pixel. Each pixel is a symmetrical speculation of its neighboring pixels. This way noisy digital lines and power supplies are shared among neighbors. Noise sensitive lines are separated from noisy ones. Pixel area is  $80 \times 80 \mu m^2$ . The contrast computation circuitry occupies 25% of the total area, the calibration system 20% of the total, the thresholding system another 20% of the total area and the integrate and fire neuron and the digital communication interface occupy the rest of the pixel area. To reduce mismatch the retina includes in-pixel calibration. The chip is calibrated by illuminating it with uniform white light. Ideally, none of the pixels should spike. However, there is mismatch and some pixels spike with a non-zero frequency. The circles in Fig. 8 show the pixels output frequencies measured before calibration, when all the pixel calibration words  $w_{cal}$  are zero. After this, for all the possible values of the calibration words, the frequencies are measured again for each pixel. Then the

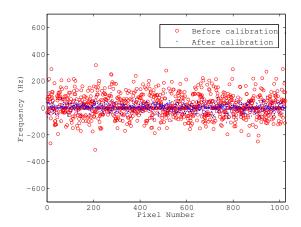

Fig. 8: Pixels output frequencies before and after calibration

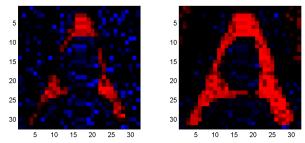

Fig. 9: Snapshots captured with the AER retina. On the left, the image was taken without calibration. On the right, the same image after calibration is shown.

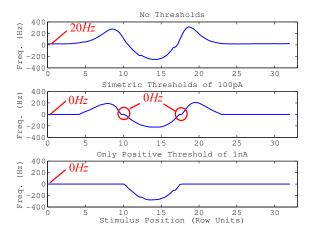

calibration words  $\mathbf{w}_{cal}$  that minimize pixel output frequency are uploaded to their internal calibration register. The average output frequency before calibration was  $f_{avg} = 62Hz$  and after calibration  $f_{avg} = 17Hz$ . Standard deviation was  $\sigma = 83Hz$ before calibration and  $\sigma = 26Hz$  after calibration. Since the full frequency range is  $\pm 4400Hz$ , the relative FPN results in  $\sigma$ =0.3%. The dots in Fig. 8 are the pixels output frequencies after calibration. Changing ambient light over 5 decades degrades FPN to  $\sigma$ =0.9% [6]. We use a set of AER hardware [11] and software [12] tools to experimentally characterize our AER chips. Fig. 9 shows two snapshots of the character 'A' before and after calibration. Without calibration, the total output frequency was  $f_t = 4 \times 10^5 Hz$  and with calibration  $f_t = 3.5 \times 10^5 Hz$ . After the calibration process, the quality of the image is higher and the bandwidth consumption is slightly lower. Negative events are plotted in a red scale and positive events in a blue one. Black color indicates no contrast. In Fig. 10, some advantages of thresholding are indicated. The output frequency of one individual pixel was plotted when a bar of 100% contrast was swept across its visual field. The x-axis represents the position of the center of the bar in row number units. The pixel under test was (13,10). Without thresholding, there was an undesirable residual mismatch after calibration of 20Hz as can be observed in the upper plot of Fig. 10. When symmetric thresholds of 100pA were set, the effect of mismatch was removed (middle plot of Fig. 10). It is also possible to set asymmetric thresholds to inhibit the positive or negative events as is shown in the bottom plot of the figure.

## VII. Conclusions

A new AER bipolar contrast retina has been presented. It uses an improved and calibrated version of Boahen's contrast circuit. Preliminary experimental results are provided. More details will be reported in [6].

Fig. 10: Example of pixel output after sweeping the visual field with a bar of 100% contrast for different values of the positive and negative thresholds.

## VIII. Acknowledgements

This work was supported by EU grant 216777 (NABAB), Spanish grants TEC2006-11730-C03-01 (SAMANTA2) and TEC2009-10639-C04-01 (VULCANO), and Andalucian grant P06TIC01417 (Brain System). JALB was supported by a JAE scholarship.

## IX. References

- M. Sivilotti, Wiring Considerations in Analog VLSI Systems with Application to Field-Programmable Networks, Ph.D. Thesis, California Institute of Technology, Pasadena CA, 1991.

- [2] K. Boahen and A. Andreou, "A contrast-sensitive retina with reciprocal synapses," in J. E. Moody (Ed.), Advances in neural information processing, vol. 4, pp. 764-772, San Mateo CA, 1992. Morgan Kaufman.

- [3] J. Costas-Santos, T. Serrano-Gotarredona, R. Serrano-Gotarredona and B. Linares-Barranco, "A Spatial Contrast Retina with On-chip Calibration for Neuromorphic Spike-Based AER Vision Systems," *IEEE Trans. Circuits and Systems, Part-I: Regular Papers*, vol. 54, No. 7, pp. 1444-1458, July 2007.

- [4] G. Vicente-Sanchez, J. Velarde-Ramirez, T. Serrano-Gotarredona and B. Linares-Barranco, "A Weak-to-Strong Mismatch Model for Analog Circuit Design", Int. Journal of Analog Integrated Circuits and Signal Processing, 59, pp. 325-340, 2009.

- [5] S. Chen, and A. Bermak, "Arbitrated Time-To-First Spike CMOS Image Sensor with On-Chip Histogram Equalization," *IEEE Trans. VLSI Systems*, vol. 15, No. 3, pp. 346-357, March 2007.

- [6] J. A. Leñero-Bardallo et al., "A 5-Decade Dynamic Range Ambient-Light-Independent Calibrated Signed-Spatial-Contrast AER Retina with 0.1ms Latency and Optional Time-toFirst-Spike Mode," IEEE Trans. Circ. Syst., Part I, under review.

- [7] B. Linares-Barranco and T. Serrano-Gotarredona, "On the Design and Characterization of Femtoampere Current-Mode Circuits," *IEEE Journal of Solid-State Circuits*, vol. 38, No. 8, pp. 1353-1363, August 2003.

- [8] A. G. Andreou and K. Boahen, "Translinear Circuits in Subthreshold CMOS," *Analog Integrated Circuits and Signal Processing*, Kluwer, no. 9, pp. 141–166, Apr. 1996.

- [9] R. Serrano-Gotarredona, T. Serrano-Gotarredona, A. Acosta-Jiménez, and B. Linares-Barranco, "A Neuromorphic Cortical Layer Microchip for Spike Based Event Processing Vision Systems," *IEEE Trans. on Circuits and Systems, Part-I*, vol. 53, No. 12, pp. 2548-2566, Dec. 2006.

- [10] J. A. Leñero-Bardallo, T. Serrano-Gotarredona, and B. Linares-Barranco, "A Calibration Technique for Very Low Current and Compact Tunable Neuromorphic Cells. Application to 5-bit 20nA DACs," *IEEE Trans. Circuits and Systems, Part-II: Brief Papers*, vol. 55, No. 6, pp. 522-526, June 2008.

- [11] F. Gomez-Rodriguez, et al., "AER Tools for Communications and Debugging," *IEEE Int. Symp. Circ. & Syst.*, pp. 3253-3256, 2006.

- [12] T. Delbruck. (2007, jAER open source project. Available: http://jaer.wiki.sourceforge.net