# University of Seville Department of Electronics and Electromagnetism Microelectronics Institute of Seville (IMSE-CNM-CSIC)

## Digital Background Self-Calibration Technique for Compensating Transition Offsets in Reference-less Flash ADCs

Thesis submitted by

#### Cristina Aledo González

to get the degree of Doctor by the University of Seville

PhD supervisor:

Eduardo José Peralías Macías

Seville, July 2019

# Universidad de Sevilla Departamento de Electrónica y Electromagnetismo Instituto de Microelectrónica de Sevilla (IMSE-CNM-CSIC)

# Técnica de auto-calibración digital en modo background para compensar offsets de transiciones en un convertidor A/D tipo flash sin referencias

Memoria presentada por:

Cristina Aledo González

para optar al título de Doctor por la Univerdad de Sevilla

Director:

Eduardo José Peralías Macías

Tutor:

Diego Vázquez García de la Vega

Sevilla, Julio de 2019

### **Acknowledgements**

This research work has been developed at the Microelectronics Institute of Seville (IMSE-CNM-CSIC) and University of Seville. It has been funded by Ministry of Economy and Competitiveness, under the Research Staff Training (FPI) program and the following projects: DANTE (Spanish Government project TEC2011-28302, cofinanced by Ministry of Science and Innovation) and n-PATETIC (Spanish Government project TEC2015-68448-R, cofinanced by Ministry of Economy and Competitiveness and the European FEDER program). During 2015, a four-month-stay has been accomplished at the Department of Electrical Engineering at Faculdade de Ciências e Tecnologia (FCT), Universidade Nova de Lisboa (UNL), Portugal.

I would like to thank my supervisor Dr. Eduardo Peralías for sharing with me his knowledge, for being a great instructor and a supportive mentor, and for his patient and dedication along theses thesis work. Also, I would like express my deep gratitude to Dra. Adoración Rueda for giving me the opportunity to work in a great group and for her infinite support and dedication during these years. Their advice and helpful guidance were crucial to carried out this work until the end.

I would like to express my special thanks to Professor João Goes for his advice on my PhD work during the months I spent at FCT. I wanted to thank as well to all my colleagues and friends of IMSE, especially to Joaquín Ceballos, Antonio Ragel, José Miguel Mora, Luis Carranza, Luis Camuñas, Rafaella Fiorelli, Juan Núñez, Manolo Suarez, Manu Jiménez, Iñaki Vázquez, Delia Velasco and Alberto Muñío, for their support and help, both technically and personally.

Finally, I would like to thank to my friends and family for their unconditional love and comprehension. Special thanks to my mother, Mireya, Manu and Enrique, for being a constant source of support throughout these years. This work would not have been possible without them.

#### **Abstract**

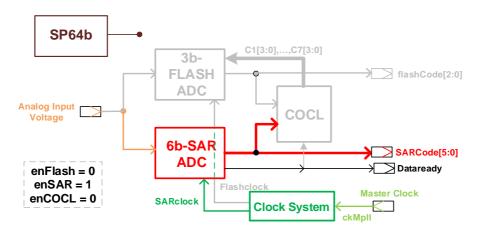

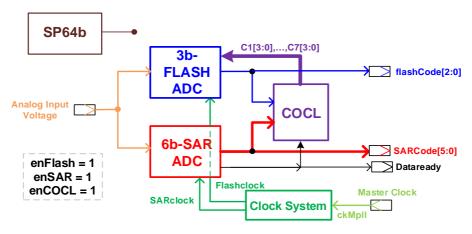

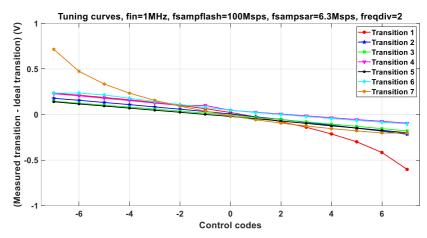

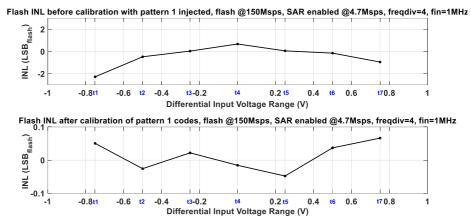

This Dissertation focusses on proving that background calibration using adaptive algorithms are low-cost, stable and effective methods for obtaining high accuracy in flash A/D converters. An integrated reference-less 3-bit flash ADC circuit has been successfully designed and taped out in UMC 180 nm CMOS technology in order to prove the efficiency of our proposed background calibration. References for ADC transitions have been virtually implemented built-in in the comparators dynamic-latch topology by a controlled mismatch added to each comparator input front-end. An external very simple DAC block (calibration bank) allows control the quantity of mismatch added in each comparator front-end and, therefore, compensate the offset of its effective transition with respect to the nominal value. In order to assist to the estimation of the offset of the prototype comparators, an auxiliary A/D converter with higher resolution and lower conversion speed than the flash ADC is used: a 6-bit capacitive-DAC SAR type. Special care in synchronization of analogue sampling instant in both ADCs has been taken into account.

In this thesis, a criterion to identify the optimum parameters of the flash ADC design with adaptive background calibration has been set. With this criterion, the best choice for dynamic latch architecture, calibration bank resolution and flash ADC resolution are selected.

The performance of the calibration algorithm have been tested, providing great programmability to the digital processor that implements the algorithm, allowing to choose the algorithm limits, accuracy and quantization errors in the arithmetic. Further, systematic controlled offset can be forced in the comparators of the flash ADC in order to have a more exhaustive test of calibration.

## Index

| A  | cknowled   | gements                               | '   |

|----|------------|---------------------------------------|-----|

| Α  | bstract    |                                       | iii |

| In | ıdex       |                                       | v   |

| 1  | Introdu    | uction                                | 1   |

|    | 1.1 M      | otivation                             | 1   |

|    | 1.2 Th     | esis proposals                        | 3   |

|    | 1.3 Th     | esis Organization                     | 5   |

| 2. | Analog     | ue-to-Digital Converters Overview     | 7   |

|    | 2.1. ADCs  | Basics                                | 8   |

|    | 2.1.1.     | Static and dynamic specifications     | 9   |

|    | 2.2. Error | s in ADCs                             | 13  |

|    | 2.2.1.     | Sampling-time jitter                  | 13  |

|    | 2.2.2.     | kT/C noise                            | 14  |

|    | 2.2.3.     | Comparator metastability              | 15  |

|    | 2.3. State | e-of-the-Art                          | 16  |

|    | 2.4. Relev | ant ADC architectures for this work   | 19  |

|    | 2.4.1.     | Flash ADC                             | 19  |

|    | 2.4.2.     | Pipeline ADC                          | 21  |

|    | 2.4.3.     | SAR ADC                               | 22  |

| 3. | Offset     | Comparator Calibration in ADCs        | 27  |

|    | 3.1. Calib | ration Overview                       | 28  |

|    | 3.1.1.     | Foreground vs. Background Calibration | 28  |

|    | 3.1.2.     | Analogue vs. Digital Calibration      | 31  |

|    | 3.2. Offse | t Calibration in Comparators          | 33  |

| 3.3. Digito | al Techniques for Offset Calibration in Comparators         | 35         |

|-------------|-------------------------------------------------------------|------------|

| 3.3.1.      | DAC-based calibration                                       | 35         |

| 3.3.2.      | Redundancy                                                  | 38         |

| 3.4. Appli  | ed Solution: Adaptive Digital Background Calibration        | 40         |

| 3.4.1.      | Offset Adaptive Estimation (OAE)                            | 41         |

| 3.4.2.      | Calibration Code Generation (CCG)                           | 43         |

| 3.4.3.      | Input estimation for calibration purpose                    | 44         |

| 3.4.4.      | Possible applications                                       | 46         |

| 4. Design   | of a Comparator and its Calibration Circuit in a Flash ADC  | 49         |

| 4.1. Flash  | ADC considerations                                          | 50         |

| 4.1.1.      | Comparator reference voltage generation                     | 50         |

| 4.1.2.      | Transitions in flash ADCs                                   | 52         |

| 4.1.3.      | Dynamic latched comparator                                  | 54         |

| 4.1.4.      | Sparkles in thermometer codification                        | 56         |

| 4.2. Com    | parator design                                              | 59         |

| 4.3. Dyna   | mic latch design                                            | 60         |

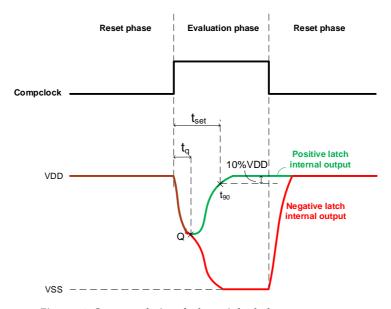

| 4.3.1.      | Dynamic latch operation                                     | 60         |

| 4.3.2.      | Different dynamic latches topologies                        | 61         |

| 4.3.3.      | Comparison study                                            | 65         |

| 4.3.4.      | Search of the maximum resolution for the flash ADC          | 71         |

| 4.4. Statio | offset estimation                                           | 73         |

| 4.5. Calib  | ration bank design                                          | <i>7</i> 5 |

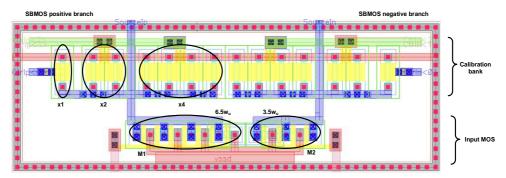

| 4.5.1.      | Selected calibration bank: Switchable bank of MOS resistors | (SBMOS)76  |

| 4.5.2.      | Considered assumptions in the design                        | 76         |

| 4.5.3.      | Bank design for symmetric transition                        | 80         |

| 4.5.4.      | Results for extremal transition                             | 83         |

| 5. Integra  | ited Demonstrator                                           | 86         |

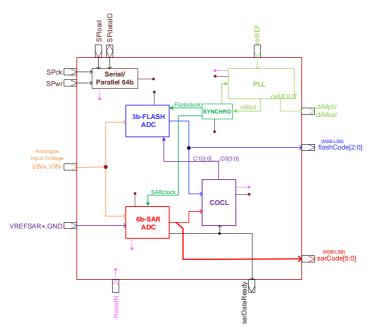

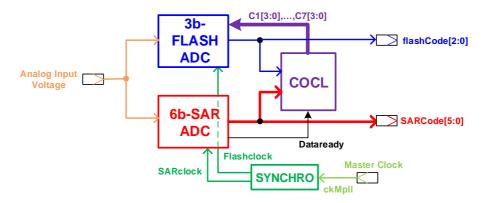

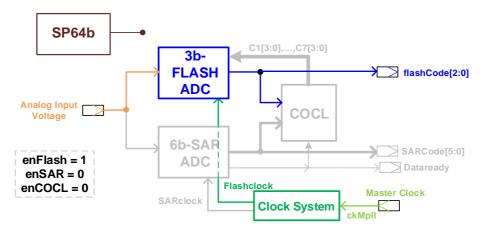

| 5.1. ASIC   | prototype architecture                                      | 87         |

| 5.2. Circu  | it operation                                                | 88         |

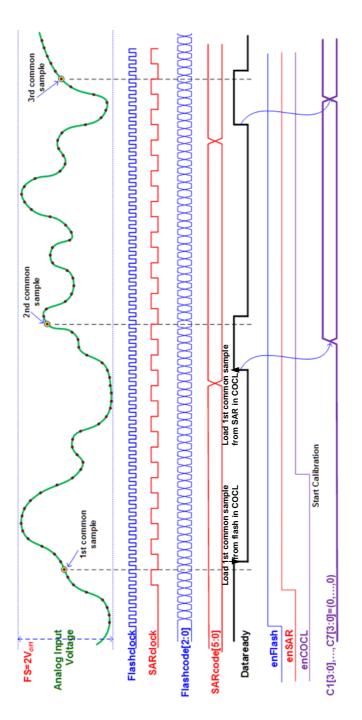

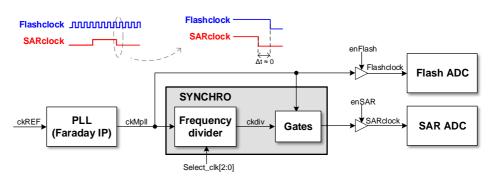

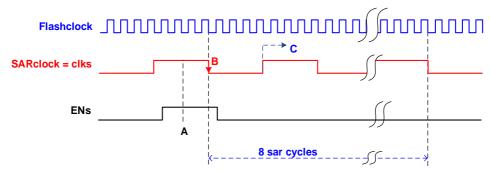

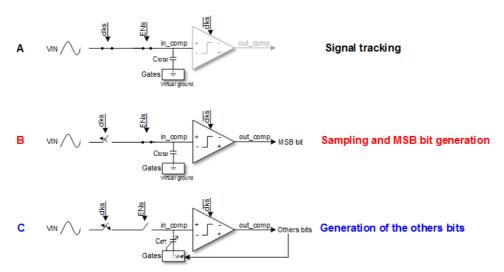

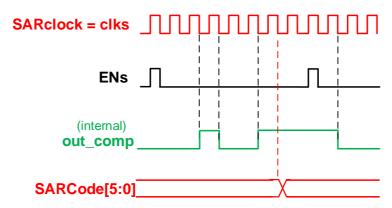

| 5.3. Flash  | and SAR ADCs Synchronisation                                | 91         |

| 5.3.1.      | Clock system                                                | 91         |

| 5.3.2.      | Sampling precision                                          | 92         |

| 5.4. 3-bit  | flash ADC design                                            | 94         |

| Index | V  |

|-------|----|

| HILLA | VI |

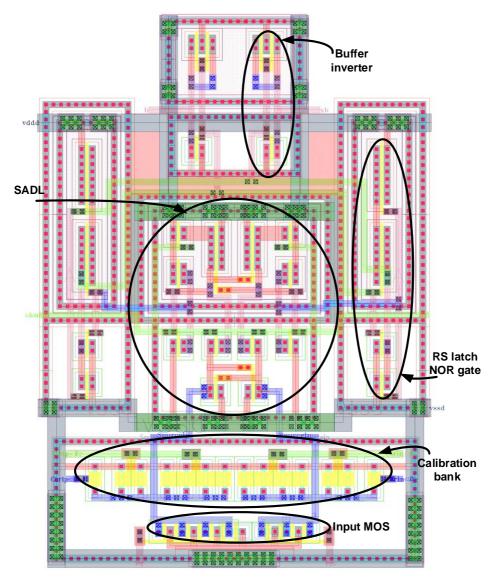

| 5.4.1.         | Comparator design                                           | 97  |

|----------------|-------------------------------------------------------------|-----|

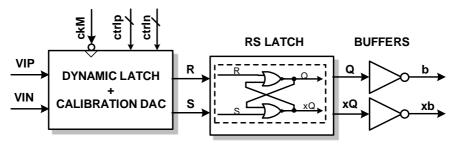

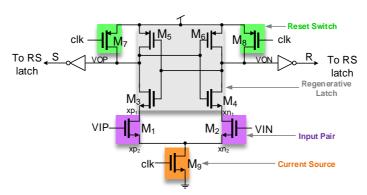

| 5.4.2.         | Dynamic latch design                                        | 98  |

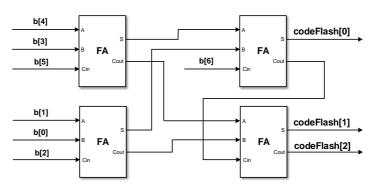

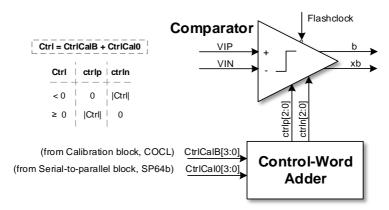

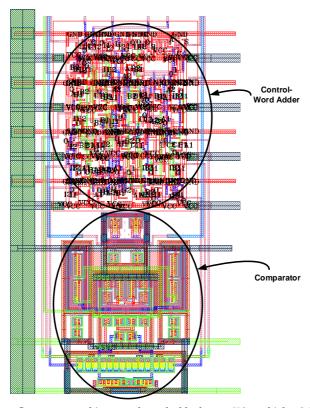

| 5.4.3.         | Control-Word Adder                                          | 101 |

| 5.4.4.         | Layout and simulations                                      | 103 |

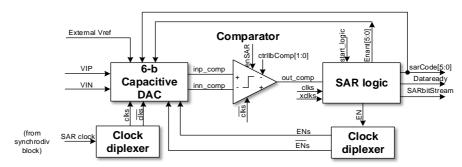

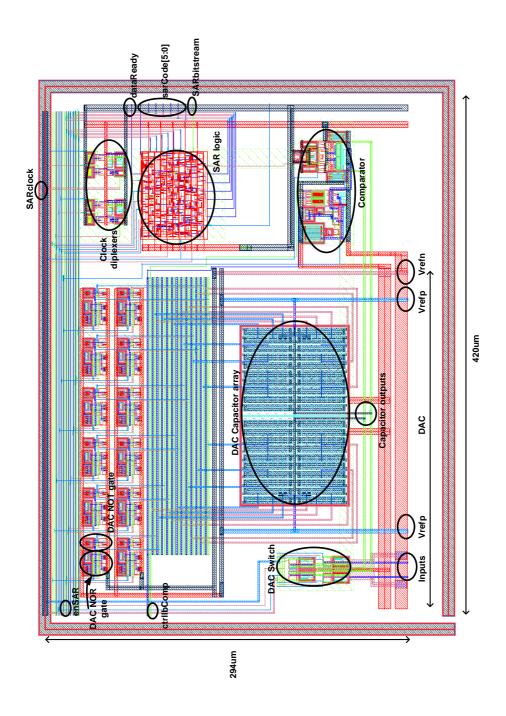

| 5.5. 6-bit S   | SAR ADC design                                              | 107 |

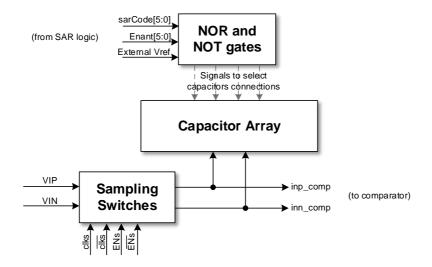

| 5.5.1.         | Binary weighted DAC                                         | 109 |

| 5.5.2.         | SAR sampling switches                                       | 112 |

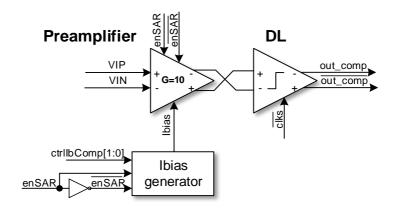

| 5.5.3.         | Comparator architecture                                     | 114 |

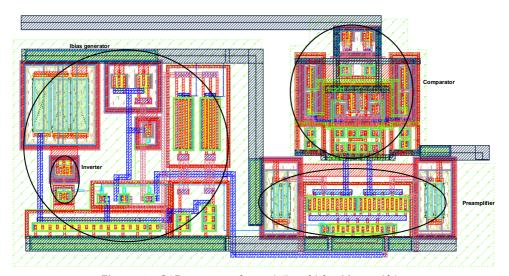

| 5.5.4.         | Layout and simulations                                      | 117 |

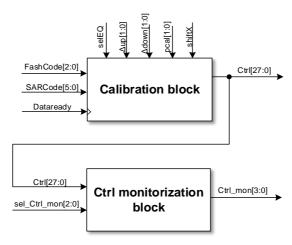

| 5.6. Calibr    | ation block (COCL)                                          | 119 |

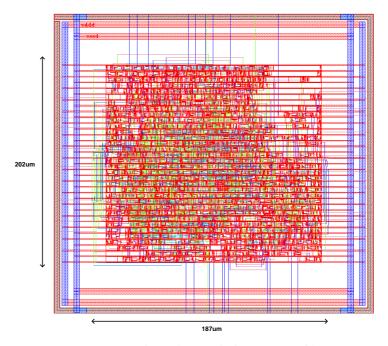

| 5.6.1.         | Layout and simulations                                      | 120 |

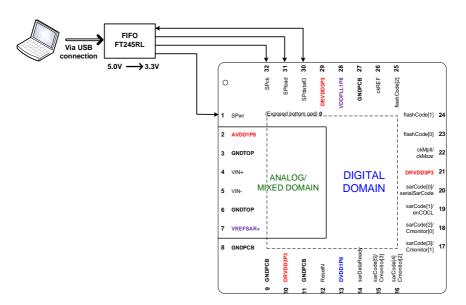

| 5.7. ASIC (    | CALFLASH layout and simulations                             | 123 |

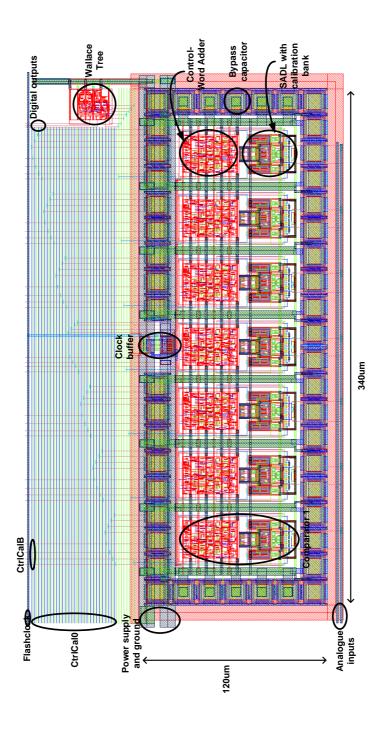

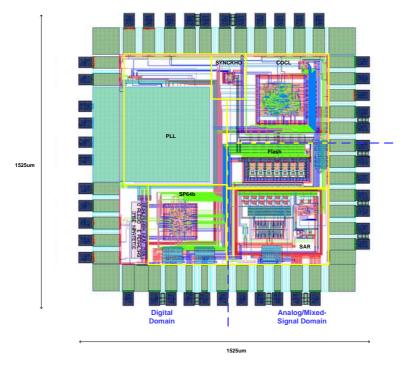

| 5.7.1.         | Layout                                                      | 123 |

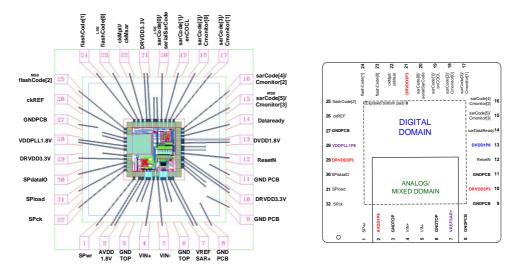

| 5.7.2.         | Bonding                                                     | 123 |

| 5.7.3.         | Simulations                                                 | 124 |

| 6. Experin     | nental Results                                              | 127 |

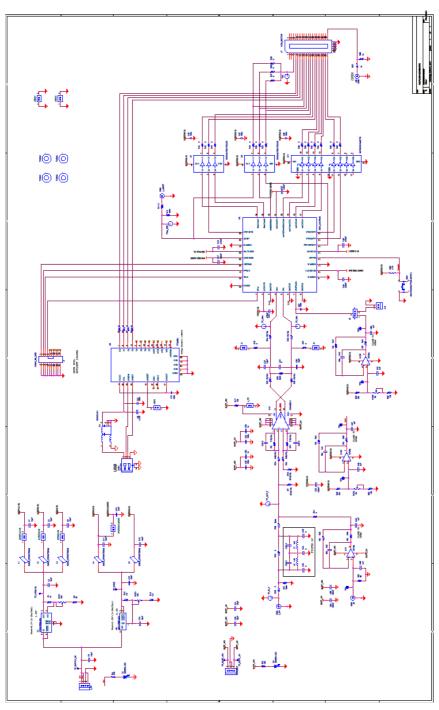

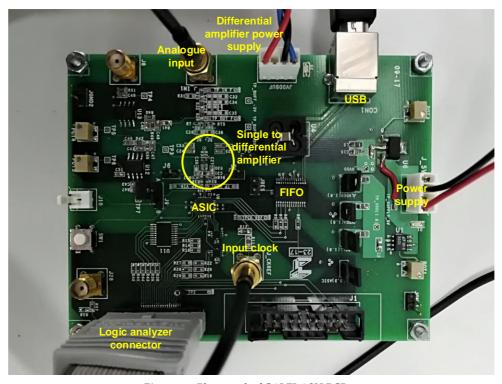

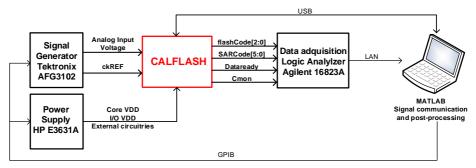

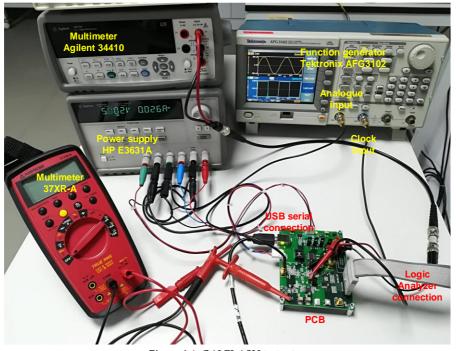

| 6.1. PCB s     | etup                                                        | 127 |

| 6.2. Test s    | etup                                                        | 129 |

| 6.3. Comn      | nunication and control                                      | 131 |

| 6.4. Meas      | ured results                                                | 131 |

| 6.4.1.         | Normal conversion of flash ADC                              | 132 |

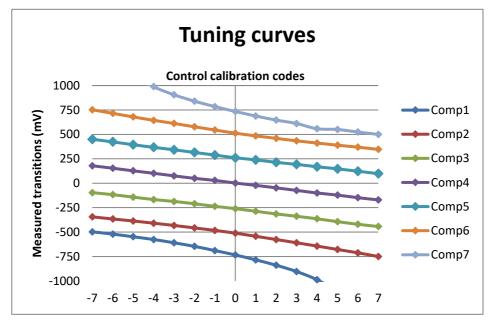

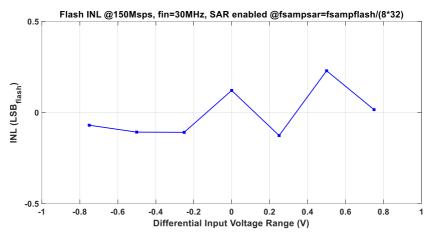

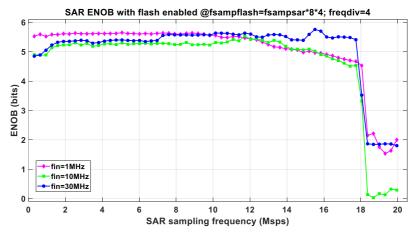

| 6.4.2.         | Normal conversion of SAR ADC                                | 139 |

| 6.4.3.         | Normal conversion of flash ADC with external offset applied | 142 |

| 6.4.4.         | Calibration of flash ADC                                    | 146 |

| 7. Conclus     | sions and Future Work                                       | 165 |

| 7.1. Concl     | usions                                                      | 165 |

| 7.2. Futur     | e work                                                      | 167 |

| List of Figure | es                                                          | 169 |

| List of Table  | s                                                           | 177 |

| List of Symb   | ols and Acronyms                                            | 179 |

| References     |                                                             | 181 |

## 1 Introduction

In this chapter an introduction of this work is given. Motivations for developing this thesis work are exposed in Section 1.1. Goals and applied proposals are summarized in Section 1.2. Finally, thesis organization is described in Section 1.3.

#### 1.1 Motivation

Analog-to-digital converters (ADCs) are one of the main building blocks in current electronic systems, especially in communication, signal processing and biomedical fields. The evolution of ADCs has been changing with the requested specifications of the devices technology.

Among the different types of ADCs, flash converter is the simplest and fastest architecture, achieving a great bandwidth (tens of GHz) [1]. Flash converters have often low resolution (currently hardly achieve 6 bits) since as resolution increases, the number of comparators greatly rises, so does the power consumption [2]. Indeed, non-idealities in ADCs appear as higher speed is demanded.

Offset caused by element mismatch errors is an important issue in flash ADCs. These errors affect greatly to the flash performance, decreasing its linearity. For this reason, using calibration techniques to reduce the offset is crucial in this kind of converters. Thanks to calibration, errors in the ADC are corrected and, thus, it is possible to relax the architecture complexity design. This way, accuracy and speed increase and both power consumption and area decrease due to the simpler architecture.

These offset errors can be corrected either in the analogue or in the digital domain. Many analogue methods have been proposed, such as error storage or trimming of elements [3]-[18] or traditional auto-zeroing techniques [19]-[21]. There are also methods, such as averaging [6]-[10] [22]-[23] which can executed in the analogue as well as digital domain. These techniques are employed to cancel for the offset in comparators, but also they can be used in preamplifiers or even in the whole comparator.

Due to the additional hardware that requires analogue calibration and the quick evolution of digital technologies, the use of digital techniques to correct the resulting errors in ADCs is quite often employed. Digital methods based on adaptive processing algorithms greatly reduce the cost of the circuit without attenuating its performance, even for rather complex digital algorithms [24]. Most of these digital methods focus on reducing gain, offset and capacitor mismatch errors [25]-[35] or correcting the coder error [36]-[37]. Several digital methods could be used in the calibration of the offset in latch-based comparators, being DAC-based calibration [32] [38]-[40] and redundancy [41]-[55] of great importance.

In DAC-based calibration, the DAC creates an imbalance in comparator front-end, which is opposite to the actual mismatch, eliminating it. This forced imbalance could be created in several ways, for instance, by varying the current in the branches [47] [56]-[58] or by adding capacitance to them [59]-[61]. Capacitive imbalance could be created by a capacitive DAC [62]-[63], typically compose of a binary weighted capacitor array. The capacitive DAC acts as a SH and, hence, no SH circuit is required in the whole circuit [64].

Moreover, with capacitive imbalance using MOS calibration DAC [59]-[61][64]-[68], a voltage difference is applied to the latch inputs by modifying the DAC control bits. This way, a variation in the offset is done. Once the optimum bits are selected, the offset in the comparator is cancelled. This popular technique has been also employed in the IC demonstrator of this work.

Offset calibration could be accomplished either in foreground or background mode. The first method requires a dedicated period to perform the calibration and, hence, the normal operation of the converter is stopped to fulfill the error measurement and/or its correction [24]. Many foreground calibration techniques are found in the literature. Some of them are aimed to correct the linearity error of the subDAC [30] [69]-[71], others

Chapter 1: Introduction 3

intend to correct the amplifiers gains or comparators offsets [27] [30] [72]-[75], and many of them are employed in offset calibration in flash topologies [32] [39]-[40] [76].

In background calibration methods, measurement and correction tasks are accomplished simultaneously and continuously without ceasing the normal operation of the ADC. Unlike in foreground techniques, no break in the input signal path is needed. All parameters are estimated and corrected in a concurrent way, in contrast to foreground techniques where the calculation and correction of the parameters are done in a sequential manner [77]. Background techniques are much more effective than foreground architectures, however, area and power consumption are increased. Many different approaches in background calibration are considered in different ADCs architectures. Some are based on skip and fill [26] [78], others focus on the reduction of interstage gain errors in pipeline ADCs [79]-[81], and there are some techniques that use a noise input signal for calibration [37] [82]-[85]. Correlation-based background calibration techniques [25] [28] [84] [86]-[90] widely used, since they are faster than the previous methods. Some background calibration architectures require a reference ADC, synchronised with the main converter [9] [91]-[93]. This auxiliary ADC is employed to measure the parameters to be corrected and thus it must have low speed and high resolution to perform an efficient conversion of the analogue input. The estimated outputs of both ADCs are expected to be equal and errors can be measured from the difference between the outputs. Background calibration methods based on digital adaptive algorithms [25]-[26] [72] [81] [83] [94]-[104] exhibit quite reduced cost in the estimation of the errors and also show low power consumption.

#### 1.2 Thesis proposals

Due to the great interest and popularity of background calibration techniques and because of the necessity of proving the efficiency and reliability of some of these methods in current circuits, this thesis has been focused on designing and proving an valuable background technique implemented in a flash ADC in CMOS technology. Since the research group in which I am working has been developed some works related with adaptive algorithms[103] [105]-[106], the first focus of this thesis was studying background calibration in depth, using the previously mentioned works as a reference for developing this dissertation. Therefore, one of the main goals of this work is to prove that background calibration using the adaptive algorithm proposed in [105] is a low-

cost, stable and effective method for obtaining high accuracy in flash and pipeline A/D converters. The algorithm in [105] is used to calibrate the comparator offsets in subADCs of pipeline ADCs and it performs two different tasks: first, the measurement of the offset in each comparator, and second, the generation of calibration code to move the transition of the comparator to its ideal value, thus cancelling its offset. Both jobs are fulfilled in the digital domain and simultaneously.

In this work, this calibration technique is employed for calibrating the comparators' offset in flash ADCs. An integrated circuit has been successfully design and taped out in UMC 180 nm CMOS technology in order to prove the efficiency of the proposed background calibration. To do this, a low-resolution reference-less flash ADC with simple structure and reduced area have been considered. Instead of using a resistive ladder, transitions are implemented built-in in the comparators, by a systemmatic mismatch added to each comparator input front-end.

The design of the comparator and its calibration circuit in a flash ADC is explained step-by-step, going deeply into the dynamic latch design and the different aspects of the comparator structure. In this work, a criterion to identify the optimum parameters of the flash design compatible with the calibration algorithm has been set. With this criterion, the best choice for dynamic latch architecture, calibration bank resolution and flash resolution are selected.

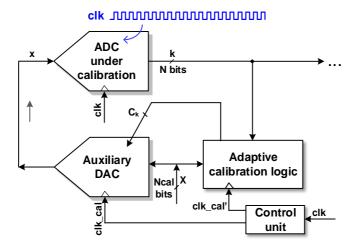

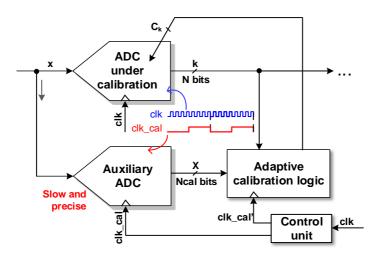

The algorithm in [105] is based on the use of an auxiliary converter with higher resolution (at least 2 more bits) than the converter under calibration to help calibrate its offset. In [105] the auxiliary ADC is the own ADC pipeline queue, but in general, if an auxiliary ADC is employed, it must be a low cost one and have reduced power consumption. It is placed in parallel to the ADC under calibration to avoid interrupting the normal working of the flash. In this work, the chosen auxiliary ADC is a SAR type with binary weighted capacitive DAC, synchronous clock and sequential SAR logic.

SAR output code and flash ADC output codes are compared in a digital processor that implements the adaptive algorithm. The processor output acts on the input comparator front-end, forcing a mismatch that corrects their offsets. In our design, a fully programmable algorithm more versatile than that proposed in [105] has been employed. This way, calibration could be improved by choosing the optimum parameters for the algorithm limits, accuracy, resolution or quantization errors. Further, it is possible to

Chapter 1: Introduction 5

inject 16 different offset values in the range of  $\pm 2$  *LSB* in every comparator of flash ADC. This way, the limits of the ADC and calibration performance could be tested.

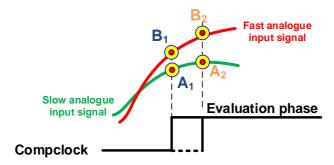

Synchronisation between both ADCs in the circuit is one of the most crucial issues in this work, since no dedicated sample and hold circuit is employed. When flash and SAR ADCs are working concurrently, both ADCs must capture the same input signal. In our design, a specific digital block has been designed to ensure the correct synchronisation between both ADCs clocks.

Using the presented calibration technique improves not only flash accuracy but also its speed, by relaxing the architecture complexity design. Also, both power consumption and area are lessened due to the simpler architecture. Moreover, calibration helps designing a more robust flash ADC, with a safety margin to assure that if there are PVT variations that affect the transitions, calibration process will cover enough range to correct the shifted transitions, bringing them back to their ideal locations. All of the above described have been validated experimentally.

#### 1.3 Thesis Organization

Contents of this work are organized as follows:

- Chapter 1: An introduction of this work is given. Motivations and applied proposals are summarized.

- Chapter 2: A general outlook of ADCs is introduced, summarizing some of the most important properties of ADC performance. Also, the ADCs state-of-the-art is reviewed and some of the most relevant ADC architectures for this work are deeply addressed.

- Chapter 3: A sketch of calibration is presented. Foreground and background

calibration methods as well as analogue and digital techniques are discussed. In

addition, a summary of offset calibration in comparators is given and most

important digital techniques for offset calibration are examined. Further, the

applied solution to correct the offset in a flash ADC is addressed.

- Chapter 4: The design of a comparator and its calibration circuit in a flash ADC is explained step-by-step, going deeply into the dynamic latch design and the different aspects of the comparator structure. Offset measurement and calibration

DAC design are also exposed.

- Chapter 5: The design of the integrated demonstrator is proposed. A general

description of chip architecture is given, analyzing in detail each of its blocks.

Moreover, circuit operation is elucidated and designs of both ADCs and calibration

block are detailed. Special attention is given to synchronisation between flash and

SAR ADCs.

- Chapter 6: Experimental results of prototype are gathered. Additionally, chip architecture and PCB design are elucidated. Test setup and communication interface are both drawn. Finally, results for test chip are presented and analyzed.

- Chapter 7: Conclusions of the thesis work are collected.

# 2. ANALOGUE-TO-DIGITAL CONVERTERS OVERVIEW

Analog-to-digital converters (ADCs) are one of the main building blocks in current electronic systems. They perform the link between the analogue world and digital processes [24]. Nowadays, there is a great deal of different ADCs which cover a wide range of telecommunication applications. ADC performance is determined by parameters like resolution, conversion speed, consumption, input signal range, price,... [107].

In the transformation of the signal from analogue to digital domain, sampling and quantization are required. These two processes must be done properly to avoid losing signal information, which modifies the spectrum. Quantization as well as thermal and jitter errors are the most important problems in ADCs. Also process inaccuracies have influence over the appearance of errors in ADCs.

Due to the widely use of ADCs in modern systems, improving their speed and precision is crucial. A greater resolution will increase the precision at a cost of a greater circuit complexity [107]. There is a variety of ADCs architectures with different properties that make them more or less convenient for a particular application. To select the proper topology, their limitations must be studied. The most employed architectures in high-speed applications, i.e., with sampling rates greater than 5MSPS [108] are flash, interpolative, folding, pipeline and successive approximation [19].

In this chapter some of the most important specifications of the ADC performance and main errors in high-speed ADCs are summarized. Moreover, the state-of-the-art is discussed and some of the most relevant ADC architectures for this work are deeply explained.

#### 2.1. ADCs Basics

Ideally, an N-bit ADC converts the continuous-time analogue input voltage x into a discrete N-bit digital output signal b with a maximum total number of codes of  $2^N$ . Every analogue input value must be approached to one digital output level. This can be achieved by generating reference voltages (also called transition levels  $t_j$ ) in the ADC and comparing the input voltage to these references, selecting the reference voltage which is closest to the input. The analogue input voltage takes infinite values from  $x_{min}$  to  $x_{max}$ , while the digital output can just have certain discrete values from 0 to  $2^N$ -1. The digital signal can be represented in different codifications: binary, decimal, sign-magnitude, two's complement, Gray or one's complement. Binary code is the most used. Gray and thermometer code advantage is that only one bit changes from code to code.

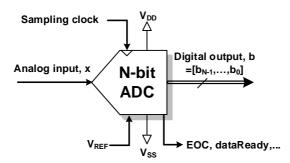

Figure 2.1. Basic N-bit ADC with external reference

An N-bit ADC symbol and its ideal input/output characteristic (transfer characteristic) are shown in Figure 2.1 and Figure 2.2. Analogue input signal x takes values in the range of [-R,R], being the full range analogue range  $FS = x_{max} - x_{min} = 2R$  [2]. The ADC translates the analogue value of x into a digital N-bit output b = ADC(x), with  $b \in [0,M]$ . M is the total number of transition levels  $(M = 2^N - 1)$ , corresponding the first

level to  $t_1 = -R + q$  and the last one to  $t_M = +R - q$ , where quantization step q is the analogue value of the LBS and represents the minimum resolution in the ADC:

$$q = LSB = \frac{FS}{2^N} \tag{2-1}$$

where  $2^N$  is the total number of quantization levels. Value  $t_k$  represents the analogue transition level at k-th digital code, that is, the analogue value where the output signal changes between code (k-1) and code k. The most significant bit (MSB) in digital output is  $b_{N-1}$  and least-significant bit (LSB) is  $b_0$ . Note that when analogue input takes large values, ADC output saturates [2].

#### 3-bit ADC

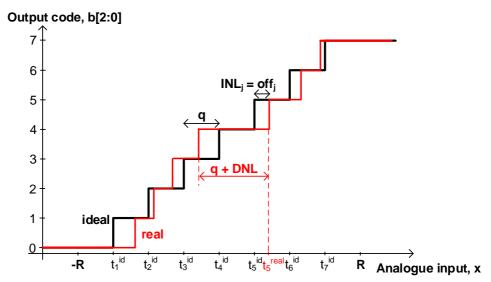

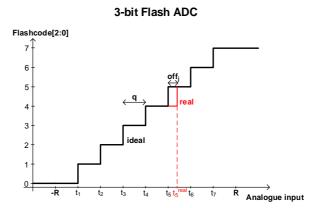

Figure 2.2. Ideal and real input/output characteristic for a 3-bit ADC

#### 2.1.1. Static and dynamic specifications

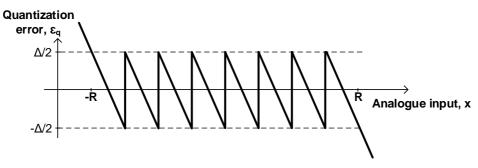

The quantization error ( $\varepsilon_q$ ) (see Figure 2.3) is the unavoidable error which appears due to discretization process. This rounding error introduces a quantization noise in the output signal, even in ideal ADCs [19]. As resolution increases, quantization error reduces and it can be considered a white noise. Assuming that into each code, quantization error has the same probability to be inside the range  $\left[-\frac{q}{2},\frac{q}{2}\right]$  [2], the

quantization noise error power is

$$P_{noise} = \frac{1}{q} \int_{-q/2}^{q/2} \varepsilon_q^2 d\varepsilon_q = \frac{q^2}{12}$$

(2-2)

Figure 2.3. ADC ideal quantization error

Considering a sine input signal  $x = R \cdot \sin(\omega_{in}t)$  with an amplitude of  $R = \frac{FS}{2}$  and  $\omega_{in} = 2\pi f_{in}$ , the signal total power is:

$$P_{signal,max} = \frac{1}{T} \int_0^T \frac{FS^2}{4} \cdot \sin^2(2\pi f_{in}t) dt = \frac{FS^2}{8} = \frac{(q \cdot 2^N)^2}{8}$$

(2-3)

being  $T = \frac{1}{f_{in}}$ . Hence, the effect of the quantization noise is valued by the signal-to-noise ratio (SNR) as the ratio between the maximum signal power and the ideal quantization error power:

$$SNR|_{dB} = \frac{P_{signal,max}}{P_{noise}} = (6.02 \cdot N + 1.76)dB$$

(2-4)

This equation gives information about performance of the ADC depending on the number of bits, *N*. If ADC resolution increases in 1 bit, the SNR improves in 6.02dB while noise power is divided by 4. All the above calculations are valid for uniform distributed quantization levels. Usually, the amplitude of the input signal is not uniformly distributed around the full-scale range, being the quantization error different for each code.

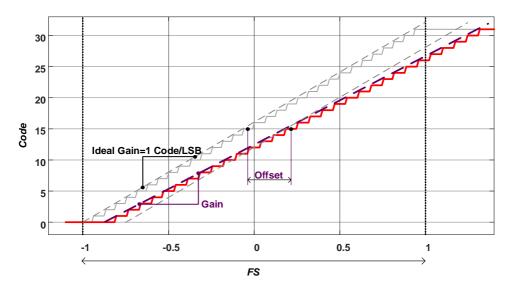

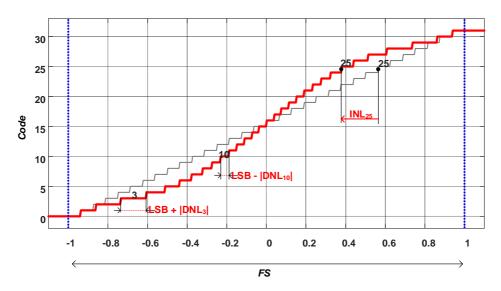

Quantization noise is not the only limitation in ADCs. Other important errors in ADCs must be considered to correctly evaluate the performance of the ADC [2]. In the following, some of these relevant errors are discussed. To measure the performance in ADCs, some well-known specifications are considered. The most common static parameters measured in ADCs are offset and gain errors, differential non-linearity (DNL) and integral non-linearity (INL) (depicted in Figure 2.4 and Figure 2.5). Since elements in the ADC are not ideal, mismatch between components occurs and, hence, the transfer function varies. Any deviation from the ideal input/output characteristic will caused the static errors above mentioned. For instance, in an ideal ADC the difference between two consecutive transitions ( $t_j$  and  $t_{j+1}$ ) is a constant:

$$q_j = t_{j+1} - t_j = q (2-5)$$

In practice, the already discussed second order effects introduce deviations that modify the transition' location and offset appears. Offset of two consecutive transitions, of  $f_j = INL_j$  and  $off_{j+1} = INL_{j+1}$ , will modify the corresponding quantum width  $q_j$  this way:

$$q_{j} = (t_{j+1}^{id} - of f_{j+1}) - (t_{j}^{id} - of f_{j}) = q + DNL_{j}$$

(2-6)

Because of its relevance for this work, offset errors are profoundly studied in the following sections.

Figure 2.4. Example of offset and gain errors

Figure 2.5. Example of INL and DNL errors

Considering the dynamic performance of A/D converters, there are several ways of characterizing the accuracy and noise in ADCs. Some of the most popular specifications are signal-to-noise ratio (SNR), signal-to-noise-distortion ratio (SNDR or SINAD),

effective number of bits (ENOB), total harmonic distortion (THD) and spurious-free dynamic range (SFDR). The SNR is related to the ENOB through equation (2-4), changing *N* by *ENOB*:

$$ENOB = \frac{SINAD|_{dB} - 1.76}{6.02} \tag{2-7}$$

Dynamic errors such as settling errors, non-linear slew, clock feedthrough or glitches [2] are due to the quick change of the input signal, especially as input frequency and amplitude increase. Based on an FFT analysis, these specifications will quantify the distortion and noise in the ADC and, hence, measuring them is essential to evaluate the ADC performance. Notice that since ADC samples the input signal, other sources of error related to sampling must be evaluated as they have a great impact in the SNR of the output signal. These kinds of errors are addresses in the following section.

#### 2.2. Errors in ADCs

In real sampling ADCs, during the conversion of the analogue input into a digital level, a great number of noise errors could appear. Some of the dominant limits of high speed ADC are jitter and thermal noises. Also, comparator metastability is another source of error to be taken into consideration.

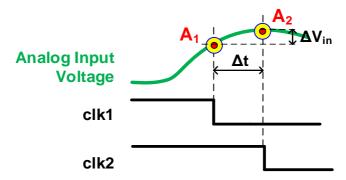

#### 2.2.1. Sampling-time jitter

In ADCs the signal must be sampled. This sampling could be done by using a sampleand-hold circuit at the input of the ADC or without it. However, in the second case the performance of the ADC at high signal frequency could be rather poor since dynamic performance is restricted by the precision in the sampling instants [2].

Sampling is influenced by the uncertainty in the clock [24], which generates clock jitter at the sampling instants. Switch imperfections and delays generated by logic blocks contribute also to the alteration of the sampling instants. Jitter affects to dynamic performance of simple-and-hold in ADCs and, hence, to the value of the sampled signal. This variation in the sampling instants produced by clock jitter originates that sampling at time t is actually the sampling time  $(t + \Delta t)$  [2]. For the sinusoidal input signal x(t) =

$R \cdot \sin(\omega_{in}t)$ , the error  $\Delta x(t)$  produced by clock jitter is

$$\Delta x(t) = \mathbf{R} \cdot \mathbf{\omega}_{in} \cdot \cos(\mathbf{\omega}_{in} \mathbf{t}) \cdot \Delta t \tag{2-8}$$

and its greatest effect is achieved when the slope of the input signal reaches its maximum, that is, when t=0:

$$\Delta x = \mathbf{R} \cdot \mathbf{\omega}_{in} \cdot \Delta t \tag{2-9}$$

Sampling error increases for high input frequencies, since a small  $\Delta t$  will lead in a great error  $\Delta x$ . However, sampling error is not dependent on the sampling clock frequency.

The power of the jitter error is

$$P_{jitter} = \langle \Delta x(t)^2 \rangle = \langle (\mathbf{R} \cdot \omega_{in} \cdot \cos(\omega_{in} t))^2 \rangle = \frac{1}{2} \cdot \mathbf{R}^2 \cdot \omega_{in}^2 \cdot \langle \Delta t^2 \rangle$$

(2-10)

The power of the input sine signal is

$$P_{signal} = \langle x(t)^2 \rangle = \frac{1}{2} \cdot \mathbb{R}^2$$

(2-11)

and the SNR is given by

$$SNR = \frac{P_{signal}}{P_{jitter}} = \frac{1}{\omega_{in}^2 \cdot \langle \Delta t^2 \rangle}$$

(2-12)

which can be expressed in dB as

$$SNR|_{dB} = -20 \cdot \log(\omega_{in}^2 \cdot \langle \Delta t^2 \rangle)$$

(2-13)

Due to sampling jitter, the SNR is degraded. For instance, achieving a SNR of 66 dB at input frequency  $f_{in} = 100MHz$  requires  $\langle \Delta t^2 \rangle = 80ps$  clock jitter [24].

#### 2.2.2. kT/C noise

Being one of the main limitations in SH circuits, thermal noise is an unavoidable error that appears in sampling switch due to the thermal excitation of charge carriers [109]. In

a typical SH circuit during sampling, switch is turned off and the capacitor holds the input signal plus the thermal noise.

The operation of a sampling circuit can be modelled by a simple RC circuit [24] and the noise power stored on the capacitor C in the band-base when switch turns off is

$$P_{noise,C} = \frac{kT}{C} \tag{2-14}$$

This noise will limit the signal performance, leading to a reduction of SNR. In order to increase the SNR, the sampling capacitance has to be greater and, hence, power consumption rises. If the capacitance increases by k, the noise voltage decreases by  $\sqrt{k}$  [24]. In low resolution ADCs, thermal noise is a minor issue. However, in high resolutions, a capacitor of tens pF is necessary to cope with the thermal noise [2].

#### 2.2.3. Comparator metastability

Metastability is a fundamental problem in a comparator output and it is associated to comparison. This source of error deteriorates the performance of ADCs at high sampling frequencies. Metastability appears when input signal is small and the comparator cannot make a decision in the assigned time, being stacked in an undefined situation where the output signal is not in a valid logic level ('1' or '0'). Usually comparators are composed of a preamplifier and a regenerative latch. The use of a preamplifier will reduce the chance of having metastability [2] [24], since the probability of having this kind of error is inversely proportional to circuit gain [2]. Metastability errors are of great importance in flash ADCs, where the number of comparators increases exponentially with the number of bits, and mitigating metastability errors in flash is crucial. This problem will be discussed in Section 4.1.

#### 2.3. State-of-the-Art

ADCs evolution has been changing with the requested specifications of the devices technology. Technology scaling in digital applications has been beneficial for ADC performance. CMOs technology is the most convenient for cost-efficient implementation of high-performance data converters, filters and radio frequency transceivers [77]. ADCs are demanding in communication, signal processing and biomedical fields. Their design is nowadays a challenge since they require great conversion efficiency, low power consumption and high bandwidth. Several architectures for ADCs have been proposed, being each of them more convenient to a certain application, depending on its performance parameters. Factors like resolution, sampling frequency, power consumption or area are considered when comparing the performance of different ADCs.

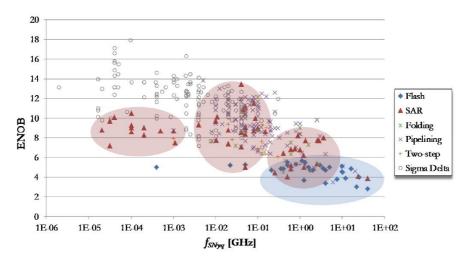

Figure 2.6 illustrates the ENOB versus the conversion rate,  $f_s$ . It contains all publications reported at the ISSCC and VLSI Symposium from 1997 to 2016, gather by Murmann in [110].

Figure 2.17 – ENOB versus sample frequency for published ADCs.

Figure 2.6. ENOB versus conversion rate  $(f_s)$  [111]

Flash converter is the fastest architecture [1] and achieves a great bandwidth (tens of GHz). It has limited resolution (up to 8 bits) because as its resolution increases, the

number of comparators greatly increases, so does the power consumption. The main limitation is mismatch errors, which reduce the flash linearity. A conventional 35GS/s, 4-bit flash ADC (ENOB of 3.7 bits) without calibration is presented in [112] for technology 180nm SiGe BiCMOS. Work [113] presents an excellent power efficient 20GS/s 6-bit time-interleaved ADC with 8 flash-type subADCs, each of them operating at 2.5GS/s with 6 bits resolution. Time-interleaved is implemented in a 32 nm CMOS SOI process and achieves a 5.49 bits of ENOB. Folding, interpolating and averaging schemes are popular among flash ADCs, as well as calibration techniques, particularly calibration methods based on DAC. Several offset correction architectures [40] [114] has been proposed achieving a great efficiency in flash. Work [115] proposed a 5-bit folding flash (4.5 ENOB) in 90nm digital CMOS with a DAC for digital calibration that greatly reduces the power consumption and a rather small trade-off between power consumption, sampling frequency and ENOB.

Pipeline ADC is employed in applications that need medium to high resolution (10-16 bits) with great bandwidth. The major drawback is the non-idealities of each stage, creating distortion. In [116] a 4GS/s 13b pipelined ADC with SNDR of 56dB implemented in 16 nm CMOS is presented. Quite challenging specifications are achieved when using nonlinearity calibration, such as in [117].

SAR ADC is used in medium resolution (8-12 bits) applications that employ medium to large bandwidths (<100MHz). This is the most interesting topology in terms of power efficiency and has a reduced size when compare with flash and pipeline ADCs.

Sigma-delta converter is employed in very high resolution (16 bits or greater) applications that require small to medium bandwidth. It provides a high SNR, however DAC nonlinearities limits the performance of this type of ADC. Work [118] proposes a 12-bit ENOB wide bandwidth sigma-delta ADC operating between 20 and 40 MS/s in 130nm CMOS technology.

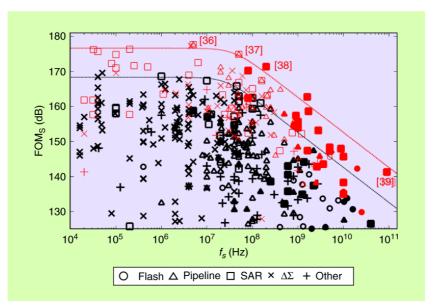

Figure 2.7 [111] illustrates the Walden Figure-of-Merit (FoM) as a function of the conversion rate,  $f_s$ , with publications in [110]. Walden FoM is defined as the power consumption divided by the conversion rate and  $2^{ENOB}$ . Works after 2010 are pointed out in red colour and time-interleaved designs are indicated by solid fill mark.

Figure 2.7. Walden FoM versus conversión rate  $(f_s)$  [111]

Nowadays, some of the ADCs performances are overlapped by different architectures. Although flash has been the fastest ADC, in recent years SAR topology has achieved ultrahigh speed, being this topology rather demanding. Such a high speed has been reached by using time-interleaving [111] [119]. For instance, a 2.6 GS/s 10b SAR interleaved ADC implemented in 65nm CMOS and with SNR up to 49dB is presented in [120] and in a recent paper [121] a 90GS/s 8-bit interleaved SAR in 32nm digital SOI CMOS is proposed, with a SNDR. Above 36dB SNDR up to 6.1GHz. Some other improved ideas include combination of SAR and pipelining as in [122] or pipelined flash-SAR ADC [123], where better resolutions than flash are achieved at high speed. The prototype in [122] is a 12-bit 50MS/s pipeline ADC that includes a SAR subADC in its first stage. The proposed circuit has been implemented in 65nm and 90nm CMOS, achieving an ENOB of 10.6 bits and Walden figure-of-merit of 52fJ/conversion-step. Paper [123] shows a 14-bit 200MHz power-efficient pipelined flash SAR ADC with no dedicated sample-and-hold circuit in the first stage, which has been designed using a 65nm CMOS technology.

#### 2.4. Relevant ADC architectures for this work

To select the most convenient ADC for each application, basic parameters and limitations of each ADC topology must be well investigated. In the following subsections a study of the most relevant ADC architectures for this work is carried out.

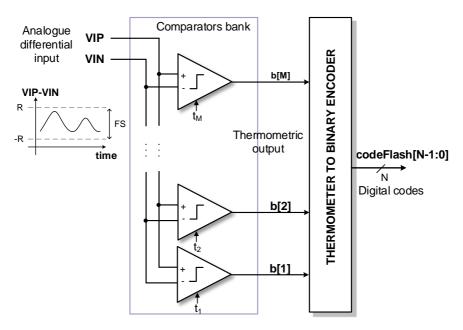

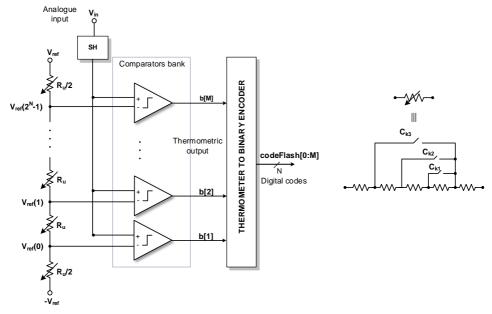

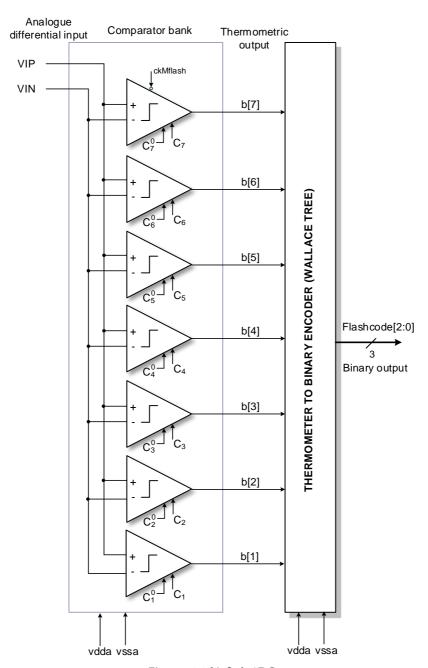

#### 2.4.1. Flash ADC

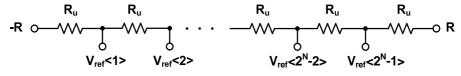

Flash ADC (see Figure 2.8) is the simplest and fastest topology, since it is formed of a series of comparators in parallel that allows achieving a high conversion speed [19]. There is one comparator for each reference level (transition  $t_j$  in the figure). Each comparator senses the input signal to its corresponding reference level [2], giving a '1' if the input signal is larger than the reference voltage, otherwise the comparator output is '0'. Therefore, the output pattern corresponds to a thermometric representation. An N-bit flash consists of  $M = 2^N - 1$  comparators and an encoder as depicted in Figure. The  $2^N - 1$  thermometric output is not so useful and, hence, an encoder is employed to transform the thermometric code into a more convenient codification, such an N-bit binary output [24] [124].

Figure 2.8. An N-bit flash ADC

As input signal is applied to all comparators at the same time, flash output is only delayed by one comparator delay and by the small delay introduced by the encoder gates [124]. However, the number of comparators increases exponentially with the number of bits, leading to large power consumption and area (and therefore cost) for resolutions above 8 bits [2]. The use of traditional techniques such as interpolation and folding [115] [125]-[128] has increased the resolution in flash while reducing the number of preamplifiers (interpolation) or comparators (folding) and also decreasing the power consumption [124]. Even for flash resolutions of 4-6 bits, to achieve good power efficiency, small transistors are used, requiring hence offset calibration in flash [38].

In addition to this limitation in resolution, another drawback due to the great number of comparators in this architecture is kickback noise at the analogue input. The effects of kickback noise from latch to the inputs when latch goes from reset mode to decision mode creates a great amount of noise at the comparators' inputs, producing an error that is proportional to the square of the number of comparators [19]. Using preamplifiers attenuates kickback noise as well as comparator offsets. Also, the capacitance at input node increases with the number of comparators. Moreover, metastable errors (already discussed in Section 2.2.3) due to the lack of SH can create sparkle errors (unwanted

zeros) in the thermometer code which can be mitigated by using additional circuitry such as a fault tolerant encoder [124]. Sparkle and offset problems will be discussed in Chapter 4.

#### 2.4.2. Pipeline ADC

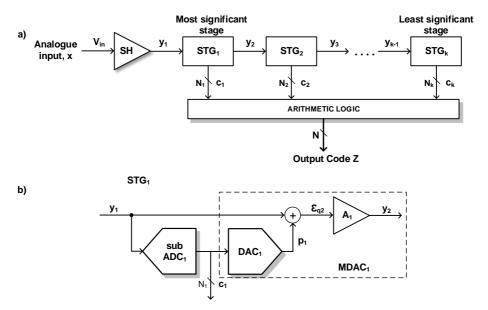

A pipeline ADC employs several stages, each of them resolving consecutively a part of the whole ADC resolution. A block diagram of a pipeline ADC with k stages is illustrated in Figure 2.9. A front-end SH circuit is followed by k stages, being  $STG_1$  the most significant stage and  $STG_k$  the least significant one. Each stage is form of a low resolution ADC (subADC), which converts the analogue input  $y_j$  into a digital code  $c_j$ , and a multiplying DAC (MDAC) to substract the subADC output from the input, obtaining a quantization error that is later amplified to obtain the residue  $(y_{j+1})$ . The residue amplification allows using the full-scale range in next stage input. In just one single clock period, the first stage samples the input and gives the MSB, while the second stage generates the residue of the previous sampled input. The first stage generates  $N_1$  bits, the second stage  $N_2$  bits, and so on. The pipeline total resolution is the addition of the bits in each stage  $(N = N_1 + N_2 + \dots + N_k)$  [24] and is generated by logic circuitry. Due to this pipeline operation in which each sample must propagate through the complete ADC structure, the output is generated with a latency time which is directly proportional to the number of stages.

Figure 2.9. a) Pipeline ADC architecture with k stages, b) Architecture of stage 1

The accuracy and, hence, design of first stages is more demanding than that of last stage. The DAC accuracy is relaxed after few stages, since input referred residue in stage k decreases by  $2^k$  [24]. Also, the amplified residue could have greater or lower amplitude than the full-scale range due to non-idealities in ADCs, DACs and amplifiers. This will be a problem if the next stage ADC is not able to convert the residue outside the full-scale range. These ADC accuracy errors could be overcome by employing techniques such as reducing the amplifiers' gain or adding redundancy levels in ADCs [24], and then compensating them with digital correction techniques.

#### 2.4.3. SAR ADC

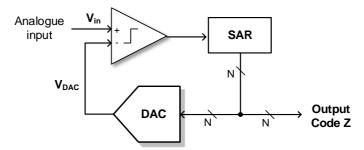

Successive Approximation Register (SAR) ADC has become very attractive due to its outstanding power efficiency at moderate conversion speed. SAR ADC is based on successive approximations algorithm and consists of a comparator, a control logic register and a DAC (see in Figure 2.10).

Figure 2.10. Typical SAR ADC circuit

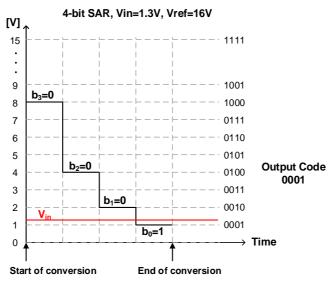

Conversion starts by forcing all the bits in the register to '0', except for the most-significant bit (MSB) which is set to '1'. The DAC converts its digital input into an analogue value  $V_{DAC}$  and the comparator compares it to the analogue input  $V_{in}$ . If analogue input is greater than the DAC output, the MSB of the register is maintained at '1', otherwise it is set to '0'. The next most-significant bit is then set to '1' and the following are set to '0'. The process is repeated for all bits in DAC. Then conversion is finished and the register output corresponds to the analogue input. Figure 2.11 shows an example of DAC output in a 4-bit SAR ADC. Notice that in first step the comparator compares  $V_{in}$  with  $V_{DAC} = \frac{V_{ref}}{2}$ , being  $V_{ref}$  the SAR reference voltage and the dynamic full-scale range  $FS = \begin{bmatrix} 0, V_{ref} \end{bmatrix}$ . In second step, the comparison of  $V_{in}$  to  $V_{DAC} = \frac{V_{ref}}{4}$  or to  $V_{DAC} = \frac{3V_{ref}}{4}$  is carried out, and so on. As conversion progresses, DAC output is approached to a stable value, which will correspond to the measured analogue input. The number of iterations is determined by the number of bits. In the example, a 4-bit SAR employs four iterations to complete the conversion. Hence, the speed of SAR converters is reduced in high resolutions [2].

Figure 2.11. Example of a DAC operation in a 4-bit SAR ADC

SAR architecture has become very popular in low-power medium-resolution, moderate-speed applications. In this kind of converters, DAC determines the conversion speed of the converter and also consumes most of the overall power dissipation of the SAR [129]. Moreover, the DAC determines the accuracy and linearity. Charge redistribution configurations in switched capacitor DAC are widely used since their accuracy and linearity are determined by the accuracy of the capacitor plate area, capacitance and mismatch emerged from fabrication processes [124]. The power consumption of the circuit is determined only by the comparator and the dynamic charging and discharging of the capacitor array [24]. In [129], the power consumed by switching the capacitors of the DAC and its linearity behaviour in three different topologies is compared: conventional binary-weighted capacitive array [130]-[132], binary-weighted capacitive array with attenuation capacitor [133]-[134] and split binary-weighted capacitive array DAC [135]-[137].

The serial topology of the SAR ADC limits its conversion speed. At high speeds, its power consumption increases. There are several methods for increasing speed in SAR ADCs. One of the most popular strategies is is the using time-interleaving [120]. In [138] authors use a nonbinary 2-bit/cycle structure, which increases the speed and robustness while relaxing the DAC settling requirements. Asynchronous dynamic logic [139]-[141]

has been also employed to reduce the conversion time, decreasing the complexity of the digital logic and, hence, the power consumption. More improvements have been included in [142], where a fast 1-bit/cycle SAR ADC containing only one comparator and asynchronous clock with domino logic is proposed.

# 3. OFFSET COMPARATOR CALIBRATION IN ADCS

Non-idealities in ADCs appear as higher speed is demanded. Errors due to inaccuracy and element mismatches affect greatly to the ADC performance. For this reason, some sort of correction is needed to compensate for these errors. When the non-idealities are measured, they could be corrected afterwards using extra analogue or digital architecture. Error compensation could be carried out online or offline, requiring the second method a period of time for calibration [24]. These aspects will be addressed in Section 3.1.

Moreover, error correction is used to improve the precision of a certain block of the ADC or the whole circuit [19]. An overview of offset calibration in comparators is presented in Section 3.2 and most important digital techniques for offset calibration are discussed in Section 3.3, such redundancy or DAC-based calibration. Finally, in Section 3.4 the applied solution to correct the offset in a flash ADC is explained. This solution consists on a digital background calibration based on the adaptive algorithm presented in paper [105]. With this algorithm is, first, measured the offset in the comparator and, then, a calibration code is generated to shift the transition of the comparator to its ideal value and, hence, cancel its offset. Both tasks are explained in this section. Moreover, two different ways of generating the digital input are considered and some possible applications of this calibration method are addressed.

### 3.1. Calibration Overview

Traditionally, analogue techniques have been employed to compensate for static and dynamic errors in ADCs, specially mismatch, non-linearity and gain deviations. Many analogue methods have been proposed, such as error storage or trimming of elements. The quick evolution of digital technologies has incited the use of digital techniques to correct the resulting errors in ADCs. These digital methods, based on adaptive processing algorithms, greatly reduce the cost of the circuit without attenuating its performance, even for rather complex digital algorithms [24].

Thanks to calibration, errors in ADC are corrected and, thus, it is possible to relax the architecture complexity design. This way, accuracy and speed increases and both power dissipation and area decrease due to its simpler architecture.

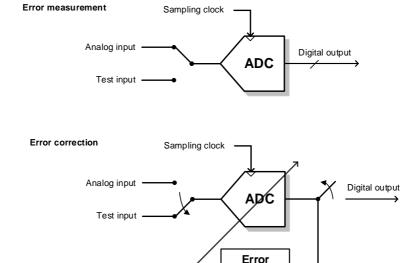

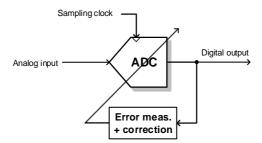

The process of error calibration in ADCs is accomplished in two phases. First phase is called *Error Measurement* and it comprises the error estimation regarding to the ideal ADC. Then the second phase, named *Error Correction*, becomes involved to cancel the errors. Both steps could be done either in foreground or background mode. Furthermore, calibration could be fulfilled in the analog or digital domain. Next sections will introduce these terms, giving some examples to a better understanding.

### 3.1.1. Foreground vs. Background Calibration

Two types of calibration could be carried out depending on whether or not the conversion is interrupted to measure and correct the errors. First group, *Foreground Calibration*, needs a dedicated period of time to perform the calibration. This approach (see Figure 3.1) is also called offline calibration, since the normal operation of the converter is stopped to perform the error measurement or its correction. Both error measurement and correction are not simultaneously executed. During the measurement phase, the ADC input is disconnected and a proper input is then applied to the ADC. Sometimes this input is generated by an accurate DAC placed on-chip, calling this process self-calibration, since the input for measurement cycle is produced by the circuit itself [24].

Most frequently, calibration cycle is carried out at power-on or during inactivity periods of the ADC [24]. Thus, any unexpected environmental change (such as power supply or

temperature) or aging effects will influence the measurements, shifting their values, and, hence, they will be wrong. Then, a new calibration cycle that interrupts the conversion is required to measure the errors properly. Hence, having periodic calibration cycles will be required in ADCs that work for long time [24].

Figure 3.1. Foreground Calibration

correction

There are many foreground calibration techniques applied to Pipeline ADCs, either to correct the linearity error of the DAC [30] [69]-[71] or the amplifiers gains and comparators offsets [27] [30] [72]-[75]. In addition, foreground methods are employed in offset calibration in flash topologies [32] [39]-[40] [76], folding structures [128] or SAR ADCs [143]-[144].

In applications in which the ADC cannot be disconnected or where the parameters have great variations, a second approach has been considered, which is faster than the foreground method. *Background Calibration*, also called online calibration, works simultaneously with the ADC as shown in Figure 3.2. Error measurement and calibration are accomplished simultaneously and continuously without ceasing the normal operation of the ADC. Unlike in foreground techniques, no break in the input signal path exists. All parameters are estimated and corrected in a concurrent way, in contrast to online techniques where the calculation and correction of the parameters are done in a sequential manner [77].

Many different approaches in background calibration are considered. One possible calibration technique is skip and fill [26] [78] and consists of skipping occasionally an input sample for measuring the errors and employing nonlinear interpolation to fill the skipped sample. Another calibration technique involves applying correlation-based calibration to correct for the errors in the ADC. In [79]-[81] the interstage gain errors are reduced in pipeline ADCs by means of correlation-based techniques. Papers [37] [82][85] use a noise input signal for calibration, avoiding the use of redundant analogue hardware. However, in some of these architectures the dynamic range of the ADC is decreased because the calibration signal employs some of the input full scale range. In addition, correlation-based calibration with split-channel ADC is widely used, which is faster than the previous methods. In this technique, the original single-channel ADC is split into two identical parallel ADC channels whose devices' sizes are halved of those of the original ADC. The same analogue input is quantized by both ADC channels and the correlation between their digital outputs is then extracted. The split-channel calibration technique has been applied to cyclic [86]-[87] as well as pipeline ADCs [88]. The latter makes use of random choppers to improve robustness of calibration scheme and a radix-based gain correction of the pipeline stages with slight signal-path modification. This technique modifies the structure of the ADC and the correlationbased algorithm needs a large number of input samples, increasing the convergence speed of the ADC. Also, correlation-based digital calibration with random choppers has been utilized for cancelling the offset, gain and timing mismatches between two channels [25] and more than two channels [89] in time-interleaved ADCs. Also, [90] employs random choppers to calibrate the offset of the comparators in a flash ADC, but conversion frequency is limited due to the slow chopping operation. Further, [28] applies correlation-based calibration to radix extraction in pipeline or cyclic ADCs to correct the errors resulting from capacitor mismatches and amplifier gain. A correlationbased algorithm 1000 times faster than the previous papers is presented in [84] applied to a pipeline or cyclic ADC without the need of any additional analogue block and able to correct the interstage gain and capacitors mismatches in MDAC.

Moreover, some calibration schemes require a reference ADC, synchronised with the main converter. This auxiliary ADC is employed to measure the parameters to be corrected and thus it must have low speed and high resolution to perform an efficient conversion of the analogue input. The estimated outputs of both ADCs are expected to

be equal and, based on them, errors can be measured. Several examples could be found in the literature. For instance, in [9] a digital background calibration to calibrate preamplifier and comparator offsets of a folding ADC is published. Calibration employs two-channel ADCs that convert the same input and averaging of the two channel outputs to obtain the whole circuit output. The difference between the two channel outputs is employed in the digital calibration. In contrast with [10] [28] [90], the ADC achieves multi-GHz with this background calibration with no need for extra analogue circuit. Further, in [91] a background calibration technique compares the pipeline ADC output to that of a cyclic ADC and improve the linearity of a fast and inaccurate pipeline ADC. Also, [92] and [93] calibrate the interstage gain in pipeline ADCs by using a slow and high-resolution reference sigma-delta ADC. Since errors are measured by the circuit on-chip, this type of background calibration is self-calibrated. Background techniques are much more effective than foreground architectures, however, area and power consumption are increased.

Figure 3.2. Background Calibration

Furthermore, background methods include digital adaptive algorithms [25]-[26] [72] [81] [83] [94]-[104] with quite reduced cost to obtain the estimation of the errors and low power consumption. In this thesis a background self-calibration technique based on this kind of adaptive algorithms is applied to a flash ADC to correct the offset errors in comparators.

### 3.1.2. Analogue vs. Digital Calibration

ADC errors can be corrected either in the analogue or in the digital domain. *Analogue calibration* fulfills the error measurement in the analogue domain, regardless of whether the error correction is done in the analogue or in the digital domain. On the contrary,

digital calibration performs the error estimation in the digital domain, based on a digital algorithm that measures the error to subsequently compensate for it. This error compensation could be done either in the analogue or in the digital domain

A *mixed-signal calibration* approach uses a digital processor to detect the parameters and then adjusts certain analogue circuits to suppress the effects of these parameters. If error measurement and correction are both done in the digital domain, this type of calibration is called *pure digital calibration*.

Many examples of analogue calibration techniques have been published. In [3]-[4] trimcapacitors are employed to calibrate the DAC mismatches and interstage gain errors in a pipeline ADC. Capacitor-averaging technique has been employed in [5]-[11] to correct the offset in comparators. In [12] a non-restoring algorithm that changes the polarity of the reference depending on the previous bit decision is used to correct errors sources in switched-capacitor in pipeline ADC in the analogue domain without the need of trimming. In [13] a SAR ADC with an analogue background calibration that detects the sign of the errors and modify the reference voltage to correct the offset error of the comparator and the DAC mismatch error. Also, in [14]-[16] the reference voltage is periodically modified in a cyclic and a pipeline ADC, respectively. [17] presents a background analogue technique to calibrate nonidealities in pipeline and SAR ADCs without the need for complex signal processing, extra data converter or extra clock. In addition, paper [18] employs a reference DAC to generate the voltages required to adjust the thresholds of the comparators and suppress the offset errors in the ADC.

Nevertheless, analogue calibration requires additional analogue hardware, hence, exhibiting greater complexity than digital techniques, since the latter employs just a digital algorithm to detect the error. Therefore, digital methods have lower cost and power consumption. They have become very popular since they benefit from fast speed due to the simplicity when measuring the errors, in contrast to the penalty in speed that analogue calibration suffers. Nevertheless, either analogue or digital calibration techniques could be employed in a single block, such as preamplifier, dynamic latch or comparator, or even in the entire ADC.

Digital calibration acts either on the hardware of the ADC or on the output code to correct the errors. For instance, many papers focus on reducing gain, offset and capacitor mismatch errors by means of digital calibration in time-interleaved [25]-[26], pipeline

[27]-[31], flash [32]-[33], algorithmic [28] [34] or SAR [35] ADCs. Others are aimed to calibrate in the digital domain the coder error of a flash [36] or in a pipeline [37] ADC. In Section 3.2 more examples of digital calibration employed to correct the offset in comparators are given.

### 3.2. Offset Calibration in Comparators

In ADCs, an optimal design of comparators is rather important since comparators are the main blocks in ADCs. ADC properties such as resolution, power dissipation and speed are influenced by the comparator design. The major concern in comparators is the offset. Caused by mismatch devices, offset can distort the output signal of the ADC, hence deteriorating its accuracy.

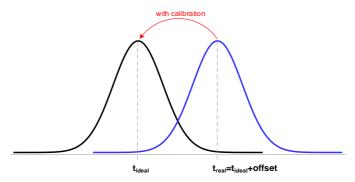

Typically, comparators for low-power high-speed applications are designed considering small transistor sizing to diminish the power dissipation, thus reducing parasitic capacitances and increasing the comparator speed. However, small elements in the dynamic latch introduce mismatches between the two branches of the latch which originate an offset in the comparator. Therefore, the use of calibration techniques to reduce the offset is essential when using small elements. Calibration acts on the comparator itself to correct the offset by moving its threshold back to its ideal value. Figure 3.3 shows the result of calibration acting on a comparator which presents an offset. Ideally, comparator threshold voltage is  $t_{ideal}$ . The exiting offset in the comparator has varied the location of the transition to the new position  $t_{real}$ . Thanks to the application of calibration, the imbalance is compensated, moving the transition location back to its ideal value  $t_{ideal}$  and, hence, being now the offset value close to zero.

Figure 3.3. Offset calibration application

Offset calibration could be done either in the analogue or in the digital domain. However, digital calibration is more often employed due to its reduced circuitry, cost and power consumption.

Traditionally, auto-zeroing techniques have been used to cancel for the offset in comparators. During the first phase, the input is disconnected and the offset is measured and stored on capacitors. In second phase, the input is connected and the offset is corrected by subtracting it from the signal [19]. This technique is employed either in dynamic latches or in preamplifiers [19]-[21].

A method that could be executed in the analogue as well as digital domain is averaging. As well as auto-zeroing, this technique is utilised in preamplifiers, dynamic latches or even in the whole comparator. Averaging is a popular method for reducing offset in preamplifiers in flash ADCs. This technique uses resistors to connect the amplifier outputs of contiguous comparators. These resistors average the offsets and reduce them. Work [22] presents a flash ADC with two-stage resistor offset averaging to reduce preamplifiers offsets without the need for calibration techniques. Paper [23] proposes a flash whose preamplifier uses a resistor averaging/interpolating network to reduce the random offsets caused by the small device mismatch. Alternatively, capacitive averaging technique could be employed, substituting resistors by capacitors. This technique is effectively used in [6]-[8]. In addition, paper [145] proposes a combination of resistors and capacitors to perform the offset averaging in a flash ADC and fulfill a greater offset reduction than previous averaging methods.

Averaging is often employed in combination with other techniques. For instance, paper [9] proposed a folding ADC with averaging of two comparator offsets and

compensation of device variation by calibration techniques. It employs a two-channel background calibration technique to improve the INL and DNL. The two ADCs convert the same input and their outputs are averaged to give the circuit output. The difference of the ADCs outputs is used in the digital calibration algorithm to reconfigure the reference connection between reference ladder and preamplifiers and correct the offset of the comparators. With this technique the offset of contiguous comparators in each ADC are averaged and reduced. Similar two-channel architecture with averaging is proposed for the algorithmic ADC in [10]. However, digital background calibration uses an adaptive process based on the least mean square algorithm.

In contrast to the offset correction in the analogue domain, different digital methods could be employed, being redundancy and digital-to-analog converter (DAC)-based methods the most employed. While redundancy is aimed only in correcting the errors in the ADC output with no need for measuring [77], DAC-based calibration corrects the offset by first measuring it and then compensating for it. These two techniques are widely explained in Section 3.3.

### 3.3. Digital Techniques for Offset Calibration in Comparators

As already explained, increasing the transistor sizes in comparator reduces the offset. However, it is convenient to work with small area transistors to reduce power and comparator area. To compensate for the existing mismatch between the two branches of the dynamic latch that appears when small devices are employed in the design, some additional elements are added to the circuit that control the imbalance in order to cancel the offset voltage in the comparator. Several digital methods could be used, being DAC-based calibration and redundancy of great importance. First method modifies the topology of the comparator to vary its threshold to the ideal value, while the second technique adds extra circuits to the comparator.

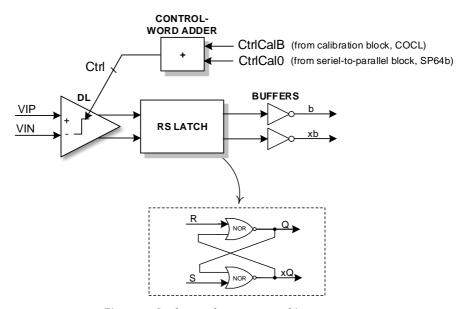

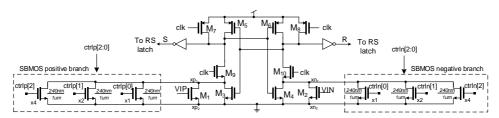

### 3.3.1. DAC-based calibration

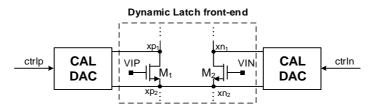

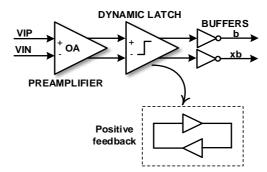

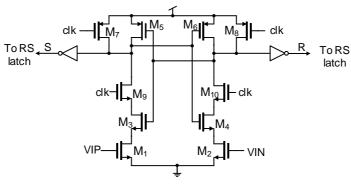

Digital calibration is typically performed by a DAC, as in Figure 3.4. A DAC-based calibration circuit (also called trim-DAC in [38]) is utilized to compensate for the existing mismatch between the two branches of the dynamic latch. The DAC applies an

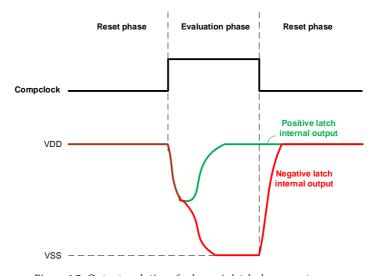

imbalance which is opposite to the actual mismatch, eliminating it. The forced imbalance could be created in several ways, for instance, by varying the current in the branches[47] [56]-[58] or by adding capacitance [59]-[61] to them. Once the proper value for the forced imbalance is generated, the offset in the circuit will be suppressed. DAC is formed of a binary weighted array whose elements are current sources, capacitors or resistors. To control the forced imbalance, each of the elements in the DAC turns ON or OFF with switches that are controlled by the digital input control bits *ctrlp* and *ctrln*, both generated by an algorithm [24]. The full scale range covered by the DAC must be enough to correct the offset [77]. Extra hardware to control the bits is needed. In foreground calibration, DAC control bits could be determined at start-up, while in background the bits are obtained ceaselessly. An advantage of DAC-based background calibration is that the extra digital circuitry required for controlling the DAC control bits works at very low speed during the normal operation of the ADC [77].

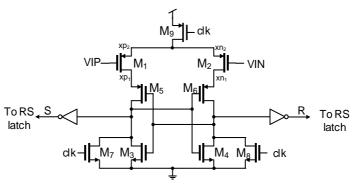

Figure 3.4. Calibration DAC in latch front-end

A dynamic latch using a current source DAC (IDAC) for offset calibration is depicted in Figure 3.5. This simple architecture is similar to those employed in [47] and [57]. IDAC is composed of a bank of binary weighted current sources and switches controlled by the DAC input bits. The DAC is placed in parallel to the input transistors of the latch and injects current through the two comparator branches at the nodes  $xp_1$  and  $xn_1$  to reduce the offset. Work in [58] uses an additional pair of transistors NMOS connected in parallel to the differential input pair of the dynamic latch as well as a charge pump to create a current imbalance to compensate for the offset in high-speed ADCs.

Figure 3.5. Dynamic latch using IDAC

Moreover, a reference ladder could be used to force a current imbalance between the branches of the comparator. Two examples of offset cancelation in flash ADCs are found in [39] and [62]. The proper reference voltage to cancel de offset in the comparator is chosen with switches connected to the resistor array.

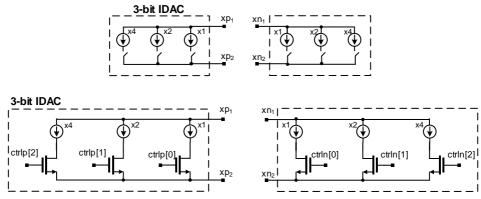

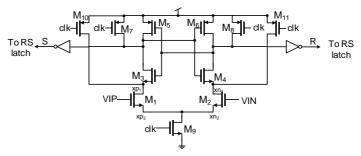

In paper [40] [63] a DAC formed of MOS transistor array (as in Figure 3.6) is placed in parallel to the input transistor of the latch in a time-interleaved flash ADC. DAC is utilized to inject currents through the branches of the latch to calibrate offset in a time-interleaved flash. DAC digital control bits (*ctrlp* and *ctrln*) will increase or decrease to reduce the offset. Also, work [32] applies this method to a flash to cancel the offset.

Figure 3.6. MOS calibration DAC (resistor DAC, RDAC)

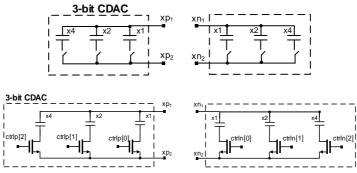

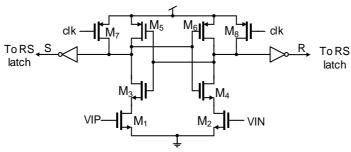

Furthermore, capacitive imbalance could be created by using a capacitive DAC (CDAC), typically compose of a binary weighted capacitor array (see Figure 3.7). The previous architectures consume only static power while CDACs dissipate dynamic power, being the latter less power consuming. Another advantage of CDAC is that they act as a SH, so no SH circuit is required in calibration circuits [64].

A standard CMOS flash ADC with CDAC calibration is presented in [146]. First, the offset must be stored in the MSB capacitor. Then, each comparator stores the offset on

the capacitor while the input voltage is stored in the capacitor bottom-plate, eliminating the offset. Also, [147] and [148] employ a CDAC for fine tuning of the offset in a flash. Further, capacitive imbalance using MOS varactors array is applied to address the offset problems in latches in SAR [60] [65] and flash ADCs [61]. As well as the previous MOS transistor DAC, MOS varactor array is connected to the internal nodes of the latch and the digital control bits control the gate voltage of the varactors. By modifying the DAC control bits, a voltage difference is applied to the latch inputs and the offset shifts. Once the optimum bits are selected, the offset in the comparator is cancelled. MOS varactor DAC has been used in [59] [61] [64] [66]-[68].

Figure 3.7. Capacitive calibration DAC (CDAC)

### 3.3.2. Redundancy

Redundancy consists of including additional comparators in the ADC and activating the proper comparator that reduces the offset of the circuit. This technique does not require error measurement. Since hardware is designed to absorb the errors without the need of measuring them previously, redundancy is a pure digital calibration method.

Consider a N-bit flash ADC with  $(2^N - 1)$  comparators. The same flash with redundancy has  $M \cdot (2^N - 1)$  comparators, with M comparators for each transition. The M comparators have the same topology but different offset. With redundancy, the optimal comparator that provides minimum offset will be selected. The rest of the comparators can be switched off without consuming power, thus being only  $(2^N - 1)$  comparators activated, the same number as in a conventional flash ADC [41]. With the use of redundancy, comparators can be designed without caring of the offset. Notice

that as the number of redundant comparators M increases, the probably of selecting a better comparator raises.

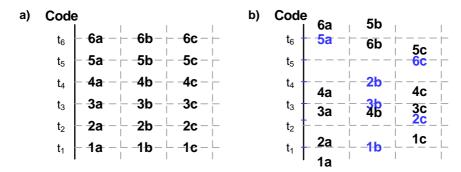

Work [41] applies redundancy to the flash ADC and, with the use of a finite state machine, the comparator which gives the minimum offset is searched for. Figure 3.8 a) shows the ideal thresholds voltages of the comparators and their actual values, which differ from the ideal values due to offset. In second figure, comparators' positions have changed due to the offset. The selected comparators are highlighted in blue colour. For instance, comparator 2a is chosen for code 2 and comparator 3b is selected for code 3. However, comparator 2b, due to its large offset, has been reassigned [42] to code 4. After reassignment, it is unknown which comparator corresponds to each code and comparators output code is no longer thermometric as in conventional flash. Comparators not selected generate a zero output, without affecting to encoder output and a Wallace tree encoder is used to generate the output in order to disengage comparators with codes. Redundancy with the use of reassigning comparators achieves fast comparators and low power consumption even when the offsets are large.

Figure 3.8. a) Ideal threshold voltages of comparators. b) Example of real threshold voltages where reassigned comparators are selected (in blue colour)

Comparator redundancy has been also applied to a flash ADC in [43] and a folding flash ADC in [44]. In [45] an extension of redundancy to cancel the offset in a flash ADC is presented. A statistical element selection methodology based on combinatorial redundancy allows measuring the offset when a certain subset of redundant element is selected, in contrast to conventional redundancy, where only one of the redundant elements is selected. This is a finer calibration than traditional redundancy.

Usually, redundancy is used with DAC-based calibration. For instance, paper [47] proposes a combination between redundancy and current DAC-based calibration to correct the comparator offsets in a flash ADC. This combination achieves small measured offsets and a better resolution and DAC range than using just a DAC to calibrate.

To sum up, redundancy increases the area as extra comparators are needed. However, the devices in comparators can be designed as small as possible, without caring how great the offset is, since using redundancy a great comparator performance is reached. Once the circuit is calibrated, the matching between devices is improved and offset is cancel. Power consumption does not increase with redundancy since the non-selected comparators are at power down.

In SAR ADCs, redundancy is applied to the SAR algorithm, introducing redundancy to the conversion steps. Consider an *N*-bit SAR ADC with one comparator. The algorithm requires more than *N* steps to resolve the *N*-bit output, that is, the algorithm number of steps is redundant. Redundancy in non-binary search algorithm is deeply analysed in [46], proving its benefits in speed when compared to binary search or conventional non-binary algorithm. In order to digitally correct the static nonlinearities in a SAR ADC, work [48] employs a sub-radix-2 redundant architecture where redundancy algorithm sizes the capacitors. Non-binary redundant search has been also used in [49] and in [50] redundancy is incorporated in a tri-level switching algorithm. Further examples of redundancy in SAR ADCs could be found in [51]-[52].

In addition, pipeline ADCs could employ redundancy. Redundancy in pipeline ADC consists of having in each stage a resolution of *N*-bit and a single bit redundancy for a comparator offset correction algorithm. With this single bit redundancy, the accuracy of each stage could be relaxed. A single bit redundancy has been used in [53]-[54]. Also, the redundancy algorithms employed in SAR and Pipeline ADCs are analysed in [55], comparing their results to that of half-bit redundancy.

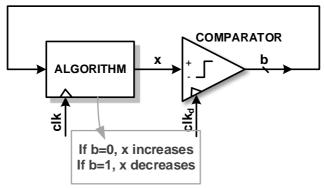

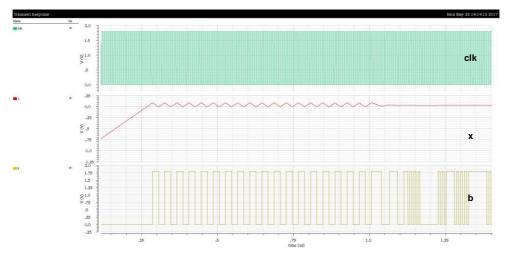

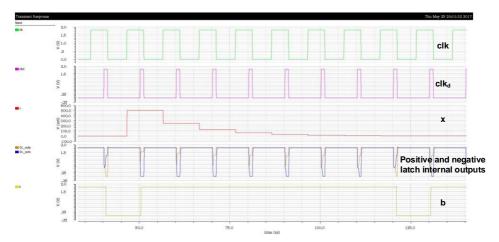

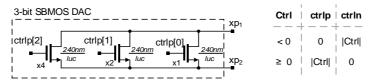

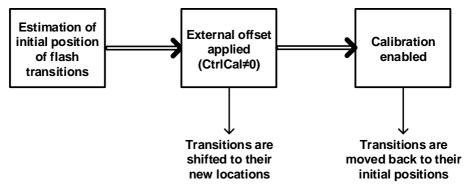

# 3.4. Applied Solution: Adaptive Digital Background Calibration

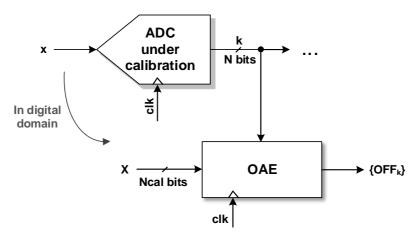

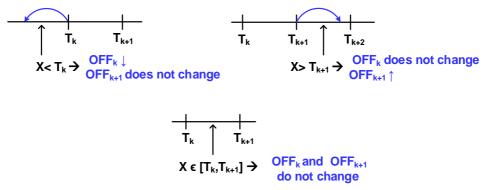

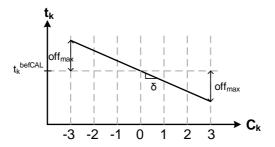

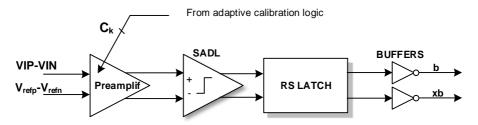

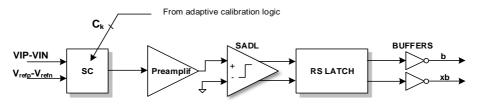

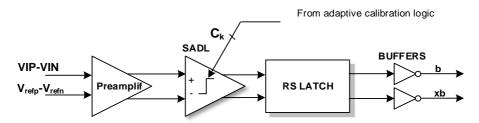

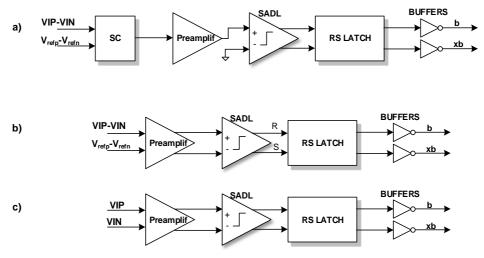

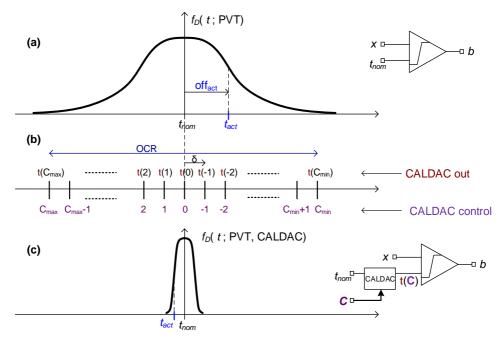

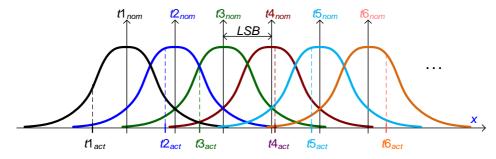

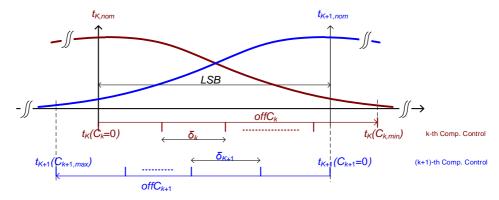

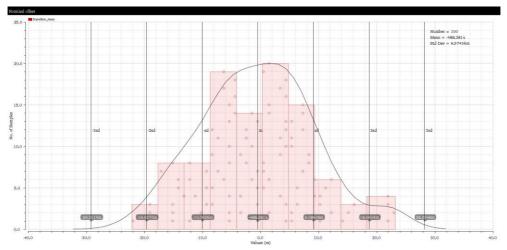

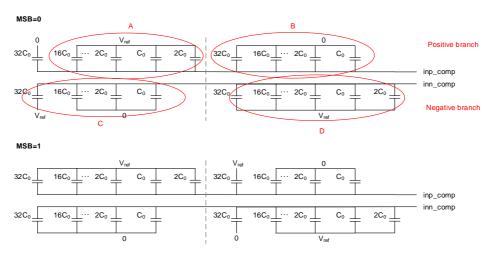

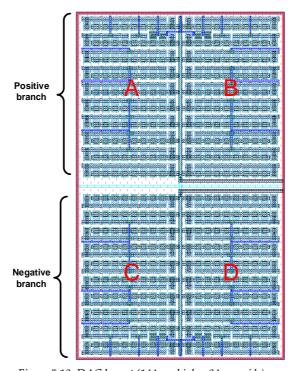

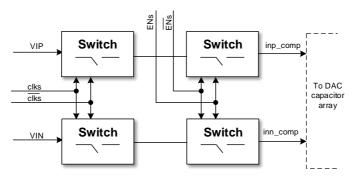

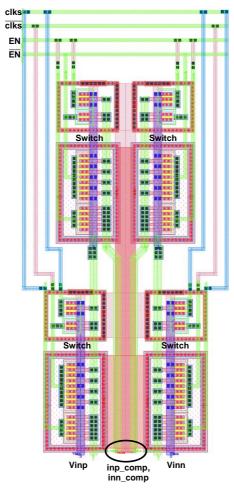

One of the main goals of this thesis is to prove that background calibration using the adaptive algorithm proposed in paper [105] is a low-cost, stable and effective method