1

# A procedure for Alternate Test feature design and selection

Manuel J. Barragan, and Gildas Leger

Abstract-Testing analog, mixed-signal and RF circuits represents the main cost component for testing complex SoCs. A promising solution to alleviate this cost is the Alternate Test strategy. Alternate test is an indirect test approach that replaces costly specification measurements by simpler signatures. Machine learning techniques are then used to map circuit signatures and circuit specifications. One key point that still remains as an open problem is the conception of adequate simple measurement candidates. This work presents efficient algorithms for selecting information rich signatures, and for designing new ones that will improve the prediction accuracy.

Index Terms-Alternate Test, machine learning, feature selection, feature design.

# I. INTRODUCTION

N OWADAYS, commercial trends of IC industry have forced the integration of acres in C. forced the integration of complex SoCs consisting of tightly integrated analog, mixed-signal, RF and digital circuitry onto a single IC substrate. This high integration level provides a significant reduction in production cost, but increases the cost of testing these devices.

Cost-effective methods for testing the digital parts of these SoCs, based on standardized fault models, are already available. However, testing Analog, Mixed-Signal and RF circuits (AMS-RF circuits) still relies on costly functional characterization. The main reason for this difference is the mathematical complexity of the problem. Digital circuits can be studied from a high level of abstraction, that allows to isolate parts of the circuit from their surroundings. The problem of AMS-RF circuits is by far more intricate. Firstly, all involved signals and states are continuous variables affected by many sources of variability, either static (like process variations) or dynamic (like noise sources). Correctness can only be defined in terms of intervals or regions. Moreover, the relation between signals and states is usually non-linear and multidimensional. Even possible defects should be considered as continuous variables, which makes standardization of fault models a challenging task.

Alternate Test, proposed by researchers at Georgia Tech [1], is a promising strategy for overcoming these issues. It leverages the power of machine-learning algorithms to interpret simplified tests in the specification domain.

# II. ALTERNATE TEST: BACKGROUND AND OPEN PROBLEMS

Alternate Test is an indirect testing framework. Conventional production test measurements are replaced by a set of

Manuel J. Barragan is with TIMA Laboratory, CNRS-Université Grenoble-Alpes, France.

Gildas Leger is with Instituto de Microlectrónica de Sevilla, IMSE-CNM-CSIC-Universidad de Sevilla, Spain.

low-cost indirect signatures, and test results are inferred by post-processing these signatures.

The usual approach to perform this replacement is based on supervised machine learning algorithms. The test process is developed in two stages: a learning stage and a testing stage. During the learning stage both circuit specifications and signatures are measured from a set of training devices. A machine learning algorithm is then trained over the two sets of measurements to build a mapping model. In the testing stage, only signatures are measured for each Device Under Test (DUT), and specifications are inferred by using the obtained mapping model.

A key issue of Alternate Test is the definition of the input space of signatures. On one hand, it is clear that we need information-rich signatures sensitive to the performance degradation mechanisms affecting the DUT. On the other hand, due to the model oriented philosophy of Alternate Test, any non-modeled errors may lead to unexpectedly bad results [2]. Hence, the input signature space must be designed to cover as much relevant information as possible, and any source of nonmodeled errors should be screened from the training. A typical example of the latter case corresponds to spot defects, that are in essence different from process variations. This motivated the introduction of defect filters [3] to identify outliers that do not fit the expected distribution of the signatures.

The current approach for designing signatures heavily relies on the expertise of the designer. Some generic approaches exist for providing an initial set of signatures, such as DC probing,  $I_{DDO}$  test, V-transform coefficients [4], process monitoring [5], etc. Work has been also presented on optimizing a particular stimulus to define optimized signatures [1], [6]. However, despite the demonstrated feasibility of these techniques, none of them guarantee a complete coverage of all possible performance deviations. To our knowledge, there is no generic method to guide the design of new signatures to systematically cover all the relevant circuit information.

In this work we propose a method to infer new signatures to enrich the information in the feature input space. The proposed methodology is a combination of feature selection and guided feature design. These two points, together with their application to a case study, are presented in the following sections.

#### **III. FEATURE SELECTION**

# A. Proposed approach

Feature selection can be defined as the process of selecting a subset of relevant features for building an accurate regression model. It is a recurrent problem in machine learning, and has been addressed by numerous researchers. It is out of the scope of this paper to produce a full review, but interested readers can refer to [7] for an excellent introduction.

Statistics almost always address feature selection from the viewpoint of overfitting reduction. In the particular application case of IC testing, though, there is a specific additional concern: the feature cost. Any additional signature is a measurement that has to be performed in production.

A direct approach to feature selection consists in preselecting a subset of features, based on some statistical observations, before training any regression models. This approach, widely used when the number of initial features is high, is known as filtering.

The most common filtering approach is the Principal Component Analysis (PCA). PCA considers a linear input space and performs an eigenvalue decomposition of the features covariance matrix to identify the principal directions, or components, of the variability in the space of signatures.

One of the main drawbacks of PCA is the fact that it is a linear method, while the relation between signatures may be non-linear. PCA is also an unsupervised method, that is, it does not make use of the performance information for signature selection. In this work we propose a methodology that takes into account the intrinsic non-linearity of the space of signatures and the non-linear mapping to the performance space by incorporating model training to the selection algorithm. This methodology is known as a wrapper approach [8].

The wrapper approach consists in using the machinelearning prediction model as a black box within an optimization loop. The model is used to evaluate the prediction error (also called generalization error) for a given signature subset, and the optimization loop tries to minimize this error by adding or removing signatures to this subset (more complex cost functions that consider the cost of each signature are also possible). The interested reader is referred to [7], [8] for a comprehensive description of the wrapper technique. In practice, a wrapper consists of three elements: a search algorithm to explore the space of features, a machine learning algorithm to evaluate the prediction error for each subset of features, and a stopping criterion.

Regarding the search algorithm, we opted for a stepwise search with compound operators, as described in [8]. This approach is based on a combination of stepwise forward addition and backward elimination operators. Starting from an initial subset of signatures, we explore all the possible children obtained by removing one existing signature or adding a new one. Up to this point, this is very similar to what was proposed in [9], but at the end of this one-change exploration, we also explore the combinations of the four children that give best results. This can significantly speed-up the exploration.

Concerning the machine learning model in the wrapper, we use a perceptron neural-network from the ENTOOL MATLAB toolbox [10]. An ensemble model is created in a classical cross-validation fashion by splitting the available data into random subsets. A detailed description of the ensemble learning algorithm and the cross-validation strategy can be found in [10], [11]. Apart from the total prediction error, we get access

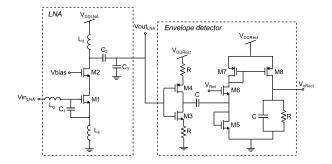

Fig. 1. Schematic view of the LNA with envelope detector

to the individual errors of the random partitions. The standard deviation of these errors gives an estimate of the confidence in the obtained prediction error.

As an arbitrary stopping criterion for the search, we consider that the generalization error improvement for a new iteration should be higher than 25% of the standard deviation estimate. An important remark in this strategy is that it is important to set aside a verification set that is not involved in the optimization loop. If not, the optimization process will optimize for this particular set. At some point, due to the finite sample size of the set, it would be possible to fit the data with random variables. We need an out-of-the-loop criterion to verify that we are not overfitting. We implemented a sanity check consisting in monitoring the model performance on an out-of-the loop verification set, to confirm that the prediction error for this set also improves.

# B. Case study: RF Low Noise Amplifier

In order to exemplify the application of the proposed feature selection technique, we have applied it to an Alternate Test strategy for predicting the gain of an RF LNA. LNAs are simple circuits with very few components, but that are quite sensitive to process variability. The variability is important to make the prediction more challenging. On the other hand, limiting the discussion to the prediction of a single performance –the LNA's gain in this case– facilitates the interpretation of the results, although the method is easily applicable to any number of target performances.

Figure 1 shows the schematic of the LNA, which has been designed in a 90nm CMOS technology. The envelope detector at the output of the LNA has been included as a built-in test instrument [12].

Our initial set of signatures in this case study contains 42 signatures, consisting in the DC voltages in all the nodes of the LNA, the output of the envelope detector, and all the previous signatures measured under power supply stress. A population of 2000 instances of the LNA was generated using Monte Carlo simulation. We set aside 10% of the data for the verification set, which represents 200 samples, and we use the remaining 1800 samples for training. 15 random partitions of the training samples are used for cross-validation.

As a first application of the feature selection method, we consider four different scenarios to predict the gain of the LNA:

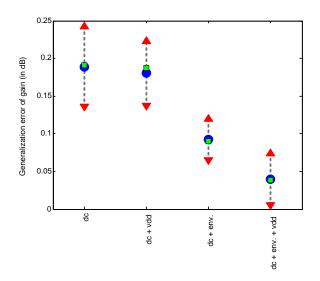

Fig. 2. Generalization error on the prediction of the LNA gain, for four different training scenarios

- only DC signatures

- DC signatures and envelope detector

- DC signatures with power supply stress

- DC signatures and envelope detector with power supply stress

Figure 2 displays the results obtained for the four scenarios. The round marker shows the expected generalization error from the ensemble model scheme while the square marker stands for the error obtained on the verification set. In all cases, we verify that this error is within the  $3\sigma$  confidence interval.

It can be observed how the use of power supply stress to augment the information fails to improve significantly the model if only DC signatures are considered. However, this is not true when the envelope detector is considered. In this case, the gain error improves from 0.09dB to 0.04dB, approximately.

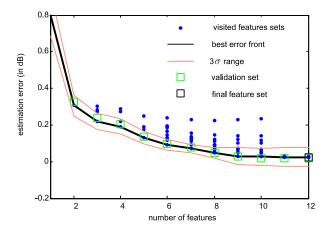

Figure 3 shows all the visited feature combinations for the four scenarios, in a scatterplot of the generalization error versus the number of features in the training set.

The optimum fronts for the different scenarios provide interesting information. Thus, in the case of DC signatures with supply stress, the model with the lowest error uses four features, but a model with three features gives almost the same prediction error, so the additional feature is probably not costeffective. Similarly, for the most complete scenario the best model uses 11 features. However, the last steep improvement occurs when going from 6 to 7 features. Is a slight error improvement worth the introduction of 4 features? This is a matter of cost optimization.

In the view of the obtained results after feature selection, we can conclude that the DC signatures alone, even with the addition of power supply stress, are missing some important information to perform a good prediction of the LNA gain. When adding the envelope detector, a much better prediction is obtained but we can still wonder if the information is complete. This is the question we pretend to answer in the next section.

Fig. 3. Generalization error versus number of features, for all of the visited cases of the four different training scenarios

#### IV. GUIDED FEATURE DESIGN

#### A. Proposed approach

A guided feature design strategy has the objectives of identifying relevant information missing from a given set of signatures and proposing new signatures for covering that information.

The cornerstone of Alternate Test is that circuit signatures and specifications are tightly correlated through a non-linear mapping function. The justification for this affirmation is that there is a unique underlying stochastic process – the fabrication process– that affects the signatures and causes performance fluctuation. Then, if process variations are the root cause of both signature and performance variations, they are the perfect candidates for diagnosis. However, in a real fabrication process, we hardly have access to all the physical parameters. On the other hand, the real fabrication process is already modeled in most design kits and we do have access to the process parameters at simulation level: this is the base of Monte Carlo process simulation. The Monte Carlo variables can then be traced back to actual physical components in the DUT thanks to the models of transistors and passive elements.

We propose to explore the set of Monte Carlo variables as if they were additional signatures that we could add to our initial set of signatures for training regression models. Since the process parameters are independent random variables, we can simply perform stepwise addition. Starting from the best available signature subset, we train a regression model and evaluate the model performance adding one process parameter at a time, include the best candidate in the test list, and iterate. In that case, we would be able to identify which Monte Carlo variables bring significant additional information with respect to the already available signatures.

This methodology can be easily extended to complex SoCs. We can perform a system-level diagnosis search including higher-level parameters for each building block in the system. For instance, if the circuit contains an amplifier, we could perform Monte Carlo simulations to retrieve its gain, bandwidth, slew-rate, etc. at a small computational cost. These high-level

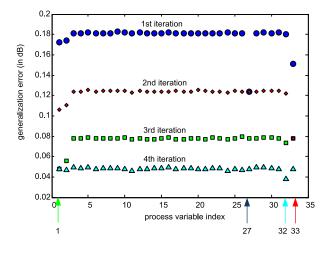

Fig. 4. Generalization error versus number of process variables, for all of the visited cases during the optimization search

parameters can be also included in the search list to guide the design of new features.

The final step of the procedure consists in designing simple tests that target the selected parameters in the DUT, in order to add the identified missing information to the regression. Obviously, this final step still depends on the expertise of the designer but the diagnosis of the most important variation causes does bring significant information: identified signatures are those that bring relevant *additional* information.

As commented in the introduction, different strategies for test generation have been proposed. The value of the proposed procedure for guided feature design is to help the designer to go beyond an available set of initial features selected among these tests by proposing new ones.

# B. Case study: RF Low Noise Amplifier

Going back to our LNA case study, after feature selection we were able to obtain good predictions for its gain, while reducing the number of necessary measurements. But the question of completeness still remains: could we add new signatures in order to improve the predictions even more? Is there non-modeled information? In order to explore these questions, this section revisits our LNA case study from the point of view of the proposed strategy for guided feature design.

Firstly, in order to get an intuitive insight into the information contained into the Monte Carlo variables, we perform our feature selection search over the 33 process variables that are defined in the design kit of the selected 90nm CMOS technology. After 9 iterations, we end up with a reduced model of 12 process variables and a generalization error of 0.024dB, as can be seen in Figure 4.

This error value is significantly lower than that obtained with DC signatures, and lower than that obtained including the envelope detector with power supply stress. These feature sets can thus be improved if we are able to design specific tests that target the missing information.

In order to diagnose which parameters should be identified, we perform a stepwise addition of the 33 process parameters.

Fig. 5. Generalization error for stepwise addition of process parameters, starting from the DC signatures with supply stress.

For this example, we consider as initial set of signatures the best feature set from the DC signatures with supply stress (corresponding to the second case in Figure 2).

Figure 5 shows the generalization errors obtained by adding one process parameter, for four iterations. At the fourth iteration, we see that the improvement is marginal. As a result of this procedure, we can identify three Monte Carlo process variables –labelled 1, 27, and 33 in Fig. 5– that bring significant additional information. By tracing back these process variables to the physical models of the devices in the design kit, we found out that our algorithm pointed at metal-insulatormetal capacitors, polysilicon resistors, and RF inductors as non-modeled information. This result is coherent with an electrical analysis of the DUT: our initial set of signatures was composed by DC levels, so parametric variations of capacitors and inductors would not have been detected, leading to nonmodeled information in our regression.

The next step to improve our regression is then to design new tests to target these components. In this example we rely on Process Monitors for this purpose. These structures mimic selected parts of the DUT and are located in the close proximity of the replicated sections, in such a way that process variations affect both structures in a similar way [5].

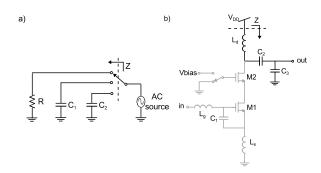

Thus, we replicate capacitors  $C_1$  and  $C_2$  (capacitor  $C_3$  is equal to  $C_2$ ), and resistor R in the arrangement shown in Fig. 6a. An external low-frequency AC source is used at the input of each monitor circuit for measuring its impedance.

This methodology, however, is not appropriate for characterizing the effect of process variations across the inductors in the LNA, given that replicating inductors  $L_g$ ,  $L_s$ , and  $L_d$ would result in an excessive area overhead. Instead of that, we propose to use the arrangement depicted in Fig. 6b. In this test set up the signal path in the LNA is broken by switching off the cascode transistor M2. An external AC source can then be used to characterize the impedance seen from the  $V_{DD}$  node, which is a function of the inductance value of  $L_d$ .

With these simple low-cost tests, we get four additional signatures. Including these new signatures, we then re-run the optimization process from scratch for the same four scenarios

Fig. 6. a) R and C monitors; b) Test set-up for detecting inductance variations

as in figure 2. Table I shows a summary of the past and new results.

In all scenarios, the introduction of passive signatures greatly improves the obtained prediction error. In particular, it is worth noticing that with the complete set of signatures a precision of 0.025dB is achieved, which is similar to the limit obtained by regressing directly from the process variables. The best improvement is observed for the case of DC signatures with supply stress, which lowers the prediction error from 0.18dB to 0.042dB. This precision is comparable to what was obtained with the envelope detector and the supply stress, but without the need of any BIST circuitry.

# V. CONCLUSIONS

This work proposes simple generic methodologies for the selection of information rich features and for guiding the design of relevant new features. Both methodologies allow to optimize Alternate Test programs at design level.

The proposed selection and design algorithms have been validated in a RF LNA case study to demonstrate its feasibility. Obtained results show a clear potential of the proposed techniques to improve the quality of the input space of signatures in an Alternate Test program.

# ACKNOWLEDGMENT

This work has been partially funded by the Andalusian Government project P09-TIC-5386, co-funded with FEDER program.

# REFERENCES

- R. Voorakaranam, S. S. Akbay, S. Bhattacharya, S. Cherubal, and A. Chatterjee, "Signature testing of analog and RF circuits: Algorithms and methodology," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 5, pp. 1018–1031, 2007.

- [2] G. N. Stenbakken, "Effects of nonmodel errors on model-based testing," *IEEE Transactions on Instrumentation and Measurement*, vol. 45, no. 2, pp. 384–388, 1996.

- [3] H.-G. Stratigopoulos, S. Mir, E. Acar, and S. Ozev, "Defect Filter for Alternate RF Test," in *European Test Symposium*, May 2009, pp. 101– 106.

- [4] S. Sindia and V. D. Agrawal, "High Sensitivity Test Signatures for Unconventional Analog Circuit Tests Paradigms," in *International Test Conference*, 2013.

- [5] A. Zjajo, M. J. Barragan, and J. P. de Gyvez, "BIST Method for Die-Level Process Parameter Variation Monitoring in Analog/Mixed-Signal Integrated Circuits," in *Design Automation and Test in Europe*, 2007.

- [6] A. Halder, S. Bhattacharya, and A. Chatterjee, "Automatic multitone alternate test generation for RF circuits using behavioral models," in *International Test Conference*, 2003.

- [7] I. Guyon and A. Elisseeff, "An introduction to variable and feature selection," *Journal of Machine Learning Research*, vol. 3, Mar. 2003.

- [8] R. Kohavi and G. H. John, "Wrappers for feature subset selection," Artificial intelligence, vol. 97, no. 1, 1997.

- [9] H.-G. Stratigopoulos and Y. Makris, "Nonlinear decision boundaries for testing analog circuits," *IEEE Transactions on Computer-Aided Design* of Integrated Circuits and Systems, vol. 24, no. 11, pp. 1760–1773, 2005.

- [10] J. D. Wichard, M. J. Ogorzalek, and C. Merkwirth, "Entool-a toolbox for ensemble modelling," in *Europhysics Conference Abstracts*, vol. 27, 2003.

- [11] T. Hastie, R. Tibshirani, and J. Friedman, *The elements of statistical learning: data mining, inference, and prediction.*, 2nd ed. Springer, 2009.

- [12] M. Barragán, R. Fiorelli, G. Leger, A. Rueda, and J. Huertas, "Alternate Test of LNAs Through Ensemble Learning of On-Chip Digital Envelope Signatures," *Journal of Electronic Testing*, vol. 27, no. 3, pp. 277–288, 2011.

**Manuel J. Barragan** received a Ph. D. degree in Microelectronics 2009 from the University of Seville, Spain. Nowadays, he holds a position of Collaborateur Expert at TIMA Laboratory, Grenoble, France. His research is focused on the topics of test and design for testability of analog, mixed-signal, and RF systems. *e-mail*: manuel.barragan@imag.fr

**Gildas Leger** received a Ph.D. degree in Microelectronics from the University of Sevilla, Spain, in 2007. He is currently holding a position of Tenured Scientist at the Instituto de Microelectrnica de Sevilla (IMSE, CNM), Spain. His research focuses on design for testability in the domain of analog to digital conversion. *e-mail*: leger@imsecnm.csic.es

TABLE I

SUMMARY OF THE BEST FEATURE SETS RESULTS

| Feature space             | Prediction error<br>(in dB) | $\sigma_{Err}$ (in dB) | Verification set error<br>(in dB) | $n_{feature}$ | Reductior<br>factor |

|---------------------------|-----------------------------|------------------------|-----------------------------------|---------------|---------------------|

| DC                        | 0.189                       | 0.018                  | 0.191                             | 8             | -                   |

| DC + vdd                  | 0.180                       | 0.014                  | 0.187                             | 4             | -                   |

| DC + env.                 | 0.092                       | 0.009                  | 0.090                             | 9             | -                   |

| DC + env. + vdd           | 0.040                       | 0.011                  | 0.039                             | 11            | -                   |

| Process Variables         | 0.024                       | 0.017                  | 0.019                             | 12            | -                   |

| DC + passive              | 0.065                       | 0.011                  | 0.066                             | 12            | 2.9                 |

| DC + vdd + passive        | 0.042                       | 0.014                  | 0.036                             | 9             | 4.3                 |

| DC + env. + passive       | 0.030                       | 0.014                  | 0.027                             | 11            | 3.1                 |

| DC + env. + vdd + passive | 0.025                       | 0.014                  | 0.022                             | 13            | 1.6                 |