# Bifurcation Diagrams in MOS-NDR Frequency Divider Circuits

Juan Núñez, María J. Avedillo, and José M. Quintana

Instituto de Microelectrónica de Sevilla-Centro Nacional de Microelectrónica Consejo Superior de Investigaciones Científicas (IMSE-CNM-CSIC), Univ. de Sevilla (US) jnunez{avedillo, josem}@imse-cnm.csic.es

Abstract— The behavior of a circuit able to implement frequency division is studied. It is composed of a block with an *I-V* characteristic exhibiting Negative Differential Resistance (NDR) built from MOS transistors plus an inductor and a resistor. Frequency division is obtained from the period adding sequences which appear in its bifurcation diagram. The analyzed circuit is an "all MOS" version of one previously reported which use Resonant Tunneling Diodes (RTDs) The results show that the dividing ratio can be selected by modulating the input signal frequency, in a similar way to the RTD-based circuit.

#### I. INTRODUCTION

Non-autonomous, very simple frequency divider circuit based on the period-adding bifurcation sequences which appear in an RTD chaos circuit have been reported in the past few years [1], [2], [3], and experimental results have been obtained, showing that the phase noise is comparable to that of conventional dividers. These circuits exploit the NDR region in the RTD I–V characteristic to obtain autonomous nonlinear oscillators and, in general, extremely complex behaviors with applications in diverse fields. Additionally, when an external periodic excitation signal is used, such circuits exhibit an increased variety of bifurcations sequences.

The basic block for these circuits is the RTD, which consists of an emitter and a collector region and a double tunnel barrier structure. This contains a low-bandgap narrow quantum well, which allows electrons to travel through only at the resonant energy level. The thickness of the barrier layers as well as the width of the well are in the nanometer range. The RTD *I–V* characteristic presents a typical *N*-shape with two positive differential resistance (PDR) and one NDR zones. Most of the reported working circuits have been fabricated in III/V materials and require a technological process usually expensive and difficult to compatibilize with MOS processes. In this paper we show an NDR device made

from MOS transistors that can be used to design a frequency divider circuit which operation is based on the same principle as the RTD.

#### II. THE MOS-NDR STRUCTURE

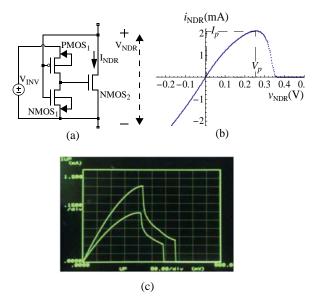

Figure 1a shows the structure of the MOS-NDR device we have used, which is based on the circuits described in [4]. It consists of one CMOS inverter, made up by NMOS<sub>1</sub> and PMOS<sub>1</sub> and biased by  $V_{\rm INV}$ , and one NMOS transistor (NMOS<sub>2</sub>) whose gate-to-source voltage is modulated by the output voltage of the CMOS inverter. Figure 1b shows the simulated current-voltage characteristic of the MOS-NDR device for transistor parameters given by  $W_{PMOS,1} = 0.16 \mu m$ ,  $W_{NMOS,1} = 2 \mu m$ , and  $W_{NMOS,2} = 5.4 \mu m$ ; channel length for all of them is  $0.12 \mu m$ . For this case, the peak current ( $I_p$ ) is 2.11 mA for a peak voltage ( $V_p$ ) of 0.25 V. Both, the PDR and the NDR zones of the I-V characteristics are obtained through the current of the NMOS<sub>2</sub> transistor.

Figure 1: (a) MOS-NDR device, (b) I-V characteristic, (c) Measured I-V characteristics.

This work has been partially supported by the Spanish Government under projects TEC2007-67245/MIC and P07-TIC-02961.

The peak voltage and current of the *I–V* characteristic in Figure 1b can be modified by setting up properly the sizes of the transistor. In this way,  $I_p$  is increased with the width of NMOS<sub>2</sub>. Assuming that all transistors have the same gate length, the position of  $V_n$  is controlled by the ratio between the widths of NMOS1 and PMOS<sub>1</sub>. In this way, higher values of  $V_p$  are obtained by decreasing the ratio  $W_{NMOS, 1}/W_{PMOS, 1}$ . Additionally, we can obtain higher peak current values by increasing  $V_{\text{INV}}$  [5]. Compared to the RTD device, the I-Vcharacteristic in the MOS-NDR device lacks the second PDR zone and presents a typical  $\Lambda$ -shape. Figure 1c depicts the I-V characteristic, measured by a HP-4145A parameters analyzer, of a MOS-NDR which we have designed and fabricated in a standard commercial 0.13µm CMOS process.

### III. ANALYSIS OF THE FREQUENCY DIVIDER.

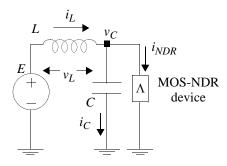

The circuit topology used for the frequency divider is shown in Figure 2. It is composed of an inductor L in series with the parallel of the MOS-NDR device (the  $\Lambda$  device) and one capacitor C. It is driven by an external periodic excitation signal E, with a DC bias  $E_{DC}$ , an amplitude  $E_A$ , and a frequency f ( $E = E_{DC} + E_A \sin[2\pi ft]$ ).

By applying Kirchoff's laws to this circuit, the equations for the voltage  $v_C$  across the capacitor C and the current  $i_L$  through the inductor L are given by the following set of two first-order coupled non-autonomous differential equations:

$$\begin{vmatrix} \frac{dv_C}{dt} = \frac{1}{C}(i_L - i_{RTD}) = \frac{1}{C}[i_L - G(v_C)] \\ \frac{di_L}{dt} = \frac{1}{L}(E - v_C) \end{vmatrix}$$

(1)

where  $G(\cdot)$  is the mathematical representation of the driving point characteristic of the MOS-NDR device. The system is non-autonomous due to the explicit de-

Figure 2: Frequency divider circuit using a MOS-NDR device ( $\Lambda$ -device).

pendence of time t in the expression for excitation signal E, and periodic with period T=1/f. If we choose  $E_M$  and  $I_M$  as scale parameters with physical dimensions of voltage and current, respectively, and rescale  $v_C = xE_M$ ,  $i_L = yI_M$ ,  $t = \tau\sqrt{LC}$ ,  $E_{DC} = \Gamma E_M$ ,  $E_A = \nu E_M$ , and  $f = \omega/\sqrt{LC}$ , then variables  $x, y, \omega$ , and  $\tau$  will be dimensionless. Redefining now  $\tau$  as t, the following set of normalized equations are obtained:

$$\begin{cases} \dot{x} = \frac{1}{\varepsilon} [y - g(x)] \\ \dot{y} = \varepsilon \left[ \Gamma + v \cdot \sin(2\pi\omega t) - x \right] \end{cases}$$

(2)

where  $\varepsilon=(E_M/I_M)\sqrt{C/L}$  and  $g(\cdot)$  come from the normalization of  $G(\cdot)$ . The dynamics of Eq. (2) now depends on parameters  $\varepsilon$ ,  $\Gamma$ ,  $\nu$ , and  $\omega$ . As the circuit is periodically driven, planes t=0 and  $t=1/\omega$  can be identified, and the 3D Euclidean phase space (x,y,t) can be transformed into the cylindrical space  $(x,y,\theta)\in R^2\times S^1$  [6] by defining the new variable  $\theta=2\pi\omega t$  which transforms the non-autonomous system of Eq. (2) into an autonomous one, now with three equations, by adding  $\theta=2\pi\omega$ . In this space, time turns around the unit circle  $S^1$ , x is represented in the horizontal axis of the cylinder and y in the vertical one.

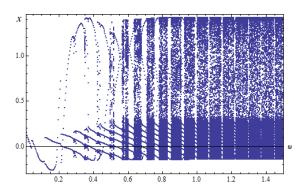

The dynamics of Eq. (2) has been extensively studied for different parameter values. By fixing  $\varepsilon$ ,  $\Gamma$ , and  $\nu$ , the frequency of the external periodic signal has been used as the control parameter, and numerical integration using an adaptive-step Runge-Kutta algorithm has been carried out to build one-parameter bifurcation diagrams in the  $(\omega - x)$  plane. These diagrams plot the normalized output voltage x sampled at a fixed phase of the normalized input signal for each normalized frequency ω, and solutions during the first 60 periods of the input signal have been discarded to avoid transient behaviour. Figure 3 shows a typical bifurcation diagram for the circuit computed when the normalized frequency  $\omega$  is swept in the range (0.01,1.5) with the following values for the remaining parameters:  $\varepsilon = 2$ ,  $\Gamma = 0.3$ , and  $\nu = 0.4$ . In circuit parameter values, this could correspond, among other possible set of values, to C = 4pF,  $L = 1\mu H$ ,  $E_M = 1V$ ,  $I_M = 1mA$ ; an external periodic signal with  $E_{DC} = 0.3 \text{V}$ ,  $E_A = 0.4 \text{V}$ , and a frequency between 10MHz and 1.5GHz. The MOS-NDR device is biased in the negative resistance region and a swing is applied. In this bifurcation diagram two kinds of regions are identified: those with a continuum of points for a given value of ω, where the behaviour is quasi-periodic or chaotic, and regions with a finite number of points, where a periodic solution with a period which is a multiple of the driving signal is found.

Figure 3: Bifurcation diagram for circuit in Figure 2 ( $\epsilon = 2$ ,  $\Gamma = 0.3$ , and  $\nu = 0.4$ )

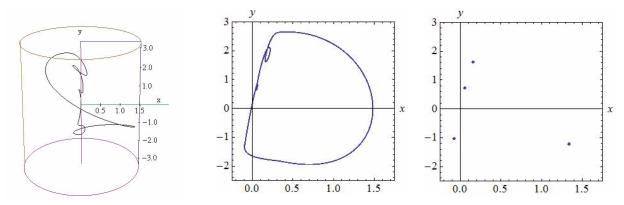

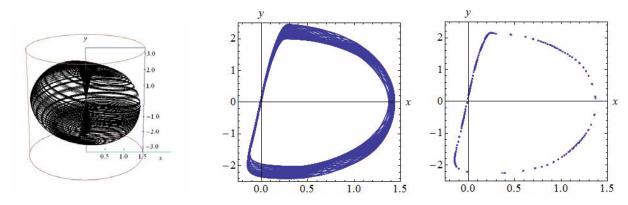

From Figure 3, the solution is a periodic orbit with a period equal to the one of the driving signal for up to  $\omega \approx 0.12$ . From this until  $\omega \approx 0.21$ , the period of the solution is the original one divided by 2. Then, until  $\omega \approx 0.28$ , the division is by 3. For  $\omega > 0.30$ , frequency-locking states of variable period which are separated by quasi-periodicity regions are obtained. Additionally, it is interesting to note that the number of branches in the periodic windows increases when the frequency increases: this behaviour is known as period-adding bifurcations [7]. In these frequency-locking regions we can obtain frequency division from the driving signal, with the division factor being the number of points in such a regions. Thus, between  $\omega \approx 0.30$  and  $\omega \approx 0.35$  the frequency-locking state has period-4, for  $0.37 \le \omega \le 0.42$ has period-5, period-6 for  $0.44 \le \omega \le 0.50$ , etc. Over  $\omega \approx 1$ , the bifurcation diagram is mainly formed by regions of quasi-periodicity. Examples of numerical results for  $\omega = 0.32$  (period 4) and  $\omega = 0.64$  (quasiperiodic behaviour) are shown in Figure 4 and Figure 5, respectively. In particular, a period-4 trajectory in the cylindrical space is shown in Figure 4a, while Figure 4b plots this trajectory in plane (x-y), and the corresponding Poincaré map with four points is shown in Figure 4c. The quasi-periodic trajectory motion for  $\omega = 0.64$  is on the surface of the torus shown in Figure 5a (cylindrical space). Figure 5b shows such a trajectory in plane (x - y). Figure 5c shows the corresponding Poincaré section, which is composed of an infinite set of points which belong to an invariant closed curve, which is typical in a quasi-periodic behaviour.

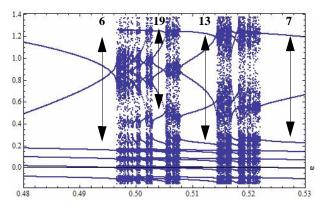

In addition to the period-adding sequences, Figure 3 also shows that periods of some of the windows satisfy the Farey sequence [8]. Between the period- $\alpha$  and period- $\beta$  windows, there exists a period- $(\alpha+\beta)$  window. Some examples of such Farey sequences in the bifurcation diagram of Figure 3 are shown in Figure 6: when the input normalized frequency  $\omega$  increases in the range

$0.45 \le \omega \le 0.53$  (period-6 to period-7), we find a frequency locked window of period-13 (=6+7) in the region  $0.508 \le \omega \le 0.514$ . Farey sequences also appear when finer regions are considered, as is also shown in Figure 6, where a period as high as 19 (6+13) appears in the region  $0.503 \le \omega \le 0.505$ . Finally, we have also performed some simulations to confirm our previous theoretical study. Figure 7 shows the obtained results for the circuit parameters in Section III ( $C = 4 \mathrm{pF}$ ,  $L = 1 \mathrm{\mu H}$ ,  $E_M = 1 \mathrm{V}$ ,  $I_M = 1 \mathrm{mA}$ ,  $E_{DC} = 0.3 \mathrm{V}$ , and  $E_A = 0.4 \mathrm{V}$ ). Figure 7a shows a division by 3 of a external periodic signal of frequency 125MHz ( $\omega = 0.25$ ), and Figure 7b the division by 5 of a signal which frequency is  $10 \mathrm{MHz}$  ( $\omega = 0.38$ ).

#### IV. CONCLUSIONS

We have shown an "all-MOS" device with an I-V characteristic exhibiting NDR which can be used to build a frequency divider. One difference with previously reported RTD-based circuits is the possibility of using a simple MOS process for its implementation. In an analog way to these previous circuits, the frequency division is also obtained from the period adding sequences which appear in its bifurcation diagram. Additionally, we have shown the Farey sequences which appear in the dynamic behavior of the circuit.

## References

- [1] Y. Kawano, Y. Ohno, S. Kishimoto, K. Maezawa, and T. Mizutani, "50 GHz frequency divider using resonant tunnelling chaos circuit," *IEE Electronics Letters*, Vol. 38, no. 7, pp. 305-306, 2002.

- [2] Y. Kawano, Y. Ohno, S. Kishimoto, K. Maezawa, T. Mizutani, and K. Sano, "88GHz dynamic 2:1 frequency divider using resonant tunnelling chaos circuit," *IEE Electronics Letters*, Vol. 39, no. 21, pp. 1546-1548, 2003.

- [3] J.M. Quintana and M.J. Avedillo, "Analysis of frequency divider RTD circuits," *IEEE Trans. on Circuits and Systems I: Regular Papers*, vol. 52, no. 10, 2005, pp. 2234-2247.

- [4] C. Wu, and K.-N. Lai, "Integrated Λ-type differential negative resistance MOSFET device", *IEEE J. Solid-State Circuits*, Vol. SC-14, pp. 1094-1101, Dec. 1979.

- [5] W.-L. Guo, "CMOS-NDR transistor", 9th International Conference on Solid-State and Integrated-Circuit Technology, (ICSICT), pp. 92-95, Oct. 2008.

- [6] T. S. Parker and L. O. Chua, Practical Numerical Algorithms for Chaotic Systems. New York: Springer-Verlag, 1989

- [7] L.-Q. Pei, F. Guo, S.-X. Wu, and L. Chua, "Experimental confirmation of the period-adding route to chaos in a nonlinear circuit," *IEEE Trans. on Circuits and Systems*, Vol. 33, no. 4, pp. 438-442, April 1986.

- [8] K. Kaneko, Collapse of Tori and Genesis of Chaos in Dissipative Systems. Singapore: World Scientific, 1986.

Figure 4: Trajectories from the numerical results for diagram for  $\omega=0.32$ , ( $\epsilon=2$ ,  $\Gamma=0.3$ , and  $\nu=0.4$ ).(a) in the cylindrical space, (b) in the plane (x-y), and (c) Poincaré map.

Figure 5: Trajectories from the numerical results for diagram for  $\omega = 0.64$ , ( $\epsilon = 2$ ,  $\Gamma = 0.3$ , and  $\nu = 0.4$ ).(a) in the cylindrical space, (b) in the plane (x - y), and (c) Poincaré map.

Figure 6: Bifurcation diagrams illustrating Farey sequences for the circuit in Figure 2.

Figure 7: Simulation results giving a frequency division of (a) 3, and (b) 5.