1 Número de publicación:  $2\ 188\ 418$

21) Número de solicitud: 200102683

(1) Int. Cl.7: **G01R 31/28** G01R 31/3181 G06F 11/30

(2) PATENTE DE INVENCIÓN

B1

- 22 Fecha de presentación: 29.11.2001

- 43 Fecha de publicación de la solicitud: 16.06.2003

Fecha de la concesión: 18.10.2004

- 45 Fecha de anuncio de la concesión: 16.11.2004

- 45) Fecha de publicación del folleto de la patente: 16.11.2004

- (3) Titular/es: Universidad de Sevilla Valparaíso, 5, Segunda Planta 41013 Sevilla, ES

- (72) Inventor/es: Aguirre Echanove, Miguel; Tombs, Jonathan; Torralba Silgado, Antonio y García Franquelo, Leopoldo

- 4 Agente: No consta

- (4) Título: Método para análisis y test funcional de circuito digitales de gran dimensión mediante emuladores hardware.

- (57) Resumen:

Método para análisis y test funcional de circuito digitales de gran dimensión mediante emuladores Hardware. Parte de un número indefinido de eventos o condiciones (1), (1')... (1n), respectivos circuitos detectores (2), (2')... (2n), actuantes en combinación con un detector de flanco (3), que recibe información del pad externo de reactivación (4), y con la colaboración de un pad externo (5) de control, del sistema, es posible vigilar tanto eventos deterministas como eventos temporales, concretamente vigilar una condición determinista en tiempo de ejecución, vigilar una condición temporal en tiempo de ejecución, generar una señal o bandera que registre el evento, cualquiera que sea su naturaleza, congelar el circuito para facilitar su análisis desde un sistema gráfico o similar, y comunicar al sistema que se ha producido un evento e identificar cuál de los eventos programados se ha producido.

FIG.1

10

15

20

25

60

### DESCRIPCION

Método para análisis y test funcional de circuito digitales de gran dimensión mediante emuladores hardware.

Objeto de la invención

La presente invención se refiere a un sistema totalmente automatizado de verificación funcional de circuitos digitales de gran dimensión, basado en tres bloques originales: en primer lugar una circuitería digital genérica para la elaboración de sistemas de test funcionales basados en circuitos integrados de lógica programable, orientados al desarrollo de circuitos integrados digitales de gran dimensión que hace posible la automatización del proceso de depuración, en segundo lugar las directrices para el desarrollo de un sistema de emulación funcional para realizar las funciones de depuración requeridas y, en tercer lugar, una modificación en el método tradicional de desarrollo y depuración de sistemas digitales.

La invención es aplicable al ámbito de los circuitos digitales de gran dimensión y permite generalizar y sistematizar la inserción de circuitería de test e inspección en el circuito prototipo de forma totalmente automática.

#### Antecedentes de la invención

Las técnicas actuales, en el ámbito del análisis y test funcional de circuitos funcionales, se basan en sistemas "ad hoc", en las que los tests se realizan mediante sistemas basados en circuitos integrados de lógica programable desarrollando un prototipo orientado a cada test.

De forma más concreta el flujo de diseño de circuitos integrados digitales tradicional utiliza para todas las tareas de verificación funcional programas de software que realizan simulaciones. Estas requieren dos elementos: un modelo de circuito y los estímulos necesarios para la verificación exhaustiva del mismo. En la actualidad las técnicas tradicionales de depuración comienzan a ser insuficientes, fundamentalmente debido a dos motivos:

- En primer lugar la funcionalidad es tan compleja que la simulación mediante software del circuito requiere tiempos de computación muy elevados y, en la mayoría de los casos, impracticables.

- En segundo lugar la elaboración de los estímulos de simulación resulta una labor que presenta grandes dificultades por tener que representar gran cantidad de situaciones del circuito final y esto resulta a menudo impracticable.

Las técnicas de realización rápida de prototipos (rapid prototyping o prototipado rápido) mediante emulación cobran ahora importancia, ya que se trabaja con un modelo hardware basado en un circuito integrado de lógica programable insertado en el sistema final con ligeras modificaciones.

Las técnicas basadas en emulación presentadas en la literatura tiene la particularidad de estar asociadas a cada aplicación y no existen en la actualidad ni un procedimiento ni los medios complementarios que permitan plantear una situación válida para todas las situaciones.

En lo que se refiere a los soportes para emulación de las técnicas de prototipado rápido, se basan en el uso de dispositivos avanzados de lógica programable tipo FPGA-SRAM. Dentro de los dispositivos que actualmente se ofrecen al mercado, los hay capaces de ofrecer las siguientes prestaciones:

- Capacidad de ser programados tantas veces como sea preciso.

- Capacidad para leer la configuración y estado de un sistema.

- Capacidad para detener un reloj de un sistema, de forma adecuada y ser controlado.

- Prestaciones suficientemente elevadas para poder emular un circuito objeto de análisis en las condiciones de diseño.

Estos son los requisitos o prestaciones exigibles para la puesta en práctica del método objeto de la invención, como se verá más adelante.

Desde el punto de vista metodológico en la actualidad, tras la generación del código en alto nivel del circuito, simulación y pruebas básicas, se puede elaborar un prototipo emulado del sistema. En el se pueden producir situaciones en tiempo real o, en el peor de los casos, casi real, dependiendo de las limitaciones del circuito emulador. Es posible verificar el sistema final, y es posible verificar el funcionamiento global.

Descripción de la invención

Dentro del objeto de la invención una circuitería vigila eventos deterministas y temporales y sus combinaciones simultáneamente. El usuario decide qué señales se han de asociar a un evento mediante la inserción de comparadores (detección de eventos temporales) para activar los eventos. El usuario puede de forma combinada aplicar contadores (detección de eventos temporales) que temporicen la actividad del evento. Cada evento tiene asociada una máquina de estados que permite su desactivación desde del exterior con una señal adicional. Todas las señales de activación de los eventos se concentran en una función lógica OR que sale al exterior mediante una salida en resistencia a alimentación (pull-up). Cuando un evento se produce, la salida vale el valor lógico 1 mediante el mencionado pull-up, mientras que en caso contrario el circuito funciona normalmente y la salida vale el valor lógico 0. El valor lógico 1 permite un diálogo bidireccional a través de las líneas.

El método tanto para la parada de circuito como para su reactivación, consiste, en primer lugar, en la activación de un control de inhibición de la señal de reloj sobre cada elemento secuencial de cada circuito. Esto se consigue mediante la señal "Clock Enable". Cuando el circuito se encuentra en estado de evento detectado, a través de la señal de activación de evento se puede, mediante una transmisión de 0 a 1 lógico forzada desde el exterior, activar un circuito detector de flanco que genere un pulso de duración un único ciclo de reloj, que conectada al control de habilitación del reloj

posibilita la transición durante un único ciclo de reloj de los elementos secuenciales. La utilización de una estrategia de salida pull-up permite que el pad tenga un comportamiento bidireccional y pueda utilizarse como control del reloj. En cuanto al método para la identificación del evento producido, la lectura de la configuración interna y del estado del emulador soporte del circuito permite leer el estado de la señal de activación de cada uno de los eventos y, por tanto, saber su estado e identificar el evento producido.

El método permite la introducción de manera prácticamente ilimitada de condiciones de eventos, de forma totalmente automática y transparente para el usuario. La mencionada circuitería se introduce desde lenguaje de alto nivel, siendo por tanto susceptible de ser automatizado todo el proceso de inserción sobre el circuito original. Dado que el número de eventos es ilimitado y solamente depende de la capacidad del emulador, el usuario puede introducir tantos eventos como sea preciso mediante una descripción simple de los mismos, y un programa puede introducir automáticamente todos los cambios.

La utilización de este sistema en el flujo de desarrollo tradicional de un circuito integrado, consiste en utilizar un emulador con capacidad para depurar el diseño mediante la introducción de los eventos y la inspección del mismo, y facilita la introducción de una nueva técnica de depuración de diseño de circuitos digitales mediante el uso de las capacidades avanzadas de los emuladores. Gracias a la inserción de las condiciones de evento es posible realizar la verificación del funcionamiento potenciando extraordinariamente el tradicional método de desarrollo de circuitos. Por tanto la inserción y la utilización de la circuitería propuesta posibilita el análisis en tiempo de ejecución, es decir, utilizando un sistema totalmente funcional

Descripción de los dibujos

Para complementar la descripción que se está realizando y con objeto de ayudar a una mejor comprensión de las características del invento, de acuerdo con un ejemplo preferente de realización práctica del mismo, se acompaña como parte integrante de dicha descripción, un juego de dibujos en donde con carácter ilustrativo y no limitativo, se ha representado lo siguiente:

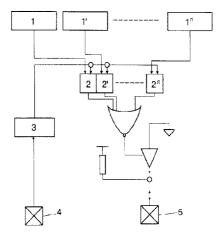

La figura 1.- Muestra la arquitectura del circuito necesario para cumplir los requerimientos del método de la invención, para varios eventos, asociados o independientes.

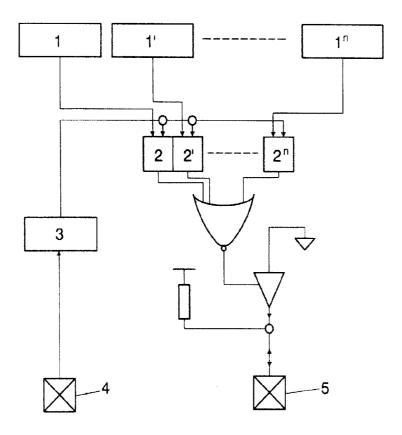

La figura 2.- Muestra el circuito de control del reloj del sistema.

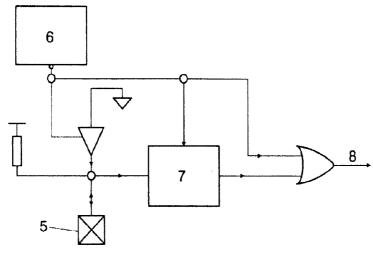

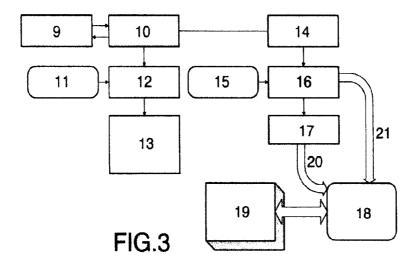

La figura 3.- Muestra, finalmente, un diagrama de bloques correspondiente a la metodología para el sistema de desarrollo de circuitos integrados digitales.

Realización preferente de la invención

El circuito objeto de análisis, en adelante COA, es un compendio de señales y operaciones combinacionales y circuitería secuencial que trabaja en general, en paralelo. La circuitería para la realización de test, en adelante CPT, que constituye la parte esencial de la invención, tiene la misión de detectar determinadas situaciones, generalmente asociadas a valores de las señales in-

ternas combinacionales y en su caso combinadas con la variable tiempo durante el funcionamiento del COA, que resultan de especial interés para el diseñador. Esto se consigue mediante la selección de eventos. Los eventos son situaciones de interés que se detectan durante el funcionamiento del circuito programadas por el usuario. Tras la evolución producida debida a su funcionamiento normal, el circuito, en el instante en que se produce el evento, puede reaccionar de dos maneras no excluyentes:

- Se detiene y permanece "congelado".

- Retiene el estado.

En ambos casos el diseñador puede inspeccionar los valores internos del sistema y analizarlo.

A partir de este concepto de "evento", el CPT debe soportar las siguientes tareas:

- Debe vigilar una combinación determinista en tiempo de ejecución, es decir, debe provocar un aviso ante un evento determinista.

- Debe vigilar la condición temporal en tiempo de ejecución, es decir, debe provocar una aviso ante un evento temporal.

- Debe generar una señal o bandera que registre el evento, cualquiera que sea su naturaleza.

- Debe congelar el circuito para facilitar su análisis desde un sistema gráfico o similar.

- Debe comunicar al sistema que se ha producido un evento e identificar cuál de los eventos programados se ha producido.

- Debe ser capaz de retomar la situación para continuar su ejecución.

De acuerdo con la misiones previstas para el CPT, que acaban de exponerse, dicho circuito debe incorporar los siguientes componentes:

- Comparadores para vigilar cada evento determinista.

- Contadores que registren ciclos de reloj para vigilar eventos temporales.

- Un circuito con la estructura de una máquina de estados finita por cada uno de los eventos, que permita que en un posterior análisis sea posible identificar que evento se ha disparado.

- Una señal que deshabilite el reloj del sistema y congela la actividad del COA.

- Una señal externa de control del sistema que se utiliza para comunicar la situación evento producido.

- Una señal externa de reactivación para deshabilitar el evento producido y reactivar el circuito objeto del análisis.

25

15

35

40

55

50

10

15

25

30

60

65

Una señal para la ejecución paso a paso del mismo.

El método propuesto no impone restricción alguna al número de eventos y su naturaleza, más que las que se deriven del emulador escogido para la realización física del sistema.

De acuerdo con la relación de componentes que acaba de exponerse, la arquitectura del circuito está representada en la figura 1 donde las referencias (1),  $(1')...(1^n)$  corresponden a respectivas condiciones específicas o eventos, (2),  $(2')...(2^n)$  los respectivos detectores, la referencia (3) a un detector de flanco y las referencias (4) y (5) respectivamente al pad externo de reactivación y el pad externo de control del sistema.

Como se desprende de la observación de la citada figura 1 la arquitectura del circuito no presenta limitación en tamaño y posibilidades de vigilancia de eventos, es decir, el CPT tiene un carácter genérico y las limitacines están impuestas por los recursos disponibles del emulador. La circuitería se describe mediante lenguajes de hardware de alto nivel, alfanuméricos (HDLs), y configuran cada comparador y cada contador por su descripción paramétrica.

En el circuito de control de reloj del sistema, representado en la figura 2, participa un bloque (6) detector de condiciones de parada, el citado pad externo (5) de control del sistema, y un bloque (7) detector de flanco positivo, generador de un ciclo, generando la señal (8) que habilita el reloj. Así pues, la sección de ejecución paso a paso se basa en la utilización de la línea de control del sistema como señal de activación de un ciclo de reloj dada su naturaleza bidireccional. El circuito central consiste en una máquina de estados que permite ser activada mediante una transmisión de la señal de control del sistema.

Los circuitos descritos en las figuras 1 y 2 son complementarias y comparten la circuitería externa.

En lo que se refiere al método de desarrollo las técnicas actuales utilizan, para el diseño del circuito de gran dimensión, los anteriormente mencionados lenguajes de alto nivel (HDLs). Mediante éstos se describen los circuitos con cierto nivel de abstracción y, a través de un proceso de síntesis y optimización, se genera una descripción de los circuitos finales. Gracias a la síntesis de generación de circuitos digitales se ha acelerado enormemente al facilitar la elaboración de circuitos altamente parametrizados y generalizados.

El CPT se acopla de modo natural al COA si ambos están descritos de una manera similar, es decir en un lenguaje de alto nivel. Una vez realizada la síntesis conjunta el circuito resultante contiene tanto la circuitería original como la específica para el análisis.

Una de las posibilidades del método es que se puede definir un sencillo lenguaje de especificación de eventos que facilite la automatización del sistema.

El sistema de análisis utiliza los siguientes elementos:

- Circuito emulador (CE) de sistemas digitales, como por ejemplo una o varias FPGA-s que cumplan con los requisitos establecidos en el apartado de antecedentes de la invención, es decir que tenga capacidad de ser programado tantas veces como sea preciso, capacidad para leer la configuración y el estado del sistema, capacidad para detener el reloj del sistema de forma adecuada y ser controlado, y finalmente capaz de ofertar prestaciones suficientemente elevadas para poder emular el COA en las condiciones del diseño.

- Sistema de visualización (SV) que permita hacer comprensible al usuario el contenido del sistema de emulación. Por lo común, este elemento será una computadora personal o una estación de trabajo y tiene como finalidad controlar y supervisar todo el proceso de emulación.

- Circuito de enlace (CL) entre el circuito emulador (CE) y el sistema de visualización (SV), que realizan las operaciones de transferencia de información entre los sistemas.

Se encarga de hacer compatibles los protocolos de transferencia de información de ambos elementos. Normalmente se utilizará un circuito integrado de aplicación específica (ASIC) programable o no.

El funcionamiento del sistema es el siguiente: el circuito emulador (CE) está configurado con ambos circuitos (COA) y (CPT), se inserta dentro del sistema final y envía una señal al sistema de visualización a través del circuito de enlace indicando que el sistema ha alcanzado una situación prevista como evento. En este instante el circuito emulador:

- Deja de funcionar y queda en estado "congelado".

- Retiene el estado del sistema para su análi-

El siguiente paso es la transferencia del contenido de circuito emulador al sistema de visualización, donde se identifica el evento y se procesa la información recogida del emulador para hacerla comprensible, lo que se realiza mediante el circuito de enlace.

Finalmente se genera la orden de continuación desde el sistema de visualización al circuito emulador, ya sea utilizando el sistema "paso a paso", o bien mediante la señal externa de reactivación.

Desde el punto de vista metodológico el CPT facilita de modo natural mecanismos de parada y continuación del sistema y permite la introducción de mecanismos de control y disparo que facilitan la detección de errores durante el funcionamiento del sistema. La circuitería puede ser introducida desde una descripción de alto nivel (HDL) del circuito, y por tanto desde una herramienta software en los estadios primarios del flujo de diseño. La descripción del circuito se realiza mediante la determinación de parámetros. Por tanto se puede realizar la inserción del CPT de forma totalmente automatizada sin que se precise intervención manual alguna.

Los emuladores anteriormente mencionados pueden ser inspeccionados y permiten que se puedan relacionar señales que están en la descripción de alto nivel con registros y señales físicamente presentes en el emulador y sus valores en funcionamiento, mediante un cuidadoso control del proceso de síntesis. Este proceso de inspección interna precisa además de la ayuda de un mapa que relacione la configuración con señales en la descripción de alto nivel. Este mapa lo facilitan los fabricantes.

La metodología aparece representada en el esquema de la figura 3, donde el bloque (9) se corresponde con la simulación modular de verificación de alto nivel, el bloque (10) con la descripción de alto nivel del circuito (HDL), el bloque (11) con la tecnología para la realización física, el bloque (12) es el bloque de síntesis y el bloque

(13) la metodología para la realización física. Paralelamente el bloque (14) se corresponde con la inserción del circuito para el test, el bloque (15) la tecnología del emulador, el bloque (16) la síntesis, el bloque (17) la metodología para la realización física para el emulador, el bloque (18) el sistema de visualización (Interface hombre-máquina), y el bloque (19) el sistema final con el emulador, correspondiéndose las flechas (20) y (21) respectivamente con la configuración y mapa de variables.

Por tanto, a partir de la inspección interna se permite relacionar el código de alto nivel con sus valores durante el funcionamiento real. La principal consecuencia de este hecho es que el sistema puede ser perfectamente caracterizado ante un evento y, lo que lo hace realmente potente, puede indentificarse el propio evento producido, además el número de eventos no está limitado.

### REIVINDICACIONES

- 1. Método para análisis y test funcional de circuito digitales de gran dimensión mediante emuladores hardware, **caracterizado** porque consisten en circuitos que vigilan eventos deterministas, temporales y sus combinaciones simultáneamente. El usuario decide en cada momento que señales se han de monitorizar mediante la inserción comparadores para activar cada evento, o bien, de forma combinada, aplicar contadores que temporicen la activación del evento. Los eventos que pueden ser desactivados desde el exterior con una señal adicional.

- 2. Método para análisis y test funcional de circuito digitales de gran dimensión mediante emuladores hardware, según reivindicación 1<sup>a</sup>. El método tanto para la parada de circuito como para su reactivación, consiste, en primer lugar, en la activación de un control de inhibición de la señal de reloj sobre cada elemento secuencial de cada circuito. Esto se consigue mediante la señal "Clock Enable" o habilitación del reloj, provista en todos ellos. Cuando el circuito se encuentra en estado de evento detectado, a través de la señal de activación de evento se puede, mediante una transición de 0 a 1 lógico forzada desde el exterior, activar un circuito detector de flanco que genere un pulso de duración un único ciclo de reloj, que conectada al control de habilitación del reloj posibilita la transición durante un único ciclo de reloj de los elementos secuenciales. La utilización de una estrategia de salida en pull-up permite que el pad tenga un comportamiento bidireccional y pueda utilizarse tanto como control del reloj, como detector del propio evento.

- 3. Método para análisis y test funcional de circuito digitales de gran dimensión mediante emuladores hardware, según reivindicaciones anterio-

- res, caracterizado porque para la identificación del evento producido, la lectura de la configuración interna y del estado del emulador soporte del circuito, permite leer el estado de la señal de activación de cada uno de los eventos y, por tanto, conocer su estado e identificar que evento se ha producido.

- 4. Método para análisis y test funcional de circuito digitales de gran dimensión mediante emuladores hardware, según reivindicaciones anteriores, caracterizado porque las condiciones de eventos, ilimitadas en número, se introducen de forma totalmente automática y transparente para el usuario, desde lenguaje de alto nivel, siendo susceptible de ser automatizado todo el proceso de inserción sobre el circuito original, sin más limitación en cuanto al número de eventos que la capacidad del emulador, efectuándose la introducción de los eventos mediante una descripción simple de los mismos, mientras que un programa permite producir automáticamente todos los cambios

- 5. Circuitería para la puesta en práctica del método de las reivindicaciones anteriores, caracterizada porque en la misma participa comparadores para vigilar cada evento determinista, contadores que registren ciclos de reloj para vigilar eventos temporales, un circuito tipo máquina de estados finita por cada uno de los eventos, que permite que en un posterior análisis sea posible identificar que evento se ha disparado, una señal que deshabilita el reloj del sistema y congela la actividad del COA, una señal externa de control del sistema que se utiliza para comunicar la situación "evento producido", una señal externa de reactivación para deshabilitar el evento producido y reactivar el circuito objeto de análisis y una señal para la ejecución paso a paso del mismo.

40

45

50

55

60

FIG.1

FIG.2

11) ES 2 188 418

②1) Nº de solicitud: 200102683

② Fecha de presentación de la solicitud: 29.11.2001

32 Fecha de prioridad:

# INFORME SOBRE EL ESTADO DE LA TÉCNICA

| (51) | Int. Cl.7: | G01R 31/28, 31/3181, G06F 11/30 |

|------|------------|---------------------------------|

|      |            |                                 |

## **DOCUMENTOS RELEVANTES**

| Categoría                                                                                                                       |                                                                                                          | Documentos citados                                                                                                                                                                         | Reivindicaciones afectadas |  |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|

| Α                                                                                                                               | US 5946472 A (GRAVES et a<br>línea 4 - columna 12, línea 5                                               | 1-5                                                                                                                                                                                        |                            |  |

| А                                                                                                                               | WO 9316433 A (SEIKO EPS<br>línea 25 - página 16, línea 10<br>línea 6; figuras 2,3,6,7.                   | 1-5                                                                                                                                                                                        |                            |  |

| А                                                                                                                               | US 5937179 A (SWOBODA)<br>línea 51 - columna 7, línea 3                                                  |                                                                                                                                                                                            | 1-5                        |  |

|                                                                                                                                 |                                                                                                          |                                                                                                                                                                                            |                            |  |

|                                                                                                                                 |                                                                                                          |                                                                                                                                                                                            |                            |  |

|                                                                                                                                 |                                                                                                          |                                                                                                                                                                                            |                            |  |

|                                                                                                                                 |                                                                                                          |                                                                                                                                                                                            |                            |  |

| Categori                                                                                                                        | a de los documentos citados                                                                              |                                                                                                                                                                                            |                            |  |

| X: de particular relevancia Y: de particular relevancia combinado con otro/s misma categoría A: refleja el estado de la técnica |                                                                                                          | O: referido a divulgación no escrita P: publicado entre la fecha de prioridad y la de pre de la solicitud E: documento anterior, pero publicado después de de presentación de la solicitud |                            |  |

| -                                                                                                                               | El presente informe ha sido realizado    para todas las reivindicaciones   para las reivindicaciones nº: |                                                                                                                                                                                            |                            |  |

| Fecha d                                                                                                                         | e realización del informe<br>05.05.2003                                                                  | <b>Examinador</b><br>P. Pérez Fernández                                                                                                                                                    | Página<br>1/1              |  |